1.本发明涉及一种存储器结构及其制造方法,且特别是涉及一种非挥发性存储器结构及其制造方法。

背景技术:

2.由于非挥发性存储器(non-volatile memory)可进行多次数据的存入、读取与抹除等操作,且具有当电源供应中断时,所存储的数据不会消失、数据存取时间短以及低消耗功率等优点,所以已成为个人计算机和电子设备所广泛采用的一种存储器。

3.专利文献1(美国专利第7,592,224号(us 7,592,224 b2))公开了一种存储元件。专利文献1的存储元件具有垂直通道以及位于沟槽中的选择栅极与控制栅极,且利用不连续的存储构件(discontinuous storage elements,dse)(如,硅纳米晶粒)来存储电荷。另外,专利文献2(美国专利第8,710,576号(us 8,710,576 b2))公开了一种闪存存储器(flash memory)。专利文献2的闪存存储器具有具有垂直通道,且利用氧化物/氮化物/氧化物(ono)结构来存储电荷。

4.然而,如何能够进一步地提升存储器元件的电性效能(electrical performance)与集成度为目前业界持续努力的目标。

技术实现要素:

5.本发明提供一种非挥发性存储器结构,其可有效地提升存储器元件的电性效能与集成度。

6.本发明提出一种非挥发性存储器结构,包括基底、选择栅极、控制栅极与电荷存储结构。在基底中具有沟槽。选择栅极设置在沟槽中。控制栅极设置在沟槽中,且位于选择栅极上。电荷存储结构设置在控制栅极与选择栅极之间以及控制栅极与基底之间。电荷存储结构包括氮化物层、第一氧化物层与第二氧化物层。氮化物层设置在选择栅极上与沟槽的两侧壁上。氮化物层为连续结构。第一氧化物层设置在氮化物层与选择栅极之间。第二氧化物层设置在控制栅极与氮化物层之间。

7.依照本发明的一实施例所述,在上述非挥发性存储器结构中,选择栅极的材料例如是掺杂多晶硅。

8.依照本发明的一实施例所述,在上述非挥发性存储器结构中,控制栅极可具有突出于基底的顶面的突出部。

9.依照本发明的一实施例所述,在上述非挥发性存储器结构中,突出部的最大宽度可大于沟槽的最大宽度。

10.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括间隙壁。间隙壁设置在突出部的侧壁上。

11.依照本发明的一实施例所述,在上述非挥发性存储器结构中,间隙壁可为单层结构。

12.依照本发明的一实施例所述,在上述非挥发性存储器结构中,间隙壁可为多层结构。

13.依照本发明的一实施例所述,在上述非挥发性存储器结构中,部分控制栅极可位于基底的顶面上。

14.依照本发明的一实施例所述,在上述非挥发性存储器结构中,控制栅极的剖面形状可为t形。

15.依照本发明的一实施例所述,在上述非挥发性存储器结构中,控制栅极的材料例如是掺杂多晶硅。

16.依照本发明的一实施例所述,在上述非挥发性存储器结构中,电荷存储结构可共形地设置在沟槽的两侧壁上与选择栅极的顶面上。

17.依照本发明的一实施例所述,在上述非挥发性存储器结构中,部分电荷存储结构可位于基底的顶面上。

18.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括介电层。介电层设置在选择栅极与基底之间。

19.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括第一掺杂区与第二掺杂区。第一掺杂区位于沟槽下方的基底中。第二掺杂区位于沟槽的一侧的基底中。

20.依照本发明的一实施例所述,在上述非挥发性存储器结构中,部分第一掺杂区可位于选择栅极两侧的基底中。第一掺杂区的顶部可低于选择栅极的顶面。

21.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括第三掺杂区。第三掺杂区位于沟槽的另一侧的基底中。

22.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括阱区。阱区位于基底中。第一掺杂区、第二掺杂区与第三掺杂区可位于阱区中。

23.依照本发明的一实施例所述,在上述非挥发性存储器结构中,阱区的导电型可不同于第一掺杂区、第二掺杂区与第三掺杂区的导电型。

24.依照本发明的一实施例所述,在上述非挥发性存储器结构中,还可包括第一轻掺杂漏极与第二轻掺杂漏极。第一轻掺杂漏极(lightly doped drain,ldd)位于第二掺杂区与控制栅极之间的基底中。第二轻掺杂漏极位于第三掺杂区与控制栅极之间的基底中。

25.依照本发明的一实施例所述,在上述非挥发性存储器结构中,第一轻掺杂漏极与第二轻掺杂漏极的导电型可同于第一掺杂区与第二掺杂区的导电型。

26.基于上述,在本发明所提出的非挥发性存储器结构中,由于作为电荷存储层的氮化物层设置在沟槽的两侧壁上,因此可实现单一存储单元中存储二位数据(two bits per cell)的存储器元件。此外,由于选择栅极与控制栅极设置在沟槽中,所以非挥发性存储器结构可具有垂直通道与埋入式的选择栅极,因此可防止短通道效应(short channel effect)与过度抹除现象(over-erase phenomenon),且可具有较高的存储单元密度(cell density)。如此一来,可有效地提升存储器元件的电性效能与集成度。

27.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

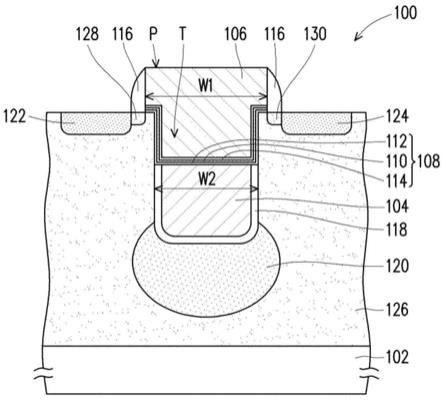

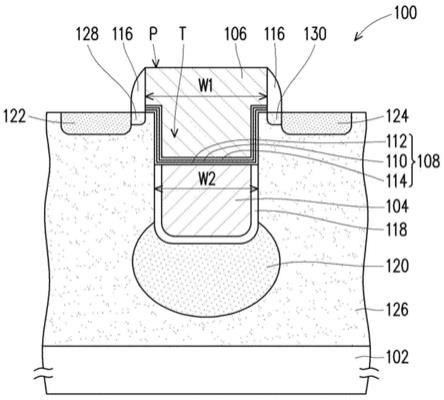

28.图1为本发明一实施例的非挥发性存储器结构的剖视图。

29.符号说明

30.100:非挥发性存储器结构

31.102:基底

32.104:选择栅极

33.106:控制栅极

34.108:电荷存储结构

35.110:氮化物层

36.112,114:氧化物层

37.116:间隙壁

38.118:介电层

39.120,122,124:掺杂区

40.126:阱区

41.128,130:轻掺杂漏极

42.p:突出部

43.t:沟槽

44.w1,w2:最大宽度

具体实施方式

45.图1为本发明一实施例的非挥发性存储器结构的剖视图。

46.请参照图1,非挥发性存储器结构100包括基底102、选择栅极104、控制栅极106与电荷存储结构108。在基底102中具有沟槽t。基底100可为半导体基底,如硅基底。

47.选择栅极104设置在沟槽t中。亦即,选择栅极104可为埋入式选择栅极。选择栅极104的材料例如是掺杂多晶硅等导体材料。

48.控制栅极106设置在沟槽t中,且位于选择栅极104上。控制栅极106可具有突出于基底102的顶面的突出部p。突出部p的最大宽度w1可大于沟槽t的最大宽度w2。如此一来,部分控制栅极106可位于基底102的顶面上,而使得控制栅极106的剖面形状可为t形。控制栅极106的材料例如是掺杂多晶硅等导体材料。

49.电荷存储结构108设置在控制栅极106与选择栅极104之间以及控制栅极106与基底102之间。电荷存储结构108可共形地设置在沟槽t的两侧壁上与选择栅极104的顶面上。此外,部分电荷存储结构108可位于基底102的顶面上。电荷存储结构108包括氮化物层110、氧化物层112与氧化物层114。氮化物层110设置在选择栅极104上与沟槽t的两侧壁上,且可用以作为电荷存储层。氮化物层110为连续结构。氧化物层112设置在氮化物层110与选择栅极104之间,且可设置在氮化物层110与基底102之间。氧化物层114设置在控制栅极106与氮化物层110之间。

50.此外,非挥发性存储器结构100还可包括间隙壁116、介电层118、掺杂区120、掺杂区122、掺杂区124、阱区126、轻掺杂漏极128与轻掺杂漏极130中的至少一者。间隙壁116设置在突出部p的侧壁上。间隙壁116可为单层结构或多层结构。间隙壁116的材料例如是氧化

硅、氮化硅或其组合。介电层118设置在选择栅极104与基底102之间。介电层118的材料例如是氧化硅。

51.掺杂区120位于沟槽t下方的基底102中。掺杂区120可作为源极线(source line)使用。部分掺杂区120可位于选择栅极104两侧的基底102中。掺杂区120的顶部可低于选择栅极104的顶面。掺杂区122位于沟槽t的一侧的基底102中。掺杂区124位于沟槽t的另一侧的基底102中。阱区126位于基底102中。掺杂区120、掺杂区122与掺杂区124可位于阱区126中。阱区126的导电型可不同于掺杂区120、掺杂区122与掺杂区124的导电型。轻掺杂漏极128位于掺杂区122与控制栅极106之间的基底102中。轻掺杂漏极130位于掺杂区124与控制栅极106之间的基底102中。在一些实施例中,「轻掺杂漏极」也可称为源极/漏极延伸区(source/drain extension,sde)。轻掺杂漏极128与轻掺杂漏极130可分别位于间隙壁116下方。轻掺杂漏极128与轻掺杂漏极130可位于阱区126中。轻掺杂漏极128与轻掺杂漏极130的导电型可同于掺杂区120、掺杂区122与掺杂区124的导电型,且可不同于阱区126的导电型。

52.举例来说,掺杂区120、掺杂区122、掺杂区124、轻掺杂漏极128与轻掺杂漏极130可为n型掺杂区,且阱区126可为p型阱区,但本发明并不以此为限。在其他实施例中,掺杂区120、掺杂区122、掺杂区124、轻掺杂漏极128与轻掺杂漏极130可为p型掺杂区,且阱区126可为n型阱区。

53.基于上述实施例可知,在本发明所提出的非挥发性存储器结构100中,由于作为电荷存储层的氮化物层110设置在沟槽t的两侧壁上,因此可实现单一存储单元中存储二位数据的存储器元件。此外,由于选择栅极104与控制栅极106设置在沟槽t中,所以非挥发性存储器结构100可具有垂直通道与埋入式的选择栅极104,因此可防止短通道效应与过度抹除现象,且可具有较高的存储单元密度。如此一来,可有效地提升存储器元件的电性效能与集成度。

54.综上所述,在上述实施例的非挥发性存储器结构中,由于将氮化物层设置在沟槽的两侧壁上,且将选择栅极与控制栅极设置在沟槽中,因此可有效地提升存储器元件的电性效能与集成度。

55.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。