1.本发明涉及数字集成电路设计技术领域,具体涉及一种数字正交混频器混频方法、混频器电路和混频器。

背景技术:

2.在当前数字混频器设计中,通常对照原理图,直接形成电路。实混频结构简单,只需要两个乘法就可以实现,但是复混频就相对复杂一点,需要四个乘法和两个加法实现,并且由于复混频特点,信号频率最大值扩大为之前的倍。还需要两个乘法器来进行幅度衰减,所以一共需要六个乘法器,两个加法器,电路设计中乘法器会占用很大的面积,因为这种电路在幅度衰减时需要用到乘法器运算,资源消耗较大。

技术实现要素:

3.本发明解决的一个主要问题是提供一种新型的数字正交混频器,减少乘法器的使用,减少资源消耗。

4.根据本发明的一个方面,提供一种数字正交混频器混频方法,包括:

5.所述数字正交混频器依次包括相位累加器,相位选择器,相幅转换器和混频器;

6.所述相位累加器利用输入的频率控制字、相位控制字进行相位在时间上的累加;

7.所述相位选择器通过所述相位的累加产生与实混频模式或复混频模式相对应的相位值;

8.所述相幅转换器根据所述相位值利用三段式cordic算法输出余弦本振信号和正弦本振信号;

9.所述混频器对所述余弦本振信号、所述正弦本振信号、i路输入信号和q 路输入信号进行数字运算以进行混频,在复混频模式下,所述混频器混频时通过乘法器和加法器进行三次乘法和四次加法运算进行混频,在实混频模式下进行两次乘法运算进行混频。

10.进一步地,通过一个加法器和一个触发器实现相位在时间上的累加,当混频模式为实混频时,相位选择器的幅度不需增加;

11.当混频模式为复混频时,所述相位选择器的幅度增加π/4。

12.进一步地,对所述正弦本振信号和所述余弦本振信号进行加法运算得到 ac1信号;

13.对i路输入信号和q路输入信号进行加法运算得到ac2信号;

14.对ac1和ac2进行乘法运算得到第一信号pro1;

15.对所述余弦本振信号和所述q路输入信号进行乘法运算得到第二信号 pro2;

16.对所述正弦本振信号和所述i路输入信号进行乘法运算得到第三信号pro3。

17.进一步地,对所述第一信号pro1、所述第二信号pro2和所述第三信号pro3 中的余弦本振信号和正弦本振信号进行和角公式变换,得到新频率的余弦本振信号和正弦本振信号。

18.进一步地,将所述新频率的余弦本振信号和所述新频率的正弦本振信号代入第一信号pro1、所述第二信号pro2和所述第三信号pro3中并进行幅度衰减得到新的pro1信号、新的pro2信号和新的pro3信号。

19.进一步地,将所述新的pro1信号和所述新的pro2信号通过加法器相加得到所述混频器i路的输出信号。

20.进一步地,将所述新的pro1信号和所述新的pro3信号相减得到所述混频器q路的输出信号。

21.根据本发明的另一个方面,还公开一种数字正交混频器混频电路,所述数字正交混频器混频电路用于实现如前任一所述的一种数字正交混频器混频方法,所述混频电路包括:

22.第一加法器、第二加法器、第三加法器、第四加法器、第一乘法器、第二乘法器和第三乘法器;

23.所述第一加法器和所述第二加法器的信号输出端分别与所述第一乘法器的信号输入端连接;

24.所述第一乘法器的信号输出端与所述第四加法器的信号输入端相连;

25.所述第一乘法器的信号输出端还与所述第三加法器的信号输出端相连;

26.所述第二乘法器信号输出端和所述第三加法器的信号输入端相连接,所述第三加法器的信号输出端用于输出i路混频信号;

27.所述第三乘法器的信号输出端和所述第四加法器的信号输入端相连接,所述第四信号输出端用于输出q路混频信号。

28.根据本发明的再一个方面,还公开一种数字正交混频器,其上载有前所述的一种数字正交混频器混频电路,所述正交混频器用于实现如前任一所述的一种数字正交混频器混频方法。

29.本发明的数字正交混频器混频方法中,在混频器装置中加入相位选择器模块,并通过优化混频器电路模块,使外部输入的i和q两路信号以及相位选择产生的cos和sin本振信号做乘加运算,包括使用三个乘法,四个加法的技术手段达到了减少乘法运算,减少芯片面积和功耗降低资源消耗的效果,同时本振信号、输入信号与0的选择器还可以起到低功耗的作用。

附图说明

30.本发明构成说明书的一部分附图描述了本发明的实施例,并且连同说明书一起用于解释本发明的原理。

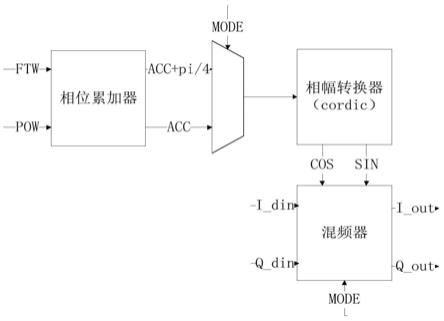

31.图1为本发明实施例中数字正交混频器的整体结构图。

32.图2为本发明实施例中相位累加器的电路示意图。

33.图3为本发明实施例中混频器电路优化结构示意图。

34.其中,1

‑

第一加法器、2

‑

第二加法器、3

‑

第三加法器、4

‑

第四加法器、5

‑

第一乘法器、6

‑

第二乘法器和7

‑

第三乘法器

具体实施方式

35.下面将结合附图来详细描述本发明的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本发明的范围。

36.同时,应当明白,为了便于描述,附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。

37.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本发明及其应用或使用的任何限制。

38.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

39.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

40.在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

41.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

42.如图1所示,为本发明的数字正交混频器的整体结构图,包括相位累加器,相位选择器,相幅转换器和混频器;所述相位累加器通过输入的ftw(频率控制字)、pow(相位控制字)来得到当前相位;相位选择器根据实混频复混频得到两个不同的相位值;相幅转换器采用三段式cordic算法,得到混频所需要的cos 和sin本振信号,最终在混频器中进行乘加运算,完成混频;

43.三段式cordic算法具体实现流程为:

44.先为rom查找表,再进行近似迭代运算,最后进行最后几个步骤的迭代运算,减少电路延时。

45.如图2所示为相位累加器模块的电路示意图,相位累加器模块通过一个加法器和一个触发器实现相位在时间上的累加,即用来计算当前正弦本振信号的相位,如果输入的频率控制字ftw为16位,那么相位累加器需要16位的加法器实现,通过加法器在每一个时刻下的值来判断当前相位,通过相位来确定当前cos和sin本振信号的具体值。

46.正交混频器混频的传统原理为:混频一般分为两种,实混频和复混频,实混频输入看作一个实数信号cos(ω0nt),将一路信号分别与本振信号 cos(ω1nt) j*sin(ω1nt)相乘,输入的iq两路信号设置为相同即可,如(1)和(2):

[0047][0048]

实混频可以看作将信号频谱向两侧搬移,产生基带分量ω0‑

ω1和高频分量ω0 ω1,经过滤波器滤波,高频分量通常会被消除,所以信号采用实混频经过滤波会有衰减;复混频输入看作一个复数信号,分为i和q两路,分别为实数部分和虚数部分cos(ω0nt) jsin(ω0nt),将这两部分与本振信号 cos(ω1nt) j*sin(ω1nt)相乘,得到最终结果,此时输入的iq两路信号为:

[0049][0050]

其中,ω0、ω1分别为不同的本振信号角频率,n=(123

……

n),t为采样间隔时间,复混频在频谱上是将输入信号单向搬移到基带,并不会产生额外的分量,经过滤波器并不会引起衰减,但是复混频之后,iq两路信号满幅会扩大倍,为了输出幅度与实混频相符,会进行3db衰减,为了把iq两路输出的幅度衰减所用到的乘法优化掉,本发明实施例在混频器电路中减少两个乘法运算,大大减少了资源消耗。

[0051]

如图3所示为优化后的混频器电路的具体结构:

[0052]

所述混频器包括第一加法器1、第二加法器2、第三加法器3、第四加法器 4、第一乘法器5、第二乘法器6和第三乘法器7;

[0053]

所述第一加法器1和所述第二加法器2的信号输出端分别与所述第一乘法器5的信号输入端连接;

[0054]

所述第一乘法器5的信号输出端与所述第四加法器4的信号输入端相连;

[0055]

所述第一乘法器5的信号输出端还与所述第三加法器3的信号输出端相连;

[0056]

所述第二乘法器6信号输出端和所述第三加法器3的信号输入端相连接,

[0057]

所述第三加法器3的信号输出端用于输出i路混频信号;

[0058]

所述第三乘法器7的信号输出端和所述第四加法器4的信号输入端相连接,所述第四信号输出端用于输出q路混频信号。

[0059]

混频器载复混频模式下的混频原理为:首先对cos本振信号,sin本振信号, i路输入信号和q路输入信号根据混频模式(实混频或复混频)进行选择;

[0060]

本实施例混频方法应用于数字下变频模块,所以复混频的结果可以看作(5) 和(6),其中i、q为输入信号:

[0061][0062][0063]

首先,我们可以把输入信号和本振信号进行两两组合,得到三个新的信号:

[0064]

pro1=(i q)*cos(ω1nt)

ꢀꢀ

(7)

[0065]

pro2=(sin(ω1nt)

‑

cos(ω1nt))*q

ꢀꢀ

(8)

[0066]

pro3=(sin(ω1nt) cos(ω1nt))*i

ꢀꢀ

(9)

[0067]

然后,将信号(7)

‑

(9)中的本振信号进行和角公式变换,得到新的信号 (10)

‑

(12):

[0068][0069][0070][0071]

接着,将公式(10)、(11)和(12)中的ω1nt π/4替换为ω2nt,得到新频率的本振信号形式,将新频率的本振信号替换到信号(7)

‑

(9)中,并且进行幅度衰减,得到新的pro1输出信号、新的pro2输出信号和新的pro3输出信号:

[0072]

pro1=1/2(i q)*(sin(ω2nt) cos(ω2nt))

ꢀꢀ

(13)

[0073]

pro2=

‑

(cos(ω2nt))*q

ꢀꢀ

(14)

[0074]

pro3=(sin(ω2nt))*i

ꢀꢀ

(15)

[0075]

最终通过新的pro1输出信号、新的pro2输出信号相加得到i路输出信号,和通过新的pro1输出信号和新的pro3输出信号相减得到q路的输出信号:

[0076]

i路=pro1 pro2

ꢀꢀ

(16)

[0077]

q路=pro1

‑

pro3

ꢀꢀ

(17)

[0078]

其中,ω2为代替之后的本振信号角频率优化后的混频器混频方法使用实混频时不需要将相位加pi/4,并且不需要在混频器中使用额外的加法乘法,而是通过选择器就行,选择器上面就是复混频,下面就是实混频,上面和0进行选择的选择器可以使实混频的时候不改变信号值,电路不进行01翻转就没有动态功耗;具体实现时需要考虑时序问题,以及电路中信号的相位问题,并使用好流水线结构。

[0079]

数字电路中乘法器占最大的资源消耗,优化后的混频器电路和正交混频器混频方法可以减少芯片面积和功耗,减少资源消耗,达到和传统混频装置同样的效果,相比现有技术,本方法共减少了三个乘法器。

[0080]

以上所述仅为本发明的较佳实施例而已,并不用于限制本发明,凡在本发明的精神和原则范围之内所作的任何修改、等同替换以及改进等,均应包含在本发明的保护范围之内。

[0081]

还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。