1.本公开内容一般地涉及半导体,并且具体地,涉及用于形成半导体结构的方法,并且具体地,涉及在载体衬底上形成碳化硅和氮化物结构。

背景技术:

2.碳化硅和第iii族氮化物,比如氮化镓,是用于信号处理和量子应用的理想半导体。与目前用于低损耗光子学和芯片上非线性光学的其他材料(比如硅、二氧化硅和氮化硅材料)相比,这些材料具有大于3ev的宽带隙和更大的非线性光学系数。

3.碳化硅(sic)是包含硅和碳的半导体材料。碳化硅可用于量子信息处理以及其他目的的装置中。例如,碳化硅结构中的色心可用于提供指示其电子自旋状态的光学读数。每个色心都是量子计算中的量子位。量子位的状态可以是逻辑“0”、逻辑“1”或两种状态的叠加。例如,可以将色心并入光子器件中,比如用于波导元件的微腔。

4.在碳化硅结构上制造器件可能具有挑战性。例如,与其他材料比如硅相比,使用具有碳化硅和第iii族氮化物的薄膜形成的器件可能比期望的更难以制造。薄膜器件包括一个或多个薄膜层,其中薄膜层的厚度可以为纳米级到几微米。

5.与材料比如硅相比,使用在晶片上形成的碳化硅和第iii族氮化物的薄膜器件的质量可能不如所期望的那样好。因此,期望有一种方法和装置考虑到至少上面讨论的一些问题以及其他可能的问题。例如,期望有一种克服关于形成具有期望质量的碳化硅和第iii族氮化物结构的技术问题的方法和装置。

技术实现要素:

6.本公开内容的实施方式提供了一种用于形成半导体结构的方法。在碳化硅衬底上形成一组第iii族氮化物层。碳化硅衬底包括掺杂层。掺杂层具有的掺杂水平使得掺杂层使用光电化学蚀刻工艺被蚀刻而碳化硅衬底的其他部分保持未被蚀刻。在所述组第iii族氮化物层上形成第一氧化物层。所述组第iii族氮化物层位于第一氧化物层和碳化硅衬底之间。将第一氧化物层与载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层。研磨碳化硅衬底。当碳化硅衬底中的一部分掺杂层实现暴露时停止研磨。使用光电化学蚀刻来蚀刻碳化硅衬底,使得当暴露碳化硅衬底中的该部分掺杂层时除去掺杂层并使碳化硅衬底中的碳化硅层保留。使用碳化硅层和所述组第iii族氮化物层形成半导体结构。

7.本公开内容的另一个实施方式提供用于形成半导体结构的方法。将位于在碳化硅衬底上形成的一组第iii族氮化物层上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层。碳化硅衬底具有掺杂层。使用光电化学蚀刻工艺蚀刻具有掺杂层的碳化硅衬底,其中掺杂层的掺杂水平使得掺杂层被除去并且碳化硅衬底中的碳化硅层保持未被蚀刻。使用碳化硅层和所述组第iii族氮化物层形成半导体结构。

8.本公开内容的又另一个实施方式提供了包括制造设备和控制系统的产品管理系统。控制系统控制制造设备以将位于在碳化硅衬底上形成的一组第iii族氮化物层上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层。碳化硅衬底具有掺杂层。使用光电化学蚀刻工艺蚀刻具有掺杂层的碳化硅衬底。掺杂层的掺杂水平使得掺杂层被除去并且碳化硅衬底中的碳化硅层保持未被蚀刻。使用碳化硅层和所述组第iii族氮化物层形成半导体结构。

9.特征和功能可以在本公开内容的各个实施方式中独立地实现,或者可以在又其他实施方式中组合,其中可以参考以下描述和附图来了解更多细节。

附图说明

10.在所附权利要求中阐述了被认为是说明性实施方式的特征的新颖特征。然而,当结合附图阅读时,通过参考本公开内容的说明性实施方式的以下详细描述,将最好地理解说明性实施方式及其优选的使用方式,其进一步的目的和特征,其中:

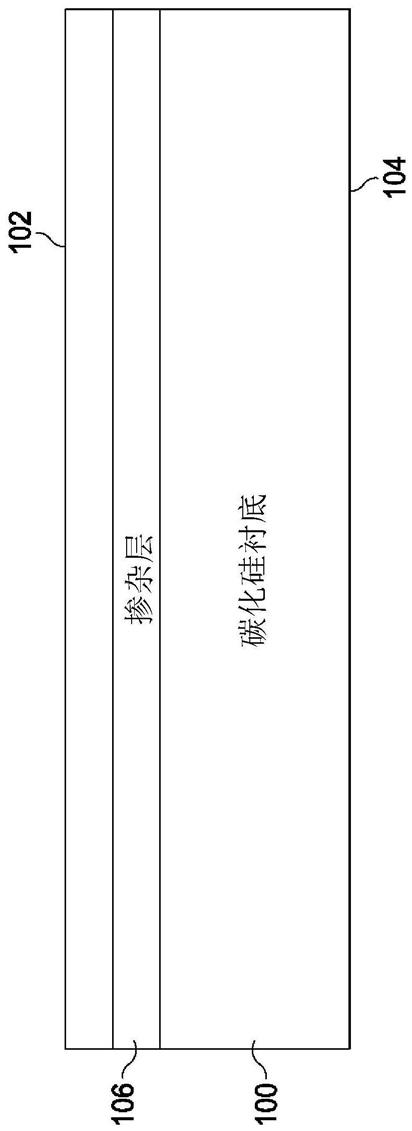

11.图1是根据说明性实施方式的碳化硅衬底的横截面图的图解;

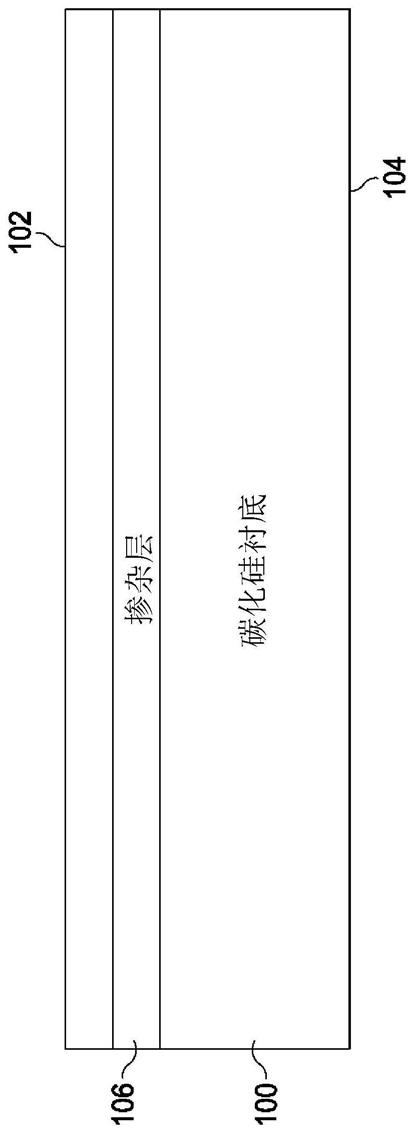

12.图2是根据说明性实施方式在碳化硅衬底上的一组第iii族氮化物层的横截面图的图解;

13.图3是根据说明性实施方式使用一组第iii族氮化物层形成的结构的横截面图的图解;

14.图4是根据说明性实施方式在碳化硅衬底的结合面上形成的碳化硅衬底覆盖结构上沉积的二氧化硅的横截面图的图解;

15.图5是根据说明性实施方式的载体衬底的横截面图的图解;

16.图6是根据说明性实施方式的与载体衬底结合的碳化硅衬底的横截面图的图解;

17.图7是显示根据说明性实施方式除去一部分碳化硅衬底的横截面图的图解;

18.图8是根据说明性实施方式的碳化硅器件层的横截面图的图解;

19.图9是根据说明性实施方式的衬底的横截面图的图解;

20.图10是根据说明性实施方式将工件与载体衬底结合的横截面图的图解;

21.图11是显示根据说明性实施方式从碳化硅衬底除去碳化硅材料的横截面图的图解;

22.图12是根据说明性实施方式蚀刻以到达碳化硅器件层的碳化硅材料的横截面图的图解;

23.图13是根据说明性实施方式的工件的横截面图的图解;

24.图14是根据说明性实施方式除去碳化硅材料的横截面图的图解;

25.图15是根据说明性实施方式的在碳化硅器件层的可及范围内(in reach of)的掺杂层的横截面图的图解;

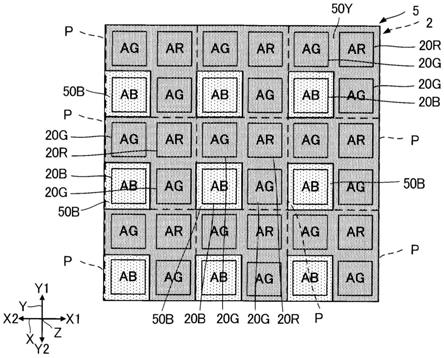

26.图16是根据说明性实例的波导耦合的光学谐振器和滤波器的图解;

27.图17是根据说明性实施方式的波导耦合的光学谐振器和滤波器的横截面图的图解;

28.图18是根据说明性实例的包含量子存储器的集成光波导的图解;

29.图19是根据说明性实施方式的包含波导耦合的量子存储器的集成光波导的横截

面图的图解;

30.图20是根据说明性实施方式的波导的横截面图;

31.图21是根据说明性实施方式的波导的另一个横截面图;

32.图22是根据说明性实施方式的波导的又另一横截面图;

33.图23是根据说明性实施方式的波导的仍另一横截面图;

34.图24是根据说明性实施方式的具有一组第iii族氮化物层的碳化硅衬底的另一个实例;

35.图25是根据说明性实施方式的用于形成半导体结构的方法的流程图的图解;

36.图26是根据说明性实施方式的用于形成半导体结构的方法的流程图的图解;

37.图27是根据说明性实施方式的用于结合部件的方法的流程图的图解;

38.图28是根据说明性实施方式的用于形成半导体结构的方法的流程图的图解;和

39.图29是根据说明性实施方式的产品管理系统的方框图的图解。

具体实施方式

40.说明性实施方式认识并考虑了一种或多种不同的考虑。例如,说明性实施方式认识并考虑到当前使用的技术可以在晶片上产生非均匀碳化硅的多晶膜。此外,说明性实施方式认识并考虑到,当使用当前技术来获得用于薄膜器件的期望厚度时,在碳化硅膜中会发生材料损坏,从而导致不期望的光学吸收或散射。

41.此外,说明性实施方式认识并考虑到,当前用于制造碳化硅(sic)纳米光子的技术主要限于外延生长在硅(si)上的3c

‑

sic(立方晶体结构)。说明性实施方式认识并考虑到,尽管由于sic和si/sio2之间的化学蚀刻选择率,3c

‑

sic易于在si或二氧化硅(sio2)上进行底切,但3c

‑

sic器件可能遭受由si

‑

sic生长界面处的位错、残留掺杂、高的膜应变和界面缺陷产生的不期望的光学损失。

42.说明性实施方式认识并考虑到,为了减轻界面缺陷,可以将3c

‑

sic转移到另一衬底上,并且可以蚀刻掉先前的界面。然而,说明性实施方式认识并考虑到由于与si衬底的晶格失配,所以3c

‑

sic包含高的不均匀应变。与在si衬底上生长的3c

‑

sic膜相反,说明性实施方式认识并考虑到,单晶块和同质外延生长的4h

‑

sic和6h

‑

sic(六方晶体结构)包含较低的晶体应变和较低的生长残余掺杂。因此,说明性实施方式认识并考虑到4h

‑

sic平台对于光子学和其他相关领域具有巨大潜力。说明性实施方式认识到并考虑到,由于在碳化硅衬底上4h

‑

sic的同质外延生长产生具有非常少的晶格缺陷的晶体材料,因此光子学还研究了碳化硅的六方sic多晶型,例如4h

‑

。说明性实施方式认识到并考虑到,考虑到该材料是在块状4h

‑

sic衬底上生长的,隔离4h

‑

sic薄膜的现有方法是有限的,使得当前使用的基础衬底的化学蚀刻是不可能的。

43.说明性实施方式认识并考虑到六角形碳化硅的薄膜适合于光子学应用,同时允许灵活的图案设计和堆叠的层。因此,说明性实施方式提供了使用碳化硅和氮化物,比如第iii族氮化物用于形成具有期望的膜厚度均匀度同时减少损伤或缺陷的结构的方法、装置和系统。在一个说明性实例中,方法形成半导体结构。将位于在碳化硅衬底上形成的一组第iii族氮化物层上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层。碳化硅衬底具有掺杂层。使用光电化学蚀

刻工艺蚀刻具有掺杂层的碳化硅衬底,其中掺杂层的掺杂水平使得掺杂层被除去并且碳化硅衬底中的碳化硅层保持未被蚀刻。可以使用碳化硅层和所述组第iii族氮化物层形成半导体结构。

44.一个或多个说明性实例使得能够使用碳化硅作为平台来制造半导体结构以提供光子功能。半导体结构包括光波导和光学谐振器中的至少一种。这些结构的功能包括成为分离器、定向耦合器、光栅耦合器、用于滤波器的微环、用于滤波器的微盘、非线性光学变频器、发光器以及其他类型的功能。说明性实例使得能够使用晶片级碳化硅薄膜来制造这些和其他类型的结构,同时保持低的光损耗。

45.如本文中所使用的,当短语“至少一个(at least one of)”与项目列表一起使用时,意味着可以使用所列出的项目中的一个或多个的不同组合,并且可能仅需要列表中的每个项目中的一个。换句话说,“至少一个(at least one of)”是指可以从列表中使用项目和项目数量的任何组合,但是并非列表中的所有项目都是必需的。该项目可以是特定的对象\事物或类别。

46.例如但不限于,“项目a、项目b或项目c中的至少一个”可以包括项目a,项目a和项目b,或项目b。该实例还可以包括项目a、项目b和项目c,或项目b和项目c。当然,这些项目的任何组合都可以存在。在一些说明性实例中,“至少一个”可以是,例如但不限于,两个项目a;一个项目b;和十个项目c;四个项目b和七个项目c;或其他合适的组合。

47.本文公开了所要求保护的结构和方法的详细实施方式。然而,应当理解,所公开的实施方式仅是可以以各种形式体现的所要求保护的结构和方法的说明。另外,结合各种实施方式给出的每个实例旨在是说明性的,而不是限制性的。

48.此外,附图不一定按比例绘制,因为一些特征可能被夸大以显示特定部件的细节。因此,本文公开的特定结构和功能细节不应被解释为限制性的,而仅仅是作为教导本领域技术人员以各种方式采用本公开内容的方法和结构的代表性基础。

49.为了下文的描述目的,术语“上(upper)”、“下(lower)”、“右(right)”、“左(left)”、“垂直(vertical)”、“水平(horizontal)”、“顶部(top)”、“底部(bottom)”及其派生词应与公开内容中的说明性实例有关,如在附图中定向的那样。术语“位于...上(positioned on)”是指第一元件比如第一结构存在于第二元件比如第二结构上,其中间插元件,比如界面结构,例如界面层,可以存在于第一元件和第二元件之间。

50.在本公开内容中,当提及元件比如层、区域或衬底在另一元件“上(on)”或“上方(over)”时,该元件可以直接在另一元件上,或者还可以存在间插元件。相反,当提及一个元件“直接在”另一元件“上”,“直接在”另一元件“上方”或“在”另一元件“上并与其直接接触”时,则不存在间插元件,并且该元件与另一元件接触。

51.下述方法、步骤和结构并未形成用于制造集成电路的完整工艺流程。可以结合本领域中当前使用的集成电路制造技术来实践本公开内容,并且为了理解本公开内容的不同实例,根据需要仅包括许多通常实践的处理步骤。附图表示制造期间集成电路的一部分的横截面,并且未按比例绘制,而是相反绘制以图解本公开内容的不同说明性特征。

52.在说明性实例中,用于制造半导体结构的方法可以利用具有不同掺杂类型的两层或更多层碳化硅。在说明性实例中,碳化硅层在晶片形式的基础碳化硅衬底上外延生长。可以通过注入(implantation)来掺杂一层或多层碳化硅层。具有基础碳化硅衬底的碳化硅层

可以统称为碳化硅衬底。此外,可以在碳化硅衬底中的最顶部的碳化硅层上方生长外延第iii族氮化物层。

53.此外,外延第iii族氮化物层的一个或多个任选层可以存在或生长在第一第iii族氮化物层上。可以使用的第iii族氮化物层的实例包括例如氮化铝(aln)、氮化镓(gan)、氮化铝镓(algan)和其他第iii族氮化物。

54.在说明性实例中,特征可以是图案化和蚀刻到第iii族氮化物层中或沉积在第iii族氮化物层上的至少一种。该结构的顶部可以覆盖有较低折射率的绝缘体,比如由二氧化硅形成的氧化物层。氧化物层是沉积在同样是晶片形式的载体衬底上的二氧化硅层。在说明性实例中,将两个晶片结合在一起。

55.在说明性实例中,可以通过研磨至少部分地除去初始的基础碳化硅衬底。在这些描绘的实例中,研磨可以是机械研磨、抛光或化学机械抛光(cmp)中的至少一种。碳化硅衬底的机械研磨可能会产生可具有不均匀厚度的碳化硅层。当在以厘米为单位测量的距离上进行研磨时,均匀性可能较低。

56.之后,可以进行光电化学(pec)蚀刻以选择性地除去暴露的不均匀的碳化硅层,直到到达蚀刻停止的碳化硅层。在该实例中,可以从碳化硅衬底的碳面或硅面进行光电化学蚀刻。碳化硅是结晶材料,并且根据方向可以具有硅面或碳面。与使用光电化学(pec)蚀刻除去的碳化硅材料相比,该碳化硅层用作蚀刻停止层,并且可以是半绝缘或不同的掺杂极性中的至少一种。

57.在说明性实例中,使用说明性实例中的技术,可以使所述组第iii族氮化物层上的所得组的碳化硅层薄于1μm,并且在一些情况下,可以薄于50nm。

58.在说明性实例中,可以使用附加的平坦化步骤。例如,可以在碳化硅层衬底的材料生长或光电化学(pec)蚀刻中的至少一种之后进行机械抛光或化学机械抛光。可以进行这些方法以减少各种界面处的粗糙度。

59.现在参考图1

‑

8,根据说明性实施方式描绘了形成半导体结构的方法中的横截面的图解。在图1中,根据说明性实施方式描绘了碳化硅衬底的横截面图的图解。如所描绘的,碳化硅(sic)衬底100可以是晶片的形式。例如,碳化硅衬底100可以是六角形碳化硅晶片。在该实例中,碳化硅材料可以是例如4h或6h晶体多型体。如所描绘的,在该实例中,碳化硅材料具有非中心对称且极性的晶体结构。如所描绘的,晶片可以例如具有25平方厘米或更高的面积。

60.在该说明性实例中,碳化硅衬底100具有结合面102和蚀刻面104。更具体地,蚀刻面104可以是碳化硅衬底100的碳面或硅面。在该实例中,结合面102为在其上形成用于半导体结构的附加材料的表面。

61.另外,碳化硅衬底100具有掺杂层106。可以使用任何当前可用的掺杂技术来进行掺杂以形成掺杂层106,所述掺杂技术包括扩散或离子注入中的至少一种。掺杂层106可以是厚度从约50纳米到几十微米的层。

62.在该说明性实例中,掺杂层106可以是p型层或n型碳化硅层。掺杂浓度使得可以使用光电化学蚀刻工艺来蚀刻掺杂层106。在该说明性实例中,掺杂使得通过光电化学蚀刻工艺来蚀刻掺杂层106,而在掺杂层106下方且与掺杂层106直接接触的碳化硅衬底100的其他部分保持未被蚀刻。

63.接下来转到图2,根据说明性实施方式描绘了在碳化硅衬底上的一组第iii族氮化物层的横截面图的图解。在说明性实例中,可以在多个附图中使用相同的附图标记。在不同附图中附图标记的这种重复使用在不同附图中表示相同的元件。

64.如所描绘的,在该实例中,在碳化硅衬底100的结合面102上生长一组第iii族氮化物层200。可以使用当前可用的用于形成氮化物层的技术生长所述组第iii族氮化物层200。

65.如本文所使用的,当“一组”在关于项目使用时表示一个或多个项目。例如,“一组第iii族氮化物层200”是第iii族氮化物层200中的一个或多个。如所描绘的,所述组第iii族氮化物层200可以是这样的薄膜层,其中这些薄膜层中的每一层的厚度从纳米的分数到几微米。例如,薄膜层可以小于一微米。

66.在该说明性实例中,所述组第iii族氮化物层200包括氮化镓(gan)、氮化铝(aln)、氮化铟(inn)、氮化铟铝镓(inalgan)或其他合适的第iii族氮化物中的至少一种。在该实例中,所述组第iii族氮化物层200包括至少10纳米厚的aln层。另外的aln、gan或al

x

ga1‑

x

n层可以任选地在该层的顶部生长。这些另外的层可以是例如纳米至几百微米厚。在该实例中,数字

‘

x’表示材料化学计量的al:ga比,并且

‘

x’可具有在0和1之间的值。

67.接下来转到图3,根据说明性实施方式描绘了使用一组第iii族氮化物层形成的结构的横截面图的图解。如所描绘的,第一金属300和第二金属302在一组第iii族氮化物层200上形成。第一金属300和第二金属302可以使用包括工业标准光刻和沉积技术的当前已知的技术形成。

68.另外,可以使用当前已知的技术比如限定硬掩模、蚀刻第iii族氮化物材料和除去硬掩模来图案化和蚀刻所述组第iii族氮化物层200。在该实例中,蚀刻中的图案化在所述组第iii族氮化物层200中形成第一开口304和第二开口306以暴露结合面102。

69.现在参考图4,根据说明性实施方式描绘了在碳化硅衬底的结合面上形成的覆盖碳化硅衬底的结构上沉积的二氧化硅的横截面图的图解。在该说明性实例中,第一氧化物层400是沉积在第一金属300、第二金属302、一组第iii族氮化物层200和暴露在所述组第iii族氮化物层200的第一开口304和第二开口306中的结合面102上的二氧化硅。可以使用已知的技术比如等离子增强化学气相沉积、溅射或用于形成第一氧化物层400的另一种合适的已知技术进行二氧化硅的沉积以形成第一氧化物层400。

70.如所描绘的,第一氧化物层400具有第一表面402。在该实例中,可以使用化学机械抛光(cmp)来加工第一表面402以改善平面度并减小表面粗糙度。此外,第一氧化物层400的第一表面402可以被处理或活化为亲水性表面。

71.现转到图5,根据说明性实施方式描绘了载体衬底的横截面图的图解。在该说明性实例中,载体衬底500可以采取许多不同的形式。例如,载体衬底500可以是碳化硅衬底、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底、氮化镓衬底和其他合适的衬底中的一种。

72.如所描绘的,载体衬底500具有带有第二表面504的第二氧化物层502。在该实例中,第二氧化物层502由二氧化硅组成。第二表面504也可以被化学机械抛光并且被处理或活化为亲水性表面。

73.在说明性实例中,图4中的碳化硅衬底100和图5中的载体衬底500可以彼此结合。在该说明性实例中,载体衬底500是用于半导体结构的衬底。另一方面,碳化硅衬底100包括

成为用于形成半导体结构的一组碳化硅器件层的碳化硅材料。

74.如所描绘的,图4中的碳化硅衬底100上的接合面102上的第一氧化物层400的第一表面402可以被放置成与图5中的第二氧化物层502的第二表面504接触。范德华力结合通过第一氧化物层400的第一表面402和第二氧化物层502的第二表面504之间的接触发生。这些通过氧化物层彼此结合的衬底可以被退火。退火可以在至少150℃的温度下进行以增强在这两个衬底的氧化物层之间形成的结合。

75.现在参考图6,根据说明性实施方式描绘了与载体衬底结合的碳化硅衬底的横截面图的图解。在该说明性实例中,碳化硅衬底100和载体衬底500彼此结合形成氧化物层600。载体衬底500是用于将要形成的半导体结构的衬底。氧化物层600是用于半导体结构的介电层。在其他说明性实例中,除氧化物层600之外或代替氧化物层600,可以使用其他类型的电介质来形成介电层。

76.现在参考图7,根据说明性实施方式描绘了显示除去了碳化硅衬底的一部分的横截面图的图解。如所描绘的,碳化硅衬底100被减薄。这种减薄可以分阶段进行。例如,可以从蚀刻面104开始研磨碳化硅衬底100,直到到达碳化硅衬底100中的掺杂层106。在此描绘的实例中,研磨是将大部分碳化硅衬底100向下除去至掺杂层106的机械研磨。在该说明性实例中,研磨可以在掺杂层106处停止或延伸到掺杂层106中。

77.现在参考图8,根据说明性实施方式描绘了碳化硅器件层的横截面图的图解。当到达掺杂层106时,可以使用光电化学(pec)蚀刻工艺来进行另外的减薄。如所描绘的,在具有蚀刻面104的碳化硅衬底100的一侧上进行光电化学(pec)蚀刻,这不使用当前可用的技术来进行。

78.该方法可以用于除去掺杂层106。选择掺杂使得在掺杂层106下方的碳化硅衬底100的其他部分不被光电化学蚀刻工艺除去。因此,碳化硅衬底100中的掺杂层106用作牺牲层。

79.将碳化硅衬底100在掺杂层106下方的部分保留为碳化硅器件层800。碳化硅器件层800是一组碳化硅层的实例。在其他说明性实例中,可以存在多个碳化硅层以用于形成半导体结构。这些另外的半导体碳化物层可以具有区分这些层的不同掺杂水平。

80.在该说明性实例中,碳化硅器件层800是薄膜层。在该说明性实例中,碳化硅器件层800具有约10纳米至几微米的厚度。在一些说明性实例中,碳化硅器件层800在约50纳米至约500纳米之间。此外,可以使用包括碳化硅器件层800、一组第iii族氮化物层200和氧化物层600的工件在载体衬底500上进行加工以制造一个或多个半导体结构。

81.与其他当前使用的技术相比,通过使用掺杂层106和光电化学蚀刻工艺,碳化硅器件层800可以具有更高的质量水平。例如,碳化硅器件层800可以是在晶片上具有期望的均匀性的多晶膜。此外,碳化硅器件层800可以具有减少的不一致性或缺陷,这导致降低不期望的光学吸收或散射。此外,在说明性实例中,除了可以产生期望的膜厚度均匀度之外,该方法还可以导致期望质量的期望外延生长。例如,使用说明性实例中的步骤,在100mm的晶片上可能发生小于50nm的厚度变化。

82.图1

‑

8中用于形成半导体结构的方法的图解是可以实施说明性实施方式的一种方式的实例。这些附图中呈现的实例并不意味着限制可以实施其他说明性实例的方式。例如,在另一个说明性实例中,可以省略所述组第iii族氮化物层200、第一金属300或第二金属

302中的至少一个。

83.接下来转到图9至图12,根据说明性实施方式描绘了在形成半导体结构的方法中的横截面图的图解。首先参考图9,根据说明性实施方式描绘了衬底的横截面图的图解。如所描绘的,碳化硅衬底900包括基础衬底902、掺杂层904和碳化硅器件层906。

84.如所描绘的,基础衬底902是块状4h

‑

sic晶片,其具有与(0001)晶体方向轴向偏离4度或其他小角度的晶片法向错切度(normal miscut)。掺杂层904是生长为被掺杂的4h

‑

sic的外延层的第一层,并且是碳化硅衬底900的牺牲部分。在该实例中,以期望的厚度和掺杂规格沉积4h

‑

sic以形成碳化硅衬底900中的碳化硅器件层906。

85.此外,一组第iii族氮化物层、氮化铝(aln)层908和氮化镓(gan)层910在碳化硅器件层906上生长。在该实例中,氮化铝层908是外延生长的未掺杂的aln缓冲层。可以使用金属有机化学气相沉积(mocvd)或分子束外延(mbe)将氮化镓层910形成为期望的规格。可以根据应用在生长阶段选择氮化镓层910的掺杂。

86.如所描绘的,第一氧化物层912沉积在氮化镓层910上。在该实例中,可以使用比如等离子增强化学气相沉积(pecvd)、溅射或原子层沉积的方法沉积二氧化硅(sio2)以形成第一氧化物层912。在该说明性实例中,各个层的生长沿箭头914的方向进行。这些不同层形成工件916。

87.现在参考图10,根据说明性实施方式描绘了用于将工件与载体衬底结合的横截面图的图解。如所描绘的,与图9中的工件916的视图相比,工件916是翻转的。然后,可以将工件916与具有第二氧化物层1002的载体衬底1000结合。在该实例中,显示了结合面1001和蚀刻面1003。如所描绘的,蚀刻面1003可以是碳化硅衬底900的硅面或碳面。

88.在该说明性实例中,载体衬底1000可以是碳化硅、硅、二氧化硅、氧化铝或其他合适的材料。如所描绘的,使用热氧化、等离子增强化学气相沉积(pevcd)、溅射、原子级沉积或其他合适的方法形成第二氧化物层1002。

89.在该说明性实例中,可以通过氧化物层之间的接触来进行结合。在该实例中,在接触之后,在约200℃的温度下退火。

90.在图11中,根据说明性实施方式描绘了从碳化硅衬底除去碳化硅材料的横截面图的图解。在该图中,第一氧化物层912和第二氧化物层1002彼此结合而形成氧化物层1100。

91.如所描绘的,碳化硅衬底900通过机械研磨减薄,并且可以如部分1102所显示的通过化学机械抛光(cmp)进行抛光。部分1102表示已经被除去的碳化硅材料。如所显示的,在该实例中,所述除去延伸到掺杂层904中。

92.在该实例中,使用机械抛光来除去一部分而不是全部掺杂层904。在某些情况下,机械研磨和抛光在比如从微米到毫米的长度规模(scale)内可能是合适的。然而,由于存在更大的长度规模,并且整个晶片都期望薄膜厚度,并且此外,这种材料除去的力和应力可能引入不希望的不一致,例如晶格缺陷、位错和晶体应变。

93.在该说明性实例中,当研磨延伸到掺杂层904中时,停止机械研磨。例如,当掺杂层904仍约几微米厚时,可以停止机械研磨。

94.转到图12,根据说明性实施方式描绘了被蚀刻以到达碳化硅器件层的碳化硅材料的横截面图的图解。如所描绘的,在该横截面图中,如部分1200所示,使用光电化学蚀刻工艺除去掺杂层904的剩余部分。该蚀刻使碳化硅器件层906暴露而不从碳化硅器件层906除

去材料。选择掺杂层904中的掺杂剂和掺杂水平,使得可以在不从碳化硅器件层906除去材料的情况下蚀刻掺杂层904。

95.利用光电化学蚀刻,可以进行掺杂剂类型选择的蚀刻,其中除去掺杂层904以暴露出碳化硅器件层906。在该说明性实例中,与使用机械研磨相比,碳化硅器件层906可以具有期望的特性,比如纯净的晶体表面以及较低的缺陷密度。

96.在该说明性实例中,可以在掺杂层904与溶液比如稀氢氧化钾或氢氟酸和水接触的同时进行光电化学蚀刻工艺。

97.此外,可以使用具有对应于在碳化硅的带隙之上的光子能量的光波长照明来进行具有不同层的载体衬底1000的照明。在该描绘的实例中,由于光源的带隙约为3.2ev,因此对4h

‑

sic来说,光源包含短于390nm的波长。可以在样品的掺杂层之一上的触点和水溶液中的铂电极之间施加电压偏置。可以通过控制直流电压偏置的大小和方向来调整和优化p型、n型和本征材料的蚀刻选择性。由于光电化学蚀刻涉及湿法化学并且根据掺杂类型是选择性的,因此碳化硅和第iii族氮化物的薄膜的最终结果在整个晶片上具有所需的均匀度和平面度。该结果与当前可用技术比如智能切割相反,智能切割使用离子注入以在限定的深度处产生非晶层。在说明性实例中,光电化学蚀刻避免了将新的点缺陷或掺杂剂引入到碳化硅和第iii族氮化物薄膜中。

98.接下来,图13

‑

15是根据说明性实施方式的使用光电化学蚀刻来蚀刻的工件的横截面图。参考图13,根据说明性实施方式描绘了工件的横截面图的图解。如所描绘的,工件1300是将碳化硅衬底与载体衬底结合的结果,其中结合在两个衬底上的氧化物层之间形成。

99.在该说明性实例中,工件1300包括硅衬底1301,其包括掺杂层1302、掺杂的碳化硅器件层1304、碳化硅器件层1306、氮化铝(aln)层1308、氮化镓(gan)层1310、氧化物层1312和载体衬底1314。在该实例中,掺杂层1302是顶层,并且不位于硅衬底1301中的其他层中,如在其他先前实例中所描绘的。工件1300具有结合面1305和蚀刻面1303。如所描绘的,蚀刻面1303可以是硅面或碳面。

100.如所描绘的,掺杂层1302是n型层。在其他说明性实例中,掺杂层1302可以是p型层。选择掺杂差异以避免掺杂的碳化硅器件层1304的蚀刻。换句话说,可以选择掺杂的碳化硅器件层1304的掺杂水平和掺杂类型,使得该层用作光电化学蚀刻工艺的蚀刻停止层。

101.在该描绘的实例中,掺杂层1302是可以使用光电化学蚀刻工艺来蚀刻的牺牲层。掺杂层1302的掺杂水平与掺杂的碳化硅器件层1304具有充分不同的掺杂类型、密度或两者,掺杂的碳化硅器件层1304具有限定蚀刻停止层的掺杂类型和水平。在该实例中,当掺杂层1302以大于1x10

18 cm

‑3的浓度掺杂并且掺杂的碳化硅器件层1304具有至少1x10

18 cm

‑3的掺杂浓度和与掺杂层1302相反的掺杂剂类型时,蚀刻选择性可以最大化。

102.在该说明性实例中,用于掺杂层1302的掺杂剂类型是n型,而用于掺杂的碳化硅器件层1304的掺杂剂的类型是p型。如果掺杂的碳化硅器件层1304需要不同类型的掺杂剂比如p型掺杂剂,则可以将在掺杂层1302中使用的掺杂剂的类型改变为n型掺杂剂。

103.在另一个说明性实例中,将牺牲层、掺杂层1302和蚀刻停止层、掺杂的碳化硅器件层1304掺杂至约1x10

17 cm

‑3的浓度或更高的浓度。在1x10

17 cm

‑3和更高的掺杂水平下,碳化硅的蚀刻速率可取决于在光电化学蚀刻过程中存在的电压偏置。蚀刻速率开始随掺杂浓度

变化更大,并且是赋予基于掺杂类型的光电化学蚀刻选择性的因素。

104.此外,掺杂的碳化硅器件层1304可以是,例如约100纳米或更厚。掺杂的碳化硅器件层1304下方的硅器件层可以是由生长形成的任何期望的厚度。例如,这些层的厚度可以是约50纳米至200微米厚,并且具有可定制的掺杂浓度。氮化物层,比如aln层和gan层各自可具有适合于特定半导体器件的厚度。

105.在该说明性实例中,可以通过欧姆接触将电压偏置施加到掺杂层1302的表面。此外,碳化硅层的表面与氢氧化钾水溶液接触并且暴露于高于带隙能量的光中。在该实例中,光可具有短于390纳米的波长。

106.转到图14,根据说明性实施方式描绘了除去碳化硅材料的横截面图的图解。在该说明性实例中,通过研磨和抛光以从掺杂层1302除去碳化硅材料来进行衬底减薄,如通过代表除去的碳化硅材料的部分1400所看到的。该抛光可以是机械抛光、化学机械抛光或两者的组合。如在该实例中可以看到的,掺杂层1302的一部分在研磨和化学机械抛光之后保留。

107.在图15中,根据说明性实施方式描绘了在碳化硅器件层可及范围内的掺杂层的横截面图的图解。在该说明性实例中,使用光电化学蚀刻工艺蚀刻掺杂层1302以到达掺杂的碳化硅器件层1304,在该实例中该掺杂的碳化硅器件层1304是蚀刻停止层。部分1500显示了除去的碳化硅材料。

108.因此,图1

‑

15中图解的方法使得能够形成用于具有期望特性的器件中的碳化硅层。例如,碳化硅器件层可以以晶片尺寸的规模形成,以使层的厚度具有期望的均匀度。另外,可以以减少的材料损坏水平来形成碳化硅器件层,使得可以避免不期望的光学吸收或散射。通过这些方法,与现有技术相比,可以在较大尺寸比如晶片上获得使用器件的碳化硅层的期望质量。

109.接下来转到图16,根据说明性实例描绘了波导耦合的光学谐振器和滤波器的图解。如所描绘的,波导耦合的光学谐振器和滤波器1600是在具有氧化物层1604、氮化铝层1606和碳化硅层1608的载体衬底1602上形成的半导体器件。可以使用图1

‑

8、图9

‑

12和图13

‑

15中图解的方法形成具有氧化物层1604、氮化铝层1606和碳化硅层1608的载体衬底1602。

110.在该说明性实例中,氮化铝层1606与碳化硅层1608直接接触。在其他实例中,一个或多个其他层可以位于氮化铝层1606和碳化硅层1608之间。

111.在该实例中,波导耦合的光学谐振器和滤波器1600具有三个部件。如所描绘的,波导耦合的光学谐振器和滤波器1600包括线性波导1601、线性波导1603和环形波导1605。在该实例中,波导耦合的光学谐振器和滤波器1600可以过滤光的选定波长。例如,行进通过线性波导1601的光可以进入环形波导1605。环形波导1605可以将选择的一个或多个波长的光传递到线性波导1603,该线性波导1603充当将光从线性波导1601传递到线性波导1603的滤波器。

112.参考图17,根据说明性实施方式描绘了波导耦合的光学谐振器和滤波器的横截面图的图解。在该图中,显示了沿图16中的线17

‑

17截取的波导耦合的光学谐振器和滤波器1600的横截面图。在该实例中,将氧化物层结合以形成氧化物层1604。此后,可以蚀刻氮化铝层1606和碳化硅层1608以形成为形成线性波导1601、线性波导1603和环形波导1605的结

构。

113.参考图18,根据说明性实例描绘了包含量子存储器的集成光波导的图解。如所描绘的,量子存储器件1800是在具有氧化物层1804、氮化铝区域1806和碳化硅区域1808的载体衬底1802上形成的半导体器件。在该实例中,可以使用图1

‑

8、图9

‑

12和图13

‑

15中图解的方法形成具有氧化物层1804、氮化铝区域1806和碳化硅区域1808的载体衬底1802。

114.如所描绘的,氮化铝区域1806具有侧面1801和侧面1803。碳化硅区域1808具有侧面1805和侧面1807。

115.在该实例中,量子存储器件1800包括量子存储器1810和集成光波导1811。量子存储器1810被耦合到集成光波导1811。量子存储器1810可以由碳化硅区域1808中的碳化硅材料中的缺陷形成。缺陷可以是例如选自碳化硅区域1808中的双空位、硅单空位、其他空位络合物、过渡金属离子或稀土离子的点缺陷。量子存储器1810可以发射光子1812,这取决于与该缺陷或色心相关的电子自旋,和光子可以与电子自旋状态纠缠的状态。从量子存储器1810发射的光子1812可以行进到集成光波导1811中。

116.参考图19,根据说明性实施方式描绘了包含量子存储器的集成光波导的横截面图的图解。在该图中,显示了沿着图18中的线19

‑

19截取的量子存储器件1800的横截面图。

117.转到图20

‑

23,根据一个或多个说明性实施方式描绘了所制造的波导结构的图解。这些描绘的波导结构可以使用图1

‑

8、图9

‑

12和图13

‑

15中图解的方法形成。这些波导也可以用来代替图16和18中描绘的光波导结构,在图17和19中图解了该光波导结构的横截面。

118.参考图20,根据说明性实施方式描绘了波导的横截面图。如所图解的,波导2000是可以在说明性实例中形成的条带波导的实例。

119.在该描绘的实例中,波导2000在载体衬底2002上形成。氧化物层2004位于载体衬底2002上。氮化铝层2006位于氧化物层2004上,并且碳化硅区域2008位于氮化铝层2006上。如该图中所显示,碳化硅区域2008已经被图案化并蚀刻以形成波导2000。

120.如本文所使用的,区域是不无限延伸的层。在该实例中,区域具有限定的侧面。如所描绘的,碳化硅区域2008具有侧面2001和侧面2003。

121.覆层2010覆盖碳化硅区域2008和氮化铝层2006。在该实例中,覆层2010与碳化硅区域2008和氮化铝层2006直接接触。覆层2010可以包括选自空气、真空、抗蚀剂、聚合物、氮化硅、二氧化硅或一些其他材料中的至少一种的材料。换句话说,在一些说明性实例中,覆层2010可以包括多于一种类型的材料。在该实例中,覆层2010具有比碳化硅区域2008的折射率更低的折射率。

122.在该说明性实例中,载体衬底2002具有约100μm的厚度。在该实例中,氧化物层2004具有约3.0μm的厚度。氮化铝层2006具有约200nm的厚度,并且碳化硅区域2008具有约300nm的厚度和约1.0μm的宽度。覆层2010具有约500nm至约5.0μm的厚度。

123.在该说明性实例中,碳化硅层可以被蚀刻以形成碳化硅区域2008,而氮化铝层2006不被蚀刻。该蚀刻可以在结合之后进行。

124.图20中描绘的波导2000的结构的横截面可用于形成半导体结构的部件。例如,碳化硅区域2008可以被复制以形成四个区域。两个外部区域可以分别是线性波导的一部分,并且两个内部区域可以用于环形波导。

125.接下来转到图21,根据说明性实施方式描绘了波导的另一横截面图。如所描绘的,

波导2100是可以在说明性实例中形成的肋形波导的实例。

126.在该说明性实例中,波导2100在载体衬底2102上形成。氧化物层2104位于载体衬底2102上。氮化铝层2106位于氧化物层2104上,并且碳化硅层2108位于氮化铝层2106上。此外,肋形区域2110是从碳化硅层2108延伸的碳化硅区域。如该图中所显示,碳化硅层2108已经被图案化并蚀刻以形成具有肋形区域2110的肋波导形式的波导2100。

127.波导2100还具有覆盖碳化硅层2108和肋形区域2110的覆层2112。在该实例中,覆层2112与这些部件直接接触。覆层2112具有低于碳化硅层2108和肋形区域2110的折射率。

128.在该说明性实例中,载体衬底2102具有约100μm的厚度。在该实例中,氧化物层2004具有约3.0μm的厚度。

129.氮化铝层2106具有约200nm的厚度。碳化硅层2108具有约100nm的厚度。从碳化硅层2008延伸的肋形区域2110具有约200nm的厚度和约1.0μm的宽度。覆层2112具有约500nm至约5.0μm的厚度。

130.在图22中,根据说明性实施方式描绘了波导的又另一横截面图。如所图解的,波导2200是埋入式脊形波导结构的实例。

131.在该描绘的实例中,波导2200在载体衬底2202上形成。氧化物层2204位于载体衬底2202上。氮化镓区域2212位于氧化物层2204中的腔2208内的氧化物层2204上。氮化铝区域2210位于氧化物层2204中的腔2208内的氮化镓区域2212上。氮化铝区域2210和氮化镓区域2212是可以掩埋在腔2208中的一组第iii族氮化物区域的实例。

132.区域是具有限定的侧面并可以位于另一种材料内的层。在该实例中,氮化镓区域2212具有在氧化物层2204中的腔2208中的侧面2201和侧面2203。氮化铝区域2210具有在氧化物层2204中的腔2208中的侧面2205和侧面2207。

133.在该实例中,碳化硅层2214位于氧化物层2204和氮化铝区域2210上。如该图中所显示,在氧化物层2204的腔2208中的碳化硅层2214、氮化铝区域2210和氮化镓区域2212形成波导2200。氮化铝区域2210和氮化镓区域2212形成掩埋在氧化物层2204中的脊2220。氮化铝区域2210或氮化镓区域2212中的至少一个的折射率高于氧化物层2204的折射率。

134.如所描绘的,波导2200具有覆盖碳化硅层2214的覆层2222。在该说明性实例中,覆层2222与碳化硅层2214直接接触。覆层2222的折射率低于碳化硅层2214的折射率。

135.在该说明性实例中,载体衬底2202具有约100μm的厚度。在该实例中,氧化物层2204具有约3.3μm的厚度。氮化铝层2210具有约100nm的厚度,和氮化镓层2212具有约200nm的厚度。腔2208中的这两个层具有约1.0μm的宽度。如所描绘的,碳化硅层2214具有约200nm的厚度。覆层2222具有约500nm至约5.0μm的厚度。

136.在该实例中,氮化铝层和氮化镓区域被蚀刻以形成氮化铝区域2210和氮化镓区域2212。形成第一氧化物层以掩埋氮化铝区域2210和氮化镓区域2212。然后将该第一氧化物层与载体衬底2202上的第二氧化物层结合。然后第一氧化物层和第二氧化物层可以结合以形成氧化物层2204。

137.在该说明性实例中,可以使用在说明性实例中描绘的操作制造图22中描绘的半导体结构。例如,可以在沉积氧化物和晶片结合之前,图案化并蚀刻第iii族氮化物层。波导结构可以与横向(水平)二极管集成,并掺杂用于碳化硅层2214中的有源电子器件和耗尽层。掺杂区域可以通过掩膜注入然后退火来制造,或者可以在生长期间衬底(sic和gan)掺杂,

然后进行图案化和蚀刻或其组合来制造。跨p

‑

n结或在金属触点之间向这些材料施加电场可用于调整光学谐振器的谐振频率或嵌入式单光子发射器的光发射频率。

138.现在参考图23,根据说明性实施方式描绘了波导的又另一横截面图。如所图解的,波导2300是埋入式光波导结构的另一个实例。

139.在该描绘的实例中,波导2300在载体衬底2302上形成。氧化物层2304位于载体衬底2302上。氮化镓区域2312位于氧化物层2304中的腔2308内的氧化物层2304上。氮化铝区域2310位于氧化物层2304中的腔2308内的氮化镓区域2312上。氮化铝区域2310具有侧面2301和侧面2303。氮化镓区域2312具有侧面2305和侧面2307。如所描绘的,氮化铝区域2310和氮化镓区域2312形成掩埋在氧化物层2304中的腔2308内的脊2317。

140.在该实例中,碳化硅层2314位于氧化物层2304和氮化铝区域2310上。此外,肋形区域2316从碳化硅层2314延伸。如该图中所显示,肋形区域2316是从碳化硅层2314延伸的碳化硅的一部分,并且可以被称为碳化硅区域。如所描绘的,氧化物层2304的腔2308内的碳化硅层2314、肋形区域2316、氮化铝区域2310和氮化镓区域2312形成波导2300。

141.如所描绘的,波导2300具有覆盖碳化硅层2314和肋形区域2316的覆层2322。如所描绘的,覆层2222与碳化硅层2214和肋形区域2316直接接触。覆层2222的折射率低于碳化硅层2214和肋形区域2316。

142.在该说明性实例中,载体衬底2302具有约100μm的厚度。在该实例中,氧化物层2304具有约3.3μm的厚度。氮化铝区域2310具有约100nm的厚度,并且氮化镓区域2312具有约200nm的厚度。腔2308中的这两个区域具有约1.0μm的宽度。如所描绘的,碳化硅层2214具有约100nm的厚度。肋形区域2316具有约1.0μm的宽度和约200nm的厚度。覆层2322具有约500nm至约5.0μm的厚度。

143.提供图20

‑

23中的波导结构的图解作为可根据一个或多个说明性实例制造的一种类型的半导体结构的实例。这些图解并不意味着限制可以实施其他说明性实例的方式。

144.例如,图解的这些层和区域的厚度是可用于薄膜实施的厚度的实例。这些厚度并不意味着限制可以在其他说明性实例中使用的厚度。

145.此外,第iii族氮化物层和区域的数量和类型可以与图20

‑

23中图解的那些不同。例如,除了描绘的氮化铝(aln)和氮化镓(gan)层以外或代替描绘的氮化铝(aln)和氮化镓(gan)层,可以使用氮化铟(inn)层和氮化铟铝镓(inalgan)层。

146.作为另一个实例,除了波导结构以外或代替波导结构,可以制造其他类型的半导体结构。例如,半导体结构可以包括超导单光子检测器、光发射器、使用碳化硅器件层内的点缺陷的量子存储器或半导体结构中的其他合适类型的部件中的至少一个。

147.可以使用一个或多个说明性实例中的操作来制造的具有一个或多个碳化硅器件层和一个或多个第iii族氮化物层的半导体结构的其他实例包括微机电系统和光子部件,其包括波导耦合的四端口和两端口环形谐振器或滤波器。在仍其他说明性实例中,可以以允许超导纳米线单光子检测器和逻辑部件在低温下与光子部件、电气部件和机械部件一起操作的方式沉积超导材料。

148.作为另一个实例,对于缝隙波导,可以通过蚀刻在一起紧密间隔的两个脊来选择较低折射率的覆层或衬底外部的真空的光学模式。间隔可以例如小于几百纳米。作为另一个实例,可以通过光刻图案化并且然后化学刻蚀掉选择性区域中的氧化物(sio2),由与这

些图中所描绘的材料类似的材料堆叠来制造悬浮式波导,这将产生将更多地扩展到空气或真空中而不是氧化层中的光学空间模式。

149.接下来参考图24,根据说明性实施方式描绘了具有一组第iii族氮化物层的碳化硅衬底的另一个实例。在该说明性实例中,工件2400是可以形成并与载体衬底比如图5中的载体衬底500结合的层的实例。

150.在该实例中,工件2400中的碳化硅衬底2402包括基础衬底2404、p型碳化硅层2406、n型碳化硅层2408、未掺杂的碳化硅层2410和p型碳化硅层2412。如所描绘的,p型碳化硅层2406是用于进行光电化学蚀刻的牺牲层。其他碳化硅层是可用于形成半导体结构的碳化硅器件层的实例。在该实例中,n型碳化硅层2408除了作为器件层之外还可以用作蚀刻停止层。

151.在该说明性实例中,基础衬底2404具有约350μm的厚度。如所描绘的,牺牲层,p型碳化硅层2406具有约5μm的厚度。在该实例中,n型碳化硅层2408具有约0.1μm的厚度;未掺杂的碳化硅层2410具有约0.2μm的厚度;和p型碳化硅层2412具有约0.1μm的厚度。

152.如所描绘的,第iii族氮化物层在碳化硅衬底2402中的p型碳化硅层2412上生长。这些第iii族氮化物层包括未掺杂的氮化铝层2414和未掺杂的氮化镓层2416。在该说明性实例中,未掺杂的氮化铝层2414具有约0.1μm的厚度,和未掺杂的氮化镓层2416具有约0.4μm的厚度。

153.在该描绘的实例中,氧化物层2418沉积在未掺杂的氮化镓层2416上。在该实例中,氧化物层2418具有约0.2μm的厚度。

154.使用工件2400,可以将碳化硅和第iii族氮化物的薄膜堆叠在具有较低折射率(n)的材料比如sio2的顶部上,比如分别地sio2的n约为1.4,单晶aln/gan的n为2.1/2.3和4h

‑

sic的n为2.6。结果,光子器件中的光学模式可以停留在碳化硅或第iii族氮化物层中的至少一层内,而不会向下方的块状衬底材料中辐射或损失光能。

155.此外,工件2400中描绘的第iii族氮化物层中的碳化硅层可用于在碳化硅材料内产生p

‑

i

‑

n结。在该实例中,与sic的暴露表面或碳化硅与氧化物之间的直接界面相比,未掺杂的氮化铝层2414的使用可以是有益的,并且可以导致更少的未钝化界面状态(特别是在低温下)。在说明性实例中,一个或多个另外的第iii族氮化物层的使用是任选的。

156.提供工件2400的图解作为其中可以实施具有一组第iii族氮化物层的碳化硅衬底的一种方式的实例。该说明并不意味着限制可以实施其他说明性实例的方式。

157.例如,其他说明性实例可以具有其他数量的层以及碳化硅衬底。在一些说明性实例中,与牺牲层相邻的层可以是未掺杂层,而不是具有与牺牲层相反掺杂类型的层。在又另一个说明性实例中,可以采用三个、五个或一些其他数量的第iii族氮化物层。此外,提供这些层的示例厚度作为可以与薄膜层一起使用的厚度的实例。在其他实例中可以使用其他厚度。

158.接下来转到图25,根据说明性实施方式描绘了用于形成半导体结构的方法的流程图的图解。该方法开始于将位于在碳化硅衬底上形成的一组第iii族氮化物层上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底与所述组第iii族氮化物层之间的氧化物层(操作2500)。碳化硅衬底具有掺杂层。

159.该方法使用光电化学蚀刻工艺蚀刻具有掺杂层的碳化硅衬底(操作2502)。掺杂层

的掺杂水平使得掺杂层被除去并且碳化硅衬底中的碳化硅器件层保持未被蚀刻。在操作2502中,掺杂层是使得能够在具有期望的碳化硅器件层的厚度均匀性或期望的光学性能水平中的至少一种的衬底比如晶片上形成碳化硅器件层的牺牲层。在操作2502中,在蚀刻面上进行光电化学蚀刻,该蚀刻面可以是碳化硅材料的硅面,或者例如是碳化硅材料的碳面。还可在作为碳化硅材料的硅面的蚀刻面上进行光电化学蚀刻。

160.该方法使用碳化硅器件层和所述组第iii族氮化物层形成半导体结构(操作2504)。此后该方法终止。在该实例中,碳化硅器件层和所述组第iii族氮化物层可以是薄膜层。半导体结构选自使用碳化硅器件层内的点缺陷的光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导、光学谐振器、光子发射量子存储器或一些其他合适的结构中的至少一种。半导体结构可以包括多个部件。例如,半导体结构可以包括相同类型或不同类型的多个波导。作为另一个实例,半导体结构可以包括一个或多个波导和量子存储器。可以选择这些和其他部件以提供半导体结构的期望的一种或多种功能。

161.接下来参考图26,根据说明性实施方式描绘了用于形成半导体结构的方法的流程图的图解。该方法开始于在碳化硅衬底上形成一组第iii族氮化物层(操作2600)。碳化硅衬底包括掺杂层。掺杂层具有这样的掺杂水平,使得掺杂层使用光电化学蚀刻工艺被蚀刻,而碳化硅衬底的其他部分保持未被蚀刻。在其他说明性实例中,所述组第iii族氮化物层的形成可以包括蚀刻所述组第iii族氮化物层以形成结构。

162.该方法在所述组第iii族氮化物层上形成第一氧化物层,其中所述组第iii族氮化物层位于第一氧化物层和碳化硅衬底之间(操作2602)。该方法将第一氧化物层与载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层(操作2604)。

163.该方法研磨碳化硅衬底(操作2606)。当暴露碳化硅衬底中的一部分掺杂层时该方法停止研磨(操作2608)。在操作2608中,掺杂的暴露层的一部分可以是掺杂层的顶部或掺杂层的某一部分。

164.该方法使用光电化学蚀刻来蚀刻碳化硅衬底,使得当暴露碳化硅衬底中的该部分掺杂层时掺杂层被除去并且碳化硅衬底中的碳化硅器件层被保留(操作2610)。

165.该方法使用碳化硅器件层和所述组第iii族氮化物层形成半导体结构(操作2612)。此后该方法终止。

166.接下来转到图27,根据说明性实施方式描绘了结合部件的图解。图27中的流程图是用于进行图25中的操作2500和图26中的操作2604的一种实施方式的实例。

167.该方法开始于使第一氧化物层的第一表面与第二氧化物层的第二表面接触(操作2700)。在操作2700中,在第一氧化物层和第二氧化物层之间发生分子间相互作用。这些分子间相互作用包括,例如,范德华力、氢键或强共价键中的至少一种。

168.该方法对第一氧化物层和第二氧化物层退火,同时使第一表面与第二表面直接接触以形成位于载体衬底和一组第iii族氮化物层之间的氧化物层(操作2702)。在该实例中,操作2702中的退火是任选的。此后该方法终止。

169.转到图28,根据说明性实施方式描绘了用于形成半导体结构的方法的流程图的图解。该方法开始于将位于碳化硅衬底上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底和碳化硅衬底之间的氧化物层(操作2800)。

170.在操作2800中,碳化硅衬底具有掺杂层。此外,在一个说明性实例中,第一氧化物层与碳化硅衬底直接接触。在另一个说明性实例中,一组间插层,比如一组第iii族氮化物层,位于第一硅层和碳化硅衬底之间。

171.该方法使用光电化学蚀刻工艺蚀刻具有掺杂层的碳化硅衬底(操作2802)。在操作2802中,掺杂层的掺杂水平是这样的,使得掺杂层被除去和碳化硅衬底中的碳化硅器件层保持未被蚀刻。

172.该方法使用碳化硅器件层形成半导体结构(操作2804)。在操作2804中,其他材料也可用于形成半导体结构。例如,所述组第iii族层或区域可以在该操作中形成。而且,还可以在操作2804中形成覆层、金属层或金属区域中的至少一个以形成半导体结构。

173.所描绘的不同实施方式中的流程图和方框图图解了说明性实施方式中的装置和方法的一些可能的实施的架构、功能和操作。在这方面,流程图或方框图中的每个方框可以表示模块、区段、功能或操作或步骤的一部分中的至少一个。例如,一个或多个方框可以被实施为程序代码、硬件或程序代码和硬件的组合中的指令,以控制用于制造半导体结构的制造设备。当以硬件实现时,硬件可以例如采用集成电路的形式,该集成电路被制造或配置为执行流程图或方框图中的一个或多个操作。当实施为程序代码和硬件的组合时,实施可以采用固件的形式。可以使用执行不同操作的专用硬件系统或专用硬件和由专用硬件运行的程序代码的组合来实现流程图或方框图中的每个框,以操作制造设备来制造半导体结构。

174.在说明性实施方式的一些可选的实施中,方框中标注的一种或多种功能可以不按图中标注的顺序发生。例如,在某些情况下,取决于所涉及的功能,可以基本上同时进行连续显示的两个框,或者有时可以以相反的顺序来进行这些框。而且,除了流程图或方框图中的图解的方框之外,还可以添加其他方框。

175.例如,在操作2604中进行的结合被显示为在操作2610中蚀刻碳化硅衬底之前进行。在其他说明性实例中,操作2604中的结合可以在操作2610中发生蚀刻之后进行。作为另一个实例,代替附图中显示和描述的二氧化硅或者除了附图中显示和描述的二氧化硅之外,可以使用具有期望的特性比如期望的介电常数的其他电介质。

176.现转到图29,根据说明性实施方式描绘了产品管理系统的方框图的图解。产品管理系统2900是物理硬件系统。在该说明性实例中,产品管理系统2900包括制造系统2902或维护系统2904中的至少一个。

177.制造系统2902配置为制造产品。如所描绘的,制造系统2902包括制造设备2906。制造设备2906包括加工设备2908或组装设备2910中的至少一个。

178.加工设备2908是用于制造用于形成产品的零件的部件的设备。加工设备2908可用于制造金属零件、复合零件、半导体、电路、紧固件、肋、蒙皮板、翼梁、天线或其他合适类型的零件中的至少一种。

179.例如,加工设备2908可以包括机器和工具。这些机器和工具可以是钻、液压机、熔炉、模具、复合带铺设机、真空系统、车床或其他合适类型的设备中的至少一种。

180.关于制造半导体部件,加工设备2908可以包括可用于制造半导体结构的外延反应器、氧化系统、扩散系统、蚀刻机、清洁机、接合机、切割机、晶片锯、离子注入机、物理气相沉积系统、化学气相沉积系统、光刻系统、电子束光刻系统、等离子刻蚀机、管芯附着机、焊线

机、管芯覆盖系统、成型设备、气密性封口机、电测试仪、老化炉、保温烤箱、uv擦除机或其他合适类型的设备中的至少一个。

181.组装设备2910是用于组装零件以形成产品比如芯片、集成电路、计算机、航空器或某种其他产品的设备。组装设备2910还可以包括机器和工具。这些机器和工具可以是机械臂、履带、紧固件安装系统、基于轨道的钻孔系统或机器人中的至少一种。

182.在该说明性实例中,维护系统2904包括维护设备2912。维护设备2912可以包括对产品进行维护所需的任何设备。维护设备2912可以包括用于对产品的零件进行不同操作的工具。这些操作可以包括拆卸零件、翻新零件、检查零件、返工零件、制造替换零件中的至少一项或者用于对产品进行维护的其他操作中的至少一种。这些操作可以用于例行维护、检查、升级、翻新或其他类型的维护操作。

183.在说明性实例中,维护设备2912可以包括超声检查装置、x射线成像系统、视觉系统、钻头、履带和其他合适的装置。在某些情况下,维护设备2912可以包括加工设备2908、组装设备2910或两者,以生产和组装维护所需的零件。

184.产品管理系统2900还包括控制系统2914。控制系统2914是硬件系统,并且还可以包括软件或其他类型的部件。控制系统2914被配置为控制制造系统2902或维护系统2904中的至少一个的操作。具体而言,控制系统2914可以控制加工设备2908、组装设备2910或维护设备2912中的至少一个的操作。

185.可以使用可以包括计算机、电路、网络和其他类型的设备的硬件来实现控制系统2914中的硬件。该控制可以采取直接控制制造设备2906的形式。例如,机器人、计算机控制的机器和其他设备可以由控制系统2914控制。在其他说明性实例中,控制系统2914可以产品制造或进行维护中管理人工操作员2916进行的操作。例如,控制系统2914可以分配任务、提供指令、显示模型或进行其他操作来管理人工操作员2916进行的操作。在这些说明性实例中,描述和图解的使用碳化硅和第iii族氮化物层来制造半导体结构的不同步骤可以使用控制系统2914实施。

186.在不同的说明性实例中,人操作员2916可以操作制造设备2906、维护设备2912或控制系统2914中的至少一个与其进行交互。可以发生这种交互来制造半导体结构和产品的其他部件,比如用于产品比如航空器、航天器、通信系统、微机电系统、光子器件或超导单光子检测器的半导体器件或部件。

187.因此,说明性实例提供了用于制造半导体结构的方法、装置和系统。在一个说明性实例中,方法形成半导体结构。将位于在碳化硅衬底上形成的一组第iii族氮化物层上的第一氧化物层与位于载体衬底上的第二氧化物层结合以形成位于载体衬底和所述组第iii族氮化物层之间的氧化物层。碳化硅衬底具有掺杂层。使用光电化学蚀刻工艺蚀刻具有掺杂层的碳化硅衬底,其中掺杂层的掺杂水平是这样的,使得掺杂层被除去并且碳化硅衬底中的碳化硅层保持未被蚀刻。使用碳化硅层和所述组第iii族氮化物层形成半导体结构。

188.此外,说明性实例中的方法适合于处理大面积晶片,例如面积为10cm2或更大的晶片。说明性实例与用于这些类型的晶片的当前使用的方法兼容,以在低折射率绝缘体上产生低损耗、高厚度均匀性的碳化硅和基于iii族氮化物的晶体结构。这使得能够用碳化硅和第iii族氮化物产生有源和无源集成的光子产品和电子产品。

189.例如,说明性实例可以包括以下的组合:晶片接合,并且然后研磨/抛光或化学机

械抛光以使碳化硅衬底减薄,随后是从碳化硅衬底的碳面进行光电化学蚀刻。通过利用其材料选择性蚀刻特性,在所列实例中使用的光电化学蚀刻将碳化硅层平坦化为干净的晶体界面,产生均匀的碳化硅膜厚度。

190.为了促进光电化学蚀刻,可以将电极附连到位于要蚀刻的表面或要蚀刻的掺杂层下方的碳化硅层的另一掺杂层上,并且可以将第二电极置于蚀刻液中。与目前使用的技术相比,以这种方式进行光电化学蚀刻提供了在绝缘膜上生产碳化硅的不同方法。此外,说明性实例中的方法可用于以保留掺杂的层(例如,p

‑

i

‑

n结)和暴露的碳化硅表面下方的结构的方式来生产碳化硅和第iii族氮化物的亚微米厚的膜。

191.在说明性实例中,最终的重构(restructure)可以采取许多不同的形式。例如但不限于,半导体结构可以选自使用碳化硅器件层内的点缺陷的光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导、光学谐振器或光子发射量子存储器中的至少一种。换句话说,半导体结构可以包括这些器件中的一个或多个,并且可以包括相同类型的多个器件。

192.已经出于图解和描述的目的呈现了不同的说明性实施方式的描述,并且其不意图是穷举的或限于所公开形式的实施方式。不同的说明性实例描述了执行动作或操作的部件。在说明性实施方式中,部件可以被配置为进行所描述的动作或操作。例如,部件的结构可以具有这样的配置或设计,该结构为部件提供执行在说明性实例中描述的认为由部件执行的动作或操作的能力。此外,就本文使用术语“包括”、“包含”、“具有”、“含有”及其变体而言,这些术语旨在以类似于作为开放式过渡词的术语“包括”的方式包括,但不排除任何另外的或其他元件。

193.此外,本公开内容包括根据下述条款的实施方式:

194.条款1.一种用于形成半导体结构的方法,所述方法包括:

195.(2600)在碳化硅衬底(100、1003)上形成一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312),其中碳化硅衬底(100、1003)包括掺杂层(106、904、1302),并且其中掺杂层(106、904、1302)具有的掺杂水平使得掺杂层(106、904、1302)使用光电化学蚀刻工艺被蚀刻,而碳化硅衬底(100、1003)的其他部分保持未被蚀刻;

196.(2602)在所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上形成第一氧化物层(402、912),其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)位于第一氧化物层(402、912)和碳化硅衬底(100、1003)之间;

197.(2604)将第一氧化物层(402、912)与载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304);

198.(2606)研磨所述碳化硅衬底(100、1003);

199.(2608)当到达碳化硅衬底(100、1003)中的一部分掺杂层(106、904、1302)时停止研磨;

200.(2610)使用光电化学蚀刻工艺蚀刻碳化硅衬底(100、1003),使得当暴露碳化硅衬底(100、1003)中的该部分掺杂层(106、904、1302)时掺杂层(106、904、1302)被除去,并使碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保留;和

201.(2612)使用碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)形成半导体结构。

202.条款2.条款1所述的方法,其中将第一氧化物层(402、912)与所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻碳化硅衬底(100、1003)之后进行。

203.条款3.前述条款中任一项所述的方法,其中将第一氧化物层(402、912)与所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)中的第iii族氮化物层之后进行。

204.条款4.前述条款中任一项所述的方法,其中将第一氧化物层(402、912)与所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻碳化硅衬底(100、1003)之前进行。

205.条款5.前述条款中任一项所述的方法,其中将第一氧化物层(402、912)与所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)包括:

206.(2700)使第一氧化物层(402、912)的第一表面与第一氧化物层(504、1002)的第二表面接触,其中在第一氧化物层(402、912)和第一氧化物层(504、1002)之间发生分子间相互作用;和

207.对第一氧化物层(402、912)和第一氧化物层(504、1002)进行退火(2702),同时使第一表面与第二表面直接接触以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)。

208.条款6.前述条款中任一项所述的方法,其中使用光电化学蚀刻工艺蚀刻碳化硅衬底(100、1003),使得当暴露碳化硅衬底(100、1003)中的一部分掺杂层(106、904、1302)时掺

杂层(106、904、1302)被除去并使碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保留,包括:

209.使用光电化学蚀刻工艺蚀刻碳化硅衬底(100、1003)的硅面和碳面中的一个,使得当暴露碳化硅衬底(100、1003)中的一部分掺杂层(106、904、1302)时掺杂层(106、904、1302)被除去并使碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保留。

210.条款7.前述条款中任一项所述的方法,其中掺杂层(106、904、1302)为使得能够在晶片上形成碳化硅器件层(100、906)的牺牲层,所述碳化硅器件层(100、906)具有期望的厚度均匀性或期望的光学性能水平中的至少一种。

211.条款8.条款1所述的方法,其中半导体结构选自使用碳化硅器件层(100、906)内的点缺陷的光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导、光学谐振器或光子发射量子存储器中的至少一种。

212.条款9.前述条款中任一项所述的方法,其中碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是薄膜层。

213.条款10.条款1所述的方法,其中载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)是碳化硅衬底(100、1003)、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底和氮化镓衬底中的一种。

214.条款11.前述条款中任一项所述的方法,其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)包括氮化镓(gan)、氮化铝(aln)、氮化铟(inn)和氮化铟铝镓(inalgan)中的至少一种。

215.条款12.一种用于形成半导体结构的方法,所述方法包括:

216.(2800)将位于在碳化硅衬底(100、1003)上形成的一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304),其中碳化硅衬底(100、1003)具有掺杂层(106、904、1302);

217.(2082)使用光电化学蚀刻工艺蚀刻具有掺杂层(106、904、1302)的碳化硅衬底(100、1003),其中掺杂层(106、904、1302)的掺杂水平使得掺杂层(106、904、1302)被除去并且碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保持未被蚀刻;和

218.(2804)使用碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)形成所述半导体结构。

219.条款13.条款12所述的方法,进一步包括:

220.(2606)在蚀刻碳化硅衬底(100、1003)之前研磨所述碳化硅衬底(100、1003);和

221.(2608)在蚀刻碳化硅衬底(100、1003)之前,当到达所述碳化硅衬底(100、1003)中的一部分掺杂层(106、904、1302)时停止所述碳化硅衬底(100、1003)的研磨。

222.条款14.条款12

‑

13中任一项所述的方法,进一步包括:

223.(2600)在碳化硅衬底(100、1003)上形成所述组第iii族氮化物层(200、908、910、

1308、1310、1606、1806、2006、2106、2210、2212、2310、2312);和

224.(2602)在所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上形成第一氧化物层(402、912),其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)位于第一氧化物层(402、912)和碳化硅衬底(100、1003)之间。

225.条款15.条款12

‑

14中任一项所述的方法,其中将位于在碳化硅衬底(100、1003)上形成的所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻碳化硅衬底(100、1003)之后进行。

226.条款16.条款12

‑

15中任一项所述的方法,其中将第一氧化物层(402、912)与所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)中的第iii族氮化物层之后进行。

227.条款17.条款12

‑

16中任一项所述的方法,其中将位于在碳化硅衬底(100、1003)上形成的所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)在蚀刻碳化硅衬底(100、1003)之前进行。

228.条款18.条款12

‑

17中任一项所述的方法,其中将位于在碳化硅衬底(100、1003)上形成的所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)包括:

229.(2700)使第一氧化物层(402、912)的第一表面与所述第一氧化物层(504、1002)的第二表面接触,其中在所述第一氧化物层(402、912)和所述第一氧化物层(504、1002)之间发生分子间相互作用;和

230.(2702)对所述第一氧化物层(402、912)和所述第一氧化物层(504、1002)进行退

火,同时使所述第一表面与所述第二表面直接接触以形成位于所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)。

231.条款19.条款12

‑

18中任一项所述的方法,其中掺杂层(106、904、1302)为使得能够在晶片上形成碳化硅器件层(100、906)的牺牲层,所述碳化硅器件层(100、906)具有期望的厚度均匀性或期望的光学性能水平中的至少一种。

232.条款20.条款12

‑

19中任一项所述的方法,其中半导体结构选自使用碳化硅器件层(100、906)内的点缺陷的光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导、光学谐振器或光子发射量子存储器中的至少一种。

233.条款21.条款12

‑

20中任一项所述的方法,其中所述碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是薄膜层。

234.条款22.条款12

‑

21中任一项所述的方法,其中所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)是碳化硅衬底(100、1003)、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底和氮化镓衬底中的一种。

235.条款23.条款12

‑

22中任一项所述的方法,其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)包括氮化镓(gan)、氮化铝(aln)、氮化铟(inn)和氮化铟铝镓(inalgan)中的至少一种。

236.条款24.一种用于形成半导体结构的方法,所述方法包括:

237.(2800)将位于碳化硅衬底(100、1003)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和碳化硅衬底(100、1003)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304),其中碳化硅衬底(100、1003)具有掺杂层(106、904、1302);

238.(2802)使用光电化学蚀刻工艺蚀刻具有所述掺杂层(106、904、1302)的碳化硅衬底(100、1003),其中所述掺杂层(106、904、1302)的掺杂水平使得掺杂层(106、904、1302)被除去并且碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保持未被蚀刻;和

239.(2804)使用所述碳化硅器件层(100、906)形成半导体结构。

240.条款25.条款24所述的方法,其中使用光电化学蚀刻工艺蚀刻具有掺杂层(106、904、1302)的碳化硅衬底(100、1003)包括:

241.使用光电化学蚀刻工艺蚀刻具有掺杂层(106、904、1302)的碳化硅衬底(100、1003)的碳面,其中掺杂层(106、904、1302)的掺杂水平使得掺杂层(106、904、1302)被除去并使碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保持未被蚀刻。

242.条款26.条款24

‑

25中任一项所述的方法,其中第一氧化物层(402、912)与碳化硅衬底(100、1003)直接接触。

243.条款27.条款24

‑

26中任一项所述的方法,其中一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)位于所述第一氧化物层(402、912)和所述碳化硅衬底(100、1003)之间。

244.条款28.一种产品管理系统(2900),其包括:

245.制造设备(2914);和

246.控制系统,其中所述控制系统控制制造设备(2914)以:

247.将位于在碳化硅衬底(100、1003)上形成的一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上的第一氧化物层(402、912)与位于载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)上的第一氧化物层(504、1002)结合以形成位于所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)之间的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304),其中碳化硅衬底(100、1003)具有掺杂层(106、904、1302);

248.使用光电化学蚀刻工艺蚀刻具有掺杂层(106、904、1302)的碳化硅衬底(100、1003),其中掺杂层(106、904、1302)的掺杂水平使得掺杂层(106、904、1302)被除去并且碳化硅衬底(100、1003)中的碳化硅器件层(100、906)保持未被蚀刻;和

249.使用碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)形成半导体结构。

250.条款29.条款28所述的产品管理系统(2900),其中所述控制系统控制制造设备(2914)以进一步包括:

251.在蚀刻所述碳化硅衬底(100、1003)之前,研磨碳化硅衬底(100、1003);和

252.在蚀刻所述碳化硅衬底(100、1003)之前,当到达所述碳化硅衬底(100、1003)中的一部分掺杂层(106、904、1302)时停止所述碳化硅衬底(100、1003)的研磨。

253.条款30.条款28

‑

29中任一项所述的产品管理系统(2900),其中所述控制系统控制制造设备(2914)以:

254.在所述碳化硅衬底(100、1003)上形成所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312);和

255.在所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)上形成第一氧化物层(402、912),其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)位于第一氧化物层(402、912)和碳化硅衬底(100、1003)之间。

256.条款31.条款28

‑

30中任一项所述的产品管理系统(2900),其中半导体结构选自使用碳化硅器件层(100、906)内的点缺陷的光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导、光学谐振器或光子发射量子存储器中的至少一种。

257.条款32.条款28

‑

31中任一项所述的产品管理系统(2900),其中碳化硅器件层(100、906)和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是薄膜层。

258.条款33.条款28

‑

32中任一项所述的产品管理系统(2900),其中所述载体衬底(500、1000、1314、1602、1802、2002、2102、2202、2302、2402)是碳化硅衬底(100、1003)、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底和氮化镓衬底中的一种。

259.条款34.条款28

‑

33中任一项所述的产品管理系统(2900),其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)包括氮化

镓(gan)、氮化铝(aln)、氮化铟(inn)和氮化铟铝镓(inalgan)中的至少一种。

260.条款41.一种半导体结构,其包括:

261.衬底(500、1000、1314、1602、1802);

262.在所述衬底(500、1000、1314、1602、1802)上的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304);

263.在所述氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)上的一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312);和

264.在所述组第iii族氮化物层(200)上的一组碳化硅层(100、906、1306、2008、2108、2214、2314)。

265.条款42.条款41所述的半导体结构,其中在所述氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)上的所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是一组第iii族氮化物区域(2210、2212)。

266.条款43.条款42所述的半导体结构,其中所述组第iii族氮化物区域(2210、2212)被掩埋在氧化物层(600)中的腔(2208)内。

267.条款44.条款43所述的半导体结构,进一步包括:

268.在所述组碳化硅层(2214)上的覆层(2222),其中所述覆层(2222)的折射率低于所述组碳化硅层(2224)的折射率。

269.条款45.条款41

‑

44中任一项所述的半导体结构,其中所述组碳化硅层(100、906、1306)是一组碳化硅区域(2008、2110、2316)。

270.条款46.条款45所述的半导体结构,其中在所述氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)上的所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是一组第iii族氮化物区域。

271.条款47.条款46所述的半导体结构,进一步包括:

272.在所述组碳化硅层(1808)中的碳化硅材料中的缺陷。

273.条款48.条款47所述的半导体结构,其中所述缺陷是双空位、硅单空位、其他空位络合物、过渡金属离子和稀土离子中的一种。

274.条款49.条款45所述的半导体结构,其中所述组碳化硅区域(2008、2110、2316)形成波导。

275.条款50.条款49所述的半导体结构,进一步包括:

276.在所述组碳化硅区域(2008、2110、2316)上的覆层(2010、2112、2322),其中覆层(2010、2112、2322)的折射率低于所述组碳化硅区域(2008、2110、2316)的折射率。

277.条款51.条款50所述的半导体结构,其中覆层(2010、2112、2322)包括选自空气、真空、抗蚀剂、聚合物、二氧化硅或氮化硅中的至少一种的材料。

278.条款52.条款51所述的半导体结构,其中所述组碳化硅层(100、906、1306)包括碳化硅层(2108、2314)和从碳化硅层(2108)延伸的碳化硅区域(2110、2316)。

279.条款53.条款52所述的半导体结构,进一步包括:

280.在碳化硅层(2108)和碳化硅区域(2110、2316)上的覆层(2112、2322),其中覆层(2112、2322)的折射率低于碳化硅层(2108)和碳化硅区域(2008、2316)的折射率。

281.条款54.条款51所述的半导体结构,其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)与氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)直接接触。

282.条款55.条款51所述的半导体结构,其中所述组碳化硅层与所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)直接接触。

283.条款56.条款51所述的半导体结构,其中衬底(500、1000、1314、1602、1802)是碳化硅衬底、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底和氮化镓衬底中的一种。

284.条款57.条款51所述的半导体结构,其中所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)包括氮化镓(gan)、氮化铝(aln)、氮化铟(inn)和氮化铟铝镓(inalgan)中的至少一种。

285.条款58.条款51所述的半导体结构,其中所述组碳化硅层和所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)是薄膜层。

286.条款59.条款51所述的半导体结构,其中半导体结构选自光波导、缝隙波导、脊形波导、肋形波导、埋入式光波导、悬浮式波导或光学谐振器中的至少一种。

287.条款60.一种半导体结构,包括:

288.衬底(500、1000、1314、1602、1802);

289.在衬底(500、1000、1314、1602、1802)上的氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304);和

290.在衬底(500、1000、1314、1602、1802)上的一组碳化硅层(100、906、1306、2008、2108、2214、2314)。

291.条款61.条款60所述的半导体结构,其中在衬底(500、1000、1314、1602、1802)上的所述组碳化硅层(100、906、1306、2008、2108、2214、2314)与氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)直接接触。

292.条款62.条款60

‑

61中任一项所述的半导体结构,进一步包括:

293.在氧化物层(600)上的一组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312),使得所述组第iii族氮化物层(200、908、910、1308、1310、1606、1806、2006、2106、2210、2212、2310、2312)位于氧化物层(600、1100、1312、1604、1804、2004、2104、2204、2304)和所述组碳化硅层(100、906、1306、2008、2108、2214、2314)之间。

294.条款63.条款60

‑

62中任一项所述的半导体结构,其中所述组碳化硅层(100、906、1306、2008、2108、2214、2314)是一组碳化硅区域(2008、2110、2316)。

295.条款64.条款60

‑

63中任一项所述的半导体结构,其中所述组碳化硅层(100、906、1306、2008、2108、2214、2314)包括碳化硅层(2108、2314)和从碳化硅层延伸的碳化硅区域(2110、2316)。

296.条款65.条款64所述的半导体结构,进一步包括:

297.在碳化硅层(2108)和碳化硅区域(2110、2316)上的覆层(2112、2322),其中覆层(2112、2322)的折射率低于碳化硅层(2108、2314)和碳化硅区域(2110、2316)的折射率。

298.条款66.条款65所述的半导体结构,其中覆层(2112、2322)包括选自空气、真空、抗

蚀剂、聚合物、二氧化硅或氮化硅中的至少一种的材料。

299.条款67.条款60

‑

66中任一项所述的半导体结构,其中所述组碳化硅层(100、906、1306、2008、2108、2214、2314)是一组薄膜层。

300.条款68.权利要求60所述的半导体结构,其中衬底(500、1000、1314、1602、1802)是碳化硅衬底、硅衬底、氧化铝衬底、氧化镓衬底、二氧化硅衬底、氮化铝衬底和氮化镓衬底中的一种。

301.对于本领域普通技术人员而言,许多修改和变型将是显而易见的。此外,与其他期望的实施方式相比,不同的说明性实施方式可以提供不同的特征。选择并描述所选择的一个或多个实施方式,以便最好地解释实施方式的原理、实际应用,并使本领域的其他普通技术人员能够理解各个实施方式的公开内容,其中各种修改适合于考虑的具体用途。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。