技术特征:

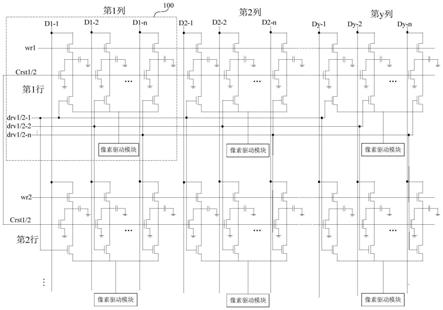

1.一种时钟生成电路,包括:信号延迟电路,其被配置为接收与图像数据一起接收到的数据时钟的一个周期相对应的窗口信号,并且通过延迟所述窗口信号来生成多个延迟信号和多个反相延迟信号;脉冲生成电路,其被配置为通过分别组合所述多个延迟信号和所述多个反相延迟信号来生成多个子信号,每个子信号具有一个脉冲;以及信号组合电路,其被配置为使用所述多个子信号来生成用于驱动像素的驱动时钟。2.根据权利要求1所述的时钟生成电路,其中,所述信号组合电路通过组合所述多个子信号中的一部分子信号来生成多个时钟,输出所述多个时钟中的一个时钟作为所述驱动时钟,并且输出所述多个时钟中的另一时钟作为用以对所述窗口信号进行计数的计数器时钟。3.根据权利要求1所述的时钟生成电路,其中,所述信号组合电路生成所述驱动时钟,使得所述驱动时钟在所述数据时钟的一个周期中或者在所述窗口信号的高电平处具有预定数量的脉冲。4.根据权利要求1所述的时钟生成电路,还包括校准初始化电路,所述校准初始化电路被配置为生成用于初始化所述信号组合电路的驱动时钟屏蔽信号,其中,所述信号组合电路根据所述驱动时钟屏蔽信号停止生成所述驱动时钟以用于初始化。5.根据权利要求4所述的时钟生成电路,其中,在初始化的情况下,所述信号组合电路生成单电平信号,而非所述驱动时钟。6.根据权利要求1所述的时钟生成电路,还包括校准选择电路,所述校准选择电路被配置为接收用于开始生成所述驱动时钟的校准开始信号,并且根据所述校准开始信号将所述窗口信号或所述数据时钟传输到所述信号延迟电路。7.根据权利要求6所述的时钟生成电路,其中,所述信号延迟电路在接收所述数据时钟时延迟所述数据时钟而非所述窗口信号,以生成所述多个延迟信号和所述多个反相延迟信号。8.根据权利要求1所述的时钟生成电路,其中,所述信号延迟电路包括彼此串联连接的多个延迟单元,其中,为了生成一个延迟信号,所述多个延迟单元中的一个延迟单元将从另一延迟单元接收到的另一延迟信号延迟一个单位。9.根据权利要求8所述的时钟生成电路,其中,所述一个延迟单元通过将所述一个延迟信号反转来生成一个反相延迟信号,所述另一延迟单元通过将所述另一延迟信号反转来生成另一反相延迟信号,并且所述脉冲生成电路使用所述脉冲生成电路内部的脉冲生成单元通过将所述一个反相延迟信号和所述另一延迟信号组合来生成一个子信号。10.根据权利要求9所述的时钟生成电路,其中,所述脉冲生成单元对所述一个延迟信号和所述另一反相延迟信号进行与运算以生成所述一个子信号。11.根据权利要求9所述的时钟生成电路,其中,所述脉冲生成电路包括多个脉冲生成单元,以及其中,所述信号组合电路包括第一信号组合电路和第二信号组合电路,所述第一信号组合电路被配置为通过组合由奇数编号的脉冲生成单元所生成的子信号来生成第一时钟,所述第二信号组合电路被配置为通过组合由偶数编号的脉冲生成单元所生成的子信号来生成第二时钟。

12.根据权利要求11所述的时钟生成电路,其中,所述信号组合电路输出所述第一时钟作为所述驱动时钟并且输出所述第二时钟作为用以对所述窗口信号进行计数的计数器时钟。13.根据权利要求1所述的时钟生成电路,其中,所述驱动时钟具有与所述数据时钟的频率的n倍相对应的频率,其中,n是1或更大的自然数。14.一种时钟生成电路,用于生成具有目标频率的第二时钟,所述目标频率对应于第一时钟的频率的p倍,其中,p是1或更大的自然数,所述时钟生成电路包括:信号延迟电路,其被配置为接收具有与所述第一时钟的一个周期相对应的脉冲的窗口信号,并且通过延迟所述窗口信号来生成多个延迟信号和多个反相延迟信号;脉冲生成电路,其被配置为通过分别组合所述多个延迟信号和所述多个反相延迟信号来生成多个子信号,每个子信号具有一个脉冲;以及信号组合电路,其被配置为使用所述多个子信号来生成一个时钟并且输出所述一个时钟作为所述第二时钟,其中,所述信号延迟电路重复地调节用于所述窗口信号的延迟时间,直到所述一个时钟的频率达到所述目标频率为止。15.根据权利要求14所述的时钟生成电路,其中,所述第一时钟是用于图像数据的通信时钟,并且所述第二时钟是用于控制用于使用所述图像数据显示图像的驱动信号的供给的驱动时钟。16.根据权利要求14所述的时钟生成电路,其中,所述信号延迟电路包括被配置为生成所述多个延迟信号的多个延迟单元,其中,在所述一个时钟的频率达到所述目标频率时,所述多个延迟单元中的一部分延迟单元被禁用,并且所述第二时钟是基于由所述多个延迟单元中的被启用的延迟单元所生成的延迟信号而生成的。17.根据权利要求14所述的时钟生成电路,其中,所述脉冲生成电路包括被配置为生成所述多个子信号的多个脉冲生成单元,其中,在所述一个时钟的频率达到所述目标频率时,所述多个脉冲生成单元中的一部分脉冲生成单元被禁用,并且所述第二时钟是通过所述多个脉冲生成单元中的被启用的脉冲生成单元所生成的子信号的组合而生成的。18.根据权利要求17所述的时钟生成电路,其中,在所述一个时钟的频率达到所述目标频率时,所述多个脉冲生成单元中的一部分奇数编号的脉冲生成单元被禁用,并且所述第二时钟是通过所述奇数编号的脉冲生成单元中的被启用的脉冲生成单元所生成的子信号的组合而生成的。19.根据权利要求14所述的时钟生成电路,其中,所述信号延迟电路包括被配置为将所述窗口信号延迟单位时间以生成所述多个延迟信号的多个延迟单元,其中,在每个延迟单元中包括被配置为确定所述单位时间的多个延迟子单元,其中,通过启用或禁用所述多个延迟子单元来确定所述单位时间。20.根据权利要求19所述的时钟生成电路,其中,所述信号延迟电路仅启用所述多个延迟子单元中的首先接收到所述窗口信号的延迟子单元,以将所述窗口信号延迟最小值。

技术总结

本发明提供一种用于驱动像素的时钟生成电路。根据实施例,在用于驱动显示设备中的像素的驱动时钟的频率达到目标频率时,延迟电路中的一部分延迟电路被禁用,从而降低用于生成驱动时钟的功耗。驱动时钟的功耗。驱动时钟的功耗。

技术研发人员:崔镇镐 金长洙 金泰根

受保护的技术使用者:硅工厂股份有限公司

技术研发日:2021.05.10

技术公布日:2021/11/14

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。