1.本公开涉及一种用于生成用以驱动显示设备的像素中所包括的发光二极管的时钟的技术。

背景技术:

2.现有技术的说明

3.发光二极管(led)面板可以在每个像素中包括一个或多个发光二极管(led)。

4.用于驱动led面板的数据驱动设备可以通过调节提供给每个像素中的发光二极管的功率量来表示图像数据即灰度值。用于调节提供给发光二极管的功率量的方法可以包括用于调节提供给发光二极管的电压的大小的方法、用于调节提供给发光二极管的电流的大小的方法、以及用于调节提供给发光二极管的电流的时间的方法。

5.用于调节提供给发光二极管的电流的时间的方法可以被称为“脉宽调制(pwm)方法”。在pwm方法中,数据驱动设备对驱动时钟进行计数,并且数据驱动设备可以向每个像素中的发光二极管提供电流,直到计数值达到每个像素的特定灰度值为止。另外,当计数值达到特定灰度值时,数据驱动设备可以重置计数值,并且可以重新计数驱动时钟以用于下一灰度值。

6.数据驱动设备可以从控制器接收数据时钟,并且可以接收与数据时钟相对应的图像数据。另外,数据驱动设备可以使用数据时钟生成驱动时钟。

7.然而,为了使用数据时钟生成驱动时钟,传统的数据驱动设备包括相位检测器(pd)和多级延迟链,其中,通过由相位检测器生成的上行信号或下行信号来调节延迟时间。然而,这种结构可能具有增加功耗的问题。在多级延迟链中包括用于将输入信号延迟预定单位的多个延迟单元(或延迟元)。这是由于如下的事实:在多级延迟链结构中所有延迟单元必须总是根据上行/下行信号来驱动,使得不需要操作的延迟单元也被驱动。

8.在这方面,本实施例提供了一种时钟生成技术,该时钟生成技术能够生成用以控制电压或电流以驱动发光二极管的驱动时钟,并且通过抑制不必要的延迟单元的驱动来减少用于生成驱动时钟的功耗。

技术实现要素:

9.相对于该背景,在一个方面,本公开提供了一种用于从用于接收图像数据的数据时钟生成用于控制向像素提供驱动信号的驱动时钟的技术。

10.在另一方面,本公开提供了一种用于通过延迟窗口信号来生成延迟信号、从延迟信号生成具有至少一个脉冲的子信号、并且通过组合子信号来生成驱动时钟的技术。

11.在另一方面,本公开提供了一种用于生成驱动时钟的技术,该驱动时钟具有与数据时钟的频率的p倍(其中,“p”是1或更大的自然数)相对应的频率。

12.在另一方面,本公开提供了一种如下技术,该技术用于调节延迟程度直到驱动时钟具有目标频率为止,并且如果驱动时钟的频率达到目标频率,则该技术禁用一些延迟电

路。

13.鉴于上述,在一方面,本公开提供一种时钟生成电路,包括:信号延迟电路,其被配置为接收与图像数据一起接收到的数据时钟的一个周期相对应的窗口信号,并且通过延迟所述窗口信号来生成多个延迟信号和多个反相延迟信号;脉冲生成电路,其被配置为通过分别组合所述多个延迟信号和所述多个反相延迟信号来生成多个子信号,每个子信号具有一个脉冲;以及信号组合电路,其被配置为使用所述多个子信号来生成用于驱动像素的驱动时钟。

14.在所述时钟生成电路中,所述信号组合电路可以通过组合所述多个子信号中的一部分子信号来生成多个时钟,可以输出所述多个时钟中的一个时钟作为所述驱动时钟,并且可以输出所述多个时钟中的另一时钟作为用以对所述窗口信号进行计数的计数器时钟。

15.在所述时钟生成电路中,所述信号组合电路可以生成所述驱动时钟,使得所述驱动时钟在所述数据时钟的一个周期中或者在所述窗口信号的高电平处具有预定数量的脉冲。

16.所述时钟生成电路还可以包括校准初始化电路,所述校准初始化电路被配置为生成用于初始化所述信号组合电路的驱动时钟屏蔽信号,并且所述信号组合电路可以根据所述驱动时钟屏蔽信号停止生成所述驱动时钟以用于初始化。

17.在所述时钟生成电路中,在初始化的情况下,所述信号组合电路可以生成单电平信号,而非所述驱动时钟。

18.所述时钟生成电路还可以包括校准选择电路,所述校准选择电路被配置为接收用于开始生成所述驱动时钟的校准开始信号,并且根据所述校准开始信号将所述窗口信号或所述数据时钟传输到所述信号延迟电路。

19.在所述时钟生成电路中,所述信号延迟电路可以在接收所述数据时钟时延迟所述数据时钟而非所述窗口信号,以生成所述多个延迟信号和所述多个反相延迟信号。

20.在所述时钟生成电路中,所述信号延迟电路可以包括彼此串联连接的多个延迟单元,并且为了生成一个延迟信号,所述多个延迟单元中的一个延迟单元将从另一延迟单元接收到的另一延迟信号延迟一个单位。

21.在所述时钟生成电路中,所述一个延迟单元可以通过将所述一个延迟信号反转来生成一个反相延迟信号,所述另一延迟单元可以通过将所述另一延迟信号反转来生成另一反相延迟信号,并且所述脉冲生成电路可以使用所述脉冲生成电路内部的脉冲生成单元通过将所述一个反相延迟信号和所述另一延迟信号组合来生成一个子信号。

22.在所述时钟生成电路中,所述脉冲生成单元可以对所述一个延迟信号和所述另一反相延迟信号进行与运算以生成所述一个子信号。

23.在所述时钟生成电路中,所述脉冲生成电路可以包括多个脉冲生成单元,以及所述信号组合电路可以包括第一信号组合电路和第二信号组合电路,所述第一信号组合电路被配置为通过组合由奇数编号的脉冲生成单元所生成的子信号来生成第一时钟,所述第二信号组合电路被配置为通过组合由偶数编号的脉冲生成单元所生成的子信号来生成第二时钟。

24.在所述时钟生成电路中,所述信号组合电路可以输出所述第一时钟作为所述驱动时钟并且可以输出所述第二时钟作为用以对所述窗口信号进行计数的计数器时钟。

25.在所述时钟生成电路中,所述驱动时钟可以具有与所述数据时钟的频率的n倍相对应的频率,其中,n是1或更大的自然数。

26.另一实施例提供一种时钟生成电路,用于生成具有目标频率的第二时钟,所述目标频率对应于第一时钟的频率的p倍,其中,p是1或更大的自然数,所述时钟生成电路可以包括:信号延迟电路,其被配置为接收具有与所述第一时钟的一个周期相对应的脉冲的窗口信号,并且通过延迟所述窗口信号来生成多个延迟信号和多个反相延迟信号;脉冲生成电路,其被配置为通过分别组合所述多个延迟信号和所述多个反相延迟信号来生成多个子信号,每个子信号具有一个脉冲;以及信号组合电路,其被配置为使用所述多个子信号来生成一个时钟并且输出所述一个时钟作为所述第二时钟,其中,所述信号延迟电路重复地调节用于所述窗口信号的延迟时间,直到所述一个时钟的频率达到所述目标频率为止。

27.在所述时钟生成电路中,所述第一时钟可以是用于图像数据的通信时钟,并且所述第二时钟可以是用于控制用于使用所述图像数据显示图像的驱动信号的供给的驱动时钟。

28.在所述时钟生成电路,所述信号延迟电路可以包括被配置为生成所述多个延迟信号的多个延迟单元。这里,在所述一个时钟的频率达到所述目标频率时,所述多个延迟单元中的一部分延迟单元可以被禁用,并且所述第二时钟可以是基于由所述多个延迟单元中的被启用的延迟单元所生成的延迟信号而生成的。

29.在所述时钟生成电路中,所述脉冲生成电路可以包括被配置为生成所述多个子信号的多个脉冲生成单元。这里,在所述一个时钟的频率达到所述目标频率时,所述多个脉冲生成单元中的一部分脉冲生成单元可以被禁用,并且所述第二时钟可以是通过所述多个脉冲生成单元中的被启用的脉冲生成单元所生成的子信号的组合而生成的。

30.在所述时钟生成电路,在所述一个时钟的频率达到所述目标频率时,所述多个脉冲生成单元中的一部分奇数编号的脉冲生成单元可以被禁用,并且所述第二时钟可以是通过所述奇数编号的脉冲生成单元中的被启用的脉冲生成单元所生成的子信号的组合而生成的。

31.在所述时钟生成电路中,所述信号延迟电路可以包括被配置为将所述窗口信号延迟单位时间以生成所述多个延迟信号的多个延迟单元,并且在每个延迟单元中可以包括被配置为确定所述单位时间的多个延迟子单元。可以通过启用或禁用所述多个延迟子单元来确定所述单位时间。

32.在所述时钟生成电路中,所述信号延迟电路可以仅启用所述多个延迟子单元中的首先接收到所述窗口信号的延迟子单元,以将所述窗口信号延迟最小值。

33.如上所述,根据本实施例,当驱动时钟的频率达到目标频率时,一些延迟电路被禁用,从而降低了用于生成驱动时钟的功耗。

34.另外,根据本实施例,时钟生成设备可以仅包括数字电路,并且这允许方便其设计。

附图说明

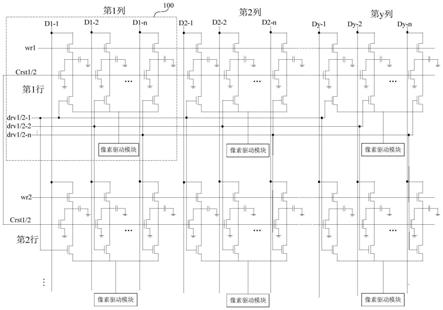

35.图1是例示根据实施例的显示设备的配置的示图;

36.图2是例示根据实施例的数据驱动设备的配置的示图;

37.图3是例示根据实施例的时钟生成电路的配置的示图;

38.图4是例示根据实施例的包括数据时钟、第一时钟、第二时钟和驱动时钟的时钟信号以及窗口信号的波形的示图;

39.图5是例示根据实施例的包括信号延迟电路的详细配置的时钟生成电路的配置的示图;

40.图6是例示根据实施例的包括信号延迟电路和脉冲生成电路的详细配置的时钟生成电路的配置的示图;

41.图7是例示根据实施例的包括第一信号组合电路和第二信号组合电路的详细配置的时钟生成电路的配置的示图;

42.图8是例示根据实施例的包括第三信号组合电路的详细配置的时钟生成电路的配置的示图;

43.图9是例示根据实施例的窗口信号、延迟信号和子信号的波形的示图;

44.图10是例示根据实施例的窗口信号、子信号、第一时钟、第二时钟和驱动时钟的波形的示图;

45.图11是例示根据实施例的包括校准选择电路和延迟禁用电路的详细配置的时钟生成电路的配置的示图;

46.图12是例示根据实施例的延迟单元的配置的示图;

47.图13是例示根据另一实施例的延迟单元的前端的详细配置的示图;

48.图14是例示根据另一实施例的延迟单元的后端的详细配置的示图;以及

49.图15是例示根据另一实施例的延迟子单元的示图。

具体实施方式

50.图1是例示根据实施例的显示设备的配置的示图。

51.参照图1,显示设备100可以包括控制器110、数据驱动设备120、栅极驱动设备130和面板140等。

52.一个或多个发光二极管(led)led可以布置在面板140上的每个像素中。发光二极管led可以以矩阵的形式布置。

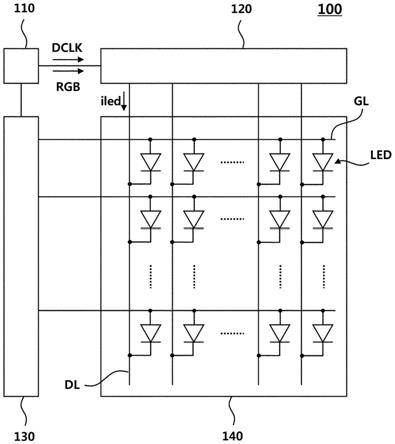

53.数据线dl可以布置在面板140上,以便在一个方向上(例如,在图1中的垂直方向上)延伸,并且栅极线gl可以布置在面板140上,以便在另一方向上(例如,在图1中的水平方向上)延伸。此外,发光二极管led的一个电极(例如,阴极)可以连接到数据线dl,并且发光二极管led的另一电极(例如,阳极)可以连接到栅极线gl。

54.栅极驱动设备130可以从多个栅极线gl中选择一个栅极线gl,并且可以向该一个栅极线提供特定电压(例如,高驱动电压vdd或低驱动电压vss)。

55.此外,数据驱动设备120可以用作用于将驱动电流iled供应至发光二极管led以使电流流经连接至栅极线gl的发光二极管led的源,或者可以用作来自发光二极管led的驱动电流iled的吸收器。

56.控制器110可以将图像数据rgb和数据时钟dclk传输到数据驱动设备120。此外,数据驱动设备120可以接收与数据时钟dclk相对应的图像数据rgb,并且可以根据图像数据rgb来控制要提供给每个像素的驱动电流iled。

57.图2是例示根据实施例的数据驱动设备的配置的示图。

58.参照图2,数据驱动设备120可以包括数据接收电路210、时钟生成电路220和像素驱动电路230等。

59.数据接收电路210可以接收与从控制器接收到的数据时钟dclk相对应的图像数据rgb。然后,数据接收电路210可以从图像数据rgb中提取与每个像素的灰度值相对应的像素数据dp并且可以将该像素数据传输到像素驱动电路230。

60.像素驱动电路230可识别包括在像素数据dp中的每个像素的灰度值,并且可根据灰度值来调节要提供给每个像素的驱动功率的量。例如,像素驱动电路230可以随着灰度值的增加而增加驱动功率的量,并且可以随着灰度值的减小而减小驱动功率的量。

61.在假设提供给布置在每个像素中的发光二极管的驱动电压恒定的情况下,可以根据提供给每个像素的驱动电流iled的大小来确定提供给每个像素的驱动功率的量。另外,像素驱动电路230可以通过调节提供给每个像素的驱动电流iled的大小来控制每个像素的灰度值。

62.像素驱动电路230可以通过在预定时间内调节用于提供驱动电流iled的时间来控制提供给每个像素的驱动电流iled的大小。这种方法可以被称为“脉宽调制(pwm)方法”。在pwm方法中,有时将提供驱动电流iled的时间与预定时间之比称为“占空比”,并且像素驱动电路230可以通过调节占空比来控制每个像素的灰度值。例如,如果灰度值高,则像素驱动电路230可增加占空比,并且如果灰度值低,则像素驱动电路230可降低占空比。

63.像素驱动电路230可以使用时钟来实现pwm方法。像素驱动电路230可以通过对时钟进行计数来调节驱动电流iled的供应时间,从而控制驱动电流iled的大小。当灰度值高时,时钟的计数值增加,并且因此占空比和驱动电流iled可以增加。当灰度值低时,时钟的计数值减小,并且因此占空比和驱动电流iled可以减小。这里,像素驱动电路230可以使用时钟的脉冲进行计数,并且可以基于脉冲的上升沿或下降沿进行计数。另外,时钟的计数值(计数的数量)可以等于灰度值或者与灰度值成比例。

64.例如,像素驱动电路230可以计数时钟,可以将计数值与灰度值(或与灰度值成比例的值)进行比较,并且可以将驱动电流iled供应至像素,直到计数值变为等于灰度值(或与灰度值成比例的值)为止。在8位图像数据和0到255的灰度值的情况下,计数值可以在0和255之间。为了对8位图像数据进行计数,时钟可以包括至少255个脉冲。当计数值变为等于特定值时,像素驱动电路230可以重置计数,并且可以重新开始计数以便驱动另一像素。此时,像素驱动电路230需要时钟,该时钟可以被称为“驱动时钟gclk”。

65.时钟生成电路220可以使用数据时钟dclk生成驱动时钟gclk。传输/接收图像数据的周期和驱动布置在面板上的像素的周期必须基本相同,或者必须具有恒定倍数的关系。为此,时钟生成电路220可以使用与传输/接收图像数据的周期相关的数据时钟dclk来生成与驱动像素的周期相关的驱动时钟gclk。

66.图3是例示根据实施例的时钟生成电路的配置的示图。

67.参照图3,时钟生成电路220可以包括第一信号组合电路310、第二信号组合电路320、第三信号组合电路330、校准选择电路340、校准初始化电路350、延迟禁用电路360、信号延迟电路370和脉冲生成电路380。

68.时钟生成电路220可从数据时钟dclk生成驱动时钟gclk。数据时钟dclk可以与图

像数据同步,并且可以由时钟生成电路220接收。像素驱动电路可以读出与数据时钟dclk相对应的图像数据。数据时钟dclk可以是用于图像数据的通信时钟。驱动时钟gclk可以用于控制用以显示图像数据的驱动信号(例如,驱动电压或驱动电流)的供应。这里,为了生成驱动时钟gclk,时钟生成电路220可以使用数据时钟dclk本身,但是本公开不限于此,并且时钟生成电路220可以使用窗口信号win。窗口信号win可以是具有与数据时钟dclk的一个周期相对应的脉冲的信号,并且可以是作为用于生成驱动时钟gclk的源的信号。

69.信号延迟电路370可从校准选择电路340接收延迟输入信号dly_in。延迟输入信号dly_in是从校准选择电路340传输到信号延迟电路370的信号,并且根据校准选择电路340的选择可以包括数据时钟dclk或窗口信号win。信号延迟电路370可接收延迟输入信号dly_in,即数据时钟dclk和窗口信号win中的任何一个,并且可执行延迟。

70.因此,信号延迟电路370可以从校准选择电路340接收数据时钟dclk本身或具有与数据时钟dclk的一个周期相对应的脉冲的窗口信号win。信号延迟电路370可以通过重复地延迟数据时钟dclk或窗口信号win来生成多个延迟信号dly_xx。信号延迟电路370可以通过将相应的延迟信号反转来生成多个反相延迟信号dly_xxb。信号延迟电路370可将多个延迟信号dly_xx或多个反相延迟信号dly_xxb输出至脉冲生成电路380或第三信号组合电路330。

71.此外,信号延迟电路370可从外部接收延迟启用信号dly_en。信号延迟电路370可从延迟禁用电路360接收延迟禁用信号dly_dis。信号延迟电路370可根据延迟启用信号dly_en来启用或开启信号延迟电路中所包含的多个延迟单元中的一些延迟单元,并且可根据延迟禁用信号dly_dis来禁用或关闭多个延迟单元中的一些延迟单元。

72.此外,信号延迟电路370可根据延迟控制信号dly_ctr来调节延迟输入信号dly_in的延迟程度。信号延迟电路370可以经由其中串联连接的多个延迟单元来延迟该延迟输入信号dly_in。信号延迟电路370启用的延迟单元越多,延迟输入信号dly_in通过的延迟单元越多,从而增加延迟。信号延迟电路370启用的延迟单元越少,延迟输入信号dly_in通过的延迟单元越少,从而减少延迟。如上所述,延迟输入信号dly_in在每次通过延迟单元时被延迟了预定程度,并且延迟输入信号dly_in被每个延迟单元延迟的程度(即,延迟单位)可以通过延迟控制信号dly_ctr来调节。

73.脉冲生成电路380可接收来自信号延迟电路370的多个延迟信号dly_xx以及多个反相延迟信号dly_xxb。脉冲生成电路380可以通过组合多个延迟信号dly_xx和多个反相延迟信号dly_xxb来生成具有一个或多个脉冲的多个子信号sub_ck。此外,脉冲生成电路380可以将子信号sub_ck传输至第一信号组合电路310及第二信号组合电路320。

74.此外,脉冲生成电路380可以经由校准开始信号calb_on来启用或禁用包括在脉冲生成电路中的多个脉冲生成单元。此外,脉冲生成电路380可以经由选择信号sel来启用或禁用多个脉冲生成单元。在一些情况下,校准开始信号calb_on或选择信号sel中的一个可以禁用所有脉冲生成单元,或者校准开始信号calb_on可以禁用一些脉冲生成单元,并且选择信号sel可以禁用其余的脉冲生成单元。在后一种情况下,校准开始信号calb_on可以控制偶数编号的脉冲生成单元的启用,并且选择信号sel可以控制奇数编号的脉冲生成单元的启用。因此,校准开始信号calb_on或选择信号sel可以禁用(屏蔽)一些脉冲生成单元,从而降低脉冲生成电路380的功耗。

75.另一方面,信号延迟电路370可重复调节延迟输入信号dly_in的延迟,直到驱动时钟gclk的频率达到目标频率为止。为了使用驱动时钟gclk作为用于驱动像素的驱动信号(例如,pwm信号),需要对包括大量脉冲的驱动信号进行计数。因此,驱动时钟gclk可以具有与数据时钟dclk的频率的p倍相对应的目标频率(其中“p”是1或更高的自然数)。也就是说,驱动时钟gclk可以倍增。为此,驱动时钟gclk必须具有足够的脉冲来计数驱动信号,并且频率必须据此增加。信号延迟电路370可调节延迟输入信号dly_in的延迟,直到驱动时钟gclk具有足够的脉冲或目标频率为止。直到此时,信号延迟电路370可重复对延迟输入信号dly_in的延迟的调节。

76.此外,当驱动时钟gclk的频率达到目标频率时,信号延迟电路370的一些延迟单元可以被禁用。这是由于被禁用的延迟单元不再需要操作以生成驱动时钟gclk这一事实。信号延迟电路370的延迟单元的启用和禁用可以由延迟启用信号dly_en和延迟禁用信号dly_dis来确定。

77.此外,当驱动时钟gclk的频率达到目标频率时,可以禁用脉冲生成电路380的一些脉冲生成单元。这是由于被禁用的脉冲生成单元不再需要操作以生成驱动时钟gclk这一事实。脉冲生成电路380的脉冲生成单元的启用和禁用可以由选择信号sel和校准开始信号calb_on来确定。

78.信号组合电路310至330可以将多个延迟信号dly_xx和多个反相延迟信号dly_xxb组合,以生成驱动时钟gclk,使得驱动时钟gclk具有预定数量的脉冲。具体地,信号组合电路310至330可以从信号延迟电路370接收多个延迟信号dly_xx和多个反相延迟信号dly_xxb,或者可以从脉冲生成电路380接收多个子信号sub_ck。信号组合电路310至330中的第一信号组合电路310可接收和组合多个子信号sub_ck以生成第一时钟clk_1。第二信号组合电路320可接收和组合多个子信号sub_ck以生成第二时钟clk_2。第三信号组合电路330可接收和组合多个延迟信号dly_xx和多个反相延迟信号dly_xxb以生成第三时钟clk_3。

79.在此,第一信号组合电路310可以将由奇数编号的脉冲生成单元所生成的多个子信号sub_ck组合以生成第一时钟clk_1,并且第二信号组合电路320可以将由偶数编号的脉冲生成单元所生成的多个子信号sub_ck组合以生成第二时钟clk_2。第三信号组合电路330可以生成第三时钟clk_3,该第三时钟的频率是数据时钟dclk的频率的两倍。

80.信号组合电路310至330可以生成多个时钟,多个时钟中的一个可以用作驱动时钟gclk,并且多个时钟中的另一时钟可以用作用于对窗口信号win进行计数的计数器时钟。在该图中,第一时钟clk_1可以用作驱动时钟gclk,并且第二时钟clk_2可以用作计数器时钟。

81.校准选择电路340可接收校准开始信号calb_on,并且可开始生成驱动时钟gclk。这是由于如下事实:只有当校准选择电路340将数据时钟dclk和窗口信号win中的一个传输到信号延迟电路370时,才能生成驱动时钟gclk。校准选择电路340可根据校准开始信号calb_on将数据时钟dclk和窗口信号win中的任何一个传输到信号延迟电路370。如果校准开始信号calb_on是1,则可以输出窗口信号win,并且如果校准开始信号calb_on是0,则可以输出数据时钟dclk。

82.校准初始化电路350可以经由驱动时钟屏蔽信号gclk_mask来初始化信号组合电路310到330。信号组合电路310至330可以通过在接收到驱动时钟屏蔽信号gclk_mask时停止生成驱动时钟gclk来初始化。信号组合电路310至330可以生成单电平信号(例如,具有低

电平或高电平的持续预定时间的信号),而不是生成时钟clk_1至clk_3,并且可以输出该单电平信号。校准初始化电路350可以仅初始化信号组合电路310至330中的一些信号组合电路,并且在该图中,第一信号组合电路310可以由校准初始化电路350初始化。

83.延迟禁用电路360可以将延迟禁用信号dly_dis传输到信号延迟电路370。延迟启用信号dly_en可以启用或开启包括在信号延迟电路370中的多个延迟单元中的一些延迟单元。延迟禁用信号dly_dis可禁用或关闭多个延迟单元中的一些延迟单元。

84.延迟禁用电路360可以经由频率倍增信号mul_x来确定启用或禁用信号延迟电路370的延迟单元的数量。频率倍增信号mul_x可以指示最终将被生成的驱动时钟gclk与数据时钟dclk相比必须被倍增多少倍。这里,倍增可以理解为将驱动时钟gclk的频率增加得高于数据时钟dclk的频率。如果频率倍增信号mul_x具有高频率,则驱动时钟gclk必须具有许多脉冲,且信号必须被延迟很多,因此许多延迟单元可以被启用。另一方面,如果频率倍增信号mul_x具有低频率,则驱动时钟gclk必须具有很少的脉冲并且信号必须被延迟很少,因此可以启用更少的延迟单元。

85.另一方面,时钟生成电路220可以生成具有目标频率的驱动时钟gclk,该目标频率对应于数据时钟dclk频率的p倍(其中“p”是1或更高的自然数)。时钟生成电路220可连续生成被选为驱动时钟gclk的第一时钟clk_1,直到第一时钟clk_1具有目标频率为止。在该时间期间,时钟生成电路220可以接收延迟控制信号dly_ctr,并且可以控制信号延迟电路370的延迟。如果第一时钟clk_1未达到目标频率,则信号延迟电路370可根据延迟控制信号dly_ctr来调节延迟单位。时钟生成电路220可重复此操作,直到第一时钟clk_1达到目标频率并且然后可以用作驱动时钟gclk。

86.此外,当第一时钟clk_1达到目标频率时,也就是说,如果第一时钟clk_1具有足以对pwm信号进行计数的多个脉冲,则信号延迟电路370可禁用用于延迟该延迟输入信号dly_in的多个内部延迟单元中的一些内部延迟单元。当多个延迟单元中的一些延迟单元被禁用时,信号延迟电路370的功耗可以相应地被降低。此外,当第一时钟clk_1达到目标频率时,即,如果第一时钟clk_1具有足以对pwm信号进行计数的多个脉冲,则脉冲生成电路380可禁用通过组合延迟信号和反相延迟信号来生成子信号的多个内部脉冲生成单元中的一些内部脉冲生成单元。当多个脉冲生成单元中的一些脉冲生成单元被禁用时,脉冲生成电路380的功耗可以相应地被降低。

87.图4是例示根据实施例的包括数据时钟、第一时钟、第二时钟和驱动时钟的时钟信号以及窗口信号的波形的示图。

88.参照图4,例示了数据时钟dclk、窗口信号win、第一时钟clk_1、第二时钟clk_2以及驱动时钟gclk的波形。

89.窗口信号win可以包括与数据时钟dclk的周期t

dclk

相对应的脉冲p

win

。脉冲p

win

可以指示信号从低电平上升到高电平、然后保持在改变后的高电平上的时间段。因此,窗口信号win的脉冲宽度可以基本与数据时钟dclk的周期t

dclk

相同。

90.另一方面,第一时钟clk_1与第二时钟clk_2可以被配置为使得第一时钟clk_1的脉冲p

clk_1

与第二时钟clk_2的脉冲p

clk_2

彼此交替。也就是说,第一时钟clk_1与第二时钟clk_2的相位可能彼此不一致,因此第一时钟clk_1与第二时钟clk_2可彼此交替。这是由于如下事实:第一时钟clk_1由脉冲生成电路的奇数编号的脉冲生成单元生成,并且第二时钟

clk_2由脉冲生成电路的偶数编号的脉冲生成单元生成。这将参照图9和图10进行描述。

91.驱动时钟gclk可以是信号组合电路生成的多个时钟中的任何一个时钟。由信号组合电路生成的多个时钟中的一个时钟可以用作驱动时钟gclk,并且剩余的时钟可以用作用于对窗口信号win进行计数的计数器时钟。这里,由第一信号组合电路使用奇数编号的脉冲生成单元的多个子信号生成的第一时钟clk_1可以用作驱动时钟。由第二信号组合电路使用偶数编号的脉冲生成单元的多个子信号生成的第二时钟clk_2可以用作计数器时钟。因此,驱动时钟gclk的脉冲p

gclk

可以与第一时钟clk_1的脉冲p

clk_1

基本相同。

92.图5是例示根据实施例的包括信号延迟电路的详细配置的时钟生成电路的配置的示图。

93.参照图5,信号延迟电路370可以在该信号延迟电路中包括多个延迟单元(dly2n)501、...、504、505、...和543。多个延迟单元501、...、504、505、...和543可以以级联方式彼此串联连接。

94.多个延迟单元501、...、504、505、...和543中的一个延迟单元可以通过从串联连接的前一延迟单元接收另一延迟信号并将该另一延迟信号延迟预定单位来生成一个延迟信号。一个延迟信号可以被随后的延迟单元延迟预定单位,从而生成另一延迟信号。同时,每个延迟单元可以通过数字地反转延迟信号来生成反相延迟信号。反相延迟信号可以具有与延迟信号相反的逻辑电平。

95.在图5中,第四延迟单元504可生成第四延迟信号dly_04,且可以将第四延迟信号传输到第五延迟单元505。同时,第四延迟单元504可生成第四反相延迟信号dly_04b。随后,第五延迟单元505可延迟第四延迟信号dly_04以生成第五延迟信号dly_05,并且可以将第五延迟信号dly_05传输到第六延迟单元(未示出)。同时,第五延迟单元505可生成第五反相延迟信号dly_05b。上述操作可以通过第一延迟单元501至第43延迟单元543连续地执行。此外,信号延迟电路370可将多个延迟信号dly_xx与多个反相延迟信号dly_xxb传输至脉冲生成电路380。

96.此外,多个延迟单元501、...、504、505、...及543可接收用以调节延迟单位的延迟控制信号dly_ctr。延迟控制信号dly_ctr可根据延迟控制信号dly_ctr中包括的数据来调节每个延迟单元的延迟单位。

97.另一方面,多个延迟单元501、...、504、505、...和543也可以包括在延迟单元之间的与门and。与门and可用来根据延迟启用信号dly_en与延迟禁用信号dly_dis的逻辑值来连接或断开相应的延迟单元。与门and可根据其位置接收延迟启用信号dly_en和延迟禁用信号dly_dis。

98.例如,与第一延迟单元501到第三延迟单元(未示出)连接的与门and可以接收延迟启用信号dly_en,并且与第四延迟单元504到第43延迟单元543连接的与门and可以接收延迟禁用信号dly_dis。如果延迟启用信号dly_en具有逻辑值1,则第一延迟单元501至第四延迟单元504可以被启用然后彼此电导通。如果延迟启用信号dly_en具有逻辑值0,则第一延迟单元501至第四延迟单元504可以被禁用然后彼此断开连接。此外,如果延迟禁用信号dly_dis具有逻辑值1,则第五延迟单元505至第43延迟单元543可以被启用然后彼此导通。如果延迟禁用信号dly_dis具有逻辑值0,则第五延迟单元505至第43延迟单元543可以被禁用,然后彼此断开连接。

99.图6是例示根据实施例的包括信号延迟电路和脉冲生成电路的详细配置的时钟生成电路的配置的示图。

100.参照图6,脉冲生成电路380可以在该脉冲生成电路中包括多个脉冲生成单元601、...、630、631、...和642。多个脉冲生成单元601、...、630、631、...和642可独立配置而不互相连接,并且可生成多个子信号sub_ck1、...、sub_ck30、sub_ck31、...和sub_ck42。

101.多个脉冲生成单元601、...、630、631、...和642中的一个脉冲生成单元可以从多个延迟单元501、...、504、505、...和543中的两个或更多个延迟单元接收延迟信号和反相延迟信号。一个脉冲生成单元可以通过组合延迟信号和反相延迟信号来生成子信号。为了组合延迟信号和反相延迟信号,一个脉冲生成单元可以使用与门and来执行与运算。然后,一个子信号可以具有一个或多个脉冲。由各个脉冲生成单元生成的子信号可以具有相同数量的脉冲,但是其相位可以彼此不同。

102.在图6中,第一脉冲生成单元601可接收并组合第一延迟信号dly_01与第二反相延迟信号dly_02b。第一脉冲生成单元601可以通过对第一延迟信号dly_01与第二反相延迟信号dly_02b执行与运算来生成第一子信号sub_ck1。类似地,第30脉冲生成单元630、第31脉冲生成单元631及第42脉冲生成单元642也可以通过对延迟信号及反相延迟信号执行与运算来分别生成第30子信号sub_ck30、第31子信号sub_ck31及第42子信号sub_ck42。

103.另一方面,多个脉冲生成单元601、...、630、631、...和642可以通过选择信号sel和校准开始信号calb_on来启用或禁用在所述脉冲生成单元中包括的多个脉冲生成单元中的一些或全部脉冲生成单元。这里,选择信号sel可以启用或禁用奇数编号的脉冲生成单元。校准开始信号calb_on可以启用或禁用偶数编号的脉冲生成单元。

104.此外,多个脉冲生成单元601、...、630、631、...和642可对选择信号sel和校准开始信号calb_on以及延迟信号和反相延迟信号执行与运算。因此,多个脉冲生成单元601、...、630、631、...及642中的一些或全部脉冲生成单元可根据选择信号sel及校准开始信号calb_on的逻辑值而被启用或禁用。

105.图7是例示根据实施例的包括第一信号组合电路和第二信号组合电路的详细配置的时钟生成电路的配置的示图。

106.参照图7,第一信号组合电路310可以通过组合多个子信号中的一些子信号来生成第一时钟clk_1,并且第二信号组合电路320可以通过组合多个子信号中的一些子信号来生成第二时钟clk_2。第一信号组合电路310和第二信号组合电路320可以被统称为“信号组合电路”。

107.例如,脉冲生成电路380可以包括m个脉冲生成单元(其中,“m”是2或更大的自然数)。然后,第一信号组合电路310可以通过组合由第x脉冲生成单元(其中,“x”是小于或等于m的奇数)生成的子信号来生成第一时钟clk_1。第二信号组合电路320可以通过组合由第y脉冲生成单元(其中,“y”是小于或等于m的偶数)生成的子信号来生成第二时钟clk_2。

108.在图7中,第一脉冲生成单元601和第31脉冲生成单元631被例示为奇数编号的脉冲生成单元,并且第30脉冲生成单元630和第42脉冲生成单元642被例示为偶数编号的脉冲生成单元。此外,第1、第3、第5、...和第41子信号sub_ck1、3、5、...和41被例示为由奇数编号的脉冲生成单元生成的奇数编号的子信号,并且第2、第4、第6、...和第42子信号sub_ck2、4、6、...和42被例示为由偶数编号的脉冲生成单元生成的偶数编号的子信号。

109.接着,信号组合电路可以通过组合多个子信号来生成时钟。信号组合电路可以对多个子信号执行或(or)运算以组合多个子信号。

110.例如,第一信号组合电路310可以接收作为奇数编号的子信号的第1、第3、第5、...和第41子信号sub_ck1、3、5、...和41,并且可以对这些子信号执行或运算。由于各个子信号具有一个或多个带有不同相位的脉冲,因此可以通过组合多个子信号来生成具有多个脉冲的第一时钟clk_1。类似地,第二信号组合电路320可以接收作为偶数编号的子信号的第2、第4、第6、...和第42子信号sub_ck2、4、6、...和42,并且可以对这些子信号执行或运算。由于各个子信号具有一个或多个带有不同相位的脉冲,因此可以通过组合多个子信号来生成具有多个脉冲的第二时钟clk_2。然后,第一时钟clk_1可以用作驱动时钟gclk,并且第二时钟clk_2可以用作计数器时钟。

111.另一方面,第一信号组合电路310可接收驱动时钟屏蔽信号gclk_mask,以便屏蔽第一信号组合电路310。在此,第一信号组合电路310可对驱动时钟屏蔽信号gclk_mask执行或运算。如果驱动时钟屏蔽信号gclk_mask的逻辑值为1,则第一时钟clk_1可以输出单个电平。也就是说,可以初始化第一信号组合电路310。该初始化操作可以在生成驱动时钟gclk之前预先执行。

112.图8是例示根据实施例的包括第三信号组合电路的详细配置的时钟生成电路的配置的示图。

113.参照图8,第三信号组合电路330可以通过组合多个子信号中的一些子信号来生成第三时钟clk_3。第一信号组合电路310、第二信号组合电路320和第三信号组合电路330可以被统称为“信号组合电路”。

114.与第一信号组合电路和第二信号组合电路类似,第三信号组合电路330也可以通过组合多个子信号来生成第三时钟clk_3。然而,第三信号组合电路330可以仅接收和组合一些特定延迟信号和反相延迟信号。例如,这是由于如下事实:当驱动时钟gclk的频率没有比数据时钟dclk的频率高得多时,在生成无数的延迟信号时不需要生成很多子信号。也就是说,即使存在一些延迟信号及反相延迟信号来生成驱动时钟gclk,也可生成足以对pwm信号进行计数的多个脉冲。因此,如果驱动时钟gclk的频率仅是数据时钟dclk的频率的两倍,则第三信号组合电路330可以通过组合延迟信号和反相信号来生成时钟。

115.在图8中,第三信号组合电路330可以通过对第一延迟信号dly_01与第四反相延迟信号dly_04b执行与运算来生成一个子信号,并且可以通过对第一反相延迟信号dly_01b与第四延迟信号dly_04执行与运算来生成另一子信号。一个子信号和另一子信号可以具有相位彼此不同的脉冲。第三信号组合电路330可以通过对一个子信号和另一子信号执行或运算来生成第三时钟clk_3。

116.图9是例示根据实施例的窗口信号、延迟信号和子信号的波形的示图。

117.参照图9,窗口信号win、延迟信号dly_01至dly_43、以及子信号sub_ck1和sub_ck2可以具有不同的相位。延迟信号dly_01至dly_43可以在窗口信号win被重复延迟的任何时候生成。子信号sub_ck1和sub_ck2通过延迟信号dly_01至dly_43及其反相信号的组合可以具有一个或多个脉冲。

118.当窗口信号win通过信号延迟电路的第一延迟单元时,窗口信号win可以被延迟t1以生成第一延迟信号dly_01。第一延迟信号dly_01与窗口信号win可以具有t1的相位差。

119.当第一延迟信号dly_01通过信号延迟电路的第二延迟单元时,第一延迟信号dly_01可以被延迟t2以生成第二延迟信号dly_02。第二延迟信号dly_02与第一延迟信号dly_01可以具有t2的相位差。

120.类似地,第二延迟信号dly_02可以被延迟t3以生成第三延迟信号dly_03,并且第三延迟信号dly_03可以被延迟t4以生成第四延迟信号dly_04。当窗口信号win通过信号延迟电路的所有延迟单元时,最终可以生成第43延迟信号dly_43。

121.这里,各个延迟信号的延迟时间t1至t4可以对应于第一延迟单元至第四延迟单元的延迟单位。各个延迟单元的延迟单位可以彼此相同或不同。优选地,由于必须生成具有预定间隔的脉冲的时钟,因此各个延迟单元的延迟单位可以相同。各个延迟单元的延迟单位可以由从外部接收到的延迟控制信号确定。

122.另一方面,可以通过延迟信号和反相延迟信号的组合来生成子信号。例如,第一子信号sub_ck1可以通过对第一延迟信号dly_01与第二反相延迟信号(未示出)(第二延迟信号dly_02的反相信号)执行与运算来生成。然后,第一子信号sub_ck1可以被生成为具有在第一延迟信号dly_01和第二反相延迟信号(未示出)重叠的位置处的脉冲。

123.类似地,第二子信号sub_ck2可以通过对第二延迟信号dly_02与第三反相延迟信号(未示出)(第三延迟信号dly_03的反相信号)执行与运算来生成。然后,第二子信号sub_ck2可以被生成为具有在第二延迟信号dly_02和第三反相延迟信号(未示出)重叠的位置处的脉冲。

124.图10是例示根据实施例的窗口信号、子信号、第一时钟、第二时钟和驱动时钟的波形的示图。

125.参照图10,窗口信号win和子信号sub_ck1、sub_ck2、sub_ck3和sub_ck4可以具有不同的相位。子信号sub_ck1、sub_ck2、sub_ck3和sub_ck4可以包括至少一个脉冲。由于子信号sub_ck1、sub_ck2、sub_ck3和sub_ck4是通过组合延迟信号生成的,所以各个子信号的脉冲可以具有不同的相位。

126.例如,第一子信号sub_ck1可以通过对第一延迟信号和第二反相延迟信号执行与运算来生成,并且与窗口信号win相比可延迟t1。第二子信号sub_ck2可以通过对第二延迟信号和第三反相延迟信号执行与运算来生成,且与第一子信号sub_ck1相比可延迟t2。第三子信号sub_ck3可以通过对第三延迟信号和第四反相延迟信号执行与运算来生成,且与第二子信号sub_ck2相比可延迟t3。第四子信号sub_ck4可以通过对第四延迟信号和第五反相延迟信号执行与运算来生成,且与第三子信号sub_ck3相比可延迟t4。

127.另一方面,第一时钟clk_1与第二时钟clk_2可以由多个子信号的组合生成。这里,可以仅使用一部分子信号来生成时钟,而不是使用所有的子信号。

128.例如,第一信号组合电路可以从脉冲生成电路的奇数编号的脉冲生成单元接收奇数编号的子信号,并且可以仅组合奇数编号的子信号,从而生成第一时钟clk_1。因此,第一时钟clk_1可以具有与第一子信号sub_ck1的脉冲相同的位置处的脉冲,并且还可以具有与第三子信号sub_ck3的脉冲相同的位置处的脉冲。此外,第二信号组合电路可从脉冲生成电路的偶数编号的脉冲生成单元接收偶数编号的子信号,并且可仅组合偶数编号的子信号,从而生成第二时钟clk_2。因此,第二时钟clk_2可以具有与第二子信号sub_ck2的脉冲相同的位置处的脉冲,并且还可以具有与第四子信号sub_ck4的脉冲相同的位置处的脉冲。

129.第一时钟clk_1与第二时钟clk_2中的一个时钟可以用作驱动时钟gclk。在图10中,具有奇数编号的子信号的脉冲的第一时钟clk_1可以被用作驱动时钟gclk。因此,驱动时钟gclk可以与第一时钟clk_1相同。

130.图11是例示根据实施例的包括校准选择电路和延迟禁用电路的详细配置的时钟生成电路的配置的示图。

131.参照图11,校准选择电路340可以在该校准选择电路中包括多路复用器mux和与门and。校准选择电路340可以通过多路复用器mux接收数据时钟dclk、窗口信号win和校准开始信号calb_on。校准选择电路340可根据校准开始信号calb_on选择窗口信号win或数据时钟dclk。

132.此外,校准选择电路340可以通过与门and接收延迟启用信号dly_en和多路复用器mux的输出。校准选择电路340可根据延迟启用信号dly_en来输出或不输出数据时钟dclk或窗口信号win至信号延迟电路370。

133.另一方面,延迟禁用电路360可以在该延迟禁用电路中包括与门and。延迟禁用电路360可以通过与门and生成延迟禁用信号dly_dis。延迟禁用电路360可以输出对频率倍增信号mul_x和延迟启用信号dly_en的逻辑值执行与运算的结果,作为延迟禁用信号dly_dis。

134.图12是例示根据实施例的延迟单元的配置的示图。

135.参照图12,延迟单元可以包括一个或多个延迟子单元1201到1232、延迟屏蔽电路1290和多路复用器mux。延迟单元可以通过延迟子单元1201至1232使得延迟输入信号dly_in延迟。一个延迟单元可以接收延迟输入信号dly_in的窗口信号,并且可以将该窗口信号延迟一个单位。另一延迟单元可以连续地延迟已经被延迟一个单位的窗口信号。这里,延迟子单元1201至1232可以确定该一个单位,并且可以通过由延迟屏蔽电路1290启用或禁用延迟子单元1201至1232中的一些延迟子单元来确定该一个单位。

136.例如,在第一延迟单元501的情况下,延迟子单元1201至1232可接收延迟输入信号dly_in。延迟输入信号dly_in可以是窗口信号或数据时钟。这里,将在窗口信号是延迟输入信号dly_in的假设下进行以下描述。第一延迟子单元1201可以通过延迟窗口信号来生成第一小延迟信号。第一小延迟信号可以被传输到多路复用器mux的第一输入端子。随后,第二延迟子单元1202可以通过延迟第一小延迟信号来生成第二小延迟信号。第二小延迟信号可以被传输到多路复用器mux的第二输入端子。其余的延迟子单元也可以以相同的方式操作。最后,第32延迟子单元1232可以通过延迟第31小延迟信号来生成第32小延迟信号,并且可以将该第32小延迟信号传输到多路复用器mux的第32输入端子。当窗口信号通过各个延迟子单元时,窗口信号可以被延迟得更长。当窗口信号通过最后一个延迟子单元(例如,第32延迟子单元1232)时,窗口信号被延迟第一延迟单元501能够延迟的最大值。另一方面,当窗口信号仅通过第一延迟子单元(例如,第一延迟子单元1201)时,窗口信号被延迟第一延迟单元501能够延迟的最小值。多路复用器mux可根据延迟控制信号dly_ctr来选择第一小延迟信号至第32小延迟信号中的一个。

137.如果第一延迟单元501不将窗口信号延迟最大值,即,如果第一延迟单元501输出除第32小延迟信号外的小延迟信号作为第一延迟信号dly_01,则延迟屏蔽电路1290可禁用延迟子单元1201至1232中的一些延迟子单元。

138.例如,如果第一延迟单元501输出第二小延迟信号作为第一延迟信号dly_01,则延迟屏蔽电路1290可禁用第三延迟子单元(未示出)至第32延迟子单元1232。延迟屏蔽电路1290可接收延迟控制信号dly_ctr,并且可根据延迟控制信号dly_ctr来启用或禁用延迟子单元1201至1232。同时,多路复用器mux还可接收延迟控制信号dly_ctr,并且可根据延迟控制信号dly_ctr输出第一小延迟信号至第32小延迟信号中的一个作为第一延迟信号dly_01。

139.如上所述,每个延迟单元可根据延迟控制信号dly_ctr来调节用于延迟信号的延迟单位。这可以通过启用或禁用相应延迟单元内的延迟子单元中的一些延迟子单元来实现。因此,用户能够容易地设置延迟单位,并且可以减少未用于延迟的组件的功耗。

140.图13是例示根据另一实施例的延迟单元的前端的详细配置的示图,并且图14是例示根据另一实施例的延迟单元的后端的详细配置的示图。

141.参照图13和图14,根据本公开的另一实施例的延迟单元可以包括能够扩展延迟的多个延迟子单元。被包括在一个延迟单元中的一个延迟子单元可以扩展或减少小延迟的程度。这里,为了便于说明,一个延迟单元的延迟可以被称为“大延迟”,并且延迟子单元的延迟可以被称为“小延迟”。也就是说,大延迟可以被理解为当延迟输入信号dly_in通过一个延迟单元时要被延迟的程度,并且小延迟可以被理解为当延迟输入信号dly_in通过一个延迟子单元时要被延迟的程度。一个延迟子单元可以在该延迟子单元中包括与门and、多个微延迟单元dl2和多路复用器mux,以便扩展或减少所述小延迟。图13仅例示被包括在延迟单元的前端中的三个延迟子单元,并且图14仅例示被包括在延迟单元的后端中的两个延迟子单元。

142.例如,第二延迟子单元1302可以从第一延迟子单元1301接收第一小延迟信号。第一小延迟信号可通过与门and、多个微延迟单元dl2以及多路复用器mux。第二延迟子单元1302可以将第一小延迟信号延迟了小延迟以生成第二小延迟信号。这里,为了调节小延迟的程度,第二延迟子单元1302可以仅使用一个微延迟单元dl2或者两个或更多个微延迟单元dl2来延迟该第一小延迟信号。第一小延迟信号通过的微延迟单元dl2越多,信号被延迟得越长。在附图中,可以仅使用两个微延迟单元dl2。第一延迟子单元1301的多路复用器mux可以选择已经通过一个微延迟单元dl2的第一延迟信号或已经通过两个微延迟单元dl2的第一延迟信号。

143.此外,第二延迟子单元1302可接收延迟扩展信号dly_ext,并且可根据延迟扩展信号dly_ext来选择已经通过一个微延迟单元dl2的第一延迟信号和已经通过两个微延迟单元dl2的第一延迟信号中的一个。

144.另外,每个延迟子单元可以通过反相器逻辑门从延迟屏蔽电路1290接收屏蔽信号。接收屏蔽信号的延迟子单元可以被启用或禁用。

145.图15是例示根据另一实施例的延迟子单元的示图。

146.参照图15,根据另一实施例,可以仅启用延迟单元中的初始地接收延迟输入信号dly_in的延迟单元,并且可以禁用剩余的延迟单元。信号延迟电路可以仅启用第一延迟单元,以便将延迟输入信号dly_in(窗口信号或数据时钟)延迟最小值。

147.例如,第一延迟子单元1501可以首先接收延迟输入信号dly_in。第一延迟子单元1501可以包括多个微延迟单元dl2及多路复用器mux。微延迟单元dl2可使延迟输入信号

dly_in延迟,且延迟输入信号dly_in的延迟程度可根据所使用的微延迟单元dl2的数量而改变。在图15中,两个微延迟单元dl2和三个微延迟单元dl2可以被包括在第一延迟子单元1501中。延迟输入信号dly_in在通过三个微延迟单元dl2时比在通过两个微延迟单元dl2时延迟得更长。

148.此外,第一延迟子单元1501可接收最小延迟信号dly_min,且可根据最小延迟信号dly_min来选择已通过两个微延迟单元dl2的信号和已通过三个微延迟单元dl2的信号中的一个信号。最小延迟信号dly_min是用于仅驱动第一延迟单元的信号,并且可以控制第一延迟单元501以将该信号延迟最小值。同时,包括第二延迟子单元1502的所有剩余的延迟子单元可以被禁用。

149.相关申请的交叉引用

150.本技术要求2020年5月11日提交的韩国专利申请10

‑

2020

‑

0055908的优先权,其全部内容通过引用并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。