一种用于pam4接收机的时钟与数据恢复电路

技术领域

1.本发明涉及高速通信领域,涉及一种用于pam4接收机的时钟与数据恢复电路。

背景技术:

2.面对传输速率以及电路带宽限制带来的压力,为了实现信息的更高速率传输,考虑使用4级脉幅调制(4

‑

level pulse amplitude modulation,pam4)或其他多级调制的方式来突破这一难题。

3.pam4接收机由模拟前端电路、时钟数据恢复电路(clock data recovery,cdr)以及数字信号处理电路等电路构成。因为在串行通信中通常没有单独的通道用来传输时钟信号,所以在接收端需要从数据中恢复出时钟。时钟数据恢复电路在整个串行链路中起到了至关重要的作用,其性能直接影响了接收信号的好坏。

4.由于pam4信号具有4个电平、12种跳变方式,跳变方式的过零点呈现出离散形式,造成了从pam4信号恢复出来的温度计码周期(脉冲宽度)不一致,并且接收机的pam4信号在判决时受时钟抖动的影响较大,需要更可靠的cdr电路,这也使得高速、低抖动的时钟数据恢复电路成了pam4接收电路的核心电路。pam4信号在经过阈值判决器后,产生的是三路温度计码,属于nrz码(非归零码)。由于不同跳变方式的过零点位置不同,所以这三路的温度计码相对于传统的nrz码具有更大的数据抖动。

5.为了使这些非对称的数据波形不对后续电路造成影响,所以在时钟恢复之前需要先筛选出过中心零点的跳变波形,但不能影响cdr对相位差的正常判决。依据筛选的数据波形与恢复的时钟鉴相,恢复的时钟对三路的温度计码重定时。

6.专利《具有波形筛选功能的pam4接收机用时钟数据恢复电路及pam4接收机》(申请号:202010455938.8)采用三种波形选择方式筛选出所有的8种过中心零点的跳变方式作为pam4 cdr的输入端,输入信号为40gb/s pam4数据,最终恢复时钟峰峰抖动为6.5ps。该专利提出的带波形筛选器的pam4 cdr具有较高的鉴相密度,但是筛选方式的电路结构略显复杂,并且不同筛选路径之间存在明显的延迟差异,不利于pam4 cdr的稳定。

7.专利《鉴频器、pam4时钟数据频率锁定方法、恢复方法及电路》(申请号:201811637731.1)采用鉴频鉴相器和双电荷泵结构,pam4电平跳变筛选方式为:相邻两个采样数据在0或1与2或3之间跳变,则认为数据有效;反之认为数据无效。其由于采用鉴频鉴相器,具有较强的锁相能力,但使用的波形筛选方式仅过滤出过中心阈值的跳变方式,虽然保证了鉴相所需的边沿密度足够高,却未筛选出过中心零点的跳变方式。因此,筛选出的输入信号仍存在不同过零点引入的相位抖动。

8.综上所述,pam4信号具有4种电平和12种跳变方式,使得过零点不尽相同,这些离散过零点造成pam4信号恢复的温度计码周期(脉冲宽度)不一致,因而引起的相位抖动。这不仅使后续解码电路产生时序错误,同时也增大接收机cdr电路的不稳定。因此,波形筛选器电路作为pam4 cdr的核心电路,从12种跳变方式中将过中心零点的跳变方式筛选出来,保证统一固定的过零点是非常重要的。

技术实现要素:

9.本发明提供了一种用于pam4接收机的时钟与数据恢复电路,该电路在保证cdr的锁相环准确锁定的前提下,减小因pam4信号跳变特性所造成的输入抖动。不同于现有的其他pam4 cdr波形筛选器(使用多种复杂的方式筛选出只过中心阈值或只过中心零点的跳变方式),本发明引入的波形筛选器通过2种筛选方式即可从12种跳变方式中筛选出4种既过中心阈值又过中心零点的跳变方式,筛选电路具有筛选电路延迟一致、筛选方式简单有效的优势。中心零点的跳变方式可有效避免跳过零点不同造成的数据相位抖动,增加pam4 cdr的稳定性,过中心阈值的跳变方式可保证pam4 cdr的鉴相密度足够高,加快cdr对输入信号频率以及相位的锁定。本发明的pam4 cdr采用全速率bang

‑

bang鉴相器中的alexander鉴相器,作为开关式系统,其不仅能对输入数据自动重定时,并且在输入数据未发生跳变时不影响振荡器的控制信号。本发明设计一款v/i转换器(电压

‑

电流转换器),充分考虑环路滤波器电容充放电路径的一致性,避免因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性。详见下文描述:

10.一种用于pam4接收机的时钟与数据恢复电路,所述电路包括:

11.一个波形筛选器,通过对pam4接收机的三路温度计码数据以及边沿信息进行逻辑判决,通过2种简单有效的筛选方式从12种跳变方式中筛选出4种既过中心阈值又过中心零点的跳变,在保证跳变沿密度足够高的前提下,解决了pam4信号的12种跳变过零点不一致导致的cdr输入信号较大的输入抖动;

12.一个鉴相器电路,用于比对波形筛选器的筛选信号与cdr恢复时钟的相位差,得出两者之间的相位超前/滞后信息;

13.一个v/i转换器,用于将反映相位差的电压脉冲转换为充放电流,充分考虑环路滤波器电容充放电路径的一致性,避免了因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性;

14.一个环路滤波器,用于反映相位差的脉冲电流对电容进行充放电,将电流信号转换为随相位差增减的控制电压信号,并减小电压信号的纹波;

15.一个压控振荡器,采用pmos交叉耦合结构,根据控制端电压信号再生时钟,其输出时钟频率随控制电压变化,实现频率改变到相位偏移的转换。

16.其中,所述鉴相器电路采用全速率的alexander鉴相器,鉴别出时钟与数据的相位超前/滞后信息,产生脉冲供给v/i转换器使用。

17.进一步地,所述波形筛选器筛选出4种具有既过中心零点又过中心阈值跳变的筛选方式为:

18.第一种跳变筛选方式:v

a

、v

c

均无跳变,v

b

发生跳变;

19.第二种跳变筛选方式:v

a

、v

b

与v

c

均发生跳变。

20.波形筛选器筛选后的跳变波形再分别与鉴相器的输出up、dn进行逻辑与,控制当前跳变周期得到的相位超前/滞后信息是否有效,实现相位信息的使能。

21.本发明提供的技术方案的有益效果是:

22.1、本发明设计结构更简单的波形筛选器,通过2种波形筛选从12种跳变方式中筛选出4种既过中心阈值又过中心零点的数据波形用以鉴相。过中心零点的跳变能避免温度计码周期和数据边沿抖动对cdr锁相的影响;过中心阈值的跳变则具有更高的边沿密度,从

而使cdr锁相速度更快。

23.2、本发明设计的v/i转换器采用全差分结构,充分考虑环路滤波器电容充放电路径的一致性,避免因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性。

24.3、本发明设计的pam4 cdr充分考虑pam4信号特性以及pam4接收机电路的搭配,pam4 cdr采用的poms交叉耦合vco,具有相位噪声低、驱动能力强的特点,差分的v

‑

i转换器缓解了vco控制电压的波动,并且波形筛选器消除了因pam4跳变特性造成的输入抖动。因此,本发明设计的pam4 cdr在保证较小的时钟峰峰值抖动的前提下,实现较大的时钟输出摆幅。

25.综上所述,本发明为筛选低抖动的过零点跳变方式提供了更简单有效的方案,通过2种波形筛选方式从12种跳变方式中筛选出4种既过中心阈值又过中心零点的数据波形用以鉴相。提出全新的v/i转换器,保证环路滤波器电容充放电路径的一致性。50gb/s pam4cdr输出的时钟具有抖动小、摆幅大的优势。对于pam4接收机cdr的波形跳变选择,以及实现低抖动、高稳定性具有很好的效果,可满足pam4接收机对与时钟恢复电路的设计要求。

附图说明

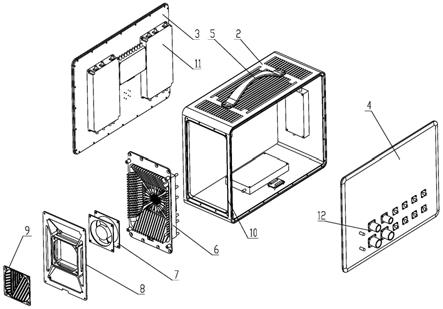

26.图1为pam4接收机的整体电路框图;

27.图2为pam4信号眼图及其12种跳变方式;

28.图3为边沿检测器的电路原理框图;

29.图4为波形选择器的电路原理框图;

30.图5为边沿检测器的时序图(双沿检测);

31.图6为边沿检测器的时序图(单沿检测);

32.图7为波形选择器的时序图;

33.图8为alexander全速率鉴相器的结构图;

34.图9为差分v/i转换器的电路原理图;

35.图10为差分v/i转换器的电路输出波形;

36.图11为压控振荡器(vco)的电路原理图;

37.图12为vco的输出眼图。

具体实施方式

38.为使本发明的目的、技术方案和优点更加清楚,下面对本发明实施方式作进一步地详细描述。

39.实施例1

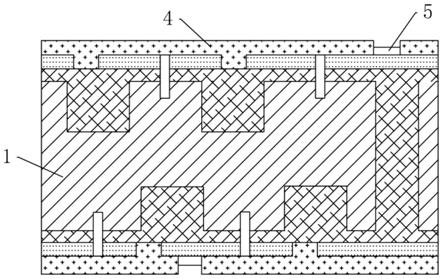

40.本发明实施例提出了一种用于pam4接收机的时钟与数据恢复电路,参见图1,该电路包括:

41.一个波形筛选器,通过对pam4接收机的三路温度计码数据以及边沿信息进行逻辑判决,通过2种简单有效的筛选方式从12种跳变方式中筛选出4种既过中心阈值又过中心零点的跳变,在保证跳变沿密度足够高的前提下,解决了pam4信号的12种跳变过零点不一致导致的cdr输入信号较大的输入抖动;

42.一个鉴相器电路,用于比对波形筛选器的筛选信号与cdr恢复的时钟的相位差,得出两者之间的相位超前/滞后信息;

43.一个v/i转换器,用于将反映相位差的电压脉冲转换为充放电流,充分考虑环路滤波器电容充放电时路径的一致性,避免因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性;

44.一个环路滤波器,用于反映相位差的脉冲电流对电容进行充放电,将电流信号转换为随相位差增减的控制电压信号,并减小电压信号的纹波;

45.一个压控振荡器,采用pmos交叉耦合结构,根据控制端电压信号再生时钟,其输出时钟频率随控制电压变化,实现频率改变到相位偏移的转换。

46.其中,波形筛选器通过对pam4接收机的三路温度计码数据和边沿信息进行逻辑判决,通过2种简单有效的筛选方式从12种跳变方式中筛选出4种既过中心阈值又过中心零点的跳变,在保证跳变沿密度足够高的前提下,解决了pam4信号的12种跳变过零点不一致导致的cdr输入信号较大的输入抖动。

47.鉴相器电路采用全速率的alexander鉴相器,鉴别出时钟与数据的相位超前/滞后信息,产生脉冲供给v/i转换器使用。作为全速率bang

‑

bang鉴相器的alexander鉴相器,其开关式系统不仅仅能对输入数据自动重定时,并且在输入数据未发生跳变时不影响振荡器的控制信号,具有更高的相位差判决准确性。

48.v/i转换器采用全差分结构,由两个传统v/i转换器组成,鉴相器输出的差分脉冲信号分别通过两个v/i转换器,将反映相位差的电压脉冲转换为充放电流,充分考虑环路滤波器电容充放电路径的一致性,避免因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性;

49.进一步地,与补偿驱动能力更强的nmos交叉耦合相比,压控振荡器则采用pmos交叉耦合型vco,其具有更低的相位噪声,对cdr的时钟抖动有较好的改善。vco根据控制端电压信号再生时钟,其输出时钟频率随控制电压变化,实现频率改变到相位偏移的转换。

50.与已有的技术相比,本发明实施例通过筛选输入数据波形,不仅保证了较高的跳变边沿密度,并且减小输入相位抖动,提高鉴相精度,通过降低输入数据抖动来提高cdr恢复时钟的抖动性能。提出的全差分v/i转换器充分考虑环路滤波器电容充放电路径的一致性,提高时钟数据恢复的准确性。

51.实施例2

52.下面结合具体的附图,对实施例1中的方案进行进一步地介绍,详见下文描述:

53.pam4信号在通过接收机的门限判决(阈值比较器)后,pam4信号转化为三路nrz的温度计码,分别为v

a

、v

b

与v

c

,如图1所示,这三路温度计码均输出到pam4 cdr中,作为cdr的输入数据。

54.pam4 cdr电路的设计包括:波形筛选器、鉴频鉴相器(pfd)、v/i转换器(或电荷泵)、环路滤波器、压控振荡器(vco)以及数据重定时器等电路模块。

55.其中,波形筛选器是pam4 cdr的核心模块,它根据输入的三路温度计码数据,分别提取出数据的边沿信息和数据信息,并以此对跳变沿进行有效的筛选。

56.pam4波形具有4种电平、12种跳变方式,如图2和表1所示:

57.其中,当pam4高位信号发生跳变,电平将跳变过中心阈值(即温度计码v

b

发生跳

变),这种跳变方式有8种(

③‑⑩

)。而8种过中心阈值的跳变方式中只有(

⑤‑⑧

)这4种跳变沿过中心零点。本发明实施例中的波形筛选器的功能就是将这4种既过中心阈值又过中心零点的跳变沿筛选出来。

58.表1 12种跳变方式的特性

[0059][0060]

波形筛选器由边沿检测器和波形选择器两部分组成,分别如图3、4所示。在边沿检测器中,以da(限幅放大器输出的其中一路nrz信号)为输入数据的单路为例(其他路同理),da为v

a

的数据信息,da经过一周期的延迟得到da1,而da与da1异或(即),则得到da的边沿信息ea,其逻辑时序图如图5所示,时序图从上而下分别是da、da1与ea。da与da1分别经过一个异或门的镜像延迟,再与ea进行与逻辑(da

·

ea=eah,da1

·

ea=eal),则得到eah与eal,其中eah为da的上升沿信息,eal为da的下降沿信息,逻辑时序图如图6所示,时序图从上而下分别是da、eah、eal与ea。

[0061]

其中,波形选择器需要从12种跳变沿中筛选出上表中的

⑤‑⑧

,这4种跳变沿可以分为两类:

[0062]1→

2、2

→

1,特点:v

a

、v

c

均无跳变,v

b

发生跳变;

[0063]0→

3、3

→

0,特点:v

a

、v

b

与v

c

均发生跳变。

[0064]

根据上述的跳变信息设计波形选择器,如图4所示,和ea

·

eb

·

ec分别为上述两种分类的选择逻辑。而为4种既过中心阈值又过中心零点的跳变沿的选择逻辑,即为跳变沿使能信号。波形选择器的逻辑时序如图7所示,从上而下分别为随机pam4信号、第一类跳变沿筛选信号、第二类跳变沿筛选信号、4种既过中心阈值又过中心零点的跳变沿筛选信号。波形选择器的输出再分别与鉴相器的输出up、dn进行逻辑与,控制当前跳变周期得到的相位超前/滞后信息是否有效。

[0065]

图8为本发明实施例采用的alexander全速率鉴相器,鉴相器对v

b

进行采样并输出数据的相位差信息。然而随机信号v

b

发生跳变并不意味着其是有效跳变沿,需要其与波形选择器的输出使能信号进行逻辑与,才能将相位脉冲信号传递给下一级的v/i转换器。

[0066]

本发明实施例设计的全差分v/i转换器与环路滤波器如图9所示。传统v/i转换器面临着相位脉冲信号up与dn由于电路延迟引起到达时间不一致的问题,使得控制信号上产

生净面积非零的三角脉冲,影响锁相环路的稳定性。全差分v/i转换器不仅解决了差分转单端的问题,而且up_p与dn_n均需要通过电流镜镜像达到环路滤波器,给电容充放电产生控制信号,缓解了传统v/i转换器延迟偏差问题。相位超前时v/i转换器的输出如图10所示,从440mv增大到780mv,在40ns后趋于稳定,纹波抖动小于5mv。

[0067]

图11为本发明实施例中采用的pmos交叉耦合vco,使用三端电感和可变电容作为谐振回路,pmos交叉耦合电路为vco提供负阻,补偿能量损耗。

[0068]

图11为本发明基于tsmc 28nm工艺,对上述电路模块进行整合和性能优化,在电源电压为0.9v、传输速率为50gb/s的pam4 cdr恢复时钟眼图。由图可见,输出摆幅大于700mv,足以使接收机的重定时触发器处于大信号开关状态。在pam4 cdr锁定后,输出时钟眼图峰峰值抖动小于2ps,低抖动的输出时钟不仅大大提高cdr的稳定性,并且通过重定时后接收机nrz信号抖动也会更小。

[0069]

综上所述,本发明实施例设计了一款带波形筛选器的pam4 cdr电路,为筛选低抖动的过零点跳变方式提供了更简单有效的方案,通过2种延迟一致的波形筛选从12种跳变方式中筛选出4种既过中心阈值又过中心零点的数据波形用以鉴相,既能减小由于跳变方式过零点离散所造成的数据相位的抖动,又保证了pam4 cdr的鉴相密度足够高。本发明提出全新的全差分v/i转换器,保证环路滤波器电容充放电路径的一致性,避免了因相位信息脉冲到达时间不一致导致控制信号上产生净面积非零的三角脉冲,提高时钟数据恢复的准确性。本发明设计的50gb/s pam4 cdr的输出时钟具有抖动小、摆幅大的优势,基于tsmc 28nm工艺,在电源电压为0.9v下实现输出时钟眼图峰峰值抖动小于2ps,输出时钟摆幅大于700mv。本发明设计的低抖动、大摆幅pam4 cdr为50gb/s pam4接收机减小数据抖动和误码率提供了有效的解决方案。

[0070]

本发明实施例对各器件的型号除做特殊说明的以外,其他器件的型号不做限制,只要能完成上述功能的器件均可。

[0071]

本领域技术人员可以理解附图只是一个优选实施例的示意图,上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

[0072]

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。