三维存储器件及其制作方法

1.本技术是申请日为2020年4月30日、申请号为202080000941.9、发明名称为“三维存储器件及其制作方法”的发明专利的分案申请。

2.相关申请的交叉引用

3.本技术要求于2020年1月17日提交的中国申请no.202010054215.7的优先权,其全部内容通过引用并入本文。

技术领域

4.本技术涉及半导体技术领域,并且特别地涉及三维(3d)半导体存储器件及其制作方法。

背景技术:

5.与非(nand)存储器是一类不需要电力来保持所存储的数据的非易失型存储器。对消费电子品、云计算和大数据的不断增长的需求带来了对更大容量、更高性能的nand存储器的持续需求。常规的二维(2d)nand存储器接近了其物理极限,现在三维(3d)nand存储器正在发挥重要作用。3d nand存储器使用单个芯片中的多个堆叠层来实现更高的密度、更高的容量、更快的性能、更低的功耗以及更好的经济有效性。

6.在3d nand存储器件的制作期间,形成栅缝隙(gls),以露出衬底上方的牺牲层。之后,刻蚀出腔体并且在该腔体中执行单晶硅和多晶硅的选择性外延生长。由于靠近腔体开口的外延生长更快,因而在填充开口时将在腔体的中间留下孔隙。这些孔隙可能导致电流的泄漏和可靠性问题。

7.gls也用于形成层堆叠体中的栅电极。在制造栅电极之前,刻蚀掉层堆叠体的牺牲堆叠层。然而,牺牲层的离gls较远的一些部分往往未被完全刻蚀掉。因而,可能只部分地制造了栅电极的某些部分,其将导致nand存储单元的故障。

8.所公开的方法和系统涉及解决上文阐述的一个或多个问题以及其他问题。

技术实现要素:

9.在本公开的一个方面,一种3d nand存储器件包括:衬底、处于衬底之上的层堆叠体、第一外延层、第二外延层、第一阵列公共源极(acs)和第二acs。层堆叠体包括存储块以及交替堆叠设置的第一堆叠层和第二堆叠层。第一外延层被沉积在穿过层堆叠体延伸的沟道层的侧面部分上。第二外延层被沉积在衬底上。第一acs和第二acs被配置为用于每一存储块并且穿过层堆叠体延伸。第一外延层与第二外延层毗连。第一acs和第二acs与第二外延层电连接。层堆叠体的部分以及第一acs处于第二acs之间。

10.在本公开的另一方面,一种用于3d nand存储器件的制作方法包括:在衬底之上形成层堆叠体;执行外延生长,以在穿过层堆叠体延伸的沟道层的侧面部分上沉积第一外延层并且在衬底上沉积第二外延层;以及形成用于每一存储块的穿过层堆叠体延伸的第一栅缝隙(gls)和第二gls。层堆叠体包括交替堆叠设置的第一堆叠层和第二堆叠层。第一外延

层与第二外延层毗连。第一gls以及层堆叠体的部分处于第二gls之间。

11.在本公开的另一方面,另一种用于3d nand存储器件的制作方法包括:在衬底之上形成层堆叠体;执行外延生长,以在穿过层堆叠体延伸的沟道层的侧面部分上沉积第一外延层并且在衬底上沉积第二外延层;以及形成用于每一存储块的穿过层堆叠体延伸的第一阵列公共源极(acs)和第二acs。层堆叠体包括交替堆叠设置的第一堆叠层和第二堆叠层。第一外延层与第二外延层毗连。第一acs和第二acs与第二外延层电连接。层堆叠体的部分以及第一acs处于第二acs之间。

12.本领域技术人员根据本公开的说明书、权利要求和附图能够理解本公开的其他方面。

附图说明

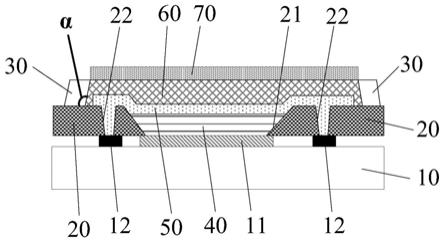

13.图1示意性地示出了根据本公开的实施例的示例性制作工艺中的三维(3d)存储器件的截面图;

14.图2和图3示意性地示出了根据本公开的实施例的在形成沟道孔之后的图1所示的3d存储器件的顶视图和截面图;

15.图4和图5示意性地示出了根据本公开的实施例的在形成栅缝隙(gls)之后的图2和图3所示的3d存储器件的顶视图和截面图;

16.图6和图7示意性地示出了根据本公开的实施例的在沉积并且继而选择性刻蚀gls间隔体之后的图4和图5所示的3d存储器件的截面图;

17.图8和图9示意性地示出了根据本公开的实施例的在执行某些刻蚀步骤之后的图7所示的3d存储器件的截面图;

18.图10示意性地示出了根据本公开的实施例在选择性外延生长之后的图9所示的3d存储器件的截面图;

19.图11示意性地示出了根据本公开的实施例在形成导体层之后的图10所示的3d存储器件的截面图;

20.图12示意性地示出了根据本公开的实施例在形成阵列公共源极(acs)之后的图11所示的3d存储器件的截面图;

21.图13示出了根据本公开的实施例的3d存储器件的制作的示意性流程图;

22.图14和图15示意性地示出了根据本公开的实施例的在形成gls之后的另一3d存储器件的顶视图和截面图;

23.图16示意性地示出了根据本公开的实施例的另一3d存储器件的顶视图;

24.图17和图18示意性地示出了根据本公开的实施例的在形成gls之后的另一3d存储器件的顶视图和截面图;并且

25.图19和图20示意性地示出了根据本公开的实施例的在几个制作步骤之后的图17和图18所示的3d存储器件的截面图和顶视图;

26.图21和图22示意性地示出了根据本公开的实施例的具有附加特征的图17和图18所示的3d存储器件的顶视图和截面图。

具体实施方式

27.下文将参考附图描述本公开的实施例中的技术解决方案。只要有可能,在所有附图中使用相同的附图标记将指示相同或相似的部分。显然,所描述的实施例只是本公开的一些而非全部实施例。可以对各种实施例中的特征进行交换和/或组合。本领域技术人员在不付出创造性努力的情况下基于本公开的实施例获得的其他实施例应当落在本公开的范围内。

28.图1

‑

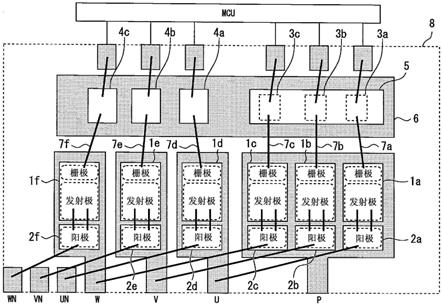

图12示意性地示出了根据本公开的实施例的示例性3d存储器件100的制作工艺。在图1

‑

图12中,截面图处于y

‑

z平面中,并且顶视图处于x

‑

y平面中。如图1所示,3d存储器件100包括衬底110。在一些实施例中,衬底110可以包括单晶硅层。在一些其他实施例中,衬底110可以包括其他半导体材料,例如锗(ge)、硅锗(sige)、碳化硅(sic)、绝缘体上硅(soi)、绝缘体上锗(goi)、多晶硅、诸如砷化镓(gaas)或磷化铟(inp)的iii

‑

v族化合物等。在一些其他实施例中,衬底110可以包括非导电材料,例如玻璃、塑料材料或陶瓷材料。在下文的描述中,作为示例,衬底110包括未掺杂的或轻掺杂的单晶硅层。在一些其他实施例中,衬底110可以不同地掺杂有p型或n型掺杂剂。当衬底110包括玻璃、塑料或陶瓷材料时,衬底110可以还包括沉积在玻璃、塑料或陶瓷材料上的多晶硅薄层,从而使得可以像多晶硅衬底那样对衬底110进行处理。

29.如图1所示,覆盖层120可以被沉积在衬底110之上。覆盖层120是牺牲层并且可以包括单个层或者具有多个层的复合层。例如,层120可以包括氧化硅层和氮化硅层中的一者或多者。层120可以通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或者这些方法中的两者或更多者的组合进行沉积。在一些其他实施例中,层120可以包括其他材料,例如,氧化铝。

30.在覆盖层120之上,可以沉积牺牲层130。牺牲层130可以包括电介质材料、半导体材料或者导电材料。例如,层130可以是单晶硅或多晶硅,其可以是通过cvd和/或pvd工艺沉积的。在下文的描述中,层130的示例性材料为多晶硅。在形成多晶硅层130之后,可以沉积层堆叠体140。层堆叠体140包括堆叠层141和142的多个对,即,层141和142交替堆叠设置。例如,层堆叠体可以包括64对、128对或者超过128对的层141和142。

31.在一些实施例中,层141和142可以分别包括第一电介质材料和不同于第一电介质材料的第二电介质材料。交替的层141和142可以是经由cvd、pvd、ald或者这些工艺中的两者或更多者的组合而沉积的。在下文的讨论中,层141和142的示例性材料分别为氧化硅和氮化硅。氧化硅层141可以被配置作为隔离层,并且氮化硅层142可以被配置作为牺牲层。牺牲堆叠层142在制作工艺期间将被刻蚀掉并且被导体层代替。在一些其他实施例中,可以使用不同的材料形成交替的堆叠层141和142。例如,层141和142可以包括除了氧化硅和/或氮化硅以外的电介质材料。此外,在一些其他实施例中,层141和142可以包括电介质层和导电层。导电层可以包括(例如)钨(w)、钴(co)、铜(cu)、铝(al)、掺杂的硅或硅化物。在下文的讨论中,如前所述,层141和142分别包括氧化硅和氮化硅。此外,氮化硅层142被配置作为在制作工艺中将被刻蚀掉的牺牲层。

32.图2和图3示意性地示出了根据本公开的实施例的在形成并且继而填充沟道孔150之后的3d存储器件100的顶视图和截面图。附图所示的沟道孔150的数量、尺寸和布置方式只是示例性的,并且用于描述器件100的结构和制作方法。沟道孔150被配置为在z方向上延

伸,并且在x

‑

y平面中形成预定图案的阵列。图3所示的截面图是沿图2的aa’线截取的。因而,图3仅示出了处于y

‑

z平面中的截面中的图2的沟道孔150中的一些。

33.沟道孔150可以是通过(例如)干法刻蚀工艺或者干法刻蚀工艺和湿法刻蚀工艺的组合形成的。也可以执行其他制作工艺,例如,涉及光刻、清洁和/或化学机械抛光(cmp)的图案化工艺,而为了简单起见省略了对这些工艺的详细描述。沟道孔150可以具有穿过层堆叠体140以及层130和120延伸并且部分地穿透衬底110的圆柱形或柱形形状。在形成沟道孔150之后,可以在沟道孔的侧壁和底部上沉积功能层151。功能层151可以包括处于沟道孔的侧壁和底部上的用于阻挡电荷流出的阻隔层152、处于阻隔层152的表面上的用于在3d存储器件100的操作期间存储电荷的电荷捕获层153、以及处于电荷捕获层153的表面上的隧穿绝缘层154。阻隔层152可以包括一个或多个层,所述一个或多个层可以包括一种或多种材料。阻隔层152的材料可以包括氧化硅、氮化硅、氮氧化硅、高k电介质材料(例如,氧化铝或氧化铪)、另一宽带隙材料等。电荷捕获层153可以包括一个或多个层,所述一个或多个层可以包括一种或多种材料。电荷捕获层153的材料可以包括多晶硅、氮化硅、氮氧化硅、纳米晶体硅、其他宽带隙材料等。隧穿绝缘层154可以包括一个或多个层,所述一个或多个层可以包括一种或多种材料。隧穿绝缘层154的材料可以包括氧化硅、氮化硅、氮氧化硅、高k电介质材料(例如,氧化铝或氧化铪)、另一宽带隙材料等。

34.在一些实施例中,功能层151可以包括氧化物

‑

氮化物

‑

氧化物(ono)结构。然而,在一些其他实施例中,功能层151可以具有不同于ono构造的结构。在下文的描述中,使用ono结构。例如,功能层151可以包括氧化硅层、氮化硅层和另一氧化硅层。

35.如图3所示,可以在沟道孔150的侧壁上沉积氧化硅层作为阻隔层152。可以在阻隔层152上沉积氮化硅层作为电荷捕获层153。可以在电荷捕获层153上沉积另一氧化硅层作为隧穿绝缘层154。在隧穿绝缘层154上可以沉积多晶硅层作为沟道层155,沟道层155也被称为“半导体沟道”。在一些其他实施例中,沟道层155(半导体沟道)可以包括非晶硅。与沟道孔类似,沟道层155(半导体沟道)也穿过层堆叠体140延伸并且延伸到衬底110中,如图3所示,每一功能层151的部分被配置在堆叠层141和142之一的部分和沟道层155之一的部分之间。阻隔层152、电荷捕获层153、隧穿绝缘层154和沟道层155可以是通过(例如)cvd、pvd、ald或者这些工艺中的两者或更多者的组合而沉积的。在形成沟道层155之后可以用氧化物材料156填充沟道孔150。

36.图4和图5示意性地示出了根据本公开的实施例的在形成栅缝隙(gls)之后的3d存储器件100的顶视图和截面图。图5所示的截面图是沿图4的bb’线截取的。3d存储器件100可以具有被配置在层堆叠体140中的很大数量的nand存储单元。层堆叠体140可以被划分成多个存储块。在一些实施例中,属于一个存储块的nand存储单元可以在块擦除操作中被一起复位。如图4所示,对应于存储块的存储块区域101可以包括沟道孔区域102,沟道孔区域102可以包括第一栅缝隙(gls)区域160。存储块区域101可以由表示第二gls区域的一对gls 170与其他存储块(未示出)分隔开。如图4所示,存储块区域101在y方向上被配置在该对gls 170之间。

37.第一gls区域160可以包括多个gls 161,多个gls 161处于gls 170之间的沟道孔区域102的中间部分中。在一些实施例中,gls 161可以具有与沟道孔150的形状相同的形状并且具有与沟道孔150的尺寸类似的尺寸。在一些实施例中,gls 161可以具有与沟道孔150

的形状不同的形状和/或与沟道孔150的尺寸不同的尺寸。例如,gls 161可以具有圆形形状、方形形状、菱形形状、椭圆形形状等。第一gls区域160可以包括某一数量的gls 161,并且在一些实施例中,第一gls区域160可以沿x方向延伸。在一些其他实施例中,第一gls区域160可以沿x方向和y方向两者延伸。第一gls区域160中的gls 161被配置为不连续,并且沿x方向相互间隔开。也就是说,相邻的gls 161相互分隔开并且两个相邻的gls 161之间的间隔可以至少大于预定值。由于gls 170沿x方向连续地延伸,因而gls 161的布置方式可以被视为沿平行于gls 170的方向延伸并且间隔开。在一些实施例中,两个相邻的gls 161之间的间隔可以是固定值。在一些其他实施例中,两个相邻的gls 161之间的间隔可以具有不同值。相邻的gls 161之间的间隔被配置为使得存储块区域101中的每一nand存储单元的栅电极被电连接。照此,第一gls区域160或者gls 161将沟道孔区域102劈开成两个电连接的部分,并且存储块区域101的功能不受gls 161影响。

38.与不连续的gls 161相比,gls 170在x方向上是连续的。如图4所示,该对gls 170相互平行,并且均在x方向上从沟道孔区域102的左侧连续地延伸到右侧。表示第二gls区域的该对gls 170可以被视作存储块区域101的两个边界区域。因而,多对gls 170可以将器件100的nand存储单元划分成多个存储块区域(未示出)。

39.gls 161和gls 170可以是通过(例如)干法刻蚀工艺或者干法刻蚀工艺和湿法刻蚀工艺的组合形成的。如图5所示,gls 161和gls 170在z方向上均穿过层堆叠体140延伸并且抵达或部分地穿透多晶硅层130。照此,在gls 161和gls 170的底部露出了多晶硅层130的部分。因为gls 161的原因,与不存在gls 161的情形相比露出了层130的更多部分或者更大总面积。因而,变得能够更快并且更容易地刻蚀掉层130,以形成腔体,而且变得能够更快并更容易地在腔体中生长外延层。此外,因为gls 161的原因,露出了堆叠层142的更多部分或更大总面积。类似地,变得能够更快并且更容易地刻蚀掉层142,以形成腔体,并且能够更快并且更容易地用导电材料填充腔体。

40.图6和图7示意性地示出了根据本公开的实施例的在沉积并且继而选择性刻蚀gls间隔体之后的3d存储器件的截面图。如图6和图7所示,gls间隔体包括可以通过cvd、pvd、ald或者这些工艺中的两者或更多者的组合依次沉积的层171、172、173和174。层171和层173可以包括(例如)氮化硅,并且层172和层174可以包括(例如)氧化硅。在沉积gls间隔体之后,执行选择性刻蚀,使得通过干法刻蚀或者干法刻蚀和湿法刻蚀的组合去除所述间隔体的处于gls 161和gls 170的底部的部分。照此,在gls 161和gls 170的底部部分地露出多晶硅层130,如图7所示。

41.图8

‑

图12均示意性地示出了根据本公开的实施例在执行一个或多个刻蚀步骤之后的3d存储器件100的截面图。执行第一选择性刻蚀工艺(例如,选择性湿法刻蚀工艺),以去除多晶硅层130的多晶硅材料。如图8所示,多晶硅材料的去除创建了腔体180,从而露出了覆盖层120和形成在沟道孔150中的上述功能层151的氧化硅层(即,阻隔层152)的底部部分。

42.在对多晶硅层130进行刻蚀之后,执行第二选择性刻蚀工艺(例如,选择性湿法刻蚀工艺),以去除功能层151的氧化硅层的在腔体180中露出的部分。结果,露出了功能层151的氮化硅层(即,电荷捕获层153)的部分。由于gls间隔体的层174是氧化硅,因而层174在第二选择性刻蚀工艺中也被去除。于是,露出了氮化硅层173。

43.在露出氮化硅层153的部分和层173之后,执行第三选择性刻蚀工艺(例如,选择性湿法刻蚀工艺),以去除露出的氮化硅材料,包括氮化硅电荷捕获层153的露出部分以及层173。氮化硅材料的去除露出了处于腔体180中的功能层151的氧化硅层(即,隧穿绝缘层154)的部分以及gls间隔体的氧化硅层172。

44.之后,执行第四选择性刻蚀工艺(例如,选择性湿法刻蚀工艺),以去除氧化硅隧穿绝缘层154的露出部分。在一些实施例中,氧化硅层172可以被配置为充分厚于层154。照此,可以在第四选择性刻蚀中在刻蚀掉层154之后仅去除层172的部分。层172的其余部分可以形成层1721。隧穿绝缘层154的去除在腔体180中露出了多晶硅层(即,沟道层155)的部分。

45.在一些实施例中,覆盖层120可以是氧化硅。之后,可以在刻蚀掉功能层151的底部部分时去除层120。在一些其他实施例中,覆盖层120可以包括除了氧化硅以外的材料,或者可以是复合层。之后,可以通过第五选择性刻蚀工艺去除层120。

46.覆盖层120的去除创建了腔体181,并且在腔体181的底部露出了衬底110的顶表面,如图9所示。腔体181比腔体180大,并且具有开口182和开口183。开口182和开口183分别对应于gls 161和gls 170。如果开口182不存在,那么腔体181将只有两个开口,即处于左侧和右侧的开口183。之后,处于中间的衬底的一些部分以及沟道层155的一些露出部分(即,腔体181的侧壁)与开口183相距的距离可以是开口183之间的距离的大约一半。与开口183越远,硅的选择性外延生长就越慢。之后,硅层在衬底110的与开口183相对的一些部分上的生长可以比在衬底的一些其他部分以及离开口183更远的一些侧壁上的生长更快。之后,在开口183之间的中间区域附近的孔隙被填满之前,沉积在衬底110上的硅可能就已经接近并且封住了开口183。也就是说,可能在沟道孔150中的一些(尤其是在开口183之间的中间区域中的那些沟道孔)附近形成孔隙。因为gls 161的原因,在开口183之间的中间区域附近建立了开口182。照此,硅层可以在该中间区域附近更快地生长,因而硅层可以在腔体181中更均匀地生长并且可以避免孔隙。

47.如图9所示,在上文描述的刻蚀工艺之后,露出了多晶硅沟道层155的靠近沟道孔150的底部的部分以及衬底110。层1721也处于露出状态下。层1721和层171可以用于在堆叠层142被刻蚀和代替之前对层堆叠体140予以保护。

48.图10示意性地示出了根据本公开的实施例在选择性外延生长之后的3d存储器件100的截面图。执行选择性外延生长,从而在腔体181中沉积硅层184。由于衬底110是单晶硅并且沟道层155的露出部分(侧壁)是多晶硅,因而在衬底上生长单晶硅层并且在腔体181的侧壁上生长多晶硅层。所述单晶硅层和多晶硅层同时生长,并且相互毗连或融合,从而形成了层184,如图10所示。在一些实施例中,层182可以掺杂有p型掺杂剂。

49.因为gls 161提供处于gls 170之间的中间区域中的开口182,所以衬底110的顶表面和腔体181的侧壁(包括处于中间区域中的那些)相对于开口182或开口183的至少其中之一处于某一距离内。因而,可以不留孔隙地以层184填充腔体181。如前所述,如果gls 161不存在,那么硅层在开口183之间的中间区域中可能生长得较慢,并且因而可能在衬底110的一些部分上方形成孔隙。这些孔隙可能导致电流的泄漏以及功能问题和可靠性问题。

50.图11示意性地示出了根据本公开的实施例在执行附加制作步骤之后的3d存储器件100的截面图。在选择性外延生长之后,可以执行刻蚀工艺(例如,选择性湿法刻蚀工艺),以去除氧化硅层1721和氮化硅层171。因为层堆叠体140的层142也是氮化硅层,因而在该刻

蚀工艺期间也去除了氮化硅层142,从而在氧化硅层141之间留下腔体。之后,生长导电材料(例如,w),以填充由层142的去除而留下的腔体,从而在氧化硅层141之间形成导体层143。也就是说,导体层143代替电介质层142,并且层堆叠体140现在包括交替的电介质层141和导体层143,如图11所示。导体层143可以平行于衬底110,并且沟道孔150中的每一功能层151的部分处于导体层143之一的部分和沟道孔150中的沟道层155的部分之间。所述导电材料可以是通过cvd、pvd、ald或者这些工艺中的两者或更多者的组合沉积的。在一些实施例中,可以使用诸如co、cu或al的另一种金属作为用于形成导体层143的导电材料。

51.每一导体层143被配置为沿y方向或者在x

‑

y平面中对一行或者多行的nand存储单元进行电连接,并且每一导体层143被配置作为3d存储器件100的字线。形成在沟道孔150中的沟道层155被配置为沿z方向对一列或者一串nand存储单元进行电连接,并且沟道层155被配置作为3d存储器件100的位线。照此,在x

‑

y平面中沟道孔150中的功能层151的部分作为nand存储单元的部分被布置在导体层143和沟道层155之间,即处于字线和位线之间。导体层143的在沟道孔150的部分附近的部分起着nand存储单元的控制栅或栅电极的作用。如图11所示的3d存储器件100可以被视为包括nand单元的串的2d阵列(这样的串又被称为“nand串”)。每一nand串包含多个nand单元,并且垂直地朝衬底110延伸。nand串形成了nand存储单元的3d布置方式。

52.在刻蚀牺牲层142并且沉积导体层143时,gls 161起着重要作用。相邻的层141之间的间隔相对较窄并且gls 170之间的距离相对较长。如果gls 161不存在,那么对层142的刻蚀就不得不贯穿层141之间的窄而长的间隔。之后,层142的水平地处于中间区域中的一些部分可能未被完全刻蚀掉。如果层142的一些部分未被刻蚀掉,那么导体层143的一些部分就可能未被沉积或者未被正确地沉积。由于导体层143起着nand存储单元的栅电极的作用,因而不完整的栅电极可能导致nand存储单元的故障。因为gls 161被配置为处于gls 170之间的中间区域附近,所以层141之间的窄而长的间隔的长度被一分为二。照此,可以将层142完全刻蚀掉,并且可以正确地沉积导体层143或栅电极。

53.在形成导体层143之后,可以制作第一阵列公共源极(acs)190和第二acs 191。首先,可以通过cvd、pvd、ald或者这些工艺中的两者或更多者的组合在gls 161和gls 170的侧壁和底表面上沉积电绝缘层。之后,可以执行干法刻蚀工艺或者干法刻蚀工艺和湿法刻蚀工艺的组合,其将去除层192的处于gls 161和gls 170的底部的部分,从而露出层184的部分。

54.之后,执行其他工艺,以在gls 161和gls 170中形成第一acs 190和第二acs 191。例如,可以将包括诸如氮化钛、w、co、cu、al、掺杂的硅或硅化物的导电材料的导电层193沉积在氧化硅层192上,并且导电层193电接触处于gls 161和gls 170的底部的层184。之后,可以用导电材料194(例如,掺杂的多晶硅)填充gls 161和gls 170。也就是说,在一些实施例中,第一acs 190和第二acs 191均可以包括沉积在gls的侧壁上的隔离层、沉积在隔离层上的导电材料、以及填充gls的导电材料。隔离层使第一acs 190和第二acs 191与导体层143绝缘。在一些实施例中,第一acs 190和第二acs 191均可以包括沉积在gls的侧壁上的隔离层以及沉积在隔离层上并填充该gls的一种或多种导电材料。如图12所示,在第一acs 190和第二acs 191被形成之后,它们变成了穿过层堆叠体140延伸并且电接触层184的导电沟道。

55.由于第一acs 190是通过填充处于第一gls区域160中的gls 161而形成的,因而第一acs 190也可以具有圆柱形或柱形形状。类似地,第二acs 191可以具有与gls 170的形状相同的形状或者类似的形状。照此,第一acs 190的布置方式与gls 161的布置方式相同,并且第二acs 191的布置方式与gls 170的布置方式相同。也就是说,第一acs 190沿x方向以非连续方式延伸并且间隔开,并且第二acs 191沿x方向以连续方式从存储块区域101的左侧延伸到右侧。第一acs 190沿平行于第二acs 191的方向间隔开并且处于第二acs 191之间的区域101的中间部分中。此外,第二acs 191将nand存储单元划分成多个存储块区域(未示出)。每一存储块区域在y方向上可以被布置在一对第二acs 191之间,并且包括沟道孔区域,该沟道孔区域包括非连续的第一acs 190。在一些其他实施例中,第一acs 190可以以非连续方式沿x方向和y方向两者延伸。当第一acs沿x方向和y方向两者延伸时,对应的制作工艺可以保持与第一acs仅沿x方向延伸时相同。

56.在形成第一acs和第二acs之后,执行其他制作步骤或工艺,以完成器件100的制作。为了简单起见,省略了其他制作步骤或工艺的细节。

57.图13示出了根据本公开的实施例的用于制作3d存储器件的示意性流程图200。在211,可以在衬底的顶表面之上沉积牺牲层。所述衬底可以包括半导体衬底,例如,单晶硅衬底。在一些实施例中,在沉积牺牲层之前可以在衬底上沉积基础层或覆盖层。基础层或覆盖层可以包括单个层或者具有在衬底之上依次沉积的多个层的复合层。在一些实施例中,基础层或覆盖层可以包括氧化硅、氮化硅和/或氧化铝。在一些其他实施例中,可以在不在衬底之上沉积基础层或覆盖层的情况下沉积牺牲层。牺牲层可以包括单晶硅、多晶硅、氧化硅或氮化硅。

58.在212,可以在牺牲层上方沉积层堆叠体。所述层堆叠体包括交替堆叠设置的第一堆叠层和第二堆叠层。在一些实施例中,第一堆叠层可以包括第一电介质层,并且第二堆叠层可以包括不同于第一电介质层的第二电介质层。在一些实施例中,第一电介质层和第二电介质层之一被配置作为牺牲堆叠层。在一些其他实施例中,第一堆叠层和第二堆叠层可以分别包括电介质层和导电层。

59.在213,可以形成穿过层堆叠体和牺牲层的沟道孔,以露出衬底的部分。功能层和沟道层可以被沉积在每一沟道孔的侧壁上。形成功能层可以包括在沟道孔的侧壁上沉积阻隔层,在阻隔层上沉积电荷捕获层,以及在电荷捕获层上沉积隧穿绝缘层。在隧穿绝缘层上沉积的沟道层起着半导体沟道的作用,并且可以包括多晶硅层。

60.在214,可以形成垂直地穿过层堆叠体延伸并且延伸到牺牲层中的第一gls和第二gls,并且第一gls和第二gls露出牺牲层的部分。第二gls也沿水平方向连续地延伸,并且将nand存储单元划分成多个存储块区域。存储块区域包括沟道孔区域,沟道孔区域包括第一gls。第一gls沿该水平方向可以是非连续的,并且可以间隔开一个或多个预定的距离值。由于第一gls是非连续的,因而第一gls不影响存储块区域的功能。

61.在215,可以刻蚀掉牺牲层并且可以在衬底上方创建腔体。该腔体露出功能层的阻隔层的处于该腔体中的部分。如果基础层或覆盖层沉积在衬底上,则在该腔体中还露出基础层或覆盖层。之后,分别通过(例如)一种或多种选择性刻蚀工艺刻蚀掉功能层的依次在腔体中露出的各个层,包括阻隔层、电荷捕获层和隧穿绝缘层。结果,可以在腔体中去除功能层的接近衬底的部分。也可以在刻蚀功能层的该部分的工艺期间或者在另一选择性刻蚀

工艺中,刻蚀掉基础层或覆盖层(如果沉积的话)。因而,在腔体中露出了衬底的部分以及沟道层的侧面部分。

62.在216,可以执行选择性外延生长,以在腔体中在衬底上生长单晶硅层并且在沟道层的露出部分(即侧壁)上生长多晶硅外延层。在外延生长期间,所述单晶硅层和多晶硅层相互毗连或者融合,以填充该腔体。因为第一gls被布置在沟道孔区域中,所以与不存在第一gls时相比,单晶硅和多晶硅在腔体中的外延生长速率将是更均匀的。照此,在填充腔体时避免了孔隙的形成。

63.在一些实施例中,层堆叠体包括两个电介质堆叠层,并且堆叠层之一是牺牲性的。牺牲堆叠层可以在217被刻蚀掉,从而留下腔体,之后在218用导电材料填充该腔体,以形成导体层。导电材料可以包括诸如w、co、cu或al的金属。因为第一gls被布置在沟道孔区域的中间,所以牺牲堆叠层可以被完全刻蚀掉。因而,可以避免不完整的栅电极的形成。

64.在219,可以在第一gls和第二gls处沉积并选择性刻蚀氧化物层,以露出填充该腔体的外延层。可以在gls中沉积诸如氮化钛、w、cu、al和/或掺杂的多晶硅的导电材料,以分别形成电接触该外延层的第一acs和第二acs。

65.图14和图15示意性地示出了根据本公开的实施例的另一3d存储器件300的顶视图和截面图。图15所示的截面图是沿图14的cc’线截取的。3d存储器件300的结构可以与器件100的结构类似,但是器件300的第一gls区域162不同于器件100的第一gls区域160。

66.如图14和图15所示,器件300的沟道孔150被配置为在z方向上延伸,并且在x

‑

y平面中形成某一图案的阵列。3d存储器件300的nand存储单元可以通过gls 171被划分成多个存储块区域(未示出)。gls 171可以具有与器件100的gls 170的结构相同的结构或类似的结构。与其他存储块区域(未示出)分隔开的存储块区域103可以包括沟道孔区域104。存储块区域103可以被配置在一对gls 171之间。沟道孔区域104可以包括第一gls区域162,第一gls区域162包括多个gls 163。gls 163沿x方向不连续地延伸并且相互间隔开,而gls 171则在x方向上连续地延伸。与器件100的在x

‑

y平面中具有圆形截面的gls 161形成对照的是,gls 163在x

‑

y平面中具有菱形截面。在一些实施例中,就像图14中那样,gls 163在沟道孔区域104中可以具有相同的形状和尺寸。在一些其他实施例中,gls 163在沟道孔区域104中可以具有不同的形状和/或不同的尺寸。

67.3d nand存储器件300的制作方法可以使用一种或多种与针对器件100所使用的那些工艺相同或类似的工艺。例如,可以在器件300的制作中使用针对器件100所使用的一种或多种沉积工艺、一种或多种刻蚀工艺和/或一种或多种填充工艺。

68.例如,如图14和图15所示,在制作3d存储器件300时,可以通过cvd、pvd、ald或者这些工艺中的两者或更多者的组合在衬底110的顶表面之上沉积层120。接下来,与器件100类似,可以在层120之上依次沉积牺牲层(例如,多晶硅层130)以及包括交替的堆叠层141和142的层堆叠体140。与器件100类似,器件300的堆叠层141和142也可以示例性地分别包括氧化硅和氮化硅。如图15所示,与器件100类似,器件300也可以包括沟道孔150、功能层151和多晶硅沟道层155(半导体沟道)。功能层151以与器件100的方式相同的方式形成在沟道孔150的侧壁和底表面上。功能层151可以示例性地包括沉积在沟道孔150的侧壁和底部上的作为阻隔层152的氧化硅层、沉积在阻隔层152的表面上的作为电荷捕获层153的氮化硅层、以及沉积在电荷捕获层153的表面上的作为隧穿绝缘层154的氧化硅层。多晶硅沟道层

155可以被沉积在隧穿绝缘层154的表面上。沟道孔150可以填充有电介质材料156。

69.接下来,可以形成gls 163和gls 171。如图14所示,gls 163的截面在x

‑

y平面中具有菱形形状。与器件100类似,可以沉积并且选择性刻蚀gls间隔体,以露出牺牲层130。接下来,可以刻蚀牺牲层130、层120以及功能层151的靠近衬底的部分,其在腔体中露出沟道层155的侧面部分以及衬底。在露出沟道孔155的侧面部分以及衬底之后,可以执行选择性外延生长,以生长填充该腔体的外延层。这些外延层电接触沟道层155的露出侧面部分。因为gls 163被配置为在gls 171之间的中间区域,因而在生长填充该腔体的外延层时可以防止孔隙的形成。

70.此后,与器件100类似,可以刻蚀掉堆叠层142并且用导体层(例如,w层)代替堆叠层142。导体层被配置作为3d存储器件300的字线,并且沟道层155被配置作为位线。之后,可以使用氧化物层的沉积和刻蚀工艺在gls 163和gls 171的底部露出该外延层。可以在gls 163和gls 171中沉积导电材料,以形成第一acs和第二acs。第一acs和第二acs均穿过层堆叠体140延伸并且电接触外延层。在此之后,执行其他制作步骤或工艺,以完成器件300的制作。

71.由于gls 163在x

‑

y平面中具有菱形截面,因而形成在gls 163中的第一acs在x

‑

y平面中也具有菱形截面。此外,与器件100类似,第一acs沿x方向以不连续方式延伸并且相互间隔开,并且第二acs沿x方向以连续方式延伸。此外,第二acs将nand存储单元划分成多个存储块区域。每一存储块区域在y方向上可以被布置在一对第二acs之间。存储块可以包括沟道孔区域,沟道孔区域包括非连续的第一acs。在一些其他实施例中,gls 163并且因而第一acs可以分别以非连续方式沿x方向和y方向两者延伸。

72.图16示意性地示出了根据本公开的实施例的另一3d存储器件400的顶视图。为了简单起见,省略了器件400的截面图。3d存储器件400的结构可以与器件100和器件300的结构类似,但是器件400的第一gls区域164不同于器件100的第一gls区域160和器件300的第一gls区域162。

73.与器件100和器件300类似,器件400的沟道孔150被配置为在z方向上延伸,并且在x

‑

y平面中形成图案。如图16所示,3d存储器件400的nand存储单元可以通过gls 172被划分成多个存储块区域(未示出)。gls 172可以具有与器件100的gls 170或者器件300的gls 171的结构相同的结构或类似的结构。与其他存储块区域(未示出)分隔开的存储块区域105可以被配置在一对gls 172之间,并且存储块区域105包括沟道孔区域106。沟道孔区域106可以包括第一gls区域164,第一gls区域164可以包括处于gls 172之间的中间区域附近的多个gls 165。在一些实施例中,gls 165可以具有与器件100的gls 161的形状和尺寸相同的形状和尺寸。在一些其他实施例中,gls 165可以具有与gls 161的形状和尺寸不同的形状或不同的尺寸,例如方形形状、椭圆形形状或其他形状。

74.此外,与gls 161或gls 163形成沿x方向延伸的单行的器件100和器件300形成对照的是,gls 165可以形成均沿x方向延伸的两行。在一行中,gls 165不连续地延伸并且相互间隔开。在一些实施例中,相邻的gls 165可以间隔开恒定的距离。在一些其他实施例中,相邻的gls 165可以间隔开不同值的距离。在一些实施例中,两行的gls 165可以被布置在gls 172之间的中间区域附近并且间隔开预定的距离。

75.在一些其他实施例中,可以将多于两行的gls 165布置在gls 172之间的中间区域

附近。照此,gls 165可以被配置为沿x方向和y方向两者延伸。也就是说,gls 165可以被配置为在存储块区域105中或者在gls 172之间在x

‑

y平面中形成适当的图案。在一些实施例中,就像图16中那样,gls 165可以沿x方向延伸比沿y方向更长的范围。

76.因为相邻的gls 165至少间隔开某一距离,所以存储块区域105中的每一nand存储单元的栅电极被电连接。照此,第一gls区域164或者gls 165可以被视为将沟道孔区域106划分成三个电连接的部分。因而,存储块区域105的功能不受影响。

77.在多于一行的gls 165被形成在一对gls 172之间时,用于刻蚀牺牲层(例如,器件100的层130和层142)的工艺可以变得更快并且更完整。类似地,外延层在腔体中的生长速率(例如,层184在器件100的腔体181中的生长速率)可以变得更加均匀,从而防止孔隙的形成。此外,在一些其他实施例中,当更多沟道孔被布置在存储块区域中时,gls 172之间的距离可以沿y方向增大。gls 172之间的距离可以变得非常大,使得一行的gls 165可能不足以在腔体中的选择性外延生长(例如,层184在器件100的腔体181中的生长)中防止孔隙的形成,或者不足以防止牺牲堆叠层(例如,器件100的层142)的不完整刻蚀。因而,在一些实施例中,可能希望多行的gls 165来避免孔隙的形成和不完整刻蚀。

78.与器件100和器件300类似,但是在附图中未示出的是,器件400可以包括衬底100以及设置在衬底上方的层堆叠体140。器件400也可以包括沿z方向垂直地穿过层堆叠体140延伸的功能层151、沟道层155、第一acs和第二acs。将省略或者不再详细重复对这样的结构的描述。

79.3d nand存储器件400的制作方法可以使用一种或多种与针对器件100和300所使用的那些工艺相同或类似的工艺。例如,可以在器件400的制作中使用针对器件100和300所使用的一种或多种沉积工艺、一种或多种刻蚀工艺和/或一种或多种填充工艺。将省略或者不再详细重复对这样的制作工艺的描述。

80.图17、图18、图19和图20示意性地示出了根据本公开的实施例的另一3d存储器件500的顶视图和截面图。图18所示的截面图是沿图17的dd’线截取的。图19所示的截面图是沿图20的ee’线截取的。3d存储器件500的结构可以与器件100、器件300和/或器件400的结构类似,但是器件500的第一gls区域166不同于器件100的第一gls区域160、器件300的第一gls区域162和器件400的第一gls区域164。

81.与器件100、器件300和器件400类似,器件500的沟道孔150被配置为在z方向上延伸,并且在x

‑

y平面中形成图案。如图17所示,3d存储器件500的nand存储单元可以通过gls 173被划分成多个存储块区域(未示出)。gls 173可以具有与器件100的gls 170或者器件300的gls 171的结构相同的结构或类似的结构。存储块区域107可以包括沟道孔区域108。存储块区域107可以被配置在一对gls 173之间,并且通过gls 173与其他存储块区域(未示出)分隔开。沟道孔区域108可以包括第一gls区域166,第一gls区域166可以包括处于gls 173之间的中间区域附近的多个gls 167。与器件100、器件300和器件400类似,gls 167在z方向上连续地延伸并且在x方向上不连续地延伸。gls 167的截面可以在x

‑

y平面中具有各种形状,例如,图17所示的矩形形状。

82.与器件400类似,但是不同于器件100和器件300,gls 167可以形成与gls 173平行并且沿x方向延伸的两行。在一些实施例中,两行的gls 167可以被布置在gls 173之间的中间区域附近并且间隔开预定的距离。在每一行中,gls 167不连续地延伸并且相互间隔开。

在一些实施例中,相邻的gls 167可以沿x方向间隔开恒定的距离。在一些实施例中,相邻的gls 167可以沿x方向隔开不同值的距离。在一些其他实施例中,可以将多于两行gls 167布置到gls 173之间的中间区域附近。照此,gls 167可以被配置为沿x方向和y方向两者延伸,并且在存储块区域107中或者在gls 173之间在x

‑

y平面中形成2d图案。在一些实施例中,gls 167可以沿x方向延伸比沿y方向更长的范围。

83.由于相邻gls 165沿x方向、y方向或者x方向和y方向之间的另一方向至少间隔开某一距离,因而存储块区域107中的每一nand存储单元的栅电极被电连接。照此,第一gls区域166或者gls 167可以被视为将沟道孔区域108划分成三个电连接的部分。因而,存储块区域107的功能不受gls 167影响。

84.与器件400类似,在多于一行的gls 167被布置到一对gls 173之间时,与不存在gls 167时的情形相比,用于刻蚀牺牲层(例如,器件100的层130或层142)的工艺可以变得更快并且更完整。此外,外延层在腔体中的生长速率(例如,层184在器件100的腔体181中的生长速率)可以变得更加均匀,从而防止孔隙的形成。此外,在一些其他实施例中,当更多沟道孔被布置在gls 173之间时,gls 173之间的距离可以相应地增大。gls 173之间的距离可以变得非常大,使得一行的gls 167可能不足以在腔体中(例如,层184在器件100的腔体181中)的选择性外延生长中防止孔隙的形成,或者不足以防止牺牲堆叠层(例如,器件100的层142)的不完整刻蚀。因而,在一些实施例中,可能需要多行的gls 167来避免孔隙的形成和不完整刻蚀。

85.与器件100、器件300和器件400类似,如图19所示,器件500可以包括衬底110、外延层185、层堆叠体140、第一acs 195和第二acs 196。

86.3d nand存储器件500的制作方法可以使用一种或多种与针对器件100、300和400所使用的那些工艺相同或类似的工艺。例如,可以在器件500的制作中使用针对器件100、300和400所使用的一种或多种沉积工艺、一种或多种刻蚀工艺和/或一种或多种填充工艺。

87.如图18和图19所示,在制作3d存储器件500时,可以通过cvd、pvd、ald或者这些工艺中的两者或更多者的组合在衬底110的顶表面之上沉积覆盖层120。接下来,与器件100、器件300和器件400类似,可以在覆盖层120之上依次沉积牺牲层(例如,多晶硅层130)以及包括交替的堆叠层141和142的层堆叠体140。与器件100、器件300和器件400类似,器件500的堆叠层141和142也可以示例性地分别包括氧化硅和氮化硅。如图17和图18所示,与器件100、器件300和器件400类似,器件500还可以包括沟道孔150、功能层151和多晶硅沟道层155(半导体沟道)。功能层151以与器件100的相同的方式形成在沟道孔150的侧壁和底表面上。功能层151可以示例性地包括沉积在沟道孔150的侧壁和底部上的作为阻隔层152的氧化硅层、沉积在阻隔层152的表面上的作为电荷捕获层153的氮化硅层、以及沉积在电荷捕获层153的表面上的作为隧穿绝缘层154的氧化硅层。多晶硅沟道层155可以被沉积在隧穿绝缘层154的表面上。沟道孔150可以填充有电介质材料156。

88.接下来,可以形成gls 167和gls 173。如图17所示,gls 167的截面在x

‑

y平面中具有矩形形状。之后,与器件100类似,可以沉积并且选择性刻蚀gls间隔体168,以露出牺牲层130,如图18所示。接下来,可以刻蚀掉牺牲层130、覆盖层120、gls间隔体168的部分以及功能层151的靠近衬底部分,其在腔体中露出沟道层155的侧面部分以及衬底。在露出沟道层155的侧面部分以及衬底之后,可以执行选择性外延生长,以在衬底上以及沟道层155的侧

面部分上生长外延单晶硅层和多晶硅层。外延生长填充了该腔体,并且形成了外延层185。外延层185与沟道层155的该侧面部分电接触。由于两行的gls 167被配置在gls 173之间的中间区域,因而在生长填充该腔体的外延层185时可以防止孔隙的形成。

89.此后,与器件100、器件300和器件400类似,可以刻蚀掉gls间隔体168的其余部分以及牺牲堆叠层142,并且可以用导体层143(例如,w层)代替层142。因为两行gls 167被配置为在gls 173之间的中间区域,所以堆叠层142可以被完全刻蚀掉。因而,可以正确地沉积导体层143,而不存在由层142的不完全刻蚀导致的问题。导体层143被配置作为3d存储器件500的字线,并且沟道层155被配置作为位线。接下来,制作第一acs 195和第二acs 196。可以执行沉积工艺,以在gls 167和gls 173的侧壁上和底表面上形成电隔离层,例如,氧化硅层197。可以对层197进行选择性刻蚀,以在gls 167和gls 173的底部露出外延层185。

90.接下来,可以执行其他工艺,以在gls 167和gls 173中形成第一acs 195和第二acs 196。如图19所示,可以沉积包括诸如氮化钛、w、co、cu、al、掺杂硅或硅化物的导电材料的导电层198以覆盖氧化硅层197并且导电层198电接触处于gls 167和gls 173的底部的层185。之后,可以用导电材料199(例如,掺杂的多晶硅)填充这些gls。图20示意性地示出了在填充gls以形成第一acs 195和第二acs 196之后的顶视图。如图19所示,在形成第一acs 195和第二acs 196之后,它们变成了穿过层堆叠体140延伸并且电接触外延层185的导电沟道。在此之后,执行其他制作步骤或工艺,以完成器件500的制作。

91.由于gls 167在x

‑

y平面中具有矩形截面,因而形成在gls 167中的第一acs 195在x

‑

y平面中也具有矩形截面。此外,与器件100、器件300和器件400类似,第一acs 195沿x方向以非连续方式延伸并且间隔开,并且第二acs 196沿x方向以连续方式从存储块区域107的左侧延伸到右侧。此外,第二acs 196可以将器件500的nand存储单元划分成多个存储块区域(未示出)。每一存储块区域(例如,存储块区域107)在y方向上可以被布置在一对第二acs 196之间。此外,每一存储块区域可以包括沟道孔区域,沟道孔区域包括非连续的第一acs 195。如图17和图19所示,第一acs 196可以以非连续方式分别沿x方向和y方向两者延伸。也就是说,在存储块区域107中或者在该对第二acs 196之间,第一acs 195可以被配置为在x

‑

y平面中形成图案,例如,2d图案。由于第二acs 196在x方向上从左侧连续地延伸到右侧,因而第一acs 195可以沿x方向比沿y方向延伸更长的范围。

92.在一些实施例中,在x方向上相邻的第一acs 195之间的间隔可以是固定值。在一些其他实施例中,在x方向上相邻的第一acs 195之间的间隔可以包括不同值。此外,在一些实施例中,gls 167在沟道孔区域108中可以具有相同的形状或尺寸。在一些其他实施例中,各gls 167在沟道孔区域108中可以具有不同的形状或尺寸。相应地,在一些实施例中,第一acs 195在沟道孔区域108中可以具有相同的形状或尺寸。在一些其他实施例中,第一acs 195在沟道孔区域108中可以具有不同的形状或尺寸。

93.第一acs 195被布置为非连续的,不相互接触,并且至少间隔开既定的距离。照此,相邻的第一acs 195之间的间隔提供了nand存储单元之间的电连接。第一acs195可以被视为将沟道孔区域108划分成三个电连接的部分。因而,存储块区域(例如,区域107)中的存储块的功能不受第一acs 195的布置影响。

94.图21和图22示意性地示出了根据本公开的实施例的具有附加特征的3d存储器件500的顶视图和截面图。图22所示的截面图是沿图21的ff’线截取的。所述附加特征是顶部

选择栅(tsg)切口。区域1951表示tsg切口并且在图21和图22中以虚线表示。如图21和图22所示,tsg切口在y方向上具有比第一acs 195的宽度更窄的宽度,并且在x方向上从沟道孔区域108的左侧连续地延伸到右侧。在垂直方向(即,z方向)上,tsg切口在有限的范围内延伸并且仅部分地穿过层堆叠体140。因而,区域1951和第一acs 195在沟道孔区域108和存储块区域107中部分地重叠。

95.在一些实施例中,一行不连续的第一acs 195可以连同tsg切口一起被配置在第二acs 196之间。例如,如果在第二acs 196之间沿y方向有十三行的沟道孔150,那么在一些实施例中,从第二acs 196开始的第七行的沟道孔150可以用于形成一行的第一acs 195。于是,六行的沟道孔150布置在所述一行的第一acs 195的每一侧。此外,多行的第一acs 195可以连同多个tsg切口一起沿y方向被配置在第二acs 196之间。例如,在一些实施例中,当存在7n

‑

1行的沟道孔150(其中,n是大于2的整数)时,可以使用从acs 196开始的第七行形成第一行的第一acs 195,并且可以使用第十四行形成第二行的第一acs 195,等等。在这样的情形中,在两个相邻的行的第一acs195之间或者在acs 196和相邻的行的acs 195之间,存在六行沟道孔150。

96.如图21和图22所示,相邻的acs 195之间的沿x方向的较小间隔意味着acs 195在x

‑

z平面中的较大面积,并且因而是上文描述的刻蚀工艺和填充工艺所期望的。然而,如果相邻acs 195之间的间隔变得太小,那么可能发生可靠性问题,因为相邻acs 195可能相互接触。因而,应当优化acs 195沿x方向的长度。

97.通过使用所公开的存储结构和方法,在存储块区域中的连续的gls之间形成不连续的gls,而不影响存储块的功能。不连续的gls改善了腔体中的选择性外延生长。因而,可以防止孔隙的形成,并且可以避免电流的泄漏问题。非连续的gls还增强了对牺牲堆叠层的刻蚀,其可以防止出现不完整的栅电极。照此,可以提高3d存储器件的质量和可靠性。

98.尽管在本说明书中通过使用具体实施例描述了本公开的原理和实施方式,但是前文对实施例的描述仅旨在辅助对本公开的理解。此外,可以对前述不同实施例的特征进行组合,以形成附加的实施例。本领域技术人员可以根据本公开的思路对所述的具体实施方式和应用范围做出修改。因而,不应将说明书的内容理解成是对本公开的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。