1.本发明涉及半导体结构,更具体地涉及半导体单晶纳米结构(例如纳米线、纳米片)及其制造方法。

背景技术:

2.为了与鳍型场效应晶体管(finfet)和平面fet的最佳性能竞争,必须提高互补型场效应晶体管(cfet)中使用的半导体单晶纳米结构(如纳米线和纳米片)中的电荷迁移率。一种提高所述迁移率的方法是通过在纳米结构中引入适当类型的应变。

3.e.capogreco等人(电子器件的ieee通信,第65卷,第11期,2018年11月,5145

‑

5150)公开了在300mm晶片上的sige应变弛豫缓冲部上制造的45nm鳍型间距压缩的应变p型ge全环绕栅极器件。沿着ge线获得的单轴应变源自ge源极/漏极与ge源极/漏极生长于其上的sige应变弛豫缓冲部之间的晶格失配。该器件依赖于从基材自下而上生长源极和漏极结构。然而,对于新兴半导体单晶纳米结构(包括cfet)而言,该生长工艺不是优选的。不同的是,在该器件中从通道的末端直接外延生长源极和漏极目前是优选的,因为其允许针对不同的叠加纳米结构使用具有不同掺杂类型的不同源极/漏极材料。然而,尚不清楚是否可以通过从这些末端(extremity)外延生长的源极/漏极材料引入应变,更不用说引入适当类型的应变了。

4.因此,在本领域中需要用于解决上述问题的新方法和结构。

技术实现要素:

5.本发明的目的是提供具有良好电荷迁移率的良好半导体结构以及获得该良好半导体结构的方法。

6.上述目的通过根据本发明的方法、半导体结构和用途来实现。

7.在第一方面,本发明涉及一种半导体结构,其包括:

8.a.具有顶表面的半导体基材,

9.b.一个或多个半导体单晶纳米结构,其各自具有第一和第二末端,第一和第二末端限定了平行于半导体基材顶表面并与顶表面隔开非零距离的轴,各纳米结构具有在第一末端上外延生长的源极结构和在第二个末端外上延生长的漏极结构,

10.其中,源极和漏极结构由p掺杂的半导体单晶材料制备,该p掺杂的半导体单晶材料的未应变晶格常数小于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变,或者其中,源极和漏极结构由n掺杂的半导体单晶材料制备,该n掺杂的半导体单晶材料的未应变晶格常数大于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生拉伸应变。

11.在第二方面,本发明涉及用于形成根据第一方面任意实施方式的半导体结构的方法,所述方法包括:

12.a.提供具有顶表面的半导体基材,

13.b.提供一个或多个半导体单晶纳米结构,各半导体单晶纳米结构的第一末端和第二末端限定了与半导体基材的顶表面平行并且与顶表面隔开非零值距离的轴,

14.c.在各半导体单晶纳米结构上、在第一末端上外延生长源极结构以及在第二末端上外延生长漏极结构,

15.其中,源极和漏极结构由p掺杂的材料制备,该p掺杂的材料的未应变晶格常数小于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变,或者其中,源极和漏极结构由n掺杂的材料制备,该材料的未应变晶格常数大于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生拉伸应变。

16.在第三方面,本发明涉及由具有第一未应变晶格常数的p掺杂半导体单晶材料制备的外延生长的源极和漏极结构在由具有第二未应变晶格常数的第二半导体单晶材料制备的半导体单晶纳米结构中引起压缩应变的用途,所述第二未应变晶格常数大于第一未应变晶格常数。

17.在第四方面,本发明涉及由具有第一未应变晶格常数的n掺杂材料制备的外延生长的源极和漏极结构在由具有第二未应变晶格常数的第二半导体单晶材料制备的半导体单晶纳米结构中引起拉伸应变的用途,所述第二未应变晶格常数小于第一未应变晶格常数。

18.本发明实施方式的优点在于,可以在形成p型晶体管的半导体单晶纳米结构中引起压缩应变,并且可以在形成n型晶体管的半导体单晶纳米结构中引起拉伸应变。

19.本发明实施方式的优点在于,可以通过从纳米结构的侧端生长源极和漏极结构来引入适当应变,从而使该结构与cfet技术兼容。

20.本发明所释放的优点在于,其利用了已用于半导体技术的材料,并且几乎不需要对目前的制造实践方式进行改造。

21.本发明实施方式的优点在于,其具有在使用(横向)半导体单晶纳米结构作为通道的fet中提高电荷迁移率并改善fet性能的潜力。

22.本发明特定和优选的方面在所附独立和从属权利要求中阐述。可以将从属权利要求中的特征与独立权利要求中的特征以及其它从属权利要求中的特征进行适当组合,而并不仅限于权利要求书中明确所述的情况。

23.虽然本领域中一直存在对装置的改进、改变和发展,但本发明的概念被认为代表了充分新和新颖的改进,包括改变现有实践,导致提供了该性质的更有效、更稳定和更可靠的装置。

24.本发明的上述和其它特性、特征和优点会在下文具体实施方式中结合附图变得显而易见,其通过实例说明本发明的原理。本说明书仅为了举例,而不是限制本发明的范围。下文引用的参考图是指附图。

附图说明

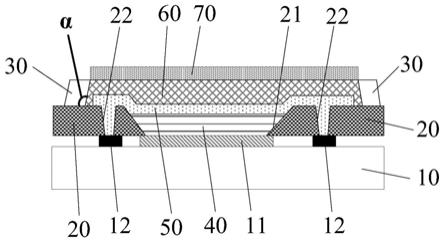

25.图1是在引发纵向应力的tcad模拟中使用的本发明第一方面的实施方式的透视示

意图。

26.图2是在引发竖直应力的tcad模拟中使用的本发明第一方面的实施方式的透视示意图。

27.图3是垂直于纵向方向和竖直方向的方向上的引发应力的tcad模拟中使用的本发明第一方面的实施方式的透视示意图。

28.图4和图5是通过根据本发明第一方面的半导体结构的竖直截面的高角环形暗场扫描透射电子显微镜图像。

29.在不同的图中,相同的附图标记表示相同或类似的元件。

具体实施方式

30.将就具体实施方式并参照某些附图对本发明进行描述,但本发明并不受此限制,仅由权利要求书限定。描述的附图仅是说明性的且是非限制性的。在附图中,一些元件的尺寸可能被夸大且未按比例尺绘画以用于说明目的。所述尺寸和相对尺寸不与本发明实践的实际减小相对应。

31.此外,在说明书和权利要求书中的术语第一、第二、第三等用来区别类似的元件,而不一定是用来描述时间、空间、等级顺序或任何其它方式的顺序。应理解,如此使用的术语在合适情况下可互换使用,本发明所述的实施方式能够按照本文所述或说明的顺序以外的其它顺序进行操作。

32.此外,在说明书和权利要求书中,术语顶部、底部、之上、之下等用于描述目的,而不一定用于描述相对位置。应理解,如此使用的术语在合适情况下可互换使用,本发明所述的实施方式能够按照本文所述或说明的取向以外的其它取向进行操作。

33.应注意,权利要求中使用的术语“包含”不应解释为被限制为其后列出的部分,其不排除其它元件或步骤。因此,其应被理解为指出所述特征、整体、步骤或组分的存在,但这并不排除一种或多种其它特征、整体、步骤或组分或其组合的存在或添加。因此,术语“包括”覆盖了仅存在所述特征的情况以及存在这些特征以及一种或多种其它特征的情况。因此,根据本发明的词“包括”作为一个实施方式还包括不存在其他部件的情况。因此,表述“包括部件a和b的器件”的范围不应被理解为限制所述器件仅由组件a和b构成。其表示对于本发明,所述器件的相关组件仅为a和b。

34.说明书中提及的“一个实施方式”或“一种实施方式”是指连同实施方式描述的具体特征、结构或特性包括在本发明的至少一个实施方式中。因此,在说明书中各处出现的短语“在一个实施方式中”或“在一种实施方式中”不一定全部指同一个实施方式,但可能全部都指同一个实施方式。此外,具体特征、结构或特性可以任何合适方式在一个或多个实施方式中组合,这对于本领域普通技术人员而言是显而易见的。

35.类似地,应理解,在本发明的示例性实施方式的描述中,本发明的不同特征有时在单一实施方式、附图或其说明中集合在一起,这是为了简化公开内容并帮助理解本发明的一个或多个不同方面。然而,本公开内容中的方法不应被理解为反映以下意图:请求保护的本发明需要比各权利要求中明确引用的具有更多的特征。并且,如同所附权利要求所反映的那样,发明方面包括的特征可能会少于前述公开的一个单一实施方式的全部特征。因此,所附权利要求书将被明确地纳入该具体说明,并且各权利要求本身表示本发明的一个独立

实施方式。

36.此外,当本文所述的一些实施方式包括一些但不包括其它实施方式中所包括的其它特征时,不同实施方式的特征的组合应意在包括在本发明范围内,并且形成不同的实施方式,这应被本领域技术人员所理解。例如,在所附的权利要求中,所请求保护的任何实施方式可以任何组合形式使用。

37.此外,本文中描述了某些实施方式作为通过计算机系统的处理器或通过实施功能的其它方式实施的方法、或方法元素的组合。因此,具有用于实施该方法或方法元素所需指令的处理器形成了用于进行该方法或方法元素的装置。此外,本文中描述的设备实施方式的元件是用于执行功能的装置的示例,所述功能通过用于实施本发明目的元件进行。

38.本文的描述中阐述了众多的具体细节。然而应理解,本发明的实施方式可不用这些具体细节进行实施。在其它情况中,为了不混淆对该说明书的理解,没有详细显示出众所周知的方法、步骤和技术。

39.提供以下术语,仅仅是为了有助于理解本发明。

40.如本文所用,除非另外说明,术语“纳米结构”是指其三个尺寸(宽度、长度或高度)中至少一个测量为1至100nm的结构。

41.如本文所用,三维物体(例如,纳米结构)的长度(l)、宽度(w)和高度(h)分别是两个水平尺寸(即,平行于基材主表面(即,顶表面))中最长的、两个水平尺寸中最短的、以及竖直尺寸(即,垂直于基材主表面(即,顶表面))。

42.如本文所用,除非另外说明,术语“纳米线”是指其两个最小尺寸测量为1至100nm的结构,其最大尺寸与第二大尺寸的比率大于2,并且其第二大尺寸与其最短尺寸之间的比率为1至2,更通常为1至1.5。

43.如本文所用,除非另外说明,术语“纳米片”是指其最小尺寸测量为1至100nm并且其第二大尺寸与其第三大尺寸之比大于2的结构。

44.纳米结构通常以横向和竖直两种取向之一存在。横向纳米结构具有对于基材或基材表面的横向取向,即,其最长尺寸(此处为其长度)与其平行。其也可以被称为水平纳米结构。竖直纳米结构的取向与基材或基材表面垂直或竖直,即,其最长尺寸(此处为其长度)与其垂直。

45.本文所指的纳米结构优选是横向(或水平)纳米结构。各纳米结构通常用作场效应晶体管中的通道。

46.如本文所用的,应变结构是在所施加机械力(称为应力)的作用下会变形的结构。在没有此力的情况下,平衡状态下,结构将处于其松弛(即,未应变)状态。在本发明的上下文中,应变结构通常是应变单晶结构,其采用与其未应变(即,松弛)晶格常数不同的(应变)晶格常数(参见下文)。晶格的变形是施加至材料的应力分量的结果,导致了(例如,压缩或拉伸)应变。当该外部应力发生于材料例如在单晶表面上外延生长时,该单晶表面的晶格常数不同于构成该层的材料的相应的未应变(即松弛)晶格常数。

47.如本文所用,区分单晶材料或表面的未应变晶格常数(即,在没有应力的情况下,材料的松弛晶格常数)和实际晶格常数(即,存在于对象结构中的单晶材料或表面的晶格常数,其可以等于或不同于其未应变晶格常数)。

48.现在通过对本发明若干实施方式的详细描述来描述本发明。很明显,可根据本领

域技术人员的知识构建本发明的其它实施方式,而不背离本发明的技术教示,本发明仅受所附权利要求书的限制。

49.参考晶体管。这些晶体管是具有第一主电极(例如漏极)、第二主电极(例如源极)以及用于控制第一主电极和第二主电极之间电荷流动的控制电极(例如栅极)的三端子器件。

50.本发明源于发明人认识到,与传统的源极/漏极应力源中所观察到的不同,并且令人惊奇的是,纳米结构(例如,纳米线或纳米片)的第一末端上外延生长源极结构并且在第二末端上外延生长漏极结构使得在源极/漏极结构的未应变晶格常数大于通道的未应变晶格常数时导致了拉伸的纵向通道应变。已经由该观察和附加的模拟和实验得出了本发明的各个方面。

51.在第一方面,本发明涉及一种半导体结构,其包括:

52.a.具有顶表面的半导体基材,

53.b.一个或多个半导体单晶纳米结构,其各自具有第一和第二末端,第一和第二末端限定了平行于半导体基材顶表面并与顶表面隔开非零距离的轴,各纳米结构具有在第一末端上外延生长的源极结构和在第二个末端外上延生长的漏极结构,

54.其中,源极和漏极结构由p掺杂的半导体单晶材料制备,该p掺杂的半导体单晶材料的未应变晶格常数小于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变,或者其中,源极和漏极结构由n掺杂的半导体单晶材料制备,该n掺杂的半导体单晶材料的未应变晶格常数大于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生拉伸应变。

55.换言之,在第一方面中,本发明涉及一种半导体结构,其包括:

56.a.具有顶表面的半导体基材,

57.b.一个或多个半导体单晶纳米结构,其各自具有第一和第二末端,第一和第二末端限定了平行于半导体基材顶表面并与顶表面隔开非零距离的轴,各纳米结构具有在第一末端上的源极结构和在第二个末端上的漏极结构,

58.其中,与第一末端表面接触的源极结构表面的晶格结构与所述第一末端表面的晶格结构匹配,

59.其中,与第二末端表面接触的漏极结构表面的晶格结构与所述第二末端表面的晶格结构匹配,

60.其中,源极和漏极结构由单晶的p掺杂半导体单晶材料制备,该单晶的p掺杂半导体单晶材料的未应变晶格常数小于制造源极和漏极结构存在于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变,或者

61.其中,源极和漏极结构由单晶的n掺杂半导体单晶材料制备,该单晶的n掺杂半导体单晶材料的未应变晶格常数大于制造源极和漏极结构存在于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生或拉伸应变。

62.第一方面的两种构想在本文中被认为是等效的,因为第二结构上外延生长的第一

结构是单晶结构,其中,其与第二结构表面接触的表面的晶格结构与所述第二结构表面的晶格结构匹配。

63.而且,不同于将第一和第二末端描述为限定与半导体基材的顶表面平行并且与顶表面隔开非零距离的轴,其等同于将第一和第二末端描述为通过半导体单晶纳米结构长度隔开,所述长度平行于半导体基材顶表面并且与其隔开非零距离。

64.在一些实施方式中,第一方面的半导体结构可以包括彼此堆叠的多个iv族半导体单晶纳米结构。例如,半导体结构可以包括堆叠于p型iv族半导体单晶纳米结构上的n型iv族半导体单晶纳米结构,或者堆叠于n型iv族半导体单晶纳米结构上的p型iv族半导体单晶纳米结构。

65.在一些实施方式中,第一方面的半导体结构可以是cfet。

66.例如,cfet可以包括位于p型(或n型)iv族半导体单晶鳍上方的n型(或p型)iv族半导体单晶纳米线。作为另一示例,cfet可以包括位于p型(或n型)iv族半导体单晶纳米线或纳米片上的n型(或p型)iv族半导体单晶纳米线或纳米片。

67.在一些实施方式中,半导体基材可以是iv族半导体基材。例如,其可以选自si、ge、si1‑

z

ge

z

(其中0<z<1)、sn、ge1‑

w

sn

w

(其中0<w<1)、si

i

ge1‑

i

‑

j

sn

j

(其中0<i<1且0<j<1,并且0<i j<1)。优选地,其选自si、ge、和si1‑

z

ge

z

(其中0<z<1)。例如,其可以是由该材料制备的晶片。在一些实施方式中,基材可以包括一个或多个鳍,并且一个或多个半导体单晶纳米结构各自直接位于鳍上方。

68.在一些实施方式中,介电层可以存在于半导体基材上。具体来说,介电层可以至少与基材上源极和漏极结构的竖直投影重叠。在生长源极和漏极结构之前,源极和漏极结构将会生长的基材上以及下方的介电层的存在阻止了从基材向外的外延生长。尽管可以容忍从基材向外的外延生长,因为其不会影响半导体单晶纳米结构中所获得的应变,但这也是不必要的。

69.在一些实施方式中,半导体基材上的介电层可以是形成基材的半导体单晶材料的氧化物。

70.介电层通常横向延伸超过半导体单晶纳米结构的末端。超出这些末端的介电层的存在确保了源极和漏极在其形成期间不会由基材表面外延生长,而是分别由第一末端和第二末端表面外延生长。

71.在一些实施方式中,介电层的厚度(即,高度)可以为1至50nm,优选5至50nm,更优选10至50nm,更优选10至35nm。

72.一个或多个半导体单晶纳米结构的数量不受限制。

73.在一些实施方式中,一个或多个半导体纳米结构可以包括第一和第二相邻、共面且分开的半导体单晶纳米结构,其中,第一纳米结构的漏极结构和源极结构均不会与第二半导体单晶纳米结构的漏极结构或源极结构接触。这是有利的,因为通过避免外延融合(epitaxial merging),避免了与之相关的典型缺陷。

74.在任意实施方式中,半导体单晶纳米结构各自由半导体单晶材料制备。半导体单晶材料优选是iv族半导体单晶材料。iv族半导体单晶材料优选选自si、si1‑

y

ge

y

和ge,其中,0<y<1。

75.在一些实施方式中,一个或多个半导体单晶纳米结构中的至少一个选自纳米线和

纳米片。

76.在一个或多个半导体单晶纳米结构中的至少一个选自纳米线和纳米片的实施方式中,半导体结构可以是互补型场效应晶体管。在该实施方式中,基材通常包括一个或多个鳍,并且一个或多个半导体单晶纳米结构各自直接位于鳍上方。

77.在一些实施方式中,各半导体单晶纳米结构的长度可以为5nm至200nm,优选10至100nm。

78.优选地,各半导体单晶纳米结构的长度对应于其第一和第二末端之间的距离。本发明的效果在末端之间距离较短的情况下最强,因为末端处引起的应变比末端之间中距处引起的应变更重要。

79.在一些实施方式中,各半导体单晶纳米结构的高度可以为3nm至200nm,优选5nm至200nm,更优选10nm至60nm,最优选15nm至50nm。

80.在一些实施方式中,各半导体单晶纳米结构的宽度可以为3nm至200nm。

81.在一些实施方式中,半导体单晶纳米结构的长度与高度之比可以为1至10,优选2至10,更优选2至4。

82.通常,各半导体单晶纳米结构包括场效应晶体管的通道。与该通道接触并覆盖(例如完全覆盖)该通道时,通常存在栅极结构和介电间隔物。介电间隔物是有利的,因为其防止外延生长离开半导体单晶纳米结构的末端。

83.在一些实施方式中,半导体基材的顶表面与半导体单晶纳米结构隔开的非零距离可以是5至50nm,优选地10至50nm,更优选地15至35nm。

84.在基材包括一个或多个鳍并且一个或多个半导体单晶纳米结构各自直接在一个鳍上方的实施方式中,非零距离可以是鳍顶部与半导体单晶纳米结构底部之间的距离。

85.源极结构和漏极结构分别在第一末端和第二末端上外延生长。

86.由于其在各自末端上外延生长,与第一/第二末端表面接触的源极/漏极结构的表面的晶格结构与所述第一/第二末端表面的晶格结构匹配。

87.在一个实施方式中,源极和漏极结构由单晶的p掺杂半导体单晶材料制备,该单晶的p掺杂半导体单晶材料的未应变晶格常数小于制造源极和漏极结构存在于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变。

88.例如,

89.‑

当源极和漏极结构生长于其上的半导体单晶纳米结构包含si1‑

y

ge

y

时,源极和漏极结构可以包括p掺杂的si1‑

x

ge

x

,其中x<y≤1;或

90.‑

当源极和漏极结构生长于其上的半导体单晶纳米结构由si或si1‑

y

ge

y

制备时,源极和漏极结构可以包括p掺杂的sic,其中0<y≤1,

91.由此在纳米结构中产生压缩应变。

92.在另一实施方式中,源极和漏极结构由单晶的n掺杂半导体单晶材料制备,该半导体单晶材料的未应变晶格常数大于制造源极和漏极结构存在于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生拉伸应变。

93.例如,

94.‑

当源极和漏极结构生长于其上的半导体单晶纳米结构包含si1‑

y

ge

y

时,源极和漏

极结构包含n掺杂的si1‑

x

ge

x

,其中x>y≥0;或

95.‑

当源极和漏极结构生长于其上的半导体单晶纳米结构由ge或si1‑

y

ge

y

制备时,源极和漏极结构包含n掺杂的ge1‑

w

sn

w

,其中,0<w<0.1,0≤y≤1;或

96.‑

当源极和漏极结构生长于其上的半导体单晶纳米结构由ge制备时,源极和漏极结构包含n掺杂的si

i

ge1‑

i

‑

j

sn

j

,其中0<i<j<1,且0<i j<1。

97.在一些实施方式中,

98.‑

当源极和漏极结构的iv族半导体生长于其上的半导体单晶纳米结构包含si1‑

y

ge

y

时,源极和漏极结构的iv族半导体包括n掺杂的si1‑

x

ge

x

,其中x>y≥0;或

99.‑

当源极和漏极结构的iv族半导体生长于其上的半导体单晶纳米结构由ge或si1‑

y

ge

y

制备时,源极和漏极结构的iv族半导体包括n掺杂的ge1‑

w

sn

w

,其中,0<w<0.1,0≤y≤1;或

100.‑

当源极和漏极结构的iv族半导体生长于其上的半导体单晶纳米结构由ge制备时,源极和漏极结构的iv族半导体包括n掺杂的si

i

ge1‑

i

‑

j

sn

j

,其中,0<i<1,0<j<1,和0<i j<1,其中,对i和j进行选择以使得si

i

ge1‑

i

‑

j

sn

j

的晶格常数大于ge的晶格常数。

101.在一些实施方式中,源极和漏极结构包含n掺杂si1‑

x

ge

x

,而源极和漏极结构生长于其上的半导体单晶纳米结构包含si,其中,0.70≥x>0,例如0.70≥x≥0.2或0.70≥x≥0.40。

102.在一些实施方式中,源极和漏极结构可以各自显示出除具有源极和漏极结构生长于其上的纳米结构末端的界面之外的表面,所述表面平行于形成该末端的表面。

103.在一些实施方式中,源极和漏极结构可以各自显示出形成一定角度的{111}族的两个相交平面,其中,源极结构的所述角度指向背离漏极结构的所述角度。

104.在其中源极和漏极结构包括n掺杂材料的实施方式中,n掺杂可能是由于sb和bi中的一种或多种、以及任选的as和p中的一种或多种的存在导致。这是有利的,因为这样的掺杂有助于使源极和漏极材料的未应变晶格常数增加超过半导体单晶材料的未应变晶格常数,使源极和漏极生长于其上的半导体单晶纳米结构拉伸应变。

105.在一些实施方式中,外延源极和漏极结构可以由掺杂有sb和bi中的一种或多种以及as和p中的一种或多种的iv族半导体制备。这是有利的,因为与不存在as和/或p相比,as和/或p的存在有助于实现更高的掺杂浓度。

106.在一些实施方式中,[sb] [bi]>[as] [p]。这有利于获得拉伸应变。优选地,([sb] [bi])>1.1([as] [p])。

[0107]

在一些实施方式中,[sb] [bi]>10

20

cm

‑3,优选[sb] [bi]>2*10

20

cm

‑3。

[0108]

在一些实施方式中,[as] [p]>10

20

cm

‑3,优选[as] [p]>2*10

20

cm

‑3。

[0109]

在任意实施方式中,源极和漏极结构的iv族半导体中的掺杂剂浓度可以为至少10

20

cm

‑3,优选大于2

×

10

20

cm

‑3。

[0110]

类似的,当在半导体单晶纳米结构中产生压缩应变,该压缩应变至少存在于半导体单晶纳米结构的纵向方向,即,沿着其长度。在一些实施方式中,压缩应变还存在于与基材垂直的方向。在一些实施方式中,压缩应变还存在于与基材平行但与半导体单晶纳米结构长度垂直的方向。通常,压缩应变存在于全部三个方向。

[0111]

类似的,当在半导体单晶纳米结构中产生拉伸应变,该拉伸应变至少存在于半导

体单晶纳米结构的纵向方向,即,沿着其长度。在一些实施方式中,拉伸应变还存在于与基材垂直的方向。在一些实施方式中,拉伸应变还存在于与基材平行但与半导体单晶纳米结构长度垂直的方向。通常,拉伸应变存在于全部三个方向。

[0112]

在第二方面,本发明涉及用于形成根据第一方面任意实施方式的半导体结构的方法,所述方法包括:

[0113]

a.提供具有顶表面的半导体基材,

[0114]

b.提供一个或多个半导体单晶纳米结构,各半导体单晶纳米结构的第一末端和第二末端限定了与半导体基材的顶表面平行并且与顶表面隔开非零值距离的轴,

[0115]

c.在各半导体单晶纳米结构上、在第一末端上外延生长源极结构以及在第二末端上外延生长漏极结构,

[0116]

其中,源极和漏极结构由p掺杂的材料制备,该材料的未应变晶格常数小于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生压缩应变,或者其中,源极和漏极结构由n掺杂的材料制备,该材料的未应变晶格常数大于制造源极和漏极结构生长于其上的半导体单晶纳米结构的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构中产生拉伸应变。

[0117]

第二方面的任意特征可以如第一方面任意实施方式对应描述。具体来说,半导体结构、组件、半导体基材、介电层、一个或多个半导体单晶纳米结构、其末端、非零距离、源极结构和漏极结构可以如本发明第一方面对应描述。

[0118]

在第三方面,本发明涉及由具有第一未应变晶格常数的p掺杂半导体单晶材料制备的外延生长的源极和漏极结构在由具有第二未应变晶格常数的第二半导体单晶材料制备的半导体单晶纳米结构中引起压缩应变的用途,所述第二未应变晶格常数大于第一未应变晶格常数。

[0119]

第三方面的任意特征可以如第一或第二方面任意实施方式对应描述。具体来说,源极和漏极结构、其外延生长、制备其的p掺杂半导体单晶材料、半导体单晶纳米结构、以及第二半导体单晶材料可以如本发明第一和第二方面任意实施方式对应描述。

[0120]

在第四方面,本发明涉及由具有第一未应变晶格常数的n掺杂材料制备的外延生长的源极和漏极结构在由具有第二未应变晶格常数的第二半导体单晶材料制备的半导体单晶纳米结构中引起拉伸应变的用途,所述第二未应变晶格常数小于第一未应变晶格常数。

[0121]

第四方面的任意特征可以如第一或第二方面任意实施方式对应描述。具体来说,源极和漏极结构、其外延生长、制备其的n掺杂半导体单晶材料、半导体单晶纳米结构、以及第二半导体单晶材料可以如本发明第一和第二方面任意实施方式对应描述。

[0122]

现在我们参考图1

‑

3,其中,各图显示了半导体结构(1)的三个实施例,各实施例包括:

[0123]

a.由其上具有任选介电层(4)的半导体基材(3)形成的组件(2),该半导体基材(3)具有顶表面(8),

[0124]

b.一个或多个半导体单晶纳米结构(5),各半导体单晶纳米结构(5)的第一末端(6)和第二末端(7)限定了与半导体基材(3)的顶表面(8)平行并且与顶表面(8)隔开非零值距离(d)的轴,各纳米结构(5)具有在第一(6)末端外延生长的源极(9)结构和在第二(7)末

端外延生长的漏极(10)结构,

[0125]

其中源极(9)和漏极(10)结构由p掺杂的半导体单晶材料制备,该半导体单晶材料的未应变晶格常数小于制造源极(9)和漏极(10)结构生长于其上的半导体单晶纳米结构(5)的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构(5)中产生压缩应变,或者其中源极(9)和漏极(10)结构由n掺杂的半导体单晶材料制备,该半导体单晶材料的未应变晶格常数大于制造源极(9)和漏极(10)结构生长于其上的半导体单晶纳米结构(5)的半导体单晶材料的未应变晶格常数,从而在该半导体单晶纳米结构(5)中产生拉伸应变(11)。

[0126]

在各图中,这三个半导体结构(1)在其所含的半导体单晶纳米结构(5)的长度上不同。图1

‑

3的各图表示这三个不同结构,但是在图1

‑

3的各图中沿不同方向对该结构中引起的应变进行测量。

[0127]

在图1中,沿纵向方向x对应变进行测量。

[0128]

在图2中,沿竖直方向z对应变进行测量。

[0129]

在图3中,沿y方向(垂直于x和z)对应变进行测量。

[0130]

在图1

‑

3的各图中,描绘了长度不同的三个不同硅单晶纳米结构(5)的右后四分之一。换句话说,描绘了右半部,描绘了后半部,但未描绘左半部,也未描绘前半部。在各图中,左侧的纳米结构(5)的长度为28nm,中间的纳米结构(5)的长度为50nm,右侧的纳米结构(5)的长度为100nm。在各图中,左侧的纳米结构(5)的宽度为14nm,中间的纳米结构(5)的宽度为24nm,右侧的纳米结构(5)的宽度为28nm。给出尺寸用于说明目的。在各情况下,基材是硅晶片,并且介电层(4)是sio2。

[0131]

仅描绘了漏极(10)的后半部,而不是其前半部。在图1至3的情况下,漏极由si

0.45

ge

0.55

制备。

[0132]

在这些图的各图中可看出形成一定角度的{111}族的两个相交平面(13,13’)。

[0133]

从这些图中还可以看出,漏极(10)是从纳米结构(5)而不是从基材生长。超出末端的任选介电层(4)的存在确保了源极(9)和漏极(10)在其形成期间不会由基材表面外延生长,而是由第一(6)末端和第二(7)末端表面外延生长。

[0134]

纳米结构(5)中显示的黑斑表示高于5.108pa的拉伸应力。

[0135]

漏极(10)中显示的黑斑表示高于5.108pa的压缩应力。

[0136]

由图1可见,纵向(x)拉伸应力主要存在于末端(7)处,并且趋向于向纳米结构(5)的中央减小。

[0137]

由图2可见,竖直(z)拉伸应力主要存在于末端(7)处,并且趋向于朝着纳米结构(5)的中央减小。

[0138]

由图3可见,与x和z垂直方向的拉伸应力主要存在于末端(7)处,并且趋向于朝着纳米结构(5)的中央减小。

[0139]

已经观察到拉伸应力值朝着纳米结构(5)中央(图中未显示)减小。

[0140]

值得注意的是,所进行的模拟表明出器件宽度的程度对所测量应力影响很小或没有影响。

[0141]

同样值得注意的是,对于最长100nm的纳米结构(5),靠近源极(9)或漏极(10)的应变可以达到1%,而源极(9)漏极(10)轴的中间测得的应变可以低于0.2%。

[0142]

图4和5是根据本发明一个实施方式制备的样品的高角暗场扫描透射电子显微镜图像,其中,硅纳米结构(5)具有生长于其末端的si

0.45

ge

0.55

。在图4中,硅纳米结构(5)的长度为约150nm,并且高度为约30nm。在图5中,一个或多个硅单晶纳米结构(5)包括第一和第二相邻、共面且分开的硅单晶纳米结构(5),其中,第一纳米结构(5)的漏极(10)结构和源极(9)结构均不会与第二半导体单晶纳米结构(5)的漏极(10)结构或源极(9)结构接触。

[0143]

应理解,虽然针对本发明的装置已讨论了优选的实施方式、具体的构造和配置以及材料,但可以各种形式和细节做出各种改变或改进而不偏离本发明的范围。对本发明范围内的所述方法可以增加或减少步骤。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。