1.本发明涉及一种功率半导体器件及制备方法,尤其是一种能降低米勒电容的功率半导体器件及制备方法。

背景技术:

2.绝缘栅双极晶体管(igbt)是一种被工业广泛应用的开关器件,它是由mos器件和pin器件组合而成,其中在充当开关器件时,会存在导通损耗和开关损耗。在高频应用领域,开关损耗占比较大,而对开关损耗影响最大的是弥勒平台阶段,弥勒平台的长短又主要是受控于弥勒电容的大小。

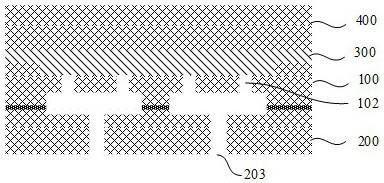

3.对元胞采用沟槽形式的igbt器件以及mosfet器件,在栅电极具体制备工艺过程中,一般是先刻蚀沟槽,再依次进行牺牲氧化、氧化刻蚀以及栅氧的工艺过程,并在栅氧后填充掺杂的多晶硅(gate poly),具体制备的结构,如图1所示。

4.采用上述工艺形式制备得到的栅电极时,弥勒电容相对较大,导致开关损耗会比较高,同时,由于沟槽底部的氧化层一般相对较薄,导致耐击穿能力较差,导致制备得到的igbt器件以及mosfet器件的可靠性较差。

技术实现要素:

5.本发明的目的是克服现有技术中存在的不足,提供一种能降低米勒电容的功率半导体器件及制备方法,其能降低米勒电容,提高器件的可靠性,与现有工艺兼容,安全可靠。

6.按照本发明提供的技术方案,所述能降低米勒电容的功率半导体器件,包括半导体衬底以及设置于所述半导体衬底中心区的元胞区;所述元胞区内包括若干并联分布的元胞,且元胞采用沟槽结构;在所述功率半导体器件的截面上,元胞包括元胞沟槽、制备于所述元胞沟槽内下部的槽底厚氧层以及支撑于所述槽底厚氧层上的槽内厚氧柱,槽内厚氧柱的顶端位于元胞沟槽槽口的下方;在元胞沟槽内填充有栅极导电多晶硅,所述栅极导电多晶硅支撑在槽底厚氧层上且包覆槽内厚氧柱,栅极导电多晶硅通过栅氧化层与元胞沟槽的侧壁绝缘隔离,栅氧化层与槽底厚氧层接触。

7.所述槽底厚氧层的厚度大于栅氧化层的厚度,所述栅氧化层以及槽底厚氧层均为二氧化硅层。

8.所述槽内厚氧柱以及槽底厚氧层为同一工艺步骤层。

9.在所述元胞区的外圈还设置终端保护区,在半导体衬底的背面设置背面电极结构,利用背面电极结构能使得所述功率半导体器件为igbt器件或mosfet器件。

10.一种能降低米勒电容的功率半导体器件的制备方法,所述制备方法包括如下步骤:步骤1、提供半导体衬底,并在所述半导体衬底的正面进行沟槽刻蚀工艺,以能在

半导体衬底内制备得到所需的元胞沟槽;步骤2、在上述半导体衬底上淀积正面厚氧化层,所述正面厚氧化层填充在元胞沟槽内并覆盖在半导体衬底的正面;步骤3、并上述正面厚氧化层进行处理,以能得到位于元胞沟槽内的厚氧槽内体,所述厚氧槽内体在元胞沟槽内的深度低于元胞沟槽的深度;步骤4、对上述厚氧槽内体进行刻蚀,以能制备得到所需的槽底厚氧层以及支撑于所述槽底厚氧层上的槽内厚氧柱,槽底厚氧层覆盖元胞沟槽下部的侧壁以及元胞沟槽的底壁;步骤5、在上述元胞沟槽内制备栅氧化层,所述栅氧化层覆盖元胞沟槽的侧壁且栅氧化层与槽底厚氧层接触;步骤6、在上述元胞沟槽填充栅极导电多晶硅,栅极导电多晶硅支撑在槽底厚氧层上且包覆槽内厚氧柱,栅极导电多晶硅通过栅氧化层与元胞沟槽的侧壁绝缘隔离。

11.所述槽底厚氧层的厚度大于栅氧化层的厚度,所述栅氧化层以及槽底厚氧层均为二氧化硅层。

12.步骤3中,对步骤2得到的正面厚氧化层进行平坦化,并对平坦化后的正面厚氧化层进行刻蚀,以能得到厚氧槽内体。

13.还包括正面工艺步骤以及背面工艺步骤,通过正面工艺步骤能形成所需的正面结构,利用背面工艺步骤能制备得到背面电极结构,利用背面电极结构能使得所述功率半导体器件为igbt器件或mosfet器件。

14.所述半导体衬底的材料包括硅。

15.本发明的优点:由于槽底厚氧层的厚度大于栅氧化层的厚度,利用槽底厚氧层能增加元胞沟槽内槽底氧化层的厚度,能有助于降低米勒电容;通过槽底厚氧层以及槽内厚氧柱与栅极导电多晶硅配合,能减少栅极导电多晶硅与半导体衬底的重叠面积,能进一步降低米勒电容。

附图说明

16.图1为现有在元胞沟槽内填充掺杂多晶硅后的示意图。

17.图2~图8为本发明具体实施工艺步骤剖视图,其中,图2为本发明半导体衬底的剖视图。

18.图3为本发明制备得到元胞沟槽后的剖视图。

19.图4为本发明制备得到的正面厚氧化层后的示意图。

20.图5为本发明对正面厚氧化层平坦化后的示意图。

21.图6为本发明制备得到厚氧槽内体后的示意图。

22.图7为本发明制备得到槽底厚氧层以及槽内厚氧柱的示意图。

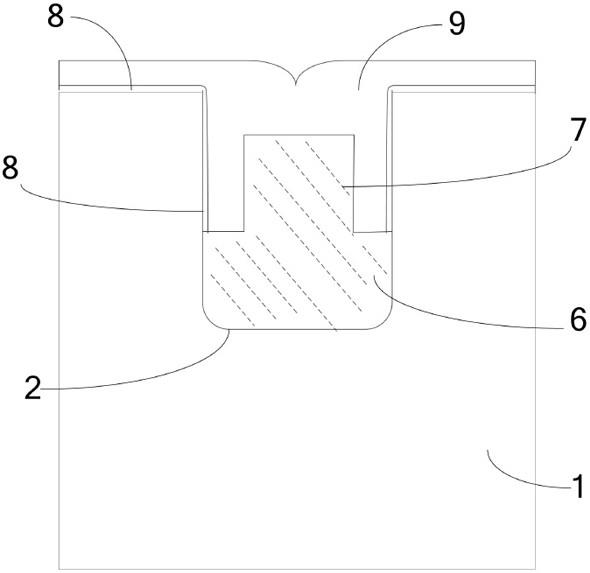

23.图8为本发明填充栅极导电多晶硅后的示意图。

24.附图标记说明:1

‑

半导体衬底、2

‑

元胞沟槽、3

‑

沟槽氧化层、4

‑

掺杂导电多晶硅、5

‑

正面厚氧化层、6

‑

槽底厚氧层、7

‑

槽内厚氧柱、8

‑

栅氧化层、9

‑

栅极导电多晶硅、10

‑

厚氧槽内体。

具体实施方式

25.下面结合具体附图和实施例对本发明作进一步说明。

26.如图1所示,为现有元胞采用沟槽形式的igbt器件或mosfet器件中栅电极的示意图,其中,在半导体衬底1内制备得到元胞沟槽2,元胞沟槽2的槽口位于半导体衬底1的正面,元胞沟槽2的深度小于半导体衬底1的厚度。在元胞沟槽2内通过热氧化等工艺能制备得到沟槽氧化层3,沟槽氧化层3同时覆盖元胞沟槽2的侧壁以及底壁,在元胞沟槽2内填充掺杂导电多晶硅4,掺杂导电多晶硅4通过沟槽氧化层3与元胞沟槽2的侧壁以及底壁绝缘隔离。

27.如图8所示,为了能降低降低米勒电容,提高器件的可靠性,本发明包括半导体衬底1以及设置于所述半导体衬底1中心区的元胞区;所述元胞区内包括若干并联分布的元胞,且元胞采用沟槽结构;在所述功率半导体器件的截面上,元胞包括元胞沟槽2、制备于所述元胞沟槽内下部的槽底厚氧层6以及支撑于所述槽底厚氧层6上的槽内厚氧柱7,槽内厚氧柱7的顶端位于元胞沟槽2槽口的下方;在元胞沟槽2内填充有栅极导电多晶硅9,所述栅极导电多晶硅9支撑在槽底厚氧层6上且包覆槽内厚氧柱7,栅极导电多晶硅9通过栅氧化层8与元胞沟槽2的侧壁绝缘隔离,栅氧化层8与槽底厚氧层6接触。

28.具体地,半导体衬底1的材料可以采用现有常用的材料形式,如可采用硅等,具体材料类型可以根据实际需要选择,此处不再赘述。在半导体衬底1正面的中心区设置元胞区,利用元胞区能形成半导体功率器件的功能区,具体与现有相一致,为本技术领域所熟知,此处不再赘述。具体实施时,元胞区内包括若干元胞,元胞区内的元胞相互并联成一体,元胞采用沟槽结构,元胞以及元胞内元胞沟槽2的具体情况均与现有相一致,此处不再赘述。

29.本发明实施例中,在元胞沟槽2内设置槽底厚氧层6,槽底厚氧层6位于元胞沟槽2的下部,槽底厚氧层6覆盖元胞沟槽2的侧壁以及底壁,槽内厚氧柱7的宽度小于槽底厚氧层6的厚度,槽内厚氧柱7竖直分布于槽底厚氧层6上,即槽内厚氧柱7与元胞沟槽2的侧壁不接触。槽内厚氧柱7的顶端位于元胞沟槽2槽口的下方,即槽底厚氧层6以及槽内厚氧柱7高度之和小于元胞沟槽2的深度。

30.为了能形成功率半导体器件的栅电极,需要在元胞沟槽2内填充栅极导电多晶硅9,栅极导电多晶硅9的具体情况可与掺杂导电多晶硅4相一致,此处不再赘述。当在元胞沟槽2填充栅极导电多晶硅9后,栅极导电多晶硅9的底部支撑在槽底厚氧层6上,且能将槽内厚氧柱7包裹在栅极导电多晶硅9内。栅极导电多晶硅9利用槽底厚氧层6能与元胞沟槽2下部的侧壁以及底壁绝缘隔离。在元胞沟槽2内还设置栅氧化层8,所述栅氧化层8覆盖元胞沟槽2内除与槽底厚氧层6接触外的其余侧壁,栅氧化层8与槽底厚氧层6接触,即利用栅氧化层8以及槽底厚氧层6能实现对元胞沟槽2的侧壁、底壁全部覆盖,确保栅极导电多晶硅9能与半导体衬底1间的绝缘隔离。

31.进一步地,所述槽底厚氧层6的厚度大于栅氧化层8的厚度,所述栅氧化层8以及槽底厚氧层6均为二氧化硅层。

32.本发明实施例中,槽底厚氧层6的厚度大于栅氧化层8的厚度,所述槽内厚氧柱7以

及槽底厚氧层6为同一工艺步骤层。栅氧化层8可以通过热氧化等工艺方式制备得到,具体与现有相一致,具体为本技术领域所熟知,此处不再赘述。栅氧化层8的厚度等情况可与图1中沟槽氧化层3等情况相一致,具体为本技术领域人员所熟知,此处不再赘述。利用元胞沟槽2以及位于所述元胞沟槽2内栅极导电多晶硅9形成栅电极的方式与现有相一致,具体为本技术领域人员所熟知,此处不再赘述。

33.具体实施时,功率半导体器件的弥勒电容取决于多个参数因子,但主要取决于栅极导电多晶硅9与集电极重叠的面积,重叠面积越小,那么弥勒电容越小,栅极导电多晶硅9和半导体衬底1之间氧化层的厚度越厚,那么,弥勒电容也相对较小。由于槽底厚氧层6的厚度大于栅氧化层8的厚度,因此,本发明利用槽底厚氧层6能增加元胞沟槽2内槽底氧化层的厚度,能有助于降低米勒电容;通过槽底厚氧层6以及槽内厚氧柱7与栅极导电多晶硅9配合,能减少栅极导电多晶硅9与半导体衬底1的重叠面积,能进一步降低的弥勒电容。

34.进一步地,在所述元胞区的外圈还设置终端保护区,在半导体衬底1的背面设置背面电极结构,利用背面电极结构能使得所述功率半导体器件为igbt器件或mosfet器件。

35.本发明实施例中,在元胞区的外圈设置终端保护区,利用终端保护区能对元胞区进行保护,提高元胞区的耐压,终端保护区与元胞区间的具体关系等均与现有相一致,具体为本技术领域人员所熟知,此处不再赘述。一般地,元胞区位于半导体衬底1的正面,即在半导体衬底1正面设置正面结构,通过正面结构能形成半导体功率器件的源电极以及集电极,正面结构与元胞沟槽2以及栅极导电多晶硅9配合形成集电极的方式均可与现有相一致,此外,形成源电极的具体形式也可以根据实际需要选择,具体为本技术领域人员所熟知,此处不再赘述。

36.当然,在半导体衬底1的背面还需要设置背面电极结构,利用背面电极结构能使得所述功率半导体器件为igbt器件或mosfet器件。背面电极结构的具体形式,以及利用背面电极结构配合形成igbt器件或mosfet器件的具体形式均与现有相一致,具体为本技术领域人员所熟知,此处不再赘述。

37.如图2~图8所示,对上述功率半导体器件,本发明能降低米勒电容的功率半导体器件的制备方法,具体地,所述制备方法包括如下步骤:步骤1、提供半导体衬底1,并在所述半导体衬底1的正面进行沟槽刻蚀工艺,以能在半导体衬底1内制备得到所需的元胞沟槽2;如图2所示,为半导体衬底1的示意图,半导体衬底1的具体情况可以根据实际需要选择,此处不再赘述。对提供的半导体衬底1,采用本技术领域常用的技术手段能制备元胞沟槽2,如图3所示。具体制备得到元胞沟槽2的工艺过程等均为本技术领域人员所熟知,元胞沟槽2的宽度以及深度等可根据实际需要选择,此处不再赘述。

38.步骤2、在上述半导体衬底1上淀积正面厚氧化层5,所述正面厚氧化层5填充在元胞沟槽2内并覆盖在半导体衬底1的正面;具体地,正面厚氧化层5可以为二氧化硅,正面厚氧化层5可以通过沉积等常用的工艺制备得到,具体为本技术领域人员所熟知,此处不再赘述。淀积正面厚氧化层5后,正面厚氧化层5不仅填充在元胞沟槽2内,还覆盖在半导体衬底1的正面,如图4所示。

39.步骤3、并上述正面厚氧化层5进行处理,以能得到位于元胞沟槽2内的厚氧槽内体10,所述厚氧槽内体10在元胞沟槽2内的深度低于元胞沟槽2的深度;

具体地,对步骤2得到的正面厚氧化层5进行平坦化,并对平坦化后的正面厚氧化层5进行刻蚀,以能得到厚氧槽内体。其中,平坦化时,可以采用cmp(chemical mechanical polishing)工艺,在平坦化后,在半导体衬底1的正面还保留一层较为薄膜,如图5所示。

40.在平坦化后,通过各项异性刻蚀和少量的各项同性刻蚀,从而能将半导体衬底1表面的正面厚氧化层5去除,从而在元胞沟槽2内形成厚氧槽内体10,如图6所示。具体通过各项异性刻蚀和少量的各项同性刻蚀,并得到厚氧槽内体10的具体工艺过程可以根据需要选择,具体为本技术领域人员所熟知,此处不再赘述。厚氧槽内体10的高度小于元胞沟槽2的深度。

41.步骤4、对上述厚氧槽内体10进行刻蚀,以能制备得到所需的槽底厚氧层6以及支撑于所述槽底厚氧层6上的槽内厚氧柱7,槽底厚氧层6覆盖元胞沟槽2下部的侧壁以及元胞沟槽2的底壁;具体地,对厚氧槽内体10刻蚀时,利用光刻版将厚氧槽内体10的中间区域遮挡保护,从而在刻蚀时,能形成槽底厚氧层6以及槽内厚氧柱7,如图7所示。槽底厚氧层6在元胞沟槽2内的深度以及槽内厚氧柱7在槽底厚氧层6上的高度均可以根据实际需要刻蚀得到,具体为本技术领域人员所熟知,此处不再赘述。槽底厚氧层6以及槽内厚氧柱7的具体情况,可以参考上述说明,此处不再赘述。

42.步骤5、在上述元胞沟槽2内制备栅氧化层8,所述栅氧化层8覆盖元胞沟槽2的侧壁且栅氧化层8与槽底厚氧层6接触;具体地,热氧化等常用工艺步骤能在元胞沟槽2内制备得到栅氧化层8,栅氧化层8覆盖元胞沟槽2的侧壁,即覆盖元胞沟槽2内除被槽底厚氧层6覆盖的侧壁,当然,在具体实施时,栅氧化层8还会同时覆盖半导体衬底1的正面。

43.步骤6、在上述元胞沟槽2填充栅极导电多晶硅9,栅极导电多晶硅9支撑在槽底厚氧层6上且包覆槽内厚氧柱7,栅极导电多晶硅9通过栅氧化层8与元胞沟槽2的侧壁绝缘隔离。

44.具体地,采用本技术领域常用的技术手段能制备得到栅极导电多晶硅9,栅极导电多晶硅9会填充在元胞沟槽2内,也会覆盖在半导体衬底1的正面,如图8所示。

45.此外,还包括正面工艺步骤以及背面工艺步骤,通过正面工艺步骤能形成所需的正面结构,利用背面工艺步骤能制备得到背面电极结构,利用背面电极结构能使得所述功率半导体器件为igbt器件或mosfet器件。

46.本发明实施例中,正面工艺步骤、背面工艺步骤的具体情况可以根据实际选择,具体以实际需要形成的正面结构以及背面电极结构为准,具体为本技术领域人员所熟知,此处不再赘述。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。