1.本发明涉及形成半导体结构,尤其涉及抵消这一形成期间的半导体材料损耗。

背景技术:

2.为了在先进的互补金属氧化物半导体(cmos)器件中成功实现鳍式fet架构,特别是用于5nm及以后的技术节点,提出了全环栅极(gate

‑

all

‑

around,gaa)场效应晶体管(fet)架构。这一gaa fet通常可以基于一个或多个纳米线或纳米片。该设计可能相对简单(诸如用于纳米线fet或纳米片fet),但也可能涉及更多(例如用于叉片fet或互补fet(cfet))。ryckaert等人提出了从纳米片到叉片再到cfet的5nm以下cmos技术缩放的进化途径(ryckaert,j.等人在2019年ieee国际电子设备会议(iedm)发表的enabling sub

‑

5nm cmos technology scaling thinner and taller(使压5纳米cmos技术能够缩放得更薄更高),ieee 2019.p.29.4.1

‑

29.4.4)。

3.垂直堆叠的gaa si纳米线fet已由例如mertens等人展示:(mertens,h.等人在2017年ieee国际电子设备会议(iedm)发表的vertically stacked gate

‑

all

‑

around si nanowire transistors:key process optimizations and ring oscillator demonstration(垂直堆叠的全环栅极si纳米线晶体管:关键工艺优化和环形振荡器展示),ieee,2017.p.37.4.1

‑

37.4.4.)。

4.barraud等人也阐述了堆叠式gaa si纳米线和纳米片fet(barraud等人在2017年ieee国际电子设备会议(iedm)发表的performance and design considerations for gate

‑

all

‑

around stacked

‑

nanowires fets(全环栅极堆叠纳米线fet的性能和设计考虑),ieee,2017.p.29.2.1

‑

29.2.4.)。

5.然而,在这些gaa fet变得与商业相关之前,仍需要进一步的改进。

技术实现要素:

6.本发明的目标是提供用于形成半导体结构的好方法。本发明的另一目标是提供与该方法相关联的好用途和半导体结构。该目标通过根据本发明的方法、半导体结构和用途来达成。

7.本发明的实施例的优点是当在牺牲层中相对于半导体层形成凹部时,可补偿半导体材料损耗(例如,半导体层的远端薄化)。本发明的实施例的另一优点是半导体层的远端薄化可被(部分)还原或进一步增加。

8.本发明的实施例的优点是可以减小对半导体层的访问电阻。

9.本发明的实施例的优点是这些实施例能适用于各种半导体结构,包括gaa fet,诸如纳米线、纳米片、叉片或互补cfet。

10.本发明的实施例的优点是这些实施例能以相对简单且经济的方式执行。

11.在第一方面,本发明涉及一种用于形成半导体结构的方法,包括:(a)提供结构,该结构包括(i)衬底、(ii)该衬底上的层堆叠、以及(iii)穿过该层堆叠的沟槽,该层堆叠包括

半导体材料的至少一个半导体层以及在半导体层下的至少一个牺牲层;(b)通过蚀刻由该沟槽暴露的部分牺牲层来在该层堆叠中形成凹部,该蚀刻使该牺牲层相对于该半导体层优先被蚀刻;以及(c)在半导体层的由该沟槽暴露的表面上外延地生长半导体材料的衬里。

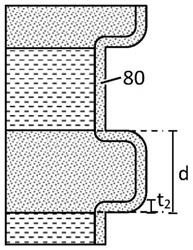

12.如果在不采用步骤c的方法中步骤b可以相对于半导体层完全选择性地执行,则可以在凹部中形成内间隔件(参见步骤d)并获得理想的结构,如图1中示意性地描绘的;后者示出半导体结构(10),包括在衬底(20)上的交替的牺牲层(32)和半导体层(31)的层堆叠(30)、贯穿该层堆叠(30)的源极/漏极结构(41)、在层堆叠(30)上的包括伪栅极氧化物(51)和伪栅极(52)的伪栅极区域(50)、侧置于该伪栅极区域(50)的栅极间隔件(60)以及邻接该牺牲层(32)的内间隔件(71)。然而,在本发明内观察到在现实中通常获得如图2示意性地描绘的结构(10),其中内间隔件(71)部分地延伸到半导体层(31)中并且每一个半导体层(31)的远端厚度(d)减小。这对于参见上文的barraud等人(例如在其中图2(3)中清楚可见的)和mertens等人(在例如图17(c)中稍微较不明显,但被确认是如此)亦如此;即使在这些公开内容中没有讨论该问题。这一半导体层远端薄化因此导致每一半导体层(31)与源极/漏极结构(41)之间的接触区域减小,从而导致寄生电阻增大,并由此对半导体层(31)的访问电阻增大。

13.对半导体层远端薄化的这一观察目前可以追溯到以下事实:这一完全选择性实际上通常无法实现并因此不可避免地发生一些半导体材料损耗。在没有理论限制的情况下,这一非期望损耗可具有各种原因,诸如以下原因中的一者或多者:(i)块状半导体材料(例如,si)和块状牺牲材料(例如,sige)之间的有限的蚀刻选择性;(ii)在半导体/牺牲层界面处的(块状)半导体和牺牲材料的混合;以及(iii)半导体层表面的氧化(例如,自然氧化物形成)。然而,不管是否是因为缺少这样的材料之间的选择性和/或因为某一界面或表面效应,蚀刻都导致发生一些半导体材料损耗,由此使凹部(70)部分延伸到半导体层(31)中并由此薄化每一半导体层(31)的远端厚度(d)。这在图3中的透射电子显微镜(tem)图像中也很明显,并在图4中进一步进行了示意性描绘。如上所示,在内间隔件(71)(参见步骤d)和源极/漏极结构(41)(参见步骤e)形成后,每一半导体层(31)和源极/漏极结构(41)之间的接触区域然后因此被减小(参见图2),从而导致增大的寄生电阻并由此增大的对半导体层(31)的访问电阻。

14.为了解决上述问题,在本发明中设想在半导体层(31)上(且可任选地在牺牲材料上)形成半导体材料的衬里(80)(步骤c),如图5中示意性地描绘的。由此,步骤b的半导体材料损耗可以(至少部分地)被补偿并且半导体层(31)的远端厚度(d)可被(至少部分地)还原。这也可在图6中看到,图6示出了不具有(左图)和具有(右图)半导体材料衬里(80)的半导体结构(10)的tem图像。尽管如此衬里(80)在其中并非与半导体层(31)(以及牺牲层(32))特别区分开的,但左图半导体结构(10)中的半导体材料损耗在右图被大大减少是清楚的。更具体地,如图6所示,远端边缘与半导体层(31)中间附件的边缘之间的高度差对于左侧半导体结构(10)测得约1.1纳米且对于右侧半导体结构(10)测得小于0.5纳米;即,远端厚度(d)的减少分别计为约2.2纳米和小于1纳米。

15.在第二方面,本发明涉及一种半导体结构,包括:(i)衬底;(ii)该衬底上的层堆叠,该层堆叠包括半导体材料的至少一个半导体层以及在半导体层下的至少一个辅助层;(iii)穿过该层堆叠的沟槽;(iv)相对于该半导体层的凹部,该凹部邻接该辅助层;以及(v)

半导体材料的衬里,该衬里相对于该沟槽衬在该半导体层以及可任选的辅助层上。

16.在第三方面,本发明涉及如在第二方面的任一实施例中限定的半导体结构中的半导体材料的衬里的用途,该用途用于减小对半导体层的访问电阻。

17.在所附独立和从属权利要求中阐述了本发明的特定和优选方面。来自从属权利要求的特征可以与独立权利要求的特征以及与其他从属权利要求的特征适当地结合,而不仅仅是如在权利要求中明确阐述的那样。

18.尽管本领域中的设备在不断地改进、改变和发展,但是相信本发明概念代表了包括偏离先前实践的充分新颖且独创的进步,从而提供了更高效、稳定和可靠的具有此性质的设备。

19.从下面结合附图的详细描述中,本发明的上述和其他特性、特征和优点将变得显而易见,附图通过示例的方式解说了本发明的原理。给出本描述仅仅是出于解说的目的,而并不限制本发明的范围。下文引用的参考图对附图进行参考。

附图说明

20.图1示意性地描绘了理想化半导体结构,该半导体结构可以如图1中示意性地描绘的那样获得。然而,在本发明中观察到在现实中是如图2示意性地描绘的结构。

21.图2示意性地描绘了图1的半导体结构的更现实的版本,该版本示出非期望半导体材料损耗的结果。

22.图3示出了透射电子显微镜(tem)图像,这些图像示出了非期望半导体材料损耗的问题。

23.图4进一步示意性地描绘了非期望半导体材料损耗的问题。

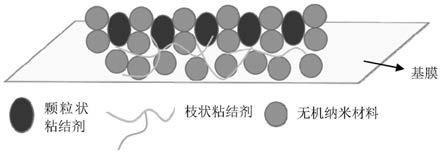

24.图5示意性地描绘了提供根据本发明的实施例的用于补偿非期望半导体材料损耗的衬里。

25.图6示出了透射电子显微镜(tem)图像,这些图像示出了不使用(左图)和使用(右图)根据本发明的实施例的衬里之间的区别。

26.图7到图13示意性地描绘了根据本发明的示例性实施例的说明性工艺流程的不同阶段处的半导体结构。

27.在不同的附图中,相同的附图标记指代相同或相似的元素。

具体实施方式

28.将就具体实施例并且参考特定附图来描述本发明,但是本发明不限于此而仅由权利要求书来限定。所描述的附图仅是示意性的且是非限制性的。在附图中,出于说明性目的,要素中的一些要素的尺寸可被放大且未按比例绘制。尺度和相对尺度不对应于对本发明的实施的实际减少。

29.此外,说明书和权利要求中的术语第一、第二和第三等用于区别类似的元件,而不一定用于描述时间、空间、排列或任何其他方式的先后顺序。应理解,如此使用的术语在适当的情况下是可互换的,并且本文中所描述的本发明的实施例能够以与本文中所描述或解说的不同的顺序来进行操作。

30.此外,说明书和权利要求书中的术语顶部、底部、上方、下方等被用于描述性的目

的,而不一定用于描述相对位置。应该理解,如此使用的这些术语在合适情况下可以与它们的反义词互换,并且本文描述的本发明的实施例能够以除了本文描述或说明的之外的其他取向来操作。

31.要注意,权利要求中使用的术语“包括”不应被解释为限定于其后列出的装置;它并不排除其他要素或步骤。因此,该术语应被解释为指定如所提到的所陈述的特征、整数、步骤或组件的存在,但不排除一个或多个其他特征、整数、步骤或组件、或其群组的存在或添加。因此,术语“包括”涵盖了仅存在该陈述特征的情况以及这些特征和一个或多个其他特征存在的情况。因此,表述“一种包括装置a和b的设备”的范围不应当被解释为局限于仅由组件a和b构成的设备。这意味着对于本发明,设备的仅有的相关组件是a和b。

32.贯穿本说明书对“一个实施例”或“实施例”的引用意指结合该实施例所描述的特定的特征、结构或特性被包括在本发明的至少一个实施例中。因此,短语“在一个实施例中”或“在实施例中”贯穿本说明书在各个地方的出现并不一定全部指代同一实施例,而是可以指代同一实施例。此外,在一个或多个实施例中,如通过本公开将对本领域普通技术人员显而易见的,特定的特征、结构或特性能以任何合适的方式进行组合。

33.类似地,应当理解,在本发明的示例性实施例的描述中,出于精简本公开和辅助理解各发明性方面中的一个或多个发明性方面的目的,本发明的各个特征有时被一起编组在单个实施例、附图或其描述中。然而,该公开方法不应被解释为反映要求保护的发明要求比每一项权利要求中明确记载的特征更多的特征的意图。相反,如所附权利要求所反映,发明性方面存在于比单个前述公开的实施例的全部特征更少的特征中。因此,具体实施方式之后所附的权利要求由此被明确纳入本具体实施方式中,其中每一项权利要求本身代表本发明的单独实施例。

34.此外,尽管本文中所描述的一些实施例包括其他实施例中所包括的一些特征但不包括其他实施例中所包括的其他特征,但是如本领域技术人员将理解的那样,不同实施例的特征的组合旨在落在本发明的范围内,并且形成不同实施例。例如,在所附的权利要求书中,所要求保护的实施例中的任何实施例均能以任何组合来使用。

35.在本文中所提供的描述中,阐述了众多具体细节。然而应理解,在没有这些具体细节的情况下也可实践本发明的实施例。在其他实例中,公知的方法、结构和技术未被详细示出,以免混淆对本描述的理解。

36.将对晶体管作出参考。这些是具有第一主端子(例如,源极或集电极)、第二主端子(例如,漏极或发射极)和控制端子(例如,栅极或基极)的器件,用于控制第一和第二主端子之间的电荷流动。

37.单独提供以下各项以便于理解本发明。

38.如此处所使用的,除非另外指明,否则

‘

源极/漏极结构’被理解为

‘

源极结构和/或漏极结构’。在各实施例中,源极结构和漏极结构可以是相当的(例如,不可区分的),并且对它们的命名可以取决于在最终的半导体结构中施加在它们之间的相对电压差。

39.如此处所使用的,除非另外指明,否则当说相对于第二实体(例如,第二层或材料)选择性地移除(例如,蚀刻)第一实体(例如,第一层或材料)时,这意味着比第二实体更快地移除第一实体。优选地,移除(例如,蚀刻)工艺将比第二实体至少快两倍或更优选地至少快五倍、再更优选地至少快十倍地移除第一实体。在一些优选实施例中,移除工艺可以基本上

不移除第二实体。

40.如此处所使用的,除非另外指明,否则

‘

伪’实体(例如,伪栅极区域)是通常被用作将在半导体加工的某一稍后阶段被功能性实体替代的占位体的非功能性实体。例如,伪栅极区域可以在替换金属栅极工艺期间被功能性栅极区域替代。

‘

伪’实体可被替代地称为

‘

牺牲’实体。

41.在第一方面,本发明涉及一种用于形成半导体结构的方法,包括:(a)提供结构,该结构包括(i)衬底、(ii)该衬底上的层堆叠、以及(iii)穿过该层堆叠的沟槽,该层堆叠包括半导体材料的至少一个半导体层以及在半导体层下的至少一个牺牲层;(b)通过蚀刻由该沟槽暴露的部分牺牲层来在该层堆叠中形成凹部,该蚀刻使该牺牲层相对于该半导体层优先被蚀刻;以及(c)在半导体层的由该沟槽暴露的表面上外延地生长半导体材料的衬里。

42.在各实施例中,半导体结构可包括或者可以是全环栅极(gaa)场效应晶体管(fet),诸如纳米线、纳米片、叉片或互补场效应晶体管。在各实施例中,该方法由此可用于形成全环栅极场效应晶体管,优选纳米线、纳米片、叉片或互补场效应晶体管。叉片fet例如已经由weckx等人(weckx等人在2019年ieee国际电子设备会议(iedm)发表的novel forksheet device architecture as ultimate logic scaling device towards 2nm(新颖的forksheet器件架构作为朝2nm方向发展的终极逻辑缩放器件),ieee,2019.p.36.5.1

‑

36.5.4.)描述,该文献通过引用纳入与此。

43.在各实施例中,衬底可以是半导体结构,例如iv簇衬底(例如si、ge或sige)、iii

‑

v簇衬底或绝缘体上半导体衬底。

44.至少一个半导体层是半导体材料层;即,它可包括半导体材料或由半导体材料构成。在一些实施例中,块状半导体层基本上可包括(例如,由其构成)半导体材料,而表面或界面包括(例如,由其构成)半导体材料的衍生物(例如,天然氧化物或混合材料)。在各实施例中,半导体材料可以是iv簇材料(例如si、ge或sige)或iii

‑

v簇材料(例如alxga1

‑

xas、gan、inas或gaxin1

‑

xp)。在各实施例中,半导体层可以是纳米线或纳米片,优选纳米片。

45.至少一个牺牲层通常是牺牲材料层;即,它可包括牺牲材料或由牺牲材料构成。在各实施例中,牺牲层同样可以是半导体材料(在此情形中它可被替代地称为

‘

牺牲半导体材料’)。在各实施例中,牺牲层可以是纳米线或纳米片,优选纳米片。命名

‘

半导体层/材料’和

‘

牺牲层/材料’由此指代其在该方法中的功能。更具体地,半导体层通常在该方法中被维持(例如,为了在最终半导体结构中扮演起作用角色),而牺牲层预期在该方法的过程中被牺牲。由此,半导体层/材料也可被处称为

‘

起作用半导体层/材料’(例如,与

‘

牺牲半导体层/材料’相反)。尽管如此,牺牲材料和半导体材料可以(尽管不必)从相同的材料列表中选择;例如,在一个实施例中,sige可以是牺牲材料,而在不同实施例中,sige可以是半导体材料。

46.在各实施例中,层堆叠可包括与牺牲层交替的多个半导体层。在优选实施例中,层堆叠的至少底层可以是牺牲层之一。在各实施例中,层堆叠的顶层可以是半导体层之一或牺牲层之一。

47.在各实施例中,半导体结构可进一步包括:(vi)层堆叠上方(例如,直接在上面)的伪栅极区域。在各实施例中,伪栅极区域可包括伪栅极氧化物(例如,sio2)和伪栅极(例如,多晶硅)。在各实施例中,半导体结构可进一步包括:(vii)侧置于伪栅极区域的栅极间隔件(例如,sicon或sibcn)。

48.注意,尽管牺牲层在步骤b中相对于半导体层优先被蚀刻,可实现的蚀刻选择性通常不可避免是有限的(即,完全选择性无法被实现),以使得一些半导体材料损耗通常是不可避免的(参见上文)。由此,半导体层的一部分仍将在步骤b中被蚀刻。

49.鉴于该有限的蚀刻选择性,步骤c然后允许通过在半导体层的由沟槽暴露的表面上外延地生长半导体材料衬里来(至少部分地)还原半导体材料损耗。在一些实施例中,可以相对于牺牲层的表面选择性地在半导体层表面上外延地生长衬里。在其他实施例中,步骤c可进一步包括在牺牲层的由沟槽暴露的表面上生长衬里(即,该衬里可以在半导体层表面和牺牲层表面这两者上外延地生长)。在牺牲层表面上也具有衬里可具有非期望效果,这表现在该衬里部分通常将保留在最终半导体结构中并且可(例如,通过降低内间隔件的有效性;参见下文)来增大其中的寄生电容。由此,在可能的情况下,可优选选择性地只在半导体层表面上生长衬里。然而,对于半导体层和牺牲层的某些组合(例如,si和sige),这一生长选择性可以是挑战性的或甚至是不可能实现的。然而,尽管然后计及衬里对最终半导体结构中的例如寄生电容的影响可以是合乎需要的,但在半导体层表面和牺牲层表面两者上生长衬里仍然产生有益的结果。例如,这可包括通过对衬里厚度的适当选择来在良好访问电阻和良好寄生电容之间取得平衡;即,足够厚以(例如,通过与源极/漏极结构的更大接触区域)充分增大访问电阻,但也足够薄以极度地增大寄生电容。

50.在各实施例中,在步骤c中生长的衬里可具有以下厚度:3纳米或更小,优选2.5纳米或更小,更优选2纳米或更小,再更优选1.5纳米或更小,诸如1.2纳米或更小。在各实施例中,在步骤c中生长的衬里可具有至少0.5纳米,再更优选至少1纳米的厚度。衬里的厚度可被有利地选择以至少部分地补偿步骤b中的半导体材料损耗,但还可计及诸如它对寄生电容的影响(参见上文)等其他因素。为此,衬里厚度(图5中的t2)可等于(即,完全补偿半导体层的远端厚度薄化)半导体材料损耗(图4中的t1),或者它可以更小(即,部分补偿)或更大(即,过度补偿)。

51.在各实施例中,该方法可包括步骤c之后的附加步骤d:(d)用介电材料填充凹部,由此形成内间隔件(可被替代地称为

‘

内部间隔件’)。内间隔件通常有利地用于减小最终半导体结构中的寄生电容(例如,栅极区域与源极/漏极结构之间;参见下文)。

52.在各实施例中,该方法可包括步骤d之后的附加步骤e:(e)在沟槽中形成源极/漏极结构(例如,sige:b或si:p)。在各实施例中,在沟槽中形成源极/漏极结构可包括在构造中外延地生长该源极/漏极结构。该源极/漏极结构(例如,源极/漏极接触部)通常有利地用于与最终半导体结构的半导体层的源极/漏极区域接触。

53.在各实施例中,该方法可包括附加步骤f:(f)移除牺牲层。在各实施例中,步骤f可以在步骤d后,优选在步骤e后执行。在各实施例中,移除牺牲层可以相对于半导体层和衬里优先(例如,选择性地)执行,优选相对于半导体层、衬里和内间隔件优先执行。例如,移除牺牲层可相对于半导体层、衬里、内间隔件和源极/漏极结构优先执行。通常获得其中移除牺牲层的开口。尽管如此,如前,相对于半导体层和衬里移除牺牲层的完全选择性通常无法被实现,以使得(半导体层和/或衬里的)一些半导体材料一般也仍然将在步骤f期间被移除。例如,在衬里与牺牲层接触的情况下,最多约1纳米的衬里厚度可以在步骤f期间损耗。对于这些衬里区域,该衬里的厚度在步骤f后可以是2纳米或更小,优选1.5纳米或更小,更优选1.2纳米或更小,再优选1纳米或更小,最优选0.8纳米,或更小(诸如被完全移除)。在衬里接

触牺牲层的地方(部分地)移除衬里可以是有利的,因为还对寄生电容产生最负面的影响且同时对访问电阻改进贡献较少的通常是这些衬里部分。

54.在各实施例中,步骤f可进一步包括(例如,在移除牺牲层之前或与之同时)移除伪栅极区域。步骤f还可被称为半导体层释放步骤(例如,纳米线或纳米片释放)。

55.在各实施例中,该方法可包括步骤f之后的附加步骤g:(g)在已在步骤f中移除牺牲层的地方形成栅极区域(例如,功能性栅极区域)。步骤g由此可包括在步骤f后获得的开口中形成栅极区域。在各实施例中,形成该栅极区域可包括形成栅极电介质(例如,高k电介质,例如hfo2)、功函数金属(例如tin、tial或tan)和栅极金属(例如w、co或ru)。在各实施例中,栅极区域可以是全环栅极栅极区域。替代金属栅极(rmg)工艺例如可用于执行步骤f和g。

56.在各实施例中,第一方面的任何实施例的任何特征可以独立地如针对任何其他方面的任何实施例相对应地描述的那样。

57.在第二方面,本发明涉及一种半导体结构,包括:(i)衬底;(ii)该衬底上的层堆叠,该层堆叠包括半导体材料的至少一个半导体层以及在半导体层下的至少一个辅助层;(iii)穿过该层堆叠的沟槽;(iv)相对于该半导体层的凹部,该凹部邻接该辅助层;以及(v)半导体材料的衬里,该衬里相对于该沟槽衬在该半导体层以及可任选的辅助层上。

58.第二方面的实施例由此对应于可以在步骤c

‑

g中的任一步骤后获得半导体结构。

59.在各实施例中,半导体结构可进一步包括:(vi)层堆叠上方(例如,直接在上面)的伪栅极区域。在各实施例中,伪栅极区域可包括伪栅极氧化物(例如,sio2)和伪栅极(例如,多晶硅)。在各实施例中,半导体结构可进一步包括:(vii)侧置于伪栅极区域的栅极间隔件(例如,sicon或sibcn)。

60.在各实施例中,辅助层可包括牺牲层、开口或栅极区域。

61.在各实施例中,凹部可包括内间隔件。

62.在各实施例中,沟槽可包括源极/漏极结构。

63.在各实施例中,第二方面的任何实施例的任何特征可以独立地如针对任何其他方面的任何实施例相对应地描述的那样。

64.在第三方面,本发明涉及如在第二方面的任一实施例中限定的半导体结构中的半导体材料的衬里的用途,该用途用于减小对半导体层的访问电阻。

65.在各实施例中,第三方面的任何实施例的任何特征可以独立地如针对任何其他方面的任何实施例相对应地描述的那样。

66.现在将通过本发明的若干实施例的详细描述来描述本发明。显然,根据本领域技术人员的知识能够配置本发明的其他实施例而不背离本发明的真正技术示教,本发明仅受限于所附权利要求书的各条款。

67.作为本发明的实施例的示例,一种用于形成全环栅极场效应晶体管(例如,纳米线、纳米片、叉片或互补场效应晶体管)的说明性工艺流程在图7到图13中描绘并且在下文中描述。

68.现在参照图7。提供了半导体结构(10),包括衬底(20)(例如,硅晶片)上的交替的牺牲层(32)(例如,sige,诸如sige纳米线或纳米片)和半导体层(31)(例如,si,诸如si纳米线或纳米片)的层堆叠(30)。该半导体结构(10)进一步包括向下穿过层堆叠(30)至衬底

(20)的一个或多个沟槽(40);层堆叠(30)上方的一个或多个伪栅极区域(50)(例如,二氧化硅伪栅极氧化物(51)和多晶硅伪栅极(52));以及侧置于伪栅极区域(50)的栅极间隔件(例如,sicon或sibcn)。

69.现在参照图8。通过蚀刻牺牲层(32)的由沟槽(40)暴露的部分来在层堆叠(30)中形成一个或多个凹部(70)。相对于半导体层(31)优先蚀刻牺牲层(32),但该选择性不可避免地是不完全的(参见上文),以使得一些半导体材料损耗(以及可能的衬底(20)材料损耗)也一定会发生(参见图3、图4和图6)。

70.现在参照图9。为了补偿半导体材料损耗,在半导体层(31)以及可任选的牺牲层(32)和/或衬底(20)的由沟槽(40)暴露的表面上外延地生长半导体材料(例如,si)的衬里(80)。例如,衬里(80)可以衬在沟槽(40)的整个底部上并向上延伸至栅极间隔件(60)。取决于期望的结果,衬里(80)可具有小于、等于或大于半导体材料损耗(图4中的t1)的厚度(图5中的t2);即,远端厚度(d)的薄化可以分别被部分地、完全(参见图5)或过度补偿。例如,在衬里(80)衬在半导体层(31)和牺牲层(32)这两者上的情况下,更厚的衬里(80)通常将导致对半导体层(31)的更低的访问电阻,但也将导致更高的寄生电容。这两者之间的平衡由此可通过选择衬里(80)的适当厚度(t2)来寻求。

71.现在参照图10。用于介电材料填充凹部(70),由此形成内间隔件(71)。

72.现在参照图11。填充沟槽(40)(例如,通过sige:b或si:p的外延式生长)以形成源极/漏极结构(41)。

73.现在参照图12。通过移除伪栅极区域(50)和牺牲层(32)来释放半导体层(31)。

74.现在参照图13。在先前移除牺牲层(32)和伪栅极区域(50)的开口(90)中形成功能性替代栅极区域,该功能性替代栅极区域包括栅极介电质(例如,hfo2)、功函数金属堆叠(例如,tin、tial或tan)和金属栅极填充物(例如,w、co或ru)。

75.可以理解,尽管本文针对根据本发明的设备讨论了优选实施例、具体结构和配置以及材料,但是可做出形式和细节上的各种改变或修改而不背离本发明的范围和技术教导。例如,上面给出的任何分子式仅代表可被使用的步骤。可从框图中增删功能,且可在功能框之间互换操作。在本发明范围内可对所述方法增删步骤。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。