一种w波段合成功率放大器

技术领域

1.本发明涉及功放设备技术领域,具体涉及一种w波段合成功率放大器。

背景技术:

2.功放主要功能是将发射激励信号放大到额定的功率输出。由于考虑功率、阻抗、失真、动态以及不同的使用范围和控制调节功能,不同的功放在内部的信号处理、线路设计和生产工艺上也各不相同。

3.现有的w频段功放存在单片输出功率低、稳定性较差、效率低等问题。

4.鉴于上述缺陷,本发明创作者经过长时间的研究和实践终于获得了本发明。

技术实现要素:

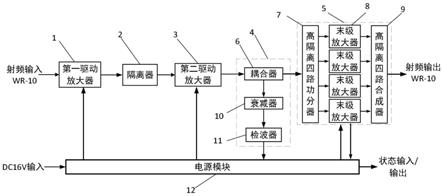

5.为解决上述技术缺陷,本发明采用的技术方案在于,提供一种w波段合成功率放大器,包括第一驱动放大器、隔离器、第二驱动放大器、功率监测模块、末级合成放大模组和电源模块;所述第一驱动放大器通过所述隔离器与所述第二驱动放大器连接,所述第二驱动放大器通过所述功率监测模块与所述末级合成放大模组连接,所述电源模块与所述第一驱动放大器、所述第二驱动放大器、所述功率监测模块、所述末级合成放大模组连接。

6.较佳的,所述功率监测模块包括耦合器、衰减器和检波器,所述耦合器设置在所述第二驱动放大器、所述末级四路合成放大模组之间,所述耦合器通过所述衰减器与所述检波器连接,所述功率监测模块的输入端为所述耦合器的输入端,所述功率监测模块的输出端为所述耦合器的直通端。

7.较佳的,所述末级合成放大模组包括隔离功分器、若干末级放大器和隔离合成器,所述隔离功分器分别通过各所述末级放大器和所述隔离合成器连接。

8.较佳的,所述第一驱动放大器和所述第二驱动放大器包括电源部和放大部,所述电源部包括电源管理芯片、正压dcdc芯片、第一正压ldo芯片,所述放大部包括放大器芯片;所述电源管理芯片的第17和第18引脚和所述放大器芯片的漏极之间依次串联第一电阻、并联第二电容,所述电源管理芯片的第16引脚和所述放大器芯片的栅极并联第二电容;所述正压dcdc芯片的第1引脚和所述第一正压ldo芯片的第6、7、8引脚之间依次串联第三电容、并联第一二极管、串联第一电感、并联第二电阻和并联第四电容;所述第一正压ldo芯片的第1、2、3引脚和所述电源管理芯片的第5、9引脚之间依次并联第五电容、并联第三电阻、并联第六电容。

9.较佳的,所述末级合成放大模组设置有调制解调电路,所述调制解调电路包括nmos栅极驱动芯片和nmos管,所述nmos栅极驱动芯片的1管脚连接dc15v,所述nmos栅极驱动芯片的3管脚连接外部提供的lvttl控制电平信号,所述nmos栅极驱动芯片的4管脚和6管脚之间串联第七电容,所述nmos栅极驱动芯片的4管脚和所述nmos管的2管脚之间依次并联第八电容、并联第二电感,所述nmos栅极驱动芯片的5管脚和所述nmos管的1管脚之间串联第四电阻。

10.较佳的,所述电源模块的主电路包括负压dcdc芯片、负压ldo芯片、第二正压ldo芯片和第一pmos管,所述负压dcdc芯片的1、2管脚和双串联肖特基势垒二极管的3管脚之间依次并联第三电感、串联第九电容,所述双串联肖特基势垒二极管的1管脚和所述负压ldo芯片的13、15管脚之间依次并联第五电阻、并联第十电容,所述负压dcdc芯片的9管脚和所述负压ldo芯片的13、15管脚之间依次并联第六电阻、串联第七电阻、并联第十一电容,所述负压dcdc芯片的4、5、7管脚和所述第二正压ldo芯片的1管脚之间依次并联第十二电容、并联第十三电容、串联第四电感、并联第十四电容、并联第十五电容,所述第二正压ldo芯片的2管脚和所述第一pmos管的2管脚之间依次并联第八电阻、并联第九电阻。

11.较佳的,所述电源模块的前级保护电路包括第二pmos管和扼流电感,所述第二pmos管的2管脚和所述扼流电感的1管脚之间依次并联第十六电容、第十七电容,所述第二pmos管的1管脚和所述扼流电感的4管脚之间依次串联第十电阻、并联第十八电容、第十九电容。

12.较佳的,所述第一驱动放大器、所述隔离器、所述第二驱动放大器、所述功率监测模块、所述末级四路合成放大模组通过矩形波导依次连接。

13.较佳的,所述w波段合成功率放大器的功放芯片焊接采用高导热率烧结银焊接工艺。

14.较佳的,所述w波段合成功率放大器还包括用于散热的散热模块,所述散热模块为配置的金属散热片和强力风机。

15.与现有技术比较本发明的有益效果在于:本发明通过第一驱动放大器和第二驱动放大器将微弱的w频段信号放大至较高的水平,通过耦合器监测信号的幅值,最后将放大后的射频信号传输至末级四路合成放大模组进行最终的放大和输出;末级四路合成放大模组所采用的波导功率分配器与合成器具有隔离度高、损耗低的特点,高隔离可降低通道间的干扰,即当个别功放芯片损坏后,整个功放组件仍然具有一定的功率输出能力,低损耗可保证合成结构具有90%以上的合成效率;功放芯片焊接采用高导热率烧结银工艺替换现有的共晶工艺,明显降低了焊接热阻和功放芯片的结温,提高了功放芯片工作稳定性,从而改善功放电性能。第一驱动放大器、微波开关模块、第二驱动放大器、功率监测模块、末级四路合成放大模组依次连接,能够增强高频信号且稳定性高,设计简单,值得被推广使用。

附图说明

16.图1为所述w波段合成功率放大器的射频电路示意图;

17.图2为所述第一驱动放大器的馈电电路图;

18.图3为所述末级放大器的馈电电路图;

19.图4为所述电源模块主电路图;

20.图5为所述电源模块中的前级保护电路图。

21.图中数字表示:

[0022]1‑

第一驱动放大器;2

‑

隔离器;3

‑

第二驱动放大器;4

‑

功率监测模块;5

‑

末级四路合成放大模组;6

‑

耦合器;7

‑

高隔离四路功分器;8

‑

末级放大器;9

‑

高隔离四路合成器;10

‑

衰减器;11

‑

检波器;12

‑

电源模块。

具体实施方式

[0023]

以下结合附图,对本发明上述的和另外的技术特征和优点作更详细的说明。

[0024]

实施例一

[0025]

本发明所述w波段合成功率放大器包括第一驱动放大器1、隔离器2、第二驱动放大器3、功率监测模块4、末级四路合成放大模组5和电源模块12。所述第一驱动放大器1通过所述隔离器2与所述第二驱动放大器3连接,所述第二驱动放大器3通过所述功率监测模块4与所述末级四路合成放大模组5连接,所述电源模块12与所述第一驱动放大器1、所述第二驱动放大器3、所述功率监测模块4、所述末级四路合成放大模组5连接。

[0026]

所述第一驱动放大器1用于接收并高增益的放大高频弱信号,所述第二驱动放大器3用于进一步将高频信号放大至所需的水平,所述隔离器2用于隔断失配导致的能量反射,提高系统工作稳定性。

[0027]

较佳的,所述第一驱动放大器1、所述隔离器2、所述第二驱动放大器3、所述功率监测模块4、所述末级四路合成放大模组5通过标准矩形波导wr

‑

10依次连接。

[0028]

较佳的,所述w波段合成功率放大器的最大输出功率不小于6w。

[0029]

较佳的,所述w波段合成功率放大器还包括用于散热的散热模块,所述散热模块为配置的金属散热片和4个强力风机。

[0030]

所述w波段合成功率放大器所有功放芯片采用裸片焊接,近端低容值的2级滤波电容需要采用同样为裸露封装的芯片电容,用于隔绝直流电源对射频通路的干扰,且芯片与微带的射频通路和芯片与芯片电容的馈电通路均采用金丝键合的连接方式。

[0031]

所述w波段合成功率放大器所有功放芯片焊接采用高导热率烧结银焊接工艺,烧结银焊接导热率可达200w/(m

·

k)以上,而普通共晶焊导热率仅约50w/(m

·

k),烧结银焊接导热率是共晶焊接的4倍。因此,采用烧结银工艺焊接高热耗低效率的w波段功放芯片,可明显降低焊接热阻和功放芯片的结温与热阻、提高功放芯片工作稳定性,从而改善功放电性能。

[0032]

所述末级四路合成放大模组5所采用的功分器与合成器具有高隔离的特点,相邻通道的隔离度大于17db。所述的功分器与合成器采用金属波导多slot耦合、多孔sic吸收体内嵌和矩形腔形状微扰技术,实现了小体积、高隔离和良好匹配等目标。

[0033]

实施例二

[0034]

所述功率监测模块4包括耦合器6、衰减器10和检波器11,所述耦合器6设置在所述第二驱动放大器3、所述末级四路合成放大模组5之间,所述耦合器6通过所述衰减器10与所述检波器11连接。所述耦合器6的耦合端与所述衰减器10连接,所述衰减器10与所述检波器11的输入端连接,所述衰减器10可防止进入所述检波器11的功率过大、保护所述检波器11,所述检波器11的输出信号用于监测所述第二驱动放大器3的输出功率正常与否;所述功率监测模块4的输入端即为所述耦合器6的输入端,所述功率监测模块4的输出端即为所述耦合器6的直通端。

[0035]

所述耦合器6用于将射频通道中的能量提取小部分,经过所述衰减器10进一步衰减后,送入所述检波器11,用于监测所述第二驱动放大器3的输出功率正常与否。

[0036]

所述末级四路合成放大模组5包括高隔离四路功分器7、四个末级放大器8和高隔离四路合成器9,所述高隔离四路功分器7分别通过各所述末级放大器8和所述高隔离四路

合成器9连接。所述末级四路合成放大模组5主要用于对射频信号进行最终的放大和输出。

[0037]

具体的,所述末级四路合成放大模组5包括四个两路合成模块、高隔离四路波导功分器和高隔离四路波导合成器,四个所述两路合成模块的输入端与高隔离四路波导功分器输出端连接,四个所述两路合成模块的输出端与所述高隔离四路波导合成器输入端连接。所述高隔离四路波导功分器、所述两路合成模块和所述高隔离四路波导合成器从左到右依次连接。

[0038]

所述电源模块12用于为各级功率放大模块提供所需的直流偏置,同时为昂贵的末级功放芯片提供上下电的时序保护;整个w波段合成功率放大器能够增强高频信号且稳定性高,设计简单。

[0039]

所述电源模块12提供外部输入dc16v稳压保护与防反接功能,扼流电感q10可隔离外部电源与功率放大器内部信号之间的干扰。外部输入dc16v经过所述电源模块12的前级保护电路后,分为三路,一路到达第一驱动放大器,一路到达第二驱动放大器,最后一路达到电源模块主电路,为末级四路合成放大模组的功放芯片提供所需直流偏置和功放芯片的上电、去电时序保护功能(上电时,先栅压后漏压;去电时,先漏压后栅压)。

[0040]

所述第一驱动放大器1所用的放大器芯片u1,其具体型号为wfdn920960

‑

p23,所述第二驱动放大器3和所述末级四路合成放大模组5所用的芯片均为放大器芯片u2,其具体型号为wfdn920960

‑

p33

‑

2,所述衰减器10所用的芯片r1,其具体型号为mwa100

‑

6db,所述检波器11所用的芯片t1,器具体型号为tcc1904j。

[0041]

如图1所示,图1为所述w波段合成功率放大器的射频电路示意图;所述第一驱动放大器1、所述隔离器2、所述第二驱动放大器3、所述功率监测模块4和所述末级四路合成放大模组5,从左到右依次连接,所述功率监测模块4对所述第二驱动放大器3的输出功率进行监测。采用所述第一驱动放大器1、所述第二驱动放大器3和所述末级四路合成放大模组5对w频段信号进行放大并输出,所述电源模块12为所述第一驱动放大器1、所述第二驱动放大器3和所述末级四路合成放大模组5提供直流偏置电压。

[0042]

所述第一驱动放大器1和所述第二驱动放大器3之间连接了所述隔离器2,所述隔离器2能改善驻波,减少反射信号的影响,提高射频链路工作稳定性。

[0043]

如图2所示,图2为所述第一驱动放大器的馈电电路图。

[0044]

所述第一驱动放大器1和所述第二驱动放大器3包括电源部和放大部,所述电源部包括电源管理芯片q1、正压dcdc芯片q3、正压ldo芯片q2,所述放大部包括放大器芯片u1或u2;具体的,所述第一驱动放大模块包括放大器芯片u1、电源管理芯片q1、正压ldo芯片q2和正压dcdc芯片q3。所述第二驱动放大模块包括放大器芯片u2、电源管理芯片q1、正压ldo芯片q2和正压dcdc芯片q3。

[0045]

所述电源管理芯片q1的第17和第18引脚和所述放大器芯片u1或u2的漏极之间依次串联电阻r7和并联电容c2,所述电源管理芯片q1的第16引脚和所述放大器芯片u1或u2的栅极并联电容c5;所述正压dcdc芯片q3的第1引脚和所述正压ldo芯片q2的第6、7和8引脚之间依次串联电容c14、并联二极管d2、串联电感l2、并联电阻r17和并联电容c17;所述正压ldo芯片q2的第1、2、3引脚和所述电源管理芯片q1的第5、9引脚之间依次并联电容c13、并联电阻r18、并联电容c15。

[0046]

所述第一驱动放大器1和所述第二驱动放大器3的电源部分分别集成在各放大器

模块的内部。

[0047]

所述电源管理芯片q1具体型号为hmc980lp4e,所述正压dcdc芯片q2具体型号为lm2841

‑

q1,所述正压ldo芯片q3具体型号为adp3336。

[0048]

如图3所示,图3为所述末级放大器的馈电电路图;

[0049]

所述末级四路合成放大模组5设置有调制解调电路,所述调制解调电路包括nmos栅极驱动芯片q8和nmos管q9,所述nmos栅极驱动芯片q8的1管脚连接dc15v,所述nmos栅极驱动芯片q8的3管脚连接外部提供的lvttl控制电平信号,所述nmos栅极驱动芯片q8的4管脚和6管脚之间串联电容c33,所述nmos栅极驱动芯片q8的4管脚和所述nmos管q9的2管脚之间依次并联电容c33、并联电感l33,所述nmos栅极驱动芯片q8的5管脚和所述nmos管q9的1管脚之间串联电阻r31。

[0050]

所述nmos栅极驱动芯片q8具体型号为ltc4440,所述nmos管具体型号为irfs3107。

[0051]

如图4所示,图4为所述电源模块主电路图。

[0052]

所述电源模块12的主电路包括负压dcdc芯片q4、负压ldo芯片q5、正压ldo芯片q6和pmos管q7,所述负压dcdc芯片q4的1、2管脚和双串联肖特基势垒二极管d41的3管脚之间依次并联电感l41、串联电容c41,双串联肖特基势垒二极管d41的1管脚和所述负压ldo芯片q5的13、15管脚之间依次并联电阻r41、并联电容c42,所述负压dcdc芯片q4的9管脚和所述负压ldo芯片q5的13、15管脚之间依次并联电阻r44、串联电阻r41、并联电容c42,所述负压dcdc芯片q4的4、5、7管脚和所述正压ldo芯片q6的1管脚之间依次并联电容c48、并联电容c49、串联电感l42、并联电容c411、并联电容c412,所述正压ldo芯片q6的2管脚和所述pmos管q7的2管脚之间依次并联电阻r411、并联电阻r410。

[0053]

所述负压dcdc芯片q4具体型号为lt3479ede,所述负压ldo芯片q5具体型号为tps7a33,所述正压ldo芯片q6具体型号为lt1083,所述pmos管q7具体型号为irfr5305。

[0054]

如图5所示,所述电源模块12的前级保护电路包括pmos管q11和扼流电感q10,所述pmos管q11的2管脚和所述扼流电感q10的1管脚之间依次并联电容c51、电容c52,所述pmos管q11的1管脚和所述扼流电感q10的4管脚之间依次串联电阻r51、并联电容c51、电容c52。

[0055]

所述pmos管q7的具体型号为irfr5305,所述扼流电感q10的具体型号为bnx027h01。

[0056]

本实施例的w波段合成功率放大器在将发射激励信号放大到额定的功率输出的基础上还具有以下功能:

[0057]

功率监测功能:采用功率监测模块4对输入末级四路合成放大模组5的功率进行监测,第二驱动放大器输出的射频信号进入末级四路合成放大模组5时,会通过耦合器6的耦合端口分出很小部分能量,进入衰减器10,衰减6db后进入检波器11,通过示波器可实时观测检波器的输出电压,当检波器输出电压≥10v,则功率正常时;当检波器输出电压小于10v时,功率异常。从而实现对第二驱动放大器输出功率的监测。

[0058]

本实施例的w波段合成功率放大器的主要技术指标有以下内容:

[0059]

功放形态:固态功放;

[0060]

工作状态:脉冲或连续波;

[0061]

功放频率:w波段(94

±

1ghz);

[0062]

最大输出功率:≥6w;

[0063]

效率:≥10%;

[0064]

功率增益:≥30db;

[0065]

上升沿:≤200ns;

[0066]

下降沿:≤300ns;

[0067]

脉冲宽度:0.2s~连续波(射频);

[0068]

脉冲顶降:≤10%;

[0069]

带内输出功率平坦度:≤0.5db;

[0070]

输入驻波比:≤1.5;

[0071]

输出驻波比:≤2.0;

[0072]

检波输出:≥10v。

[0073]

本实施例的w波段合成功率放大器的射频输入输出接口、各级射频模块端口均为标准矩形波导口(wr

‑

10);

[0074]

本实施例的w波段合成功率放大器的电源采用dc16v供电;

[0075]

本实施例的w波段合成功率放大器在保证有效散热面积的情况下,采用4个12瓦风机进行强迫风冷,以满足散热要求。

[0076]

综上所述,该w波段合成功率放大器,通过第一驱动放大器和第二驱动放大器将微弱的w频段信号放大至较高的水平,通过功率监测模块监测第二驱动放大器输出信号的幅值,最后将放大后的射频信号传输至功放末级四路合成放大模组进行最终的放大和输出;第一驱动放大器、隔离器、第二驱动放大器、功率监测模块、末级四路合成放大模组从左到右依次连接,能够增强高频信号且稳定性高,设计简单,值得被推广使用。

[0077]

以上所述仅为本发明的较佳实施例,对本发明而言仅仅是说明性的,而非限制性的。本专业技术人员理解,在本发明权利要求所限定的精神和范围内可对其进行许多改变,修改,甚至等效,但都将落入本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。