1.本发明涉及一种光声重建算法的硬件加速方法,采用该硬件加速方法的装置及采用该装置的系统。

背景技术:

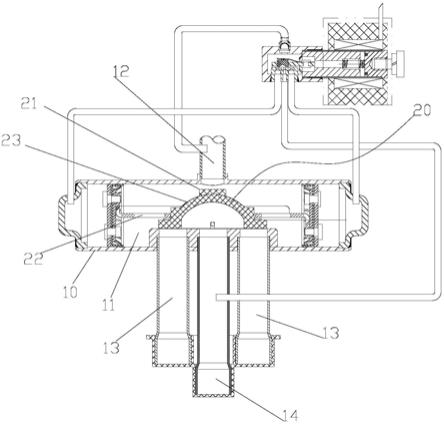

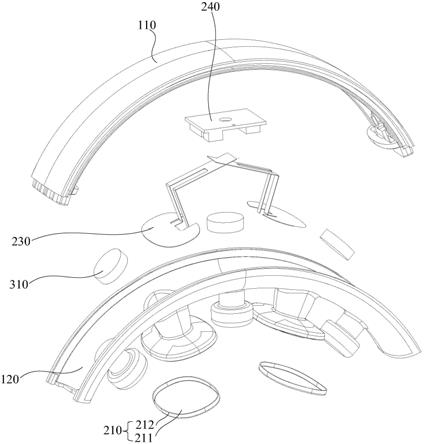

::2.光声效应是指当物体受到脉冲的光照射之后,物体会吸收光强,产生瞬时温度升降和体积涨缩现象,从而向外辐射出声信号的物理现象。基于光声效应,光声成像技术已经获得了广泛的关注和飞速的发展。如今,光声成像技术已经在小动物成像、血氧饱和度定量、肿瘤良恶性诊断上取得了一定的成功。3.在光声成像中,基于das(delay‑and‑sum)的图像重构算法被广泛应用于光声系统当中。在das算法中,假设系统使用的是线阵探头,共有n个超声探头,波束成形信号与接收到的超声信号的关系可以表示为:[0004][0005]式(1)中:sdas(x,y)表示波束成形信号在成像区域中位于坐标位置(x,y)处的值;s(i,τ(x,y,i))表示接收到的第i个超声探头信号在延迟时间τ(x,y,i)处的值,τ(x,y,i)表示从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间,c是超声的传播速度。[0006]基于式(1)可以得到成像区域每个位置的波束成型信号,从而得到最终的光声成像图像,如图1所示。[0007]运用das算法可以从接收到的光声信号中,重建初始压力场的分布。然而在实际运用过程中,由于光声信号的数据量较大,尽管算法结构简单,但在大量的数据传输过程中,实时性难以得到保证。技术实现要素:[0008]本发明要解决的技术问题是:在大量的数据传输过程中,利用das算法重建初始压力场的分布难以保证实时性。[0009]为了解决上述技术问题,本发明的一个技术方案是提供了一种光声重建算法的硬件加速方法,其特征在于,包括以下步骤:[0010]步骤1、基于已知的实际超声探头数量、各个超声探头的实际位置、采样率和超声的传播速度c计算得到从不同成像区域坐标位置到不同超声探头的超声传播时间,其中,将从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间定义为τ(x,y,i),i=1,2,...,n,n表示超声探头的总个数;[0011]步骤2、基于步骤1计算得到的超声传播时间建立查找表,将步骤1计算得到的超声传播时间τ(x,y,i)及对应的成像区域坐标位置(x,y)、第i个超声探头设置为查找表中的一条记录,在查找表中,将所有记录按照成像区域的坐标依次排列,即每个坐标位置(x,y),对应一个超声传播时间所对应的光声信号地址偏移量;若成像区域的大小为128x128像素,则查找表的大小为n×128×128;[0012]步骤3、采集n个超声探头给出的所有光声信号,将所有光声信号存储在存储单元中,所有光声信号的存储地址按照接收到该光声信号的延迟时间顺序存储,使得每个光声信号的存储地址与查找表中成像区域的每个坐标对应的超声转播时间对应的地址偏移量相关联;[0013]步骤4、根据查找表获取对应成像区域坐标位置的光声信号值的存储地址,基于存储地址读取光声信号,并生成成像区域图像;[0014]步骤5、获得当前通道的光声成像图片后,在下一个通道重复步骤3至步骤4获得下一个通道的光声成像图片,直至获得所有m个通道的光声成像图片后,m≥2,将所有通道的光声成像图片加合,得到最终的光声成像图片。[0015]本发明的另一个技术方案是提供了一种基于上述硬件加速方法的装置,其特征在于,包括:[0016]ram存储单元一,用于存储所述n个超声探头给出的所有光声信号;[0017]rom存储单元,用于存储所述查找表;[0018]ram存储单元二,根据所述查找表获得所述存储地址后,依据所述存储地址将所述光声信号从ram存储单元一读出后存入ram存储单元二内,由ram存储单元二输出当前通道的所述光声成像图片。[0019]本发明的另一个技术方案是提供了一种上述的装置应用,其特征在于,采用m个上述的装置,m≥2,每个上述的装置生成一个通道的所述光声成像图片,将所有上述的装置生成的所述光声成像图片加合后得到m通道的所述光声成像图片。[0020]本发明的另一个技术方案是提供了一种基于上述硬件加速方法的系统,其特征在于,包括:[0021]存储单元,用于存储所述n个超声探头给出的所有光声信号;[0022]可编程只读存储单元,用于存储所述查找表;[0023]das算法单元,用于实现上述的硬件加速方法,输出所述最终的光声成像图片。[0024]优选地,还包括总控单元以及输入输出单元,总控单元通过输入输出单元获得所述n个超声探头给出的所有光声信号后,再存入所述存储单元;[0025]在所述das算法单元获得所述光声成像图片后,总控单元控制输入输出单元将所述光声成像图片输出至外部设备。[0026]本发明提出了一种将das算法前置到前端的一种硬件加速设计,本发明根据固有的系统参数(探头数量、探头位置、采样率等)生成查找表,并根据查找表将das算法简化成对光声信号在ram中作存储操作,完成算法后,直接输出图片给后端pc。本发明提供的方法直接减少了大量的数据传输过程,大大降低系统成像时间,提高实时性,同时也提高了系统的集成度。本发明适用于das算法及其各种变体,可用于专用芯片的设计,也可用于soc集成芯片的设计。附图说明[0027]图1为das算法原理图;[0028]图2为单通道芯片das_asic设计框架;[0029]图3为多通道芯片das_asic设计框架;[0030]图4为单通道芯片das_asic的成像结果;[0031]图5为多通道芯片das_asic的成像结果;[0032]图6为soc芯片das_rec设计框架;[0033]图7为soc芯片das_rec中das_rec单元的设计框架;[0034]图8为soc芯片das_rec的成像结果。具体实施方式[0035]下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本技术所附权利要求书所限定的范围。[0036]根据das算法的原理,本发明提供的一种光声重建算法的硬件加速方法包括以下步骤:[0037]步骤1、将基于已知的实际超声探头数量、各个超声探头的实际位置、采样率和超声的传播速度c计算得到从不同成像区域坐标位置到不同超声探头的超声传播时间。其中,将从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间定义为τ(x,y,i),i=1,2,...,n,n表示超声探头的总个数。[0038]步骤2、基于步骤1计算得到的超声传播时间建立查找表。通过查找表建立了(x,y)、i以及τ(x,y,i)这三者之间的映射关系,即通过查找表建立了超声传播时间、成像区域坐标位置以及光声信号采样点之间的对应关系。[0039]设超声传播时间τ(x,y,i)及对应的成像区域坐标位置(x,y)、第i个超声探头设置为查找表中的一条记录,则将本实施例中将所有记录按照成像区域坐标位置(x,y),由大至小排序或者由小至大排序,每个坐标位置(x,y),对应一个超声传播时间所对应的光声信号地址偏移量。[0040]步骤3、采集n个超声探头给出的所有光声信号,将所有光声信号存储在前端硬件系统开辟的存储单元中。所有光声信号按照接收到该光声信号的延迟时间由小到大或者由大到小排列。存储时,从初始地址开始以固定的步长形成地址偏移量,将所有所述光声信号依之前确定的顺序存储在存储单元中。采用上述方式后,使得每个光声信号的存储地址与查找表中相匹配记录在查找表中的每个坐标位置(x,y)对应的值相关联。[0041]步骤4、从查找表的第一条或者最后一条记录开始,获得每一个成像区域坐标位置(x,y)相匹配的光声信号的存储地址。依据该存储地址,从存储单元中读取对应的光声信号。遍历所有坐标位置,即可获得当前通道的光声图像。。[0042]步骤5、获得当前通道的光声成像图片后,在下一个通道重复步骤3至步骤4获得下一个通道的光声成像图片,直至获得所有通道的光声成像图片后,将所有通道的光声成像图片加合,得到最终的光声成像图片。。[0043]本发明引入查找表的形式,将复杂的计算简化成光声信号存储和读取的过程。因为查找表的具体值与探头数量、探头位置、采样率和传播速度这些系统固有参数有关,故可将查找表当成常数提前烧入系统当中。此外若使用das的变体算法(dmas、das‑cf、muti‑das等),只需要更新查找表的值,即可完成变体的运算,泛化能力强。[0044]基于本发明提出的一种光声重建算法的硬件加速方法可以进行芯片设计,本实施例中,单通道芯片das_asic设计框架如图2所示。[0045]本实施例中,ram存储单元ram_data接收并存储1×1028×8bit的光声信号raw_data。rom存储单元table_data用于存储查找表。将ram存储单元ram_data存储的数据根据rom存储单元table_data中的查找表写入ram存储单元ram_img中(读取rom存储单元table_data中的查找表后获得ram存储单元ram_data的存储地址,依据该存储地址读取ram存储单元ram_data中的数据),ram存储单元ram_img输出128×128×8bit的光声成像图片rec_img。[0046]如图3所示,上述单通道芯片das_asic可以生成一通道光声成像图片,在128通道的情况下,使用128个该单通道芯片das_asic同时得到128张128×128×8bit的图像,然后再进行加合,最终得到128×128的最终成像结果。[0047]实施例中使用的数据结构如下:[0048]输入原始数据raw_data,即光声信号raw_data:sensor_num×depth×unit,其中,sensor_num表示探头数目,选值1、16、32、64、128;depth表示采样深度,选值1024;unit表示原始数据最小处理单元,选值8bit。[0049]输出图像数据rec_img,即光声成像图片rec_img:res_hor×res_ver×pixel_val,其中,res_hor表示输出图像水平分辨率,选值128;res_ver表示输出图像垂直分辨率,选值128;pixel_val表示单个像素值,选值8bit。[0050]使用单通道芯片das_asic和多通道芯片das_asic的成像结果如图4及图5所示,可以发现与使用pc端成像的结果一致。[0051]设计性能评估:[0052]存储一次1204×8bit的传感数据sensor_data需要1024个cycle,得到一张128×128的图像需要128×128=16384cycle。在系统中,128个单通道芯片das_asic同时工作,得到128张128×128的图片,然后将这128张图片按像素进行加合,需要加合时间128×128=16384cycle。总计1024 16384 16384=33792cycle。[0053]在200m的工作频率下,最终输出图像大概需要1.7ms(33792×5ns),按2ms预期达到的效果为每秒500帧。[0054]基于本发明提出的一种光声重建算法的硬件加速方法可以进行soc设计,如图6所示,包括:[0055]das_rec单元,实现光声重建算法的硬件加速方法,将原始数据raw_data处理成图像数据rec_img;[0056]ddr3单元:用于存储大量的原始数据raw_data;[0057]flash单元:用于存储das_rec单元所需的查找表数据,即光声重建算法的硬件加速方法中每个像素点的延迟时间对应的采样点位置;[0058]arm单元:为总控模块,本实施例使用cortex‑a9。[0059]i/o单元:为输入输出外设。[0060]上述soc芯片的工作步骤如下:[0061]1)下载系统数据,将根据实际探头数量、采样率和传播速度得到的查找表table_data烧入flash单元中。[0062]2)通过i/o单元,一次导入所有原始数据raw_data,并将数据存入ddr3单元。[0063]3)将ddr3单元中的一路原始数据raw_data(共有sensor_num路raw_data)和flash单元中的对应的查找表table_data的数据导入das_rec单元中,并流水实现重构分辨率为128×128的图像,并存储在das_rec单元中的ram模块中。[0064]4)重复步骤3)sensor_num次,每一次生成的128×128图像和前一次生成的图像进行加合,并将结果存储在das_rec单元中的ram模块中。[0065]5)通过i/o单元,输出图像数据rec_img。[0066]如图7所示,das_rec单元的工作步骤如下:[0067]1)接收传感数据sensor_data(1×1028×8bit),将数据存入ram模块ram_data中。[0068]2)将ram模块ram_data的数据根据查找表table_data写入ram模块ram_img(查找表table_data后获得ram模块ram_data的存储地址,依据该存储地址读取ram模块ram_data中的数据),[0069]3)重复步骤1)及步骤2)sensor_num次,并将每一次生成的图像数据ram_img和前一次的图像数据ram_img加合,[0070]4)输出128×128×8bit的图像。[0071]实施例中使用的数据结构如下:[0072]输入原始数据raw_data:sensor_num×depth×unit。其中,sensor_num表示探头数目,选值1、16、32、64、128;depth表示采样深度,选值1024;unit表示原始数据最小处理单元,选值8bit。[0073]输出图像数据rec_img:res_hor×res_ver×pixel_val。其中,res_hor表示输出图像水平分辨率,选值128;res_ver表示输出图像垂直分辨率,选值128;pixel_val表示单个像素值,选值8bit。[0074]配置flash单元数据table_data:sensor_num×table_hor×table_ver×delay_val。其中,sensor_num表示探头数目,选值1、16、32、64、128;table_hor表示输出图像水平分辨率,选值128;table_ver表示输出图像垂直分辨率,选值128;time_val表示单个像素位置的延迟时间,选值10bit。[0075]使用128通道的成像结果如图8所示,可以发现soc系统成像与使用pc端成像的结果一致。[0076]soc系统设计性能评估:[0077]在图6所示设计下一次导入128通道sensor_data,存储一路通道数据到ram_data需要1024个cycle,接下来根据table_data重构分辨率为128×128的图像,在这个过程中同时存储下一路通道数据,总共需要128×128=16384cycle,则完整的生成一张128通道的重构图像,需要1024 128×128×128=2098176cycle。在200m的工作频率下,最终输出图像大概需要10ms(2098176×5ns),预期达到的效果为每秒100帧。当前第1页12当前第1页12

背景技术:

::2.光声效应是指当物体受到脉冲的光照射之后,物体会吸收光强,产生瞬时温度升降和体积涨缩现象,从而向外辐射出声信号的物理现象。基于光声效应,光声成像技术已经获得了广泛的关注和飞速的发展。如今,光声成像技术已经在小动物成像、血氧饱和度定量、肿瘤良恶性诊断上取得了一定的成功。3.在光声成像中,基于das(delay‑and‑sum)的图像重构算法被广泛应用于光声系统当中。在das算法中,假设系统使用的是线阵探头,共有n个超声探头,波束成形信号与接收到的超声信号的关系可以表示为:[0004][0005]式(1)中:sdas(x,y)表示波束成形信号在成像区域中位于坐标位置(x,y)处的值;s(i,τ(x,y,i))表示接收到的第i个超声探头信号在延迟时间τ(x,y,i)处的值,τ(x,y,i)表示从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间,c是超声的传播速度。[0006]基于式(1)可以得到成像区域每个位置的波束成型信号,从而得到最终的光声成像图像,如图1所示。[0007]运用das算法可以从接收到的光声信号中,重建初始压力场的分布。然而在实际运用过程中,由于光声信号的数据量较大,尽管算法结构简单,但在大量的数据传输过程中,实时性难以得到保证。技术实现要素:[0008]本发明要解决的技术问题是:在大量的数据传输过程中,利用das算法重建初始压力场的分布难以保证实时性。[0009]为了解决上述技术问题,本发明的一个技术方案是提供了一种光声重建算法的硬件加速方法,其特征在于,包括以下步骤:[0010]步骤1、基于已知的实际超声探头数量、各个超声探头的实际位置、采样率和超声的传播速度c计算得到从不同成像区域坐标位置到不同超声探头的超声传播时间,其中,将从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间定义为τ(x,y,i),i=1,2,...,n,n表示超声探头的总个数;[0011]步骤2、基于步骤1计算得到的超声传播时间建立查找表,将步骤1计算得到的超声传播时间τ(x,y,i)及对应的成像区域坐标位置(x,y)、第i个超声探头设置为查找表中的一条记录,在查找表中,将所有记录按照成像区域的坐标依次排列,即每个坐标位置(x,y),对应一个超声传播时间所对应的光声信号地址偏移量;若成像区域的大小为128x128像素,则查找表的大小为n×128×128;[0012]步骤3、采集n个超声探头给出的所有光声信号,将所有光声信号存储在存储单元中,所有光声信号的存储地址按照接收到该光声信号的延迟时间顺序存储,使得每个光声信号的存储地址与查找表中成像区域的每个坐标对应的超声转播时间对应的地址偏移量相关联;[0013]步骤4、根据查找表获取对应成像区域坐标位置的光声信号值的存储地址,基于存储地址读取光声信号,并生成成像区域图像;[0014]步骤5、获得当前通道的光声成像图片后,在下一个通道重复步骤3至步骤4获得下一个通道的光声成像图片,直至获得所有m个通道的光声成像图片后,m≥2,将所有通道的光声成像图片加合,得到最终的光声成像图片。[0015]本发明的另一个技术方案是提供了一种基于上述硬件加速方法的装置,其特征在于,包括:[0016]ram存储单元一,用于存储所述n个超声探头给出的所有光声信号;[0017]rom存储单元,用于存储所述查找表;[0018]ram存储单元二,根据所述查找表获得所述存储地址后,依据所述存储地址将所述光声信号从ram存储单元一读出后存入ram存储单元二内,由ram存储单元二输出当前通道的所述光声成像图片。[0019]本发明的另一个技术方案是提供了一种上述的装置应用,其特征在于,采用m个上述的装置,m≥2,每个上述的装置生成一个通道的所述光声成像图片,将所有上述的装置生成的所述光声成像图片加合后得到m通道的所述光声成像图片。[0020]本发明的另一个技术方案是提供了一种基于上述硬件加速方法的系统,其特征在于,包括:[0021]存储单元,用于存储所述n个超声探头给出的所有光声信号;[0022]可编程只读存储单元,用于存储所述查找表;[0023]das算法单元,用于实现上述的硬件加速方法,输出所述最终的光声成像图片。[0024]优选地,还包括总控单元以及输入输出单元,总控单元通过输入输出单元获得所述n个超声探头给出的所有光声信号后,再存入所述存储单元;[0025]在所述das算法单元获得所述光声成像图片后,总控单元控制输入输出单元将所述光声成像图片输出至外部设备。[0026]本发明提出了一种将das算法前置到前端的一种硬件加速设计,本发明根据固有的系统参数(探头数量、探头位置、采样率等)生成查找表,并根据查找表将das算法简化成对光声信号在ram中作存储操作,完成算法后,直接输出图片给后端pc。本发明提供的方法直接减少了大量的数据传输过程,大大降低系统成像时间,提高实时性,同时也提高了系统的集成度。本发明适用于das算法及其各种变体,可用于专用芯片的设计,也可用于soc集成芯片的设计。附图说明[0027]图1为das算法原理图;[0028]图2为单通道芯片das_asic设计框架;[0029]图3为多通道芯片das_asic设计框架;[0030]图4为单通道芯片das_asic的成像结果;[0031]图5为多通道芯片das_asic的成像结果;[0032]图6为soc芯片das_rec设计框架;[0033]图7为soc芯片das_rec中das_rec单元的设计框架;[0034]图8为soc芯片das_rec的成像结果。具体实施方式[0035]下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本技术所附权利要求书所限定的范围。[0036]根据das算法的原理,本发明提供的一种光声重建算法的硬件加速方法包括以下步骤:[0037]步骤1、将基于已知的实际超声探头数量、各个超声探头的实际位置、采样率和超声的传播速度c计算得到从不同成像区域坐标位置到不同超声探头的超声传播时间。其中,将从成像区域坐标位置(x,y)到第i个超声探头的超声传播时间定义为τ(x,y,i),i=1,2,...,n,n表示超声探头的总个数。[0038]步骤2、基于步骤1计算得到的超声传播时间建立查找表。通过查找表建立了(x,y)、i以及τ(x,y,i)这三者之间的映射关系,即通过查找表建立了超声传播时间、成像区域坐标位置以及光声信号采样点之间的对应关系。[0039]设超声传播时间τ(x,y,i)及对应的成像区域坐标位置(x,y)、第i个超声探头设置为查找表中的一条记录,则将本实施例中将所有记录按照成像区域坐标位置(x,y),由大至小排序或者由小至大排序,每个坐标位置(x,y),对应一个超声传播时间所对应的光声信号地址偏移量。[0040]步骤3、采集n个超声探头给出的所有光声信号,将所有光声信号存储在前端硬件系统开辟的存储单元中。所有光声信号按照接收到该光声信号的延迟时间由小到大或者由大到小排列。存储时,从初始地址开始以固定的步长形成地址偏移量,将所有所述光声信号依之前确定的顺序存储在存储单元中。采用上述方式后,使得每个光声信号的存储地址与查找表中相匹配记录在查找表中的每个坐标位置(x,y)对应的值相关联。[0041]步骤4、从查找表的第一条或者最后一条记录开始,获得每一个成像区域坐标位置(x,y)相匹配的光声信号的存储地址。依据该存储地址,从存储单元中读取对应的光声信号。遍历所有坐标位置,即可获得当前通道的光声图像。。[0042]步骤5、获得当前通道的光声成像图片后,在下一个通道重复步骤3至步骤4获得下一个通道的光声成像图片,直至获得所有通道的光声成像图片后,将所有通道的光声成像图片加合,得到最终的光声成像图片。。[0043]本发明引入查找表的形式,将复杂的计算简化成光声信号存储和读取的过程。因为查找表的具体值与探头数量、探头位置、采样率和传播速度这些系统固有参数有关,故可将查找表当成常数提前烧入系统当中。此外若使用das的变体算法(dmas、das‑cf、muti‑das等),只需要更新查找表的值,即可完成变体的运算,泛化能力强。[0044]基于本发明提出的一种光声重建算法的硬件加速方法可以进行芯片设计,本实施例中,单通道芯片das_asic设计框架如图2所示。[0045]本实施例中,ram存储单元ram_data接收并存储1×1028×8bit的光声信号raw_data。rom存储单元table_data用于存储查找表。将ram存储单元ram_data存储的数据根据rom存储单元table_data中的查找表写入ram存储单元ram_img中(读取rom存储单元table_data中的查找表后获得ram存储单元ram_data的存储地址,依据该存储地址读取ram存储单元ram_data中的数据),ram存储单元ram_img输出128×128×8bit的光声成像图片rec_img。[0046]如图3所示,上述单通道芯片das_asic可以生成一通道光声成像图片,在128通道的情况下,使用128个该单通道芯片das_asic同时得到128张128×128×8bit的图像,然后再进行加合,最终得到128×128的最终成像结果。[0047]实施例中使用的数据结构如下:[0048]输入原始数据raw_data,即光声信号raw_data:sensor_num×depth×unit,其中,sensor_num表示探头数目,选值1、16、32、64、128;depth表示采样深度,选值1024;unit表示原始数据最小处理单元,选值8bit。[0049]输出图像数据rec_img,即光声成像图片rec_img:res_hor×res_ver×pixel_val,其中,res_hor表示输出图像水平分辨率,选值128;res_ver表示输出图像垂直分辨率,选值128;pixel_val表示单个像素值,选值8bit。[0050]使用单通道芯片das_asic和多通道芯片das_asic的成像结果如图4及图5所示,可以发现与使用pc端成像的结果一致。[0051]设计性能评估:[0052]存储一次1204×8bit的传感数据sensor_data需要1024个cycle,得到一张128×128的图像需要128×128=16384cycle。在系统中,128个单通道芯片das_asic同时工作,得到128张128×128的图片,然后将这128张图片按像素进行加合,需要加合时间128×128=16384cycle。总计1024 16384 16384=33792cycle。[0053]在200m的工作频率下,最终输出图像大概需要1.7ms(33792×5ns),按2ms预期达到的效果为每秒500帧。[0054]基于本发明提出的一种光声重建算法的硬件加速方法可以进行soc设计,如图6所示,包括:[0055]das_rec单元,实现光声重建算法的硬件加速方法,将原始数据raw_data处理成图像数据rec_img;[0056]ddr3单元:用于存储大量的原始数据raw_data;[0057]flash单元:用于存储das_rec单元所需的查找表数据,即光声重建算法的硬件加速方法中每个像素点的延迟时间对应的采样点位置;[0058]arm单元:为总控模块,本实施例使用cortex‑a9。[0059]i/o单元:为输入输出外设。[0060]上述soc芯片的工作步骤如下:[0061]1)下载系统数据,将根据实际探头数量、采样率和传播速度得到的查找表table_data烧入flash单元中。[0062]2)通过i/o单元,一次导入所有原始数据raw_data,并将数据存入ddr3单元。[0063]3)将ddr3单元中的一路原始数据raw_data(共有sensor_num路raw_data)和flash单元中的对应的查找表table_data的数据导入das_rec单元中,并流水实现重构分辨率为128×128的图像,并存储在das_rec单元中的ram模块中。[0064]4)重复步骤3)sensor_num次,每一次生成的128×128图像和前一次生成的图像进行加合,并将结果存储在das_rec单元中的ram模块中。[0065]5)通过i/o单元,输出图像数据rec_img。[0066]如图7所示,das_rec单元的工作步骤如下:[0067]1)接收传感数据sensor_data(1×1028×8bit),将数据存入ram模块ram_data中。[0068]2)将ram模块ram_data的数据根据查找表table_data写入ram模块ram_img(查找表table_data后获得ram模块ram_data的存储地址,依据该存储地址读取ram模块ram_data中的数据),[0069]3)重复步骤1)及步骤2)sensor_num次,并将每一次生成的图像数据ram_img和前一次的图像数据ram_img加合,[0070]4)输出128×128×8bit的图像。[0071]实施例中使用的数据结构如下:[0072]输入原始数据raw_data:sensor_num×depth×unit。其中,sensor_num表示探头数目,选值1、16、32、64、128;depth表示采样深度,选值1024;unit表示原始数据最小处理单元,选值8bit。[0073]输出图像数据rec_img:res_hor×res_ver×pixel_val。其中,res_hor表示输出图像水平分辨率,选值128;res_ver表示输出图像垂直分辨率,选值128;pixel_val表示单个像素值,选值8bit。[0074]配置flash单元数据table_data:sensor_num×table_hor×table_ver×delay_val。其中,sensor_num表示探头数目,选值1、16、32、64、128;table_hor表示输出图像水平分辨率,选值128;table_ver表示输出图像垂直分辨率,选值128;time_val表示单个像素位置的延迟时间,选值10bit。[0075]使用128通道的成像结果如图8所示,可以发现soc系统成像与使用pc端成像的结果一致。[0076]soc系统设计性能评估:[0077]在图6所示设计下一次导入128通道sensor_data,存储一路通道数据到ram_data需要1024个cycle,接下来根据table_data重构分辨率为128×128的图像,在这个过程中同时存储下一路通道数据,总共需要128×128=16384cycle,则完整的生成一张128通道的重构图像,需要1024 128×128×128=2098176cycle。在200m的工作频率下,最终输出图像大概需要10ms(2098176×5ns),预期达到的效果为每秒100帧。当前第1页12当前第1页12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。