1.本发明涉及半导体技术领域,特别是涉及一种改良的半导体元件的制造方法。

背景技术:

2.应力工程(stress engineering)已被用于提高场效晶体管(fet)元件的元件性能。通常,n型fet使用拉伸(tensile)应力,p型fet使用压缩(compressive)应力以提高元件性能。

3.静态随机存取存储器(sram)常应用于集成电路中。嵌入式sram在高速通信、图像处理和系统单芯片(soc)应用中特别受欢迎。sram单元具有无需刷新即可保存数据的优点。

4.然而,在制造40纳米以下超低电压(ulp)sram的过程中所省略的p型轻掺杂漏极(pldd)光掩模往往导致sram面临较高的等待漏电流(isb)问题。

技术实现要素:

5.本发明的主要目的在于提供一种改良的形成半导体元件的方法,以解决现有技术的不足与缺点。

6.本发明一方面提供一种形成半导体元件的方法,包括:提供一基底,其上具有一逻辑电路区和一存储单元区;在所述逻辑电路区内形成具有一第一栅极的一第一晶体管并且在所述存储单元区内形成具有一第二栅极的一第二晶体管,其中所述第一晶体管为一nmos晶体管,所述第二晶体管为一pmos晶体管;沉积一应力层,覆盖所述逻辑电路区中的所述第一晶体管和所述存储单元区中的所述第二晶体管;以及使所述第一晶体管和所述第二晶体管在所述应力层的影响下进行一退火制作工艺,以再结晶所述第一栅极和所述第二栅极。

7.根据本发明实施例,所述应力层是氮化硅层。

8.根据本发明实施例,所述应力层具有拉伸应力。

9.根据本发明实施例,所述应力层产生一压缩应力,在所述退火制作工艺中对所述第一栅极和所述第二栅极进行再结晶时,所述压缩应力被存储在所述第一栅极和所述第二栅极内。

10.根据本发明实施例,被存储在所述第一栅极和所述第二栅极内的所述压缩应力在所述第一晶体管的一第一通道区和所述第二晶体管的一第二通道区内引起一压缩应变。

11.根据本发明实施例,所述压缩应变提高了所述第一晶体管的性能,而降低了所述第二晶体管的性能。

12.根据本发明实施例,所述第一栅极和所述第二栅极为多晶硅栅极。

13.根据本发明实施例,对所述第一晶体管和第二晶体管进行所述退火制作工艺后,所述方法另包含:去除所述应力层。

附图说明

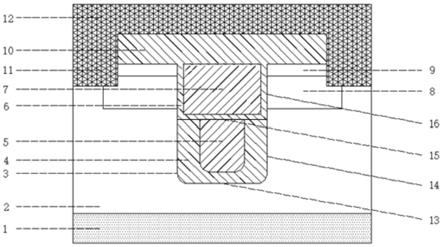

14.图1至图3例示一种形成半导体元件的方法的示意图。

15.主要元件符号说明

16.1 半导体元件

17.100 基底

18.110 nmos晶体管

19.120 pmos晶体管

20.111、121、311、321 栅极

21.111l、121l、311l、321l 栅极介电层

22.112、114 nldd区

23.116、118 n型重掺杂区

24.122、124、312、314、322、324 pldd区

25.126、128、316、318、326、328 p型重掺杂区

26.119、129、319、329 间隙壁

27.ch

‑

1、ch

‑

2、chn、chp 通道区

28.lr 逻辑电路区

29.mr 存储单元区

30.pl pmos拉升晶体管

31.pr pmos拉升晶体管

32.sl 应力层

33.st 沟槽隔离结构

具体实施方式

34.在下文中,将参照附图说明细节,该些附图中的内容也构成说明书细节描述的一部分,并且以可实行该实施例的特例描述方式来绘示。下文实施例已描述足够的细节使该领域的一般技术人士得以具以实施。

35.当然,也可采行其他的实施例,或是在不悖离文中所述实施例的前提下作出任何结构性、逻辑性、及电性上的改变。因此,下文的细节描述不应被视为是限制,反之,其中所包含的实施例将由随附的权利要求来加以界定。

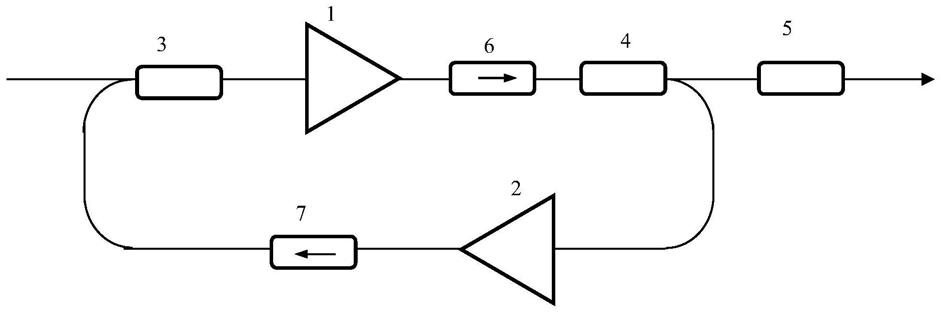

36.请参阅图1至图3,其例示一种形成半导体元件1的方法。首先

37.如图1所示,提供一基底100,其上具有一逻辑电路区lr和一存储单元区mr。根据本发明实施例,存储单元区mr内将形成由复数个晶体管所构成的静态随机存取存储器(sram),例如,六晶体管(6t)sram单元,由两个交叉耦合的反相器和存取晶体管组成,用于读取和写入数据,其中,6tsram单元的存取架构中可以包括两个pmos拉升晶体管(pull up transistor)pl和pr。

38.在制造40纳米以下超低电压(ulp)sram的过程中,省略了p型轻掺杂漏极(pldd)光掩模,pmos拉升晶体管pl的pldd掺杂是与嵌入式高压元件一同形成,这使得sram单元的pmos拉升晶体管pl在电性表现上的反应过快,导致sram面临较高的等待漏电流(isb)问题。本发明可以解决这个问题。

39.根据本发明实施例,在图1中,两个pmos拉升晶体管pl和pr彼此串接在一起,其中,pmos拉升晶体管pl包含一栅极311,例如,多晶硅栅极,设置在基底100上。在栅极311和基底

100之间,可以设置一栅极介电层311l。pmos拉升晶体管pl还包含一pldd区312和一pldd区314,其中pldd区312连接一p型重掺杂区316,而pldd区314连接一p型重掺杂区318。在pldd区312和pldd区314之间是一通道区ch

‑

1。在栅极311的侧壁上可以设置有一间隙壁319。

40.根据本发明实施例,pmos拉升晶体管pr包含一栅极321,例如,多晶硅栅极,设置在基底100上。在栅极321和基底100之间,可以设置一栅极介电层321l。pmos拉升晶体管pr还包含一pldd区322和一pldd区324,其中pldd区322连接一p型重掺杂区326,而pldd区324连接一p型重掺杂区328。p型重掺杂区328和p型重掺杂区318连接在一起。在pldd区322和pldd区324之间是一通道区ch

‑

2。在栅极321的侧壁上可以设置有一间隙壁329。

41.根据本发明实施例,在逻辑电路区lr内可以形成有一nmos晶体管110和一pmos晶体管120。根据本发明实施例,nmos晶体管110包含一栅极111,例如,多晶硅栅极,设置在基底100上。在栅极111和基底100之间,可以设置一栅极介电层111l。nmos晶体管110还包含一nldd区112和一nldd区114,其中nldd区112连接一n型重掺杂区116,而nldd区114连接一n型重掺杂区118。在nldd区112和nldd区114之间是一通道区chn。在栅极111的侧壁上可以设置有一间隙壁119。

42.根据本发明实施例,pmos晶体管120包含一栅极121,例如,多晶硅栅极,设置在基底100上。在栅极121和基底100之间,可以设置一栅极介电层121l。pmos晶体管120还包含一pldd区122和一pldd区124,其中pldd区122连接一p型重掺杂区126,而pldd区124连接一p型重掺杂区128。在pldd区122和pldd区124之间是一通道区chp。在栅极121的侧壁上可以设置有一间隙壁129。基底100内设置有一沟槽隔离结构st,用来将nmos晶体管110和pmos晶体管120彼此隔离。

43.根据本发明实施例,在完成逻辑电路区lr和存储单元区mr内的晶体管的制作后,接着,全面沉积一应力层(stressor layer)sl,覆盖逻辑电路区lr中的nmos晶体管110和pmos晶体管120,和存储单元区mr中的pmos拉升晶体管pl和pr。根据本发明实施例,应力层sl可以是氮化硅层。根据本发明实施例,应力层sl具有拉伸应力(tensile stress)。

44.如图2所示,接着,利用光刻及蚀刻制作工艺,将逻辑电路区lr内覆盖在pmos晶体管120上的应力层sl去除,而剩下的应力层sl继续覆盖着逻辑电路区lr内的nmos晶体管110和存储单元区mr内的pmos拉升晶体管pl和pr。

45.如图3所示,接着,对逻辑电路区lr中的nmos晶体管110和pmos晶体管120和存储单元区mr中的pmos拉升晶体管pl和pr,进行一退火制作工艺。逻辑电路区lr中的nmos晶体管110的栅极111和存储单元区mr中的pmos拉升晶体管pl和pr的栅极311和321在应力层sl的影响下进行再结晶。

46.根据本发明实施例,应力层sl产生一压缩应力,在退火制作工艺中,栅极111和栅极311和321再结晶时,所述压缩应力被存储在栅极111和栅极311和321内。根据本发明实施例,被存储在栅极111和栅极311和321内的所述压缩应力在nmos晶体管110的通道区chn和pmos拉升晶体管pl和pr的通道区ch

‑

1和ch

‑

2内引起压缩应变(compressive strain)。

47.根据本发明实施例,所述压缩应变提高了nmos晶体管110的性能,而降低了pmos拉升晶体管pl和pr的性能。根据本发明实施例,在完成对退火制作工艺后,接着去除剩下的应力层sl。

48.本发明的技术特征在于,利用具有拉伸应力的应力层sl,刻意使存储单元区mr内

的pmos拉升晶体管pl和pr的性能降低,解决了sram单元的pmos拉升晶体管pl在电性表现上的反应过快的问题,使得sram的等待漏电流(isb)可以恢复到正常范围。

49.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。