具有双阱隔离的延伸漏极mos

技术领域

1.本公开涉及集成电路领域。更具体地,本公开涉及集成电路中的延伸漏极金属氧化物半导体(mos)晶体管。

背景技术:

2.一些集成电路包括延伸漏极金属氧化物半导体(mos)晶体管,其中漏极具有与下面的衬底相同的导电类型。漏极必须与衬底隔离,这涉及更多的工艺复杂性或增大的组件区域,或两者都有。在不降低晶体管性能和可靠性参数(诸如开态电流、关态电流、阈值和热载流子可靠性)的情况下提供隔离已被证明具有挑战性。

技术实现要素:

3.本公开介绍集成电路,其包括位于集成电路的衬底中的下层上方的延伸漏极金属氧化物半导体(mos)晶体管。延伸漏极mos晶体管的漏极阱和下层都具有第一导电类型。漏极阱通过具有与第一导电类型相反的第二导电类型的漏极隔离阱与下层分开。延伸漏极mos晶体管的源极区通过具有第二导电类型的体阱与下层分开。漏极隔离阱和体阱都接触下层。漏极隔离阱中的第二导电类型的平均掺杂剂密度小于体阱中的第二导电类型的平均掺杂剂密度。

附图说明

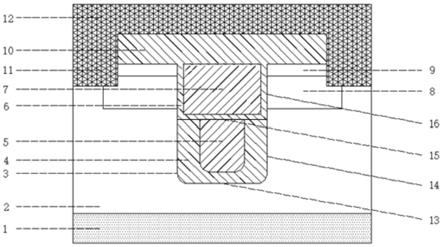

4.图1是包括具有双阱隔离的延伸漏极mos晶体管的示例集成电路的横截面。

5.图2a到图2d是在示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。

6.图3是包括具有双阱隔离的延伸漏极mos晶体管的另一示例集成电路的横截面。

7.图4a到图4d是在另一示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。

8.图5是包括具有双阱隔离的延伸漏极mos晶体管的又一示例集成电路的横截面。

9.图6a到图6d是在又一示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。

具体实施方式

10.参照附图描述本公开。附图不是按比例绘制的,且提供它们只是为了说明本公开。下面参考用于说明的示例应用描述本公开的几个方面。应当理解,阐述许多具体细节、关系和方法以提供对本公开的理解。本公开不受所说明的动作或事件的顺序的限制,因为一些动作可以以不同的顺序发生和/或与其他动作或事件同时发生。此外,并非需要所有说明的动作或事件来实施根据本公开的方法。

11.此外,虽然本文说明的实施例中的一些以具有深度和宽度的各种区的二维视图示

出,但应清楚地理解,这些区仅是实际上作为具有三维结构的器件的一部分的说明。因此,当在实际器件上制造时,这些区将具有三个维度,包括长度、宽度和深度。不旨在将本发明的有源器件限于所示的物理结构。包括这些结构以证明本发明对当前优选实施例的效用和应用。

12.集成电路具有衬底,该衬底带有具有第一导电类型的半导体材料的下层。集成电路包括位于下层上方的延伸漏极金属氧化物半导体(mos)晶体管。延伸漏极mos晶体管的漏极阱具有第一导电类型。漏极阱通过漏极隔离阱与下层分开,该漏极隔离阱接触漏极阱并接触下层。漏极隔离阱具有与第一导电类型相反的第二导电类型。延伸漏极mos晶体管的源极区通过体阱与下层分开。体阱接触源极区和下层。体阱具有第二导电类型。漏极隔离阱中的第二导电类型的平均掺杂剂密度小于体阱中的第二导电类型的平均掺杂剂密度。

13.在本公开中可以使用诸如顶、在

……

上方、在

……

之上、在

……

下方和在

……

之下的术语。这些术语不应解释为限制结构或元件的位置或取向,而是应该用于提供结构或元件之间的空间关系。

14.如在本公开中使用的术语“基本上相等”在一方面是指在集成电路制造期间遭遇的制造容差内相等的量,诸如平均掺杂剂密度。在另一方面中,在本公开中使用的术语“基本上相等”是指在量的测量期间遭遇的测量容差内相等的量(诸如平均掺杂剂密度)的测量结果。

15.图1是包括具有双阱隔离的延伸漏极mos晶体管的示例集成电路的横截面。集成电路100具有衬底101,该衬底101具有顶表面102并且包括具有第一导电类型的半导体材料的下层103。在此示例中,第一导电类型为p型,如图1所示。衬底101还可以包括延伸到顶表面102的场氧化物层104。场氧化物层104可以横向分开集成电路100中的组件和元件。为了本公开的目的,术语“横向”和“横向地”被理解为指平行于顶表面102的平面的方向。类似地,术语“竖直”和“竖直地”被理解为指垂直于顶表面102的平面的方向。术语横向、横向地、竖直和竖直地在随后的示例中类似地理解。场氧化物层104可以具有浅沟槽隔离(sti)结构,其中场氧化物层104在顶表面102之下延伸至250纳米至750纳米的深度,具有基本上笔直的侧壁,并且不在顶表面102之上延伸超过100纳米,如图1所描绘。

16.集成电路100包括具有第一极性的延伸漏极mos晶体管105。在此示例中,第一极性是p沟道。延伸漏极mos晶体管105包括位于衬底101中的具有第一导电类型的漏极阱106;在此示例中,漏极阱106为p型。例如,漏极阱106可以具有10

16

cm

‑3至10

18

cm

‑3的第一导电类型的平均掺杂剂密度,以使得延伸漏极mos晶体管105能够在期望电压下操作。为了本公开的目的,术语“第一导电类型的掺杂剂浓度”和“第一导电类型的掺杂剂”是指提供第一导电类型的掺杂剂。对于第一导电类型为p型的情况,如在此示例中,硼、镓和铟是第一导电类型的掺杂剂,因为它们提供p型导电。对于第一导电类型是n型的情况,磷、砷和锑是第一导电类型的掺杂剂,因为它们提供n型导电。延伸漏极mos晶体管105可以可选地包括接触漏极阱106并延伸至顶表面102的漏极接触区107。漏极接触区107具有第一导电类型,第一导电类型的平均掺杂剂密度例如为10

19

cm

‑3到10

21

cm

‑3以提供对漏极阱106的期望低电阻连接。

17.延伸漏极mos晶体管105包括位于衬底101中的具有第一导电类型的源极区108;在此示例中,源极区108为p型。源极区108和漏极接触区107可以具有基本上相等的第一导电类型的掺杂剂的平均密度。延伸漏极mos晶体管105包括在衬底101的顶表面102上的栅极介

电层109和在栅极介电层109上的栅极110。栅极介电层109可以包括二氧化硅、氮化二氧化硅、氧化铪、氧化锆或适用于mos晶体管的其他介电材料。栅极介电层109可以具有适合于在集成电路100的操作期间的期望栅极

‑

漏极电势的厚度。例如,延伸漏极mos晶体管105可以在8伏到100伏的栅极

‑

漏极电势下操作。例如,栅极介电层109可以具有3纳米至10纳米的厚度。栅极110可以包括例如多晶硅、氮化钛、氮化钽或金属硅化物。栅极110从源极区108延伸到漏极阱106,与漏极阱106的一部分重叠。在此示例中,延伸漏极mos晶体管105可以包括场氧化物层104a的元件,其位于漏极接触区107和与栅极110重叠的漏极阱106的一部分之间。漏极阱106在场氧化物层104a的元件下方延伸,如图1所描绘。此漏极构造可以通过在场氧化物层104a的元件下方的漏极阱106的部分的两端提供电压降,而有利地使延伸漏极mos晶体管105的区域(area)减小。延伸漏极mos晶体管105可以包括在栅极110的侧表面上的栅极侧壁间隔件111。栅极侧壁间隔件111可以包括例如氮化硅、二氧化硅或氮氧化硅。

18.漏极阱106通过漏极隔离阱112与下层103竖直分开,该漏极隔离阱112位于衬底101中并具有与第一导电类型相反的第二导电类型。漏极隔离阱112接触下层103和漏极阱106。在此示例中,漏极隔离阱112为n型,如图1所示。漏极隔离阱112可以具有例如10

15

cm

‑3至10

17

cm

‑3的第二导电类型的平均掺杂剂密度,以在漏极隔离阱112和漏极阱106之间的结处提供期望结电容,并且在漏极隔离阱112和漏极阱106之间提供期望击穿电势。为了本公开的目的,术语“第二导电类型的掺杂剂浓度”和“第二导电类型的掺杂剂”是指提供第二导电类型的掺杂剂。漏极隔离阱112中的第二导电类型的掺杂剂浓度可以随着顶表面102之下的竖直距离而降低,并且可以随着距漏极接触区107的横向距离而降低,这可以通过适当放置漏极隔离阱112和漏极阱106之间的结来实现期望结电容和期望击穿电势。

19.源极区108通过体阱113与下层103竖直分开,该体阱113位于衬底101中并具有第二导电类型。体阱113接触下层103和源极区108。在此示例中,体阱113为n型,如图1所示。体阱113可以具有例如10

16

cm

‑3至10

18

cm

‑3的第二导电类型的平均掺杂剂密度,以提供用于延伸漏极mos晶体管105的期望阈值电势。漏极隔离阱112的第二导电类型的平均掺杂剂密度小于体阱113的第二导电类型的平均掺杂剂密度。在此示例中,体阱113可以在栅极110下方接触漏极阱106,如图1所示,这可以有利地减小延伸漏极mos晶体管105的区域。体阱113可以可选地围绕漏极阱106横向延伸,如图1所描绘。延伸漏极mos晶体管105的构造(具有通过漏极隔离阱112与下层103隔离的漏极阱106,且具有通过体阱113与下层103隔离的源极区108,其中漏极隔离阱112和体阱113两者都接触下层103)可以通过消除对在延伸漏极mos晶体管105下方完全延伸的单个隔离结构的需要而有利地减小延伸漏极mos晶体管105的区域。延伸漏极mos晶体管105可以可选地包括接触体阱113并延伸到顶表面102的体接触区114。体接触区114具有第二导电类型,其中第二导电类型的平均掺杂剂密度例如为10

19

cm

‑3至10

21

cm

‑3以提供对体阱113的期望低电阻连接。

20.延伸漏极mos晶体管105在图1中描绘为具有非对称构造,其中源极区108位于漏极阱106的一侧上。在此示例的替代版本中,延伸漏极mos晶体管105可具有对称构造,其中源极区108位于漏极阱106的相对侧上。

21.集成电路100可以可选地包括具有第一极性的第一低电压mos晶体管115和具有与第一极性相反的第二极性的第二低电压mos晶体管116。在此示例中,第一低电压mos晶体管115为p沟道,且第二低电压mos晶体管116为n沟道。出于本公开的目的,如应用于mos晶体管

的术语“低电压”是指在小于3伏的漏极

‑

源极电势下操作的mos晶体管。此类晶体管通常用于逻辑电路和静态随机存取存储器(sram)电路。第一低电压mos晶体管115具有在衬底101的顶表面102上的第一低电压栅极结构117、在衬底101中的第一源极118以及在衬底101中的第一漏极119。第一低电压mos晶体管115设置在第一阱120中。第一阱120具有第二导电类型,在此示例中为n型,如图1所示。第一阱120可以具有与体阱113基本上相等的第二导电类型的平均掺杂剂密度。

22.第二低电压mos晶体管116具有在衬底101的顶表面102上的第二低电压栅极结构121、在衬底101中的第二源极122以及在衬底101中的第二漏极123。第二低电压mos晶体管116设置在第二阱124中。第二阱124具有第一导电类型,在此示例中为p型,如图1所示。第二阱124可以具有与漏极阱106基本上相等的第一导电类型的平均掺杂剂密度。在半导体工业中,具有与衬底相同导电类型的阱有时仅被称为衬底,而根本不是阱。然而,如本文所用,术语“阱”旨在表示n型阱或p型阱,并且包括可以具有与衬底相同导电类型的阱。

23.集成电路100可以可选地包括具有第一极性(在此示例中为p沟道)的第一高电压mos晶体管125,以及具有第二极性(在此示例中为n沟道)的第二高电压mos晶体管126。出于本公开的目的,应用到mos晶体管的术语“高电压”是指在3伏至6伏的漏极

‑

源极电势下操作的mos晶体管。此类晶体管通常用于输入/输出电路和模拟电路。第一高电压mos晶体管125具有在衬底101的顶表面102上的第一高电压栅极结构127、在衬底101中的第三源极128以及在衬底101中的第三漏极129。第一高电压mos晶体管125设置在第三阱130中。第三阱130具有第二导电类型,其在此示例中为n型,如图1所示。第三阱130可以具有与漏极隔离阱112基本上相等的第二导电类型的平均掺杂剂密度。

24.第二高电压mos晶体管126具有在衬底101的顶表面102上的第二高电压栅极结构131、在衬底101中的第四源极132以及在衬底101中的第四漏极133。第二高电压mos晶体管126设置在第四阱134中。第四阱134具有第一导电类型,在此示例中为p型,如图1所示。

25.集成电路100可以包括在衬底101的顶表面102上方的介电层135。介电层135可以表现为具有一个或多个子层的预金属介电(pmd)层,例如顶表面102上的氮化硅的pmd衬里,二氧化硅、磷硅玻璃(psg)或硼磷硅玻璃(bpsg)的层,以及氮化硅、氧氮化硅、碳化硅或碳氮化硅的覆盖层。集成电路100还可以包括延伸穿过介电层135的接触件136以提供对延伸漏极mos晶体管105、第一低电压mos晶体管115、第二低电压mos晶体管116、第一高电压mos晶体管125和第二高电压mos晶体管126的电连接。接触件136可以包括具有钨芯的钛和氮化钛或氮化钽的衬里。集成电路100还可以包括在介电层135上的互连件137,从而制作对接触件136的电连接。例如,互连件可以包括铝或铜。

26.图2a到图2d是在示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。参考图2a,形成集成电路200包括获取衬底201。衬底201可以实施为体型半导体晶片、具有外延层的半导体晶片、绝缘体上硅(soi)晶片或适合于形成集成电路200的其他结构。衬底201具有顶表面202,并且在顶表面202之下包括具有第一导电类型的半导体材料的下层203。在此示例中,第一导电类型为p型,如图2a所示。

27.衬底201包括用于延伸漏极mos晶体管205的区域、用于第一低电压mos晶体管215的区域、用于第二低电压mos晶体管216的区域、用于第一高电压mos晶体管225的区域以及用于第二高电压mos晶体管226的区域。如参考图1所描述的那样使用术语“低电压”和“高电

压”。

28.保护层238可以形成在顶表面202上。保护层238可以包括通过热氧化工艺形成的二氧化硅。例如,保护层238可以具有5纳米至25纳米的厚度。保护层238有时被称为垫层或垫氧化物层。保护层238可以在后续制造操作期间有利地减少衬底201的污染。保护层238的其他组成和形成方法在此示例的范围内。

29.在保护层238上方形成第一注入掩模239。第一注入掩模239在用于延伸漏极mos晶体管205的区域中的用于随后形成的漏极隔离阱212(如图2b所示)的区域240中暴露保护层238。在此示例中,区域240可以在平行于图2a的平面的方向上具有横向尺寸,其小于随后形成的漏极隔离阱212在相同方向上的横向尺寸的一半。第一注入掩模239可以在用于第一高电压mos晶体管225的区域中可选地暴露用于随后形成的第三阱230(如图2b所示)的区域。第一注入掩模239可以使用光刻工艺由光刻胶形成。替代地,第一注入掩模239可以由硬掩模材料(诸如氮氧化硅)形成。用于形成第一注入掩模239的其他材料和工艺在此示例的范围内。

30.在由第一注入掩模239暴露的区域中,将第一掺杂剂241注入到衬底201中,以在用于延伸漏极mos晶体管205的区域中形成漏极隔离注入区243,并在用于第一高电压mos晶体管225的区域中形成阱注入区244。第一掺杂剂241是第二导电类型的掺杂剂,在此示例中,其为n型掺杂剂,诸如磷。可以以10

12

cm

‑2至10

14

cm

‑2的剂量注入第一掺杂剂241,以在随后形成的漏极隔离阱212和随后形成的第三阱230中提供期望的第二导电类型的平均掺杂剂密度。可以以足以将第一掺杂剂241的主要部分穿过保护层238且进入衬底201的能量注入第一掺杂剂241。例如,可以以20千电子伏(kev)至100kev的能量注入第一掺杂剂241。

31.在注入第一掺杂剂241之后移除第一注入掩模239。可以通过等离子体蚀刻工艺,然后是湿法蚀刻清除工艺来移除第一注入掩模239。

32.参考图2b,衬底201通过热工艺245来加热以扩散和激活在图2a的漏极隔离注入区243中和阱注入区244中的图2a的第一掺杂剂241,以分别形成漏极隔离阱212和第三阱230。热工艺245可以具有足以扩散第一掺杂剂241的热分布,使得漏极隔离阱212在平行于图2b的平面的方向上的横向尺寸是由图2a的第一注入掩模230暴露的区域240在相同方向上的横向尺寸的两倍以上。举例来说,热工艺245可将衬底201加热至1080℃至1120℃,持续300分钟至400分钟。热工艺245可以实施为使用包括一些氧的外界环境的炉处理,以在衬底201的顶表面202上生长额外二氧化硅。作为热工艺245的结果,漏极隔离阱212中的第一掺杂剂241在漏极隔离阱212和下层203之间的结处的密度可以比在包围漏极隔离注入区243的区中的密度小。

33.参考图2c,形成延伸至衬底201中的场氧化物层204。场氧化物层204可以通过sti工艺来形成,使得场氧化物层204具有如图2c所描绘的sti结构。示例sti工艺包括在衬底201上方形成氮化硅的化学机械抛光(cmp)停止层,穿过cmp停止层并进入衬底201来蚀刻隔离沟槽,以及利用使用原硅酸四乙酯(teos)的等离子体增强化学气相淀积(pecvd)工艺、高密度等离子体(hdp)工艺、使用teos和臭氧的高纵横比工艺(harp)、使用硅烷的大气化学气相沉积(apcvd)工艺或使用二氯硅烷的亚大气压化学气相沉积(sacvd)工艺,用二氧化硅填充隔离沟槽。通过氧化物cmp工艺从cmp停止层上方移除过量二氧化硅,且随后移除cmp停止层,留下场氧化物层204。在此示例中,场氧化物层204a的元件可以形成在漏极隔离阱212。

34.第四阱234可以形成在用于第二高电压mos晶体管226的区域中。第四阱234具有第一导电类型,在此示例中为p型,如图2c所示。

35.第二注入掩模246形成在保护层238上方。第二注入掩模246在用于延伸漏极mos晶体管205的区域中的用于随后形成的体阱213的区域中暴露保护层238。第二注入掩模246可以可选地在用于第一低电压mos晶体管215的区域中暴露用于随后形成的第一阱220的区域。例如,第二注入掩模246可以包括光刻胶或硬掩模材料,并且可以通过与图2a的第一注入掩模239类似的工艺来形成。

36.在由第二注入掩模246暴露的区域中,将第二掺杂剂247注入到衬底201中。第二掺杂剂247是第二导电类型的掺杂剂,在此示例中,为n型掺杂剂,例如磷和砷。可以在多于一个注入步骤中注入第二掺杂剂247,其中主要步骤具有剂量为10

12

cm

‑2至10

14

cm

‑2的磷,以400kev至600kev的能量注入。第二掺杂剂247的额外注入步骤可以具有较低剂量和较低能量,以设置用于延伸漏极mos晶体管205和第一低电压mos晶体管215的阈值电势。

37.在第二掺杂剂247注入之后移除第二注入掩模246。可以通过与用于移除图2a的第一注入掩模239的工艺类似的工艺移除第二注入掩模246。

38.随后加热衬底201以激活注入到衬底201中的第二掺杂剂247,以形成体阱213和第一阱220。可以通过快速热工艺来加热衬底201,以减少第二掺杂剂247和图2a的第一掺杂剂241在漏极隔离阱212中的不希望的扩散。例如,衬底201可以被加热到1000℃到1100℃,持续20秒到60秒。体阱213具有比漏极隔离阱212高的第二导电类型的平均掺杂剂密度。

39.参考图2d,在用于延伸漏极mos晶体管205的区域中,在衬底201中形成漏极阱206,使得漏极阱206通过漏极隔离阱212与下层203竖直分开。此示例的漏极阱206经形成以便在场氧化物层204a的元件下方延伸。漏极阱206具有第一导电类型;在此示例中,漏极阱206为p型。在用于第二低电压mos晶体管216的区域中,可以在衬底201中形成第二阱224。第二阱224具有第一导电类型,并且可以形成为具有与漏极阱206类似的第一导电类型的掺杂剂的分布。

40.漏极阱206和第二阱224可以通过使用适当注入掩模(图2d中未示出)将第一导电类型的掺杂剂(诸如硼)注入到衬底201中而同时形成。第一导电类型的掺杂剂可以在多于一个注入步骤中注入,主要步骤具有剂量为10

12

cm

‑2至10

14

cm

‑2的硼,以200kev至400kev的能量注入。第一导电类型的掺杂剂的额外注入步骤可以具有较低剂量和较低能量,以设置用于第二低电压mos晶体管216的阈值电势。随后衬底201被加热以激活注入到衬底201中的第一导电类型的掺杂剂,以形成漏极阱206和第二阱224。衬底201可以通过与参考图2c描述的类似工艺加热。与分别形成漏极阱206和第二阱224相比,形成漏极阱206和第二阱224可以降低集成电路200的制造成本。在示例的一些版本中,激活第一导电类型的掺杂剂可以与激活图2c的第二掺杂剂247同时进行。

41.图2c的保护层238随后被移除。例如,可以通过使用氢氟酸的缓冲稀水溶液的湿法蚀刻工艺移除保护层238。

42.在用于延伸漏极mos晶体管205区域中,在衬底201的顶表面202上形成栅极介电层209。栅极介电层209可以通过热氧化工艺,或通过经由例如原子层沉积(ald)工艺沉积氧化物材料来形成。延伸漏极mos晶体管205的栅极210形成在栅极介电层209上。栅极210例如可以通过以下来形成:在栅极介电层209上形成多晶硅层,且然后使用蚀刻掩模和反应离子蚀

刻(rie)工艺图案化多晶硅层。栅极侧壁间隔件211可以形成在栅极210的侧表面上。栅极侧壁间隔件211可以通过以下来形成:在栅极210上方形成氮化硅、二氧化硅或氮氧化硅的一个或多个共形层,并使用各向异性蚀刻工艺从栅极210和衬底201的水平表面移除一个或多个共形层,从而在栅极210的侧表面上留下一个或多个共形层以提供栅极侧壁间隔件211。

43.在用于第一低电压mos晶体管215的区域中,在衬底201的顶表面202上形成第一低电压栅极结构217。在用于第二低电压mos晶体管216的区域中,在衬底201的顶表面202上形成第二低电压栅极结构221。在用于第一高电压mos晶体管225的区域中,在衬底201的顶表面202上形成第一高电压栅极结构227。在用于第二高电压mos晶体管226的区域中,在衬底201的顶表面202上形成第二高电压栅极结构231。第一低电压栅极结构217、第二低电压栅极结构221、第一高电压栅极结构227和第二高电压栅极结构231的部分或全部可以与延伸漏极mos晶体管205的栅极介电层209、栅极210和栅极侧壁间隔件211同时形成。

44.源极区208形成在衬底201中,与邻近栅极210的体阱213接触,并且定位成与漏极阱206相对。源极区208具有第一导电类型;在此示例中,源极区208为p型。源极区208可以通过在两个或更多个注入步骤中注入第一导电类型的掺杂剂(诸如硼)而形成。源极区208的第一部分可以通过在形成栅极侧壁间隔件211之前注入第一导电类型的掺杂剂的第一部分来形成,并且源极区208的第二部分可以通过在形成栅极侧壁间隔件211后注入第一导电类型的掺杂剂的第二部分而形成。例如,第一导电类型的掺杂剂的总剂量可以是1

×

10

14

cm

‑2至1

×

10

16

cm

‑2。衬底201随后被加热以激活注入到衬底201中的第一导电类型的掺杂剂,以形成源极区208。衬底201可以通过尖峰退火工艺加热,以减少已经激活的掺杂剂在衬底201中的不希望的扩散。例如,衬底201可以被加热到950℃到1100℃,持续1秒到10秒。

45.漏极接触区207可以可选地形成在衬底201中,接触漏极阱206。漏极接触区207具有第一导电类型;在此示例中,漏极接触区207为p型。漏极接触区207可以与源极区208同时形成。

46.在用于第一低电压mos晶体管215的区域中,在第一低电压栅极结构217的相对侧上,在衬底201中形成第一源极218和第一漏极219。在用于第一高电压mos晶体管225的区域中,在第一高电压栅极结构227的相对侧上,在衬底201中形成第三源极228和第三漏极229。第一源极218、第一漏极219、第三源极228和第三漏极229具有第一导电类型;在此示例中,第一源极218、第一漏极219、第三源极228和第三漏极229为p型。第一源极218、第一漏极219、第三源极228和第三漏极229可以与源极区208同时形成。

47.体接触区214可以可选地形成在衬底201中,接触体阱213。体接触区214具有第二导电类型;在此示例中,体接触区214为n型。体接触区214可以通过可选地在两个或更多个注入步骤中将第二导电类型的掺杂剂(诸如磷、砷和锑)注入到衬底201中来形成。例如,第二导电类型的掺杂剂的总剂量可以是1

×

10

14

cm

‑2至1

×

10

16

cm

‑2。随后衬底201被加热以激活注入到衬底201中的第二导电类型的掺杂剂,以形成体接触区214。衬底201可以通过尖峰退火工艺来加热,以减少已经激活的掺杂剂在衬底201中的不希望的扩散。例如,衬底201可以被加热到950℃到1100℃,持续1秒到10秒。

48.在用于第二低电压mos晶体管216的区域中,在第二低电压栅极结构221的相对侧上,在衬底201中形成第二源极222和第二漏极223。在用于第二高电压mos晶体管226的区域中,在第二高电压栅极结构231的相对侧上,在衬底201中形成第四源极232和第四漏极233。

第二源极222、第二漏极223、第四源极232和第四漏极233具有第二导电类型;在此示例中,第二源极222、第二漏极223、第四源极232和第四漏极233为n型。第二源极222、第二漏极223、第四源极232和第四漏极233可以与体接触区214同时形成。

49.集成电路200的形成可以通过在衬底201的顶表面202上方形成介电层(图2d中未示出)来继续,该介电层类似于图1的介电层135。可以穿过介电层形成接触件(未在图2d中示出),类似于图1的接触件136。可以在介电层上形成互连件(图2d未示出),从而制作对接触件的电连接,类似于图1的互连件137。

50.图3是包括具有双阱隔离的延伸漏极mos晶体管的另一示例集成电路的横截面。集成电路300具有衬底301,该衬底301具有顶表面302并且包括具有第一导电类型的半导体材料的下层303。在此示例中,第一导电类型为p型,如图3所示。衬底301还可以包括延伸至顶表面302的场氧化物层304。场氧化物层304可以具有sti结构,如图3所描绘。

51.集成电路300包括具有第一极性(在此示例中为p沟道)的延伸漏极mos晶体管305。延伸漏极mos晶体管305包括位于衬底301中的具有第一导电类型的漏极阱306;在此示例中,漏极阱306为p型。漏极阱306可以具有如参考图1的漏极阱106所公开的第一导电类型的平均掺杂剂密度。延伸漏极mos晶体管305可以可选地包括漏极接触区307,其接触漏极阱306并延伸至顶表面302。漏极接触区307具有第一导电类型,具有如参考图1的漏极接触区107所公开的第一导电类型的平均掺杂剂密度。

52.延伸漏极mos晶体管305包括位于衬底301中的具有第一导电类型的源极区308;在此示例中,源极区308为p型。在此示例中,源极区308对称地布置在漏极阱306的相对侧上,如图3所描绘。源极区308和漏极接触区307可以具有类似的第一导电类型的掺杂剂的平均密度。延伸漏极mos晶体管305包括在衬底301的顶表面302上的栅极介电层309和栅极介电层309上的栅极310。在此示例中,栅极310和栅极介电层309对称地布置在漏极阱306的相对侧上,如图3所描绘。栅极310和栅极介电层309可以包括参考图1的栅极110和栅极介电层109所公开的材料。栅极310从源极区308朝向漏极阱306延伸;在此示例中,栅极310不与漏极阱306的一部分重叠。延伸漏极mos晶体管305可以包括在栅极310的侧表面上的栅极侧壁间隔件311。硅化物阻挡层348设置在衬底301的顶表面302上方,从栅极310延伸到漏极接触区307。硅化物阻挡层348可以包括一层或多层二氧化硅、氮化硅、氮氧化硅或适于防止在顶表面302上形成金属硅化物的其他材料。在此示例的一些版本中,硅化物阻挡层348可以表现为栅极侧壁间隔件311的延伸。

53.漏极阱306通过漏极隔离阱312与下层303竖直分开,该漏极隔离阱312位于衬底301中并具有与第一导电类型相反的第二导电类型。在此示例中,漏极隔离阱312为n型,如图3所示。漏极隔离阱312接触下层303和漏极阱306。漏极隔离阱312可以具有例如10

15

cm

‑3至10

17

cm

‑3的第二导电类型的平均掺杂剂密度。如图3所描绘,漏极隔离阱312可以横向围绕漏极阱306,以及在漏极阱306下方完全延伸。在此示例中,漏极隔离阱312可以具有较高第二导电类型的掺杂剂密度的彼此横向相邻使得两个或更多个区312a,其中区312a之间的漏极隔离阱具有比区312a低的第二导电类型的掺杂剂密度。较高掺杂剂密度的区312a可以提供第二导电类型的掺杂剂的更均匀分布,与图1漏极隔离阱112的横向降低的掺杂剂浓度相比,这可以有利地实现漏极阱306在漏极阱306的横向周边周围的期望结电容和期望击穿电势。

54.源极区308通过体阱313与下层303竖直分开,该体阱313位于衬底301中并具有第二导电类型。在此示例中,体阱313为n型,如图3所示。体阱313接触下层303和源极区308。体阱313可以具有例如10

16

cm

‑3至10

18

cm

‑3的第二导电类型的平均掺杂剂密度。漏极隔离阱312的第二导电类型的平均掺杂剂密度小于体阱313的第二导电类型的平均掺杂剂密度。在此示例中,体阱313可以通过漏极隔离阱312与漏极阱306在栅极310下方分开,如图3所描绘,与其中体阱接触漏极阱的类似晶体管相比,这可以有利地使得延伸漏极mos晶体管305能够在更高电势下操作。延伸漏极mos晶体管305的构造(具有通过漏极隔离阱312与下层303隔离的漏极阱306,并且具有通过体阱313与下层303隔离的源极区308,其中漏极隔离阱312和体阱313两者都接触下层303)可以通过消除对在延伸漏极mos晶体管305下方完全延伸的单个隔离结构的需要而有利地减小延伸漏极mos晶体管305的区域。延伸漏极mos晶体管305可以可选地包括接触体阱313并延伸到顶表面302的体接触区314。体接触区314具有第二导电类型,其中第二导电类型的平均掺杂剂密度例如为10

19

cm

‑3至10

21

cm

‑3,以提供对体阱313的期望低电阻连接。

55.延伸漏极mos晶体管305在图3中被描绘为具有对称构造,其中源极区308位于漏极阱306的两侧上。在此示例的替代版本中,延伸漏极mos晶体管305可以具有非对称构造,其中源极区308位于漏极阱306的一侧上。

56.在此示例中,金属硅化物349设置在漏极接触区307上、源极区308上和体接触区314上。金属硅化物349可以有利地提供对漏极接触区307、源极区308和体接触区314的减小电阻的连接。由于存在硅化物阻挡层348,在漏极接触区307和栅极310之间的顶表面302不含金属硅化物349。金属硅化物349可以包括例如钛硅化物、钴硅化物、镍硅化物、铂硅化物或钨硅化物。

57.集成电路300可以可选地包括具有第一极性(此示例中为p沟道)的第一低电压mos晶体管315。第一低电压mos晶体管315具有在衬底301的顶表面302上的第一低电压栅极结构317、在衬底301中的第一源极318以及在衬底301中的第一漏极319,其中金属硅化物349在第一源极318和第一漏极319上。第一低电压mos晶体管315设置在第一阱320中,该第一阱320具有第二导电类型,在此示例中为n型,如图3所示。第一阱320可以具有与体阱313基本上相等的第二导电类型的平均掺杂剂密度。

58.集成电路300还可以可选地包括具有第二极性(在此示例中为n沟道)的第二低电压mos晶体管316。第二低电压mos晶体管316具有在衬底301的顶表面302上的第二低电压栅极结构321、在衬底301中的第二源极322以及在衬底301中的第二漏极323,其中金属硅化物349在第二源极322和第二漏极323上。第二低电压mos晶体管316设置在第二阱324中,该第二阱324具有第一导电类型,在此示例中为p型,如图3所示。第二阱324可以具有与漏极阱306基本上相等的第一导电类型的平均掺杂剂密度。

59.集成电路300可以可选地包括具有第一极性(在此示例中为p沟道)的第一高电压mos晶体管325。第一高电压mos晶体管325具有在衬底301的顶表面302上的第一高电压栅极结构327、在衬底301中的第三源极328以及在衬底301中的第三漏极329,其中金属硅化物349在第三源极328和第三漏极329上。第一高电压mos晶体管325设置在第三阱330中,该第三阱330具有第二导电类型,在此示例中为n型,如图3所示。第三阱330可以具有与漏极隔离阱312基本上相等的第二导电类型的平均掺杂剂密度。

60.集成电路300还可以可选地包括具有第二极性(在此示例中为n沟道)的第二高电压mos晶体管326。第二高电压mos晶体管326具有在衬底301的顶表面302上的第二高电压栅极结构331、在衬底301中的第四源极332以及在衬底301中的第四漏极333,其中金属硅化物349在第四源极332和第四漏极333上。第二高电压mos晶体管326设置在第四阱334中,该第四阱334具有第一导电类型,在此示例中为p型,如图3所示。

61.集成电路300可以包括在衬底301的顶表面302上方的介电层335。介电层335可以表现为类似于参考图1所公开的pmd层的pmd层。集成电路300还可以包括延伸穿过介电层335到达金属硅化物349的接触件336,以提供对延伸漏极mos晶体管305、第一低电压mos晶体管315、第二低电压mos晶体管316、第一高电压mos晶体管325和第二高电压mos晶体管326的电连接。接触件336可以具有参考图1的接触件136所公开的结构。集成电路300还可以包括在介电层335上的互连件337,从而制作对接触件336的电连接。

62.图4a到图4d是在另一示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。参考图4a,集成电路400的形成包括获取衬底401,其可以如参考图2a的衬底201所公开的那样实施。衬底401具有顶表面402,并且包括在顶表面402之下的半导体材料的下层403。下层403具有第一导电类型,在此示例中为p型,如图4a所示。

63.衬底401包括用于延伸漏极mos晶体管405的区域、用于第一低电压mos晶体管415的区域、用于第二低电压mos晶体管416的区域、用于第一高电压mos晶体管425的区域以及用于第二高电压mos晶体管426的区域。如参考图1所描述的那样使用术语“低电压”和“高电压”。

64.保护层438可以形成在顶表面402上。保护层438可以具有如参考图2a的保护层238所描述的组成和结构。第一注入掩模439形成在保护层438上方。第一注入掩模439在用于延伸漏极mos晶体管405的区域中的用于随后形成的漏极隔离阱412(如图4b所示)的区域中暴露保护层438。在此示例中,第一注入掩模439在用于延伸漏极mos晶体管405的区域中的多个子区域450中暴露保护层438。子区域450可以彼此分开,或者可以在图2a的平面之外连接。第一注入掩模439可以可选地在用于第一高电压mos晶体管425的区域中暴露用于随后形成的第三阱430(图4b所示的)的区域。可以如参考图2a的第一注入掩模239所公开的那样形成第一注入掩模439。

65.在由第一注入掩模439暴露的区域中将第一掺杂剂441注入到衬底401中,以在用于延伸漏极mos晶体管405的区域中形成多个漏极隔离注入区443,并在用于第一高电压mos晶体管425的区域中形成阱注入区444。在此示例中,漏极隔离注入区443对应于由第一注入掩模439暴露的子区域450,如图4a所描绘。第一掺杂剂441为第二导电类型的掺杂剂,在此示例中为n型掺杂剂,诸如磷。可以以10

12

cm

‑2至10

14

cm

‑2的剂量注入第一掺杂剂441,以在随后形成的漏极隔离阱412和随后形成的第三阱430中提供期望的第二导电类型的平均掺杂剂密度。具有多个漏极隔离注入区443可以在漏极隔离注入区443中提供第一掺杂剂441的第一平均剂量,并且可以在用于第一高电压mos晶体管425的区域中的阱注入区444中提供第一掺杂剂441的第二平均剂量,其中漏极隔离注入区443中的第一掺杂剂441的第一期望平均剂量低于阱注入区444中的第一掺杂剂441的第二平均剂量。第一掺杂剂441可以在足以将第一掺杂剂441的主要部分穿过保护层438并进入衬底401的能量下注入。在注入第一

掺杂剂441之后移除第一注入掩模439。

66.参考图4b,衬底401通过热工艺445来加热以扩散和激活在图4a的漏极隔离注入区443和阱注入区444中的图4a的第一掺杂剂441,以分别形成漏极隔离阱412和第三阱430。热工艺445可以具有足以使第一掺杂剂441充分扩散以形成跨漏极隔离注入区连续的漏极隔离阱412的热分布。具有多个漏极隔离注入区443可以引起在漏极隔离阱412中的第二导电类型的较高掺杂剂密度的彼此横向相邻的多个区412a,其中每个区412a对应于漏极隔离注入区443。举例来说,热工艺445可以将衬底401加热至1080℃至1120℃,持续300分钟至400分钟。热工艺445可以如参考图22b所公开的那样实施。漏极隔离阱412中的第一掺杂剂441的平均密度可以低于第三阱430中的第一掺杂剂441的平均密度。

67.参考图4c,形成延伸到衬底401中的场氧化物层404。场氧化物层404可以通过sti工艺来形成,使得场氧化物层404具有如图4c所描绘的sti结构。第四阱434可以形成在用于第二高电压mos晶体管426的区域中。第四阱434具有第一导电类型,在此示例中为p型,如图4c所示。

68.第二注入掩模446形成在保护层438上方。第二注入掩模446在用于延伸漏极mos晶体管405的区域中的用于随后形成的体阱413的区域中暴露保护层438。第二注入掩模446可以可选地在用于第一低电压mos晶体管415的区域中暴露用于随后形成的第一阱420的区域。可以通过与图4a的第一注入掩模439类似的工艺来形成第二注入掩模446。在由第二注入掩模446暴露的区域中将第二掺杂剂447注入到衬底401中。在此示例中,第二掺杂剂447是第二导电类型的掺杂剂,n型掺杂剂,诸如磷和砷。可以在多于一个注入步骤中注入第二掺杂剂447,其中主要步骤具有剂量为10

12

cm

‑2至10

14

cm

‑2的磷,以400kev至600kev的能量注入。第二掺杂剂447的额外注入步骤可以具有较低的剂量和较低的能量,以设置用于延伸漏极mos晶体管405和第一低电压mos晶体管415的阈值电势。在注入第二掺杂剂447之后移除第二注入掩模446。可以通过与用于移除图4a的第一注入掩模439的工艺类似的工艺移除第二注入掩模446。

69.衬底401随后被加热以激活注入到衬底401中的第二掺杂剂447,以形成体阱413和第一阱420。衬底401可以通过快速热工艺来加热,以减少第二掺杂剂447和图4a的第一掺杂剂441在漏极隔离阱412中的不希望的扩散。体阱413具有比漏极隔离阱412高的第二导电类型的平均掺杂剂密度。

70.参考图4d,在用于延伸漏极mos晶体管405的区域中,在衬底401中形成漏极阱406,使得漏极阱406通过漏极隔离阱412与下层403竖直分开。漏极阱406具有第一导电类型;此示例中为p型。在用于第二低电压mos晶体管416的区域中,可以在衬底401中形成第二阱424。第二阱424具有第一导电类型,并且可以形成为具有与漏极阱406类似的第一导电类型的掺杂剂的分布。漏极阱406和第二阱424可以如参考图2d的漏极阱206和第二阱224所公开的那样同时形成,从而获得降低制造成本的类似优势。图4c的保护层438随后被移除。

71.在用于延伸漏极mos晶体管405的区域中,在衬底401的顶表面402上形成栅极介电层409。延伸漏极mos晶体管405的栅极410形成在栅极介电层409上。栅极410和栅极介电层409可以如参考图2d的栅极210和栅极介电层209所公开的那样形成。栅极侧壁间隔件411可以形成在栅极410的侧表面上。栅极侧壁间隔件411可以如参考图2d的栅极侧壁间隔件211所公开的那样形成。硅化物阻挡层448形成在衬底401的顶表面402上方,从栅极410延伸到

漏极接触区407。硅化物阻挡层448可以通过以下来形成:在栅极410上方和衬底401的顶表面402上方形成一层或多层二氧化硅、氮化硅或氮化硅,然后使用等离子体蚀刻工艺在被蚀刻掩模(图4d中未示出)暴露的地方移除一个或多个层l来图案化一个或多个层。替代地,硅化物阻挡层448可以通过图案化用于形成栅极侧壁间隔件411的共形层来形成,使得硅化物阻挡层448被实施为栅极侧壁间隔件411的延伸。

72.在用于第一低电压mos晶体管415的区域中,在衬底401的顶表面402上形成第一低电压栅极结构417。在用于第二低电压mos晶体管416的区域中,在衬底401的顶表面402上形成第二低电压栅极结构421。在用于第一高电压mos晶体管425的区域中,在衬底401的顶表面402上形成第一高电压栅极结构427。在用于第二高电压mos晶体管426的区域中,在衬底401的顶表面402上形成第二高电压栅极结构431。第一低电压栅极结构417、第二低电压栅极结构421、第一高电压栅极结构427和第二高电压栅极结构431的部分或全部可以与延伸漏极mos晶体管405的栅极介电层409、栅极410和栅极侧壁间隔件411同时形成。

73.源极区408形成在衬底401中,与邻近栅极410的体阱413接触,并且定位成与漏极阱406相对。源极区408具有第一导电类型;在此示例中,源极区408为p型。源极区408可以如参考图2d的源极区208所公开的那样形成。漏极接触区407可以可选地形成在衬底401中,接触漏极阱406。漏极接触区407具有第一导电类型;在此示例中,漏极接触区407为p型。漏极接触区407可以与源极区408同时形成。在用于第一低电压mos晶体管415的区域中,在第一低电压栅极结构417的相对侧上,在衬底401中形成第一源极418和第一漏极419。在用于第一高电压mos晶体管425的区域中,在第一高电压栅极结构427的相对侧上,在衬底401中形成第三源极428和第三漏极429。第一源极418、第一漏极419、第三源极428和第三漏极429具有第一导电类型;在此示例中,第一源极418、第一漏极419、第三源极428和第三漏极429为p型。第一源极418、第一漏极419、第三源极428和第三漏极429可以与源极区408同时形成。

74.体接触区414可以可选地形成在衬底401中,接触体阱413。体接触区414具有第二导电类型;在此示例中,体接触区414为n型。体接触区414可以如参考图2d的体接触区214所公开的那样形成。在用于第二低电压mos晶体管416的区域中,在第二低电压栅极结构421的相对侧上,在衬底401中形成第二源极422和第二漏极423。在用于第二高电压mos晶体管426的区域中,在第二高电压栅极结构431的相对侧上,在衬底401中形成第四源极432和第四漏极433。第二源极422、第二漏极423、第四源极432和第四漏极433具有第二导电类型;在此示例中,第二源极422、第二漏极423、第四源极432和第四漏极433为n型。第二源极422、第二漏极423、第四源极432和第四漏极433可以与体接触区414同时形成。

75.金属硅化物449形成在漏极接触区407、源极区408、体接触区414、第一源极418、第一漏极419、第二源极422、第二漏极423、第三源极428、第三漏极429、第四源极432和第四漏极433上。用于形成金属硅化物449的示例工艺可以包括在衬底401的顶表面402上形成金属层(图4d中未示出),包括钛、镍与百分之几的铂、钴或铂,使得金属接触在漏极接触区407、源极区408、体接触区414、第一源极418、第一漏极419、第二源极422、第二漏极423、第三源极428、第三漏极429、第四源极432和第四漏极433上暴露的硅。氮化钛的覆盖层可以形成在金属层上方以提供扩散屏障。随后例如在快速热处理器中将金属层加热,使金属层与暴露的硅反应以形成金属硅化物449。金属层的未反应金属例如通过使用酸性或碱性试剂的水性溶液的湿法蚀刻来移除。金属硅化物449可以随后被退火以提供期望结晶相。

76.集成电路400的形成可以通过在衬底401的顶表面402上方形成介电层(图4中未示出)来继续,其类似于图3的介电层335。可以穿过介电层形成接触件(未在图4d中示出),类似于图4d的接触件336。可以在介电层上形成互连件(图4d中未示出),从而制作对接触件的电连接,类似于图3的互连件337。

77.图5是包括具有双阱隔离的延伸漏极mos晶体管的又一示例集成电路的横截面。集成电路500具有衬底501,该衬底501具有顶表面502并且包括具有第一导电类型的半导体材料的下层503。在此示例中,第一导电类型为n型,如图5所示。衬底501还可以包括延伸至顶表面502的场氧化物层504。场氧化物层504可以具有硅局部氧化(locos)结构,其中场氧化物层504在顶表面502之下延伸至250纳米到750纳米的深度,并且在顶表面502之上延伸至150纳米到500纳米的高度,具有锥形端部,有时被称为鸟喙,如图5所描绘。

78.集成电路500包括具有第一极性(在此示例中为n沟道)的延伸漏极mos晶体管505。延伸漏极mos晶体管505包括位于衬底501中的漏极阱506,其具有第一导电类型,在此示例中为n型。漏极阱506可以具有如参考图1的漏极阱106所公开的第一导电类型的平均掺杂剂密度。延伸漏极mos晶体管505可以可选地包括漏极接触区507,其接触漏极阱506并延伸至衬底501的顶表面502。漏极接触区507具有第一导电类型,并且可以具有如参考图1的漏极接触区107所公开的第一导电类型的平均掺杂剂密度。

79.延伸漏极mos晶体管505包括位于衬底501中的具有第一导电类型的源极区508;在此示例中,源极区508为n型。源极区508和漏极接触区507可以具有第一导电类型的掺杂剂的类似平均密度。延伸漏极mos晶体管505包括在衬底501的顶表面502上的栅极介电层509和在栅极介电层509上的栅极510。栅极510和栅极介电层509可以是参考图1的栅极110和栅极介电层109所公开的材料。栅极510从源极区508朝向漏极阱506延伸;在此示例中,栅极510与漏极阱506的一部分重叠。在此示例中,延伸漏极mos晶体管505可以包括在漏极接触区507和与栅极510重叠的漏极阱506的该部分之间的场氧化物层504a的元件。漏极阱506在场氧化物层504a的元件下方延伸,如图5所描绘。延伸漏极mos晶体管505可以包括在栅极510的侧表面上的栅极侧壁间隔件511。

80.漏极阱506通过漏极隔离阱512与下层503竖直分开,该漏极隔离阱512位于衬底501中并具有与第一导电类型相反的第二导电类型。在此示例中,漏极隔离阱512为p型,如图5所示。漏极隔离阱512接触下层503和漏极阱506。漏极隔离阱512可以具有例如10

15

cm

‑3至10

17

cm

‑3的第二导电类型的平均掺杂剂密度。如图5所示,漏极隔离阱512可以横向围绕漏极阱506,并且在漏极阱506下方完全延伸。在此示例中,漏极隔离阱512可以具有第二导电类型的较高掺杂剂密度的彼此竖直相邻的两个或更多个区512a。较高掺杂剂密度的区512a可以提供第二导电类型的掺杂剂的更均匀竖直分布,与图1的漏极隔离阱112的竖直降低的掺杂剂浓度相比,这可以有利地实现漏极阱506的围绕漏极阱506的横向周边的期望结电容和期望击穿电势。

81.源极区508通过体阱513与下层503竖直分开,该体阱513位于衬底501中并具有第二导电类型。在此示例中,体阱513为p型,如图5所示。体阱513接触下层503和源极区508。体阱513可以具有例如10

16

cm

‑3至10

18

cm

‑3的第二导电类型的平均掺杂剂密度。漏极隔离阱512的第二导电类型的平均掺杂剂密度小于体阱513的第二导电类型的平均掺杂剂密度。在此示例中,体阱513可以通过漏极隔离阱512与漏极阱506在栅极510下方分开,如图5所描绘。

延伸漏极mos晶体管505的构造(具有通过漏极隔离阱512与下层503隔离的漏极阱506,且具有通过体阱513与下层503隔离的源极区508,其中漏极隔离阱512和体阱513两者都接触下层503)可以通过消除对在延伸漏极mos晶体管505下方完全延伸的单个隔离结构的需要而有利地减小延伸漏极mos晶体管505的区域。延伸漏极mos晶体管505可以可选地包括体接触区514,其接触体阱513并延伸到衬底501的顶表面502。体接触区514具有第二导电类型,其中第二导电类型的平均掺杂剂密度为例如10

19

cm

‑3到10

21

cm

‑3以提供对体阱513的期望低电阻连接。

82.延伸漏极mos晶体管505在图5中被描绘为具有非对称构造,其中源极区508位于漏极阱506的一侧上。在此示例的替代版本中,延伸漏极mos晶体管505可以具有对称构造,其中源极区508位于漏极阱506的相对侧上。

83.集成电路500可以可选地包括具有第一极性(在此示例中为n沟道)的第一低电压mos晶体管515。第一低电压mos晶体管515具有在衬底501的顶表面502上的第一低电压栅极结构517、在衬底501中的第一源极518以及在衬底501中的第一漏极519。第一低电压mos晶体管515设置在第一阱520中,其具有第二导电类型,在此示例中为p型,如图5所示。第一阱520可以具有与体阱513基本上相等的第二导电类型的平均掺杂剂密度。

84.集成电路500还可以可选地包括具有第二极性(在此示例中为p沟道)的第二低电压mos晶体管516。第二低电压mos晶体管516具有在衬底501的顶表面502上的第二低电压栅极结构521、在衬底501中的第二源极522以及在衬底501中的第二漏极523。第二低电压mos晶体管516设置在第二阱524中,其具有第一导电类型,在此示例中为n型,如图5所示。第二阱524可以具有与漏极阱506基本上相等的第一导电类型的平均掺杂剂密度。

85.集成电路500可以可选地包括具有第一极性(在此示例中为n沟道)的第一高电压mos晶体管525。第一高电压mos晶体管525具有在衬底501的顶表面502上的第一高电压栅极结构527、在衬底501中的第三源极528以及在衬底501中的第三漏极529。第一高电压mos晶体管525设置在第三阱530中,其具有第二导电类型,在此示例中为p型,如图5所示。第三阱530可以具有与漏极隔离阱512基本上相等的第二导电类型的平均掺杂剂密度,并且可以具有与漏极隔离阱512基本上相等的第二导电类型的较高掺杂剂密度的彼此竖直相邻的两个或更多个区530a。

86.集成电路500还可以可选地包括具有第二极性(在此示例中为p沟道)的第二高电压mos晶体管526。第二高电压mos晶体管526具有在衬底501的顶表面502上的第二高电压栅极结构531、在衬底501中的第四源极532以及在衬底501中的第四漏极533。第二高电压mos晶体管526设置在第四阱534中,其具有第一导电类型,在此示例中为n型,如图5所示。

87.集成电路500可以包括在衬底501的顶表面502上方的介电层535。介电层535可以表现为pmd层,其基本上等于参考图1所公开的pmd层。集成电路500还可以包括延伸穿过介电层535的接触件536,以提供对延伸漏极mos晶体管505、第一低电压mos晶体管515、第二低电压mos晶体管516、第一高电压mos晶体管525和第二高电压mos晶体管526的电连接。接触件536可以具有参考图1的接触件136所公开的结构。集成电路500还可以包括在介电层535上的互连件537,从而制作对接触件536的电连接。

88.图6a到图6d是在又一示例形成方法的各阶段中描绘的包括具有双阱隔离的延伸漏极mos晶体管的集成电路的横截面。参考图6a,集成电路600的形成包括获取衬底601,其

可以如参考图2a的衬底201所公开的那样被实施。衬底601具有顶表面602,并且包括在顶表面602之下的半导体材料的下层603。下层603具有第一导电类型,在此示例中为n型,如图6a所示。衬底601包括用于延伸漏极mos晶体管605的区域、用于第一低电压mos晶体管615的区域、用于第二低电压mos晶体管616的区域、用于第一高电压mos晶体管625的区域以及用于第二高电压mos晶体管626的区域。如参考图1所描述的那样使用术语“低电压”和“高电压”。

89.保护层638可以形成在顶表面602上。保护层638可以具有如参考图2a的保护层238所描述的组成和结构。第一注入掩模639形成在保护层638上方。第一注入掩模639在用于延伸漏极mos晶体管605的区域中的用于随后形成的漏极隔离阱612(如图6b所示)的区域中暴露保护层638。第一注入掩模639可以可选地在用于第一高电压mos晶体管625的区域中暴露用于随后形成的第三阱630(如图6b所示)的区域。可以如参考图2a的第一注入掩模239所公开的那样形成第一注入掩模639。

90.在由第一注入掩模639暴露的区域中将第一掺杂剂641注入到衬底601中,以形成竖直排列在用于延伸漏极mos晶体管605的区域中的多个漏极隔离注入区643,且形成竖直排列在用于第一高电压mos晶体管625的区域中的阱注入区644。在此示例中,漏极隔离注入区643对应于以不同注入能量注入的第一掺杂剂641的注入。第一掺杂剂641是第二导电类型的掺杂剂,在此示例中为p型掺杂剂,诸如硼。可以10

12

cm

‑2至10

14

cm

‑2的总剂量以100kev至1000kev的注入能量注入第一掺杂剂641,以形成呈竖直排列构造的阱注入区644。在用于延伸漏极mos晶体管605的区域中具有多个漏极隔离注入区643并且在用于第一高电压mos晶体管625的区域中具有阱注入区644可以在随后形成的漏极隔离阱612(如图6b所示)中以及在随后形成的第三阱630中(如图6b所示)提供更均匀的竖直掺杂剂分布。在注入第一掺杂剂641之后移除第一注入掩模639。

91.参考图6b,衬底601通过热工艺645被加热以扩散和激活在图6a的漏极隔离注入区643和阱注入区644中的图6a的第一掺杂剂641,以分别形成漏极隔离阱612和第三阱630。热工艺645可以具有热分布,其足以充分扩散第一掺杂剂641以从漏极隔离注入区643形成连续漏极隔离阱612并且从阱注入区644形成连续第三阱630,如图6b所示。具有多个漏极隔离注入区643可以引起在漏极隔离阱612中彼此竖直相邻的较高第二导电类型的掺杂剂密度的多个区612a,其中每个区612a对应于漏极隔离注入区643。类似地,具有多个阱注入区644可以引起在第三阱630中彼此竖直相邻的较高第二导电类型的掺杂剂密度的多个区630a,其中每个区630a对应于漏极隔离注入区643。举例来说,热工艺645可以将衬底601加热至1080℃至1120℃,持续100分钟至300分钟。热工艺645可以如参考图2b所公开的那样实施。

92.参考图6c,形成场氧化物层604,其延伸到衬底601中。场氧化物层604可以通过locos工艺来形成,使得场氧化物层604具有图6c所描绘的locos结构。示例性locos工艺包括在保护层638上方形成氮化硅层,图案化氮化硅层以在用于场氧化物层604区域中暴露保护层638,通过热氧化工艺生长场氧化物层604,以及移除氮化硅层。在场氧化物层604形成之后,保护层638可以通过热氧化工艺形成的新保护材料层(诸如新的二氧化硅层)来增加。

93.可以在用于第二高电压mos晶体管626的区域中形成第四阱634。第四阱634具有第一导电类型,在此示例中为n型,如图6c所示。

94.第二注入掩模646形成在保护层638上方。第二注入掩模646在用于延伸漏极mos晶体管605的区域中的用于随后形成的体阱613的区域中暴露保护层638。第二注入掩模646可

以可选地在用于第一低电压mos晶体管615的区域中暴露用于随后形成的第一阱620的区域。可以通过与图6a的第一注入掩模639类似的工艺来形成第二注入掩模646。在由第二注入掩模646暴露的区域中将第二掺杂剂647注入到衬底601中。第二掺杂剂647是第二导电类型的掺杂剂,在此示例中为p型掺杂剂,诸如硼。可以在多于一个注入步骤中注入第二掺杂剂647,其中主要步骤具有剂量为10

12

cm

‑2至10

14

cm

‑2的磷,以400kev至600kev的能量注入。第二掺杂剂647的额外注入步骤可以具有较低的剂量和较低的能量,以设置用于延伸漏极mos晶体管605和第一低电压mos晶体管615的阈值电势。在第二掺杂剂647注入之后移除第二注入掩模646。可以通过与用于移除图6a的第一注入掩模639的工艺类似的工艺移除第二注入掩模646。

95.随后加热衬底601以激活注入到衬底601中的第二掺杂剂647,以形成体阱613和第一阱620。可以通过快速热工艺来加热衬底601,以减少第二掺杂剂647和图6a的第一掺杂剂641在漏极隔离阱612中的不希望的扩散。相比于漏极隔离阱612,体阱613具有较高的第二导电类型的平均掺杂剂密度。

96.参考图6d,在用于延伸漏极mos晶体管605的区域中,在衬底601中形成漏极阱606,使得漏极阱606通过漏极隔离阱612与下层603竖直分开。漏极阱606可以在栅极610下方部分延伸,如图6所描绘,使得漏极阱606通过漏极隔离阱612与体阱613在栅极610下方横向分开。此示例的漏极阱606被形成以便在场氧化物层604a的元件下方延伸。漏极阱606具有第一导电类型;在此示例中为n型。

97.在用于第二低电压mos晶体管616的区域中,可以在衬底601中形成第二阱624。第二阱624具有第一导电类型,并且可以形成为具有与漏极阱606类似的第一导电类型的掺杂剂的分布。漏极阱606和第二阱624可以如参考图2d的漏极阱206和第二阱224所公开的那样同时形成,从而获得降低制造成本的类似优势。图6c的保护层638随后被移除。

98.在用于延伸漏极mos晶体管605的区域中,在衬底601的顶表面602上形成栅极介电层609。延伸漏极mos晶体管605的栅极610形成在栅极介电层609上。栅极610和栅极介电层609可以如参考图2d的栅极210和栅极介电层209所公开的那样形成。在此示例中,栅极610可以从源极区608延伸到漏极阱606中的场氧化物层604a的元件。栅极侧壁间隔件611可以形成在栅极610的侧表面上。栅极侧壁间隔件611可以如参考图2d的栅极侧壁间隔件211所公开的那样形成。

99.在用于第一低电压mos晶体管615的区域中,在衬底601的顶表面602上形成第一低电压栅极结构617。在用于第二低电压mos晶体管616的区域中,在衬底601的顶表面602上形成第二低电压栅极结构621。在用于第一高电压mos晶体管625的区域中,在衬底601的顶表面602上形成第一高电压栅极结构627。在用于第二高电压mos晶体管626的区域中,在衬底601的顶表面602上形成第二高电压栅极结构631。第一低电压栅极结构617、第二低电压栅极结构621、第一高电压栅极结构627和第二高电压栅极结构631的部分或全部可以与延伸漏极mos晶体管605的栅极介电层609、栅极610和栅极侧壁间隔件611同时形成。

100.源极区608形成在衬底601中,与邻近栅极610的体阱613接触,且定位成与漏极阱606相对。源极区608具有第一导电类型;在此示例中,源极区608为n型。源极区608可以如参考图2d的源极区208所公开的那样形成。漏极接触区607可以可选地形成在衬底601中,接触漏极阱606。漏极接触区607具有第一导电类型;在此示例中,漏极接触区607为n型。漏极接

触区607可以与源极区608同时形成。在用于第一低电压mos晶体管615的区域中,在第一低电压栅极结构617的相对侧上,在衬底601中形成第一源极618和第一漏极619。在用于第一高电压mos晶体管625的区域中,在第一高电压栅极结构627的相对侧上,在衬底601中形成第三源极628和第三漏极629。第一源极618、第一漏极619、第三源极628和第三漏极629具有第一导电类型;在此示例中,第一源极618、第一漏极619、第三源极628和第三漏极629为n型。第一源极618、第一漏极619、第三源极628和第三漏极629可以与源极区608同时形成。

101.体接触区614可以可选地形成在衬底601中,接触体阱613。体接触区614具有第二导电类型;在此示例中,体接触区614为p型。体接触区614可以如参考图2d的体接触区214所公开的那样形成。在用于第二低电压mos晶体管616的区域中,在第二低电压栅极结构621的相对侧上,在衬底601中形成第二源极622和第二漏极623。在用于第二高电压mos晶体管626的区域中,在第二高电压栅极结构631的相对侧上,在衬底601中形成第四源极632和第四漏极633。第二源极622、第二漏极623、第四源极632和第四漏极633具有第二导电类型;在此示例中,第二源极622、第二漏极623、第四源极632和第四漏极633为p型。第二源极622、第二漏极623、第四源极632和第四漏极633可以与体接触区614同时形成。

102.集成电路600的形成可以通过在衬底601的顶表面602上方形成介电层(图6d中未示出)来继续,类似于图5的介电层535。可以穿过介电层形成接触件(图6d中未示出示),类似于图5的接触件536。可以在介电层上形成互连件(图6d未示出),从而制作对接触件的电连接,类似于图5的互连件537。

103.在本文公开的示例的各种特征可以在示例集成电路的其他表现形式中组合。延伸漏极mos晶体管105、305和505中的任一个可以具有对称或非对称构造,延伸漏极mos晶体管105、305和505中的任一个可以具有p沟道极性或n沟道极性,其中对第一导电类型和第二导电类型进行适当改变。延伸漏极mos晶体管105、305和505中的任一个可以在对应的漏极阱106、306和506中具有场氧化物的元件。延伸漏极mos晶体管105、305和505中的任一个可以具有sti或locos场氧化物。延伸漏极mos晶体管105、305和505中的任一个可以具有金属硅化物,并且可以具有硅化物阻挡层。漏极隔离阱112、312和512中的任一个可以根据参考图2a和图2b、图4a和图4b、图6a和图6b所公开的示例方法来形成。

104.虽然上文已经描述本公开的各种实施例,但是应当理解,它们仅通过示例而非限制的方式呈现。在不脱离本公开的精神或范围的情况下,可以根据本文的公开对所公开的实施例进行多种改变。因此,本发明的广度和范围不应受任何上述实施例的限制。而是,本公开的范围应根据所附权利要求及其等同物来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。