技术特征:

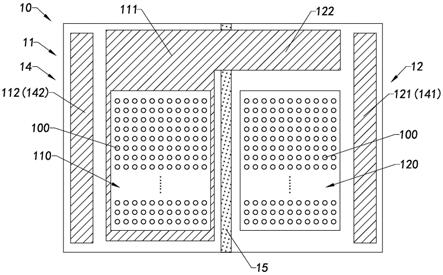

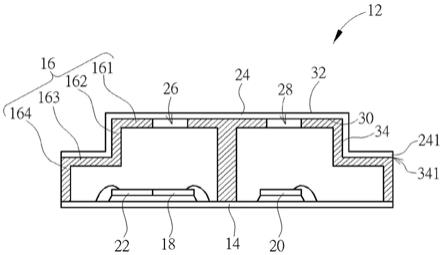

1.一种制造存储器元件的方法,其特征在于,包括:在周边区的介电层的第一叠层、阶梯区以及存储器阵列区的第一阶中的多个存储单元上形成介电层的中间叠层;刻蚀所述阶梯区和所述存储器阵列区中的所述介电层的中间叠层的一个或多个介电层;在所述周边区、所述阶梯区和所述存储器阵列区中在经刻蚀的所述介电层的中间叠层上沉积接着垫层;平坦化所述接着垫层以暴露所述介电层的中间叠层的顶面,由此经平坦化的所述接着垫层形成中央接着垫;形成介电层的第二叠层;以及刻蚀穿过所述介电层的第二叠层、所述介电层的中间叠层和所述介电层的第一叠层,以在所述阶梯区中形成阶梯,其中所述介电层的第二叠层、所述介电层的中间叠层和所述介电层的第一叠层的介电层包括不同组成的交替层。2.如权利要求1所述的制造存储器元件的方法,还包括:以介电材料填充所述阶梯上的凹陷;向下穿过所述存储器阵列区的第二阶中的所述介电层的第二叠层和所述中央接着垫刻蚀出多个存储单元孔,所述多个存储单元孔实质上与所述存储器阵列区的所述第一阶中的存储单元孔对准;在所述存储器阵列区的所述第二阶中制造多个存储单元;刻蚀出延伸穿过所述存储器阵列区的所述第二阶和所述第一阶的多个狭缝沟道;通过刻蚀出的所述多个狭缝沟道,从所述存储器阵列区和所述阶梯区中的所述介电层的第一叠层、所述介电层的中间叠层和所述介电层的第二叠层中移除一种类型的介电层;在由经移除的所述一种类型的介电层而留下的空间中形成多个栅极层;以及将导电材料沉积到所述多个狭缝沟道,以在所述存储器阵列区中形成导电狭缝。3.如权利要求2所述的制造存储器元件的方法,其中形成所述多个栅极层包括:穿过所述狭缝沟道的侧壁,从所述存储器阵列区和所述阶梯区中的所述介电层的第一叠层、所述介电层的中间叠层和所述介电层的第二叠层选择性地刻蚀所述一种类型的介电层;以及将栅极材料填充到由经刻蚀的所述一种类型的介电层产生的所述空间中,以形成所述多个栅极层,其中所述多个栅极层作为字线。4.如权利要求2所述的制造存储器元件的方法,其中制造所述多个存储单元包括:刻蚀穿过所述介电层的第二叠层和位于所述介电层的第二叠层下方的所述中央接着垫,从而形成向下的所述存储单元孔;在所述存储单元孔的内部侧壁上形成电极间介电质;在所述电极间介电质内沉积导电通道;以及在每个所述存储单元孔的中心沉积介电杆。5.如权利要求1所述的制造存储器元件的方法,其中在所述阶梯的形成期间,所述中央接着垫保持水平地嵌入在所述介电层的中间叠层中,且

其中刻蚀穿过所述介电层的第二叠层、所述介电层的中间叠层和所述介电层的第一叠层以形成所述阶梯包括重复执行以下步骤:在位于所述阶梯区上方的图案化光刻胶上,进行二维修整或最小增量层成本修整中的至少一个;以及沿经修整的所述光刻胶进行定向刻蚀穿过直到所述阶梯区中的所述介电层的第二叠层、所述介电层的中间叠层和所述介电层的第一叠层。6.一种存储器元件,其特征在于,包括:存储器阵列区,包括垂直排列的多个阶,所述多个阶的每个阶包括:多个存储单元;以及分别耦接到所述多个存储单元的多个字线;中央接着垫,位于所述多个阶的两个相邻阶之间;阶梯区,包括:阶梯,其中所述阶梯位于所述中央接着垫的一端附近,且其中所述阶梯的台阶形成在所述中央接着垫的厚度内;以及多个导电柱,与所述阶梯连接;以及周边区,包括介电层的多个叠层以及下向穿过所述介电层的多个叠层的通孔接点。7.如权利要求6所述的存储器元件,还包括位于所述存储器阵列区下方或邻近所述存储器阵列区的电路,且其中所述电路设置为控制所述存储器元件的操作。8.如权利要求6所述的存储器元件,还包括位于所述存储器元件的顶部上的多个内连线,其中所述多个内连线通过所述多个导电柱和所述阶梯区中的所述多个字线而分别连接在所述存储器阵列区中的所述多个存储单元。9.如权利要求6所述的存储器元件,其中所述导电柱中的至少一个向下延伸并接触包括导电材料的所述中央接着垫。10.如权利要求6所述的存储器元件,其中所述介电层包括一对氧化硅层和氮化硅层、一对氧化硅层和多晶硅层、一对氮化硅层和多晶硅层、一对氧化硅层和钨层以及一组氧化硅层、氮化硅层和多晶硅层中的一个。11.一种存储器元件,包括:周边区,包括介电层的多个叠层;存储器阵列区,包括垂直排列的多个阶,所述多个阶的每个阶包括:多个存储单元;以及分别耦接到所述多个存储单元的多个字线;阶梯区,包括阶梯,其中所述阶梯包括从所述存储器阵列区延伸的所述多个字线的一部分;以及中央接着垫,位于所述存储器阵列区中的所述多个阶之间,其中所述中央接着垫的顶面和底面与所述周边区中的所述介电层之间的两个相应过渡界面共面。12.如权利要求11所述的存储器元件,其中所述中央接着垫的厚度等于所述周边区中的一个或多个连续的所述介电层的厚度的总和。13.如权利要求11所述的存储器元件,其中所述中央接着垫的一端与包括所述阶梯区

中的所述阶梯的栅极层的一个或多个台阶相邻。14.如权利要求11所述的存储器元件,还包括电路,所述电路位于所述存储器阵列区下方或邻近所述存储器阵列区,且设置为执行包括存储单元行和列译码、位线预充电逻辑读取、感测放大器或时序控制的功能。15.如权利要求14所述的存储器元件,还包括:位于所述电路的顶面上的多个接触垫;内连线,位于所述周边区、所述阶梯区和所述存储器阵列区上方;以及多个通孔接点,穿过所述周边区中的所述介电层的所述多个叠层,且连接所述内连线和所述接触垫。16.如权利要求15所述的存储器元件,还包括导电柱,所述导电柱从所述内连线延伸到所述阶梯区中的所述多个字线的一端。17.如权利要求11所述的存储器元件,其中所述多个字线平行地排列且沿存储器叠层方向隔开,且其中所述多个字线设置为用作所述多个存储单元的控制栅极。18.如权利要求17所述的存储器元件,还包括位于所述多个存储单元下方的共同源极线,其中所述共同源极线设置为将所述控制栅极耦接到所述多个字线,且其中所述共同源极线由多晶硅制成并被介电层隔开。19.如权利要求11所述的存储器元件,其中所述中央接着垫由多晶硅、钨、氮化硅、氧化硅、氮氧化硅,高介电常数介电材料或硅化物制成。20.如权利要求13所述的存储器元件,其中包括所述阶梯的所述栅极层的所述一个或多个台阶不接触所述阶梯区中的任何导电柱。

技术总结

一种半导体存储器结构及其制造方法。在一方面,在第一阶中的介电层的第一叠层上形成介电层的中间叠层。然后,部分或完全刻蚀介电层的中间叠层并在其上沉积接着垫层。响应于平坦化接着垫层以暴露介电层的中间叠层的顶面,在经平坦化的接着垫层上方沉积介电层的第二叠层。通过刻蚀存储器元件的阶梯区中的介电层的第二叠层、介电层的中间叠层和介电层的第一叠层而形成阶梯。所述阶梯位于中央接着垫的一端附近,其中阶梯的台阶在中央接着垫的厚度内形成。成。成。

技术研发人员:邱建岚 郑俊民

受保护的技术使用者:旺宏电子股份有限公司

技术研发日:2020.06.03

技术公布日:2021/11/4

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。