半导体器件

1.相关申请的交叉引用

2.本技术要求于2022年3月17日在韩国知识产权局(kipo)递交的韩国专利申请no.10-2022-0033237的优先权,其公开内容通过整体引用并入本文。

技术领域

3.实施例涉及半导体器件。更具体地,实施例涉及三维半导体存储器件。

背景技术:

4.随着半导体存储器件的集成度增加,已经开发了其中存储单元在竖直方向上堆叠的三维半导体存储器件。

技术实现要素:

5.示例实施例提供了一种具有高集成度的半导体器件。

6.根据示例实施例,一种半导体器件可以包括:衬底上的第一柱状绝缘图案、衬底上的第二柱状绝缘图案、堆叠在衬底上以在竖直方向上彼此间隔开的硅图案、每个硅图案的上表面和下表面中的每个表面上的字线、接触硅图案的至少第一硅图案的第一侧壁的位线、以及接触第一硅图案的第二侧壁的电容器。第一柱状绝缘图案中的每一个可以从衬底的上表面沿竖直方向延伸。第一柱状绝缘图案可以在第一方向上彼此间隔开,并且可以排成行。第二柱状绝缘图案中的每一个可以沿竖直方向延伸。第二柱状绝缘图案可以在第一方向上彼此间隔开,并且可以排成行。第二柱状绝缘图案和第一柱状绝缘图案可以在与第一方向垂直的第二方向上彼此重叠。硅图案中的每一个可以沿第二方向延伸并位于两个第一柱状绝缘图案之间和两个第二柱状绝缘图案之间,并且硅图案中的每一个可以包括在第一方向上彼此相对并且具有直线形状的两个侧壁。每条字线可以沿第一方向延伸以与硅图案交叉。每条字线可以接触第一柱状绝缘图案中的至少一个绝缘图案和/或第二柱状绝缘图案中的至少一个绝缘图案的侧壁。位线可以沿竖直方向延伸。电容器可以沿水平方向设置,以具有水平地位于下电极和上电极之间的介电层。

7.根据示例实施例,一种半导体器件可以包括:其中存储单元层和绝缘层图案交替地堆叠在衬底上的多层堆叠结构、在竖直方向上穿过多层堆叠结构的第一柱状绝缘图案、以及在竖直方向上穿过多层堆叠结构的第二柱状绝缘图案。第一柱状绝缘图案可以在第一方向上彼此间隔开,并且可以排成行。第二柱状绝缘图案可以在第一方向上彼此间隔开,并且可以排成行。每个第二柱状绝缘图案和相应的第一柱状绝缘图案可以在与第一方向垂直的第二方向上彼此重叠。每个存储单元层可以包括硅图案和字线。硅图案可以在第一柱状绝缘图案和第二柱状绝缘图案之间,并且可以沿第二方向延伸。硅图案可以在第一柱状绝缘图案集和第二柱状绝缘图案集之间沿第二方向延伸,并且可以与第一柱状绝缘图案集和第二柱状绝缘图案集间隔开。硅图案的在第一方向上彼此相对的侧壁可以具有直线形状。字线可以在硅图案的上表面和下表面中的每个表面上。字线可以沿第一方向延伸以与硅图

案交叉。每条字线的沿第一方向延伸的至少一个侧壁可以包括凹部。

8.根据示例实施例,一种半导体器件可以包括:与衬底的表面间隔开的硅图案;字线,在硅图案的上表面和下表面中的每个表面上;硅图案中的第一杂质区,与硅图案的第一侧壁相邻;硅图案中的第二杂质区,与硅图案的第二侧壁相邻,第二侧壁与第一侧壁相对;硅图案的第一侧壁上的位线;以及硅图案的第二侧壁上的电容器。硅图案具有在第一方向上彼此相对的两个侧壁。侧壁可以具有直线形状,并且硅图案可以沿与第一方向垂直的第二方向延伸。字线可以沿第一方向延伸以与硅图案交叉。位线可以沿竖直方向延伸,并且位线可以接触第一杂质区。电容器可以沿水平方向设置,以具有水平地位于下电极和上电极之间的介电层,并且电容器可以接触第二杂质区。字线的在第二方向上彼此相对且与硅图案重叠的侧壁可以具有沿第一方向延伸的直线形状。字线的在第二方向上彼此相对且不与硅图案重叠的侧壁部分可以具有凹形,使得宽度减小。

9.在根据示例实施例的半导体器件中,用于形成存储单元的硅图案的上表面的在第一方向上的两侧可以具有直线形状,并且硅图案可以沿第二方向延伸。由于硅图案的宽度是均匀的,因此形成在硅图案上的单元器件(例如,晶体管)的特性可以是均匀的。另外,字线可以形成在硅图案的上表面和下表面中的每一个上,并且字线可以沿第一方向延伸以与硅图案交叉。字线的上表面的与硅图案重叠的在第二方向上的两个侧壁可以具有沿第一方向延伸的直线形状。字线的上表面的不与硅图案重叠的在第二方向上的两个侧壁的部分可以具有凹形,使得宽度减小。字线可以沿第一方向延伸而不在硅图案和字线的交叉点处被切割。

附图说明

10.根据以下结合附图的详细描述,将更清楚地理解示例性实施例。图1至图40表示本文所述的非限制性示例实施例。

11.图1至图3是示出了根据示例实施例的三维半导体存储器件的透视图、平面图和截面图;

12.图4是示出了图1中所示的3d半导体存储器件的硅图案的透视图;

13.图5是示出了图1中所示的3d半导体存储器件的硅图案和字线的透视图;

14.图6是示出了根据本发明实施例的三维半导体存储器件的平面图;

15.图7是示出了图6中所示的3d半导体存储器件的硅图案和字线的透视图;

16.图8是示出了根据示例实施例的三维半导体存储器件的平面图;

17.图9是示出了图8中所示的3d半导体存储器件的硅图案和字线的透视图;

18.图10是示出了根据示例实施例的三维半导体存储器件的平面图;

19.图11至图40是用于说明制造根据示例实施例的3d半导体存储器件的方法的截面图、平面图和透视图。

具体实施方式

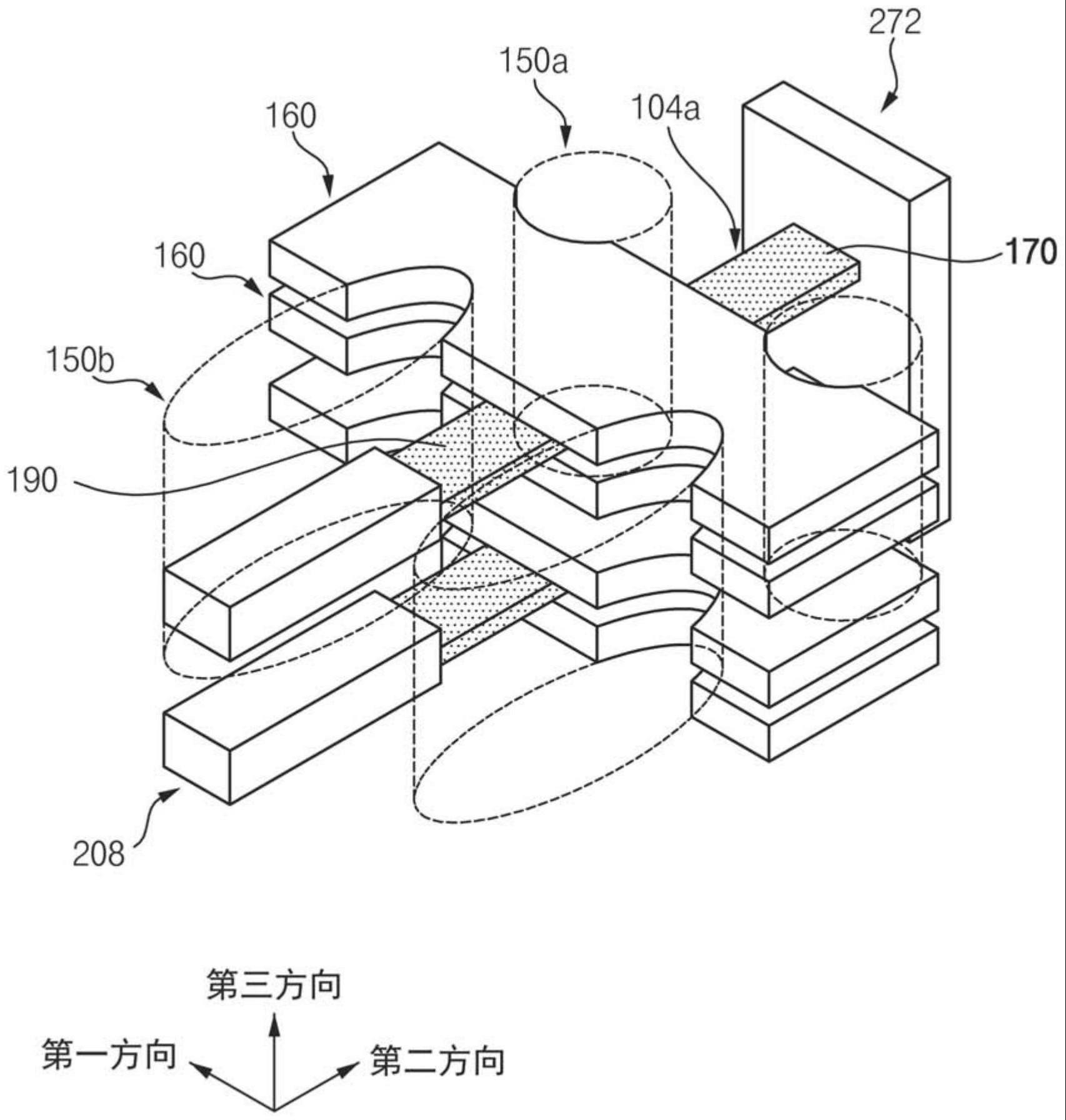

20.图1、图2和图3分别是示出了根据示例实施例的三维半导体存储器件的透视图、平面图和截面图。图4是示出了图1中所示的三维半导体存储器件的硅图案的透视图。图5是示出了图1中所示的三维半导体存储器件的硅图案和字线的透视图。

21.下面的三维半导体存储器件可以是例如dram器件。如本文中所使用的,半导体器件例如可以指诸如半导体芯片(例如,形成在管芯上的存储器芯片和/或逻辑芯片)、半导体芯片的堆叠、包括堆叠在封装衬底上的一个或多个半导体芯片的半导体封装的器件,或包括多个封装的叠层封装器件。这些器件可以使用球栅阵列、布线接合、衬底贯通孔或其他电连接元件来形成,并且可以包括诸如易失性或非易失性存储器件的存储器件。半导体封装可以包括封装衬底、一个或多个半导体芯片、以及形成在封装衬底上并覆盖半导体芯片的密封剂。各种附图示出了半导体器件的部分。

22.参考图1至图5,存储单元层10可以堆叠在硅衬底(未示出)上。存储单元层10可以在与硅衬底的表面垂直的竖直方向上彼此间隔开。每个存储单元层10可以包括晶体管和电容器208。位线172可以形成为与每个存储单元层10的晶体管的一部分电连接。

23.硅衬底可以包括例如单晶硅衬底。硅衬底可以具有(100)晶体取向。

24.晶体管可以包括硅图案104a、字线160(或一对字线160)、以及第一杂质区170和第二杂质区190。晶体管可以竖直地堆叠在硅衬底上。位线172可以沿竖直方向(例如,第三方向)延伸,并且可以接触形成在每个层中的第一杂质区170。位线172可以具有例如竖直延伸的柱形。电容器208可以接触形成在每个层中的第二杂质区190,并且可以形成在第二杂质区190的在横向方向上的侧壁上。

25.具体地,可以在硅衬底上形成其中存储单元层10和第三填充绝缘图案132在竖直方向上交替堆叠的多层堆叠结构。多层堆叠结构可以沿第一方向延伸。第一方向可以是与硅衬底的表面水平的方向,并且可以是字线的延伸方向。贯穿本说明书,当组件被描述为具有“延伸方向”或被描述为“纵向延伸”时,所述组件沿所述方向比沿其他方向延伸得更远。

26.在多层堆叠结构中,可以描述每个存储单元层10。存储单元层10可以包括硅图案104a。硅图案104a可以包括单晶硅或由单晶硅形成。硅图案104a例如可以通过外延生长工艺来形成。

27.硅图案104a可以沿与第一方向垂直且与硅衬底的表面水平的第二方向延伸。可以在硅图案104a的面向第一方向的两侧(例如,相对侧)(在下文中,第一方向上的两侧)上形成第四填充绝缘图案150c。第四填充绝缘图案150c可以包括氮化硅或可以由氮化硅形成。

28.可以在硅图案104a的表面上形成栅极绝缘层(未示出)。栅极绝缘层可以包括例如氧化硅或可以由例如氧化硅形成。

29.可以在硅图案104a上方和下方的栅极绝缘层上形成字线160。可以分别在硅图案104a的上表面和下表面上形成字线160。每条字线160可以沿第一方向延伸以与硅图案104a交叉。每条字线160可以延伸而不在硅图案104a和字线160的交叉点处被切割(例如,不在硅图案104a和字线160的交点处具有切口部分)。除非上下文另有说明,本文所使用的术语“接触”是指直接连接(即,触碰)。与硅图案104a接触并相邻的一对字线在这里可以被简单地描述为字线,因为它们可以一起用作单条字线。

30.在示例实施例中,可以在字线160的在第二方向上的一侧上形成第五填充绝缘图案164。第五填充绝缘图案164可以包括氧化硅和/或氮化硅,或可以由氧化硅和/或氮化硅形成。应当注意,“第一”、“第二”、“第三”等的序数可以简单地用作某些元件、步骤等的标签,以将这些元件、步骤等彼此区分开。在说明书中未使用“第一”、“第二”等描述的术语在权利要求中仍可被称为“第一”或“第二”。另外,用特定序数(例如,特定权利要求中的“第

一”)引用的术语可以在别处以不同的序数(例如,说明书或另一权利要求中的“第二”)来描述。

31.可以在硅图案104a的不与字线160竖直重叠且与字线160的相对侧壁相邻的边缘或端部掺杂杂质,以分别形成第一杂质区170和第二杂质区190。第一杂质区170可以形成在与字线160的第一侧相邻的硅图案104a中。第二杂质区190可以形成在与字线160的第二侧相邻的硅图案104a中。

32.包括硅图案104a、第一杂质区170和第二杂质区190、字线160和第五填充绝缘图案164的层结构可以用作存储单元的晶体管。

33.多个层结构可以布置为在竖直方向上堆叠且彼此间隔开。第三填充绝缘图案132可以形成在层结构之间。第三填充绝缘图案132可以从层结构的在第二方向上的侧壁横向地突出。第三填充绝缘图案132可以包括氧化硅或由氧化硅形成。

34.第一开口(参见图15的110)可以穿过多层堆叠结构,并且可以延伸到硅衬底的上表面。第一柱状绝缘图案150a可以分别填充第一开口110。第一柱状绝缘图案150a可以从硅衬底的上表面沿竖直方向延伸。

35.第二开口(参见图15的112)可以穿过多层堆叠结构,并且可以延伸到硅衬底的上表面。第二柱状绝缘图案150b可以分别填充第二开口112。第二柱状绝缘图案150b可以从硅衬底的上表面沿竖直方向延伸。第一柱状绝缘图案150a和第二柱状绝缘图案150b中的每一个可以包括氧化硅或由氧化硅形成。

36.第一柱状绝缘图案150a可以在第二方向上与多层堆叠结构的第一侧壁相邻。第二柱状绝缘图案150b可以在第二方向上与多层堆叠结构的与第一侧壁相对的第二侧壁相邻。

37.第一开口110可以具有孔形状,该孔形状具有第一内部宽度。在示例实施例中,第一柱状绝缘图案150a的上表面可以具有圆形。

38.第一开口110可以在第一方向上彼此间隔开,并且可以在第一方向上排成一条直线。因此,第一柱状绝缘图案150a可以在第一方向上彼此间隔开,并且可以在第一方向上排成一条直线。

39.第二开口112可以具有孔形状,该孔形状具有大于第一内部宽度的第二内部宽度。第二开口112的在第二方向上的宽度可以大于第一开口110的在第二方向上的宽度。电容器中的下电极的宽度(横向高度)可以由第二开口112的在第二方向上的宽度来确定。随着第二开口112的在第二方向上的宽度增加,电容器中的下电极的宽度可以增加。因此,每个第二开口112可以具有在第二方向上的宽度比在第一方向上的宽度大的形状。在示例实施例中,第二柱状绝缘图案150b的上表面可以具有卵形,例如椭圆形。

40.第二开口112可以在第一方向上彼此间隔开,并且可以平行布置成行。因此,第二柱状绝缘图案150b可以在第一方向上彼此间隔开,并且可以在第一方向上排成一条直线。

41.第一柱状绝缘图案150a的上表面的形状和第二柱状绝缘图案150b的上表面的形状可以彼此不同。第二柱状绝缘图案150b的上表面的在第二方向上的宽度可以比第一柱状绝缘图案150a的上表面的在第二方向上的宽度大。

42.第一柱状绝缘图案150a和第二柱状绝缘图案150b可以在第二方向上彼此面对,因此,可以在第二方向上重叠。例如,它们可以在第二方向上具有最外部,最外部在第二方向上彼此对齐。在多层堆叠结构中,一个第一柱状绝缘图案150a和一个第二柱状绝缘图案

150b可以在第二方向上彼此面对。

43.每个层结构的硅图案104a可以设置在相邻的两个第一柱状绝缘图案150a之间以及相邻的两个第二柱状绝缘图案150b之间。硅图案104a可以与第一柱状绝缘图案150a的侧壁和第二柱状绝缘图案150b的侧壁间隔开。在一个实施例中,硅图案104a不接触第一柱状绝缘图案150a的侧壁或第二柱状绝缘图案150b的侧壁。硅图案104a可以沿第二方向延伸。硅图案104a可以具有第二方向为纵向的直线形状。

44.在平面图中,硅图案104a的在第一方向上的每个侧壁(例如,在第一方向上彼此相对的侧壁)可以具有直线形状,该直线形状可以沿第二方向从硅图案104a的一端或边缘延伸至硅图案104a的相对端或边缘。硅图案104a的上表面的在第一方向上的两个边缘(即,轮廓)可以具有直线形状。硅图案104a可以用作存储单元的有源图案。

45.这样,硅图案104a可以不具有与第一柱状绝缘图案150a和第二柱状绝缘图案150b中的每个柱状绝缘图案的侧壁轮廓相同或相似的侧壁轮廓。例如,从平面图中看,硅图案104a的上表面的相对边缘可以不具有倒圆部分或不同线宽的部分,因此从平面图中看,硅图案104a的形状可以是矩形。

46.由于硅图案104a的在第一方向上的两个侧壁具有直线形状,因此硅图案104a的线宽可以是均匀的。因此,硅图案104a可以不具有局部尺寸不同的部分。因此,形成在硅图案104a上的单元器件(例如,晶体管)的电特性可以是均匀的。

47.在示例实施例中,如图24中所示,在截面图中,当从第二方向观察时,硅图案104a的沿第一方向延伸的每个侧壁可以包括凹部。

48.每个层的字线160可以沿第一方向延伸,并且可以穿过在第一柱状绝缘图案150a和相邻的柱状绝缘图案150b之间的一个或多个区域。字线160可以接触第一柱状绝缘图案150a中的至少一个第一柱状绝缘图案和/或第二柱状绝缘图案150b中的至少一个第二柱状绝缘图案的侧壁。因此,字线160的至少一个侧壁可以沿一个或多个第一柱状绝缘图案150a的侧壁轮廓和/或一个或多个第二柱状绝缘图案150b的侧壁轮廓形成。

49.在示例实施例中,在平面图中,字线160可以沿第一方向延伸,以接触第一柱状绝缘图案150a和第二柱状绝缘图案150b的侧壁。因此,字线160可以沿第一柱状绝缘图案150a的侧壁轮廓和第二柱状绝缘图案150b的侧壁轮廓形成。在平面图中,字线160包括不接触第一柱状绝缘图案150a和第二柱状绝缘图案150b的第一部分、接触第一柱状绝缘图案150a的第二部分、以及接触第二柱状绝缘图案150b的第三部分。字线160的第一部分可以具有沿第一方向延伸的直线形状。字线160的第二部分和第三部分中的每一个可以具有凹形。字线160的第二部分和第三部分中的每一个可以具有倒圆的形状。

50.这样,字线160的上表面的在第二方向上彼此相对(并沿第一方向延伸)的两个侧壁中的每一个可以包括其中字线160的宽度减小的凹部。另外,字线160可以包括相对较窄的部分(例如,边缘是凹的)和相对较宽的部分(例如,边缘是平行且直的)。

51.由于第一柱状绝缘图案150a重复地设置为在第一方向上彼此间隔开,因此字线160的第二部分可以重复地设置为在第一方向上彼此间隔开。由于第二柱状绝缘图案150b重复地设置为在第一方向上彼此间隔开,因此字线160的第三部分可以重复地设置为在第一方向上彼此间隔开。另外,字线160的第二部分和第三部分可以在第二方向上彼此相对。

52.字线160的第一部分可以具有第一宽度。在字线160中,其中第二部分和第三部分

在第二方向上彼此相对的区域可以具有小于第一宽度的第二宽度。在这种情况下,第二宽度可以沿第一方向逐渐减小,然后再次逐渐增大。

53.字线160的上表面的与硅图案104a重叠的在第二方向上的两个侧壁可以具有沿第一方向延伸的直线形状。字线160的上表面的不与硅图案104a重叠的在第二方向上的两个侧壁中的每一个可以具有凹形,使得宽度减小。因此,字线160可以在硅图案104a和字线160的重叠部分处具有第一宽度。

54.可以在硅图案104a和字线160的重叠部分的硅图案104a处形成晶体管的沟道。硅图案104a与字线160的重叠部分的面积可以是均匀的,使得每个层的晶体管的电特性可以是均匀的。硅图案104a和字线160的重叠部分可以具有第一宽度,从而可以确保每个晶体管的沟道长度为第一宽度。

55.字线160可以包括金属材料或由金属材料形成。字线160可以包括例如钨或由其形成。

56.位线172可以形成在多层堆叠结构的第一侧壁上。位线可以沿竖直方向延伸以接触每个层结构的硅图案104a的第一侧壁。位线172可以接触每个层结构的硅图案104a的第一杂质区170。位线172可以形成在沟槽的与多层堆叠结构的第一侧壁相对应的侧壁上。位线172可以在沟槽中(例如,在第一方向上)彼此间隔开。位线172可以包括金属或金属氮化物或由其形成。

57.第六填充绝缘图案174和第七填充绝缘图案178可以填充沟槽。第六填充绝缘图案174和第七填充绝缘图案178可以包括例如氧化硅或由其形成。第六填充绝缘图案174可以形成在位线172的侧壁上。第六填充绝缘图案174和第七填充绝缘图案178可以包括相同的材料,使得第六填充绝缘图案174和第七填充绝缘图案178可以合并为一个绝缘图案。

58.电容器208可以在从层结构的在第二方向的一个侧壁横向突出的第三填充绝缘图案132之间沿竖直方向形成在一间隙中。电容器208可以包括下电极200、介电层202、上电极204和板电极206。

59.在电容器208中,下电极200可以具有圆柱形。下电极200可以在每个层中沿水平方向形成。下电极200可以接触硅图案104a的第二侧壁(例如,与接触位线172的侧壁相对的侧壁)。下电极200可以接触硅图案104a的第二杂质区190。

60.介电层202可以共形地形成在下电极200的表面上。上电极204可以共形地形成在介电层202上。板电极206可以形成在上电极204上,并且可以填充具有圆柱形的下电极200的内部。板电极206可以在竖直方向上具有连接的集成结构(例如,连续竖直地延伸经过多个硅图案104a)。

61.下电极200和上电极204中的每一个可以包括诸如钛、钽、钨、铜或铝之类的金属材料、诸如氮化钛或氮化钽之类的导电金属氮化物、或诸如掺杂硅或掺杂锗之类的掺杂半导体材料,或由其形成。介电层202可以包括高k材料或由高k材料形成。例如,高k材料可以包括或可以是氧化铪、氧化铪硅、氧化镧、氧化锆、氧化锆硅、氧化钽、氧化钛、氧化钡锶钛、氧化钡钛、氧化锶钛、氧化锂、氧化铝、氧化铅钪钽、铌酸铅锌或其组合。

62.在一些示例实施例中,在电容器中,下电极可以包括具有柱形的部分。下电极可以包括在每个层中沿水平方向形成的部分。对于每个层结构,下电极可以具有杯形或圆柱形,该杯形或圆柱形具有在第二方向上与底表面相对的开口端。

63.图6是示出了根据示例实施例的三维半导体存储器件的平面图。图7是示出了图6中所示的三维半导体存储器件的硅图案和字线的透视图。

64.除了字线的形状之外,图6和图7中所示的三维半导体存储器件可以与参考图1至图5描述的三维半导体存储器件相同。

65.参考图6和图7,在平面图中,字线160可以包括不接触第一柱状绝缘图案150a和第二柱状绝缘图案150b的第一部分、以及接触第二柱状绝缘图案150b的第三部分。字线160可以不接触第一柱状绝缘图案150a,或可以仅接触第一柱状绝缘图案150a的侧壁的最外周。

66.在字线160的上表面中,字线160的与第一柱状绝缘图案150a相邻的侧壁可以具有沿第一方向延伸的直线形状。在字线160的上表面中,与第二柱状绝缘图案150b相邻的侧壁可以交替地具有直线形状和倒圆的形状。例如,字线160的第一部分可以具有直线形状,并且字线160的第三部分可以具有倒圆的形状。

67.这样,字线160的在第二方向上的两个侧壁中的至少一个可以包括倒圆的部分。

68.图8是示出了根据示例实施例的三维半导体存储器件的平面图。图9是示出了图8中所示的三维半导体存储器件的硅图案和字线的透视图。

69.除了字线的形状之外,图8和图9中所示的三维半导体存储器件可以与参考图1至图5描述的三维半导体存储器件相同。

70.参考图8和图9,在平面图中,字线160可以包括不接触第一柱状绝缘图案150a和第二柱状绝缘图案150b的第一部分、以及接触第一柱状绝缘图案150a的第二部分。字线160可以不接触第二柱状绝缘图案150b,或可以仅接触第二柱状绝缘图案150b的侧壁的最外周。

71.在字线160的上表面中,与第二柱状绝缘图案150b相邻的侧壁可以具有沿第一方向延伸的直线形状。在字线160的上表面中,与第一柱状绝缘图案150a相邻的侧壁可以交替地具有直线形状和倒圆的形状。例如,字线160的第一部分可以具有直线形状,并且字线160的第二部分可以具有倒圆的形状。

72.这样,字线160的在第二方向上的相对侧壁中的至少一个可以包括倒圆的部分。

73.图10是示出了根据示例实施例的三维半导体存储器件的平面图。

74.除了字线的形状之外,图10中所示的三维半导体存储器件可以与参考图1至图5描述的三维半导体存储器件相同。

75.参考图10,第一柱状绝缘图案151a和第二柱状绝缘图案151b中的每个柱状绝缘图案的上表面可以具有矩形。

76.在示例实施例中,第一柱状绝缘图案151a和第二柱状绝缘图案151b中的每个柱状绝缘图案的上表面可以是具有倒圆顶点的矩形。

77.在平面图中,字线160a可以包括不接触第一柱状绝缘图案151a和第二柱状绝缘图案151b的第一部分、接触第一柱状绝缘图案151a的第二部分、以及接触第二柱状绝缘图案151b的第三部分。字线160a的第一部分可以具有沿第一方向延伸的直线形状。字线160a的第二部分和第三部分可以沿第一柱状绝缘图案151a和第二柱状绝缘图案151b的侧壁形成。例如,字线160a的第二部分和第三部分中的每一个可以具有凹形,使得字线160a的宽度减小。

78.然而,在一些实施例中,类似于图6至图9,仅第一柱状绝缘图案151a或第二柱状绝缘图案151b之一可以接触字线160a。这样,字线160a的在第二方向上的两个侧壁中的至少

一个可以包括凹部。

79.第一柱状绝缘图案151a可以重复地设置为在第一方向上间隔开,使得字线160a的第二部分可以重复地设置为在第一方向上彼此间隔开。第二柱状绝缘图案151b可以重复地设置为在第一方向上彼此间隔开,使得字线160a的第三部分可以重复地设置为在第一方向上彼此间隔开。另外,字线160a的第二部分和第三部分可以在第二方向上彼此相对。

80.字线160a的第一部分可以具有第一宽度。在字线160a中,其中第二部分和第三部分在第二方向上彼此相对的区域可以具有小于第一宽度的第二宽度。

81.图11至图40是用于示出制造根据示例实施例的三维半导体存储器件的方法的截面图、平面图和透视图。

82.图11、图12和图15是透视图。图13、图16、图18、图20、图22、图26、图29、图31、图33、图36和图38是沿图11、图12和图15的i-i

′

和ii-ii

′

截取的截面图。图14、图17、图19、图21、图23、图27、图30、图32、图34、图37、图39和图40是沿图11、图12和图15的iii-iii

′

和iv-iv

′

截取的截面图。图24、图25、图28和图35是沿图11、图12和图15的v-v

′

截取的截面图。

83.图13、图16、图18、图20、图22、图26、图29、图31、图33、图36和图38是硅层和牺牲层的区域的平面图。图14、图17、图19、图21、图23、图27、图30、图32、图34、图37、图39和图40是硅图案和柱状绝缘图案的区域的竖直截面图。图24、图25、28和图35是字线的区域的竖直截面图。

84.参见图11,可以在硅衬底100上交替重复地堆叠牺牲层102和硅层104。

85.硅衬底100可以包括单晶硅衬底或可以是单晶硅衬底。硅衬底100可以是具有(100)晶体取向的硅衬底。

86.牺牲层102和硅层104可以通过外延生长工艺来形成。硅层104可以是单晶硅。牺牲层102可以用作用于形成具有单晶硅的硅层的层。在示例实施例中,硅层104的厚度可以大于牺牲层102的厚度。牺牲层可以包括例如硅锗层或可以是例如硅锗层。

87.包括硅层104和牺牲层102的堆叠层的最上层可以是硅层104。还可以在最上方硅层上形成封盖层108,以覆盖最上方硅层。封盖层108可以包括氮化硅或可以是氮化硅。

88.因此,可以在硅衬底100上形成初步堆叠结构106和在其上的封盖层108,初步堆叠结构106包括交替堆叠的牺牲层102和硅层104。

89.参考图12至图14,可以蚀刻初步堆叠结构106的部分,以形成沿第一方向延伸的第一沟槽和第二沟槽。第一沟槽和第二沟槽可以穿过初步堆叠结构106以暴露硅衬底100的上表面。初步堆叠结构106可以被第一沟槽120a和第二沟槽120b分为彼此分开的多个部分,使得可以在硅衬底100上形成沿第一方向延伸的堆叠结构106a。

90.包括堆叠结构106a的第一侧壁的沟槽被称为第一沟槽120a,并且包括堆叠结构106a的与第一侧壁相对的第二侧壁的沟槽被称为第二沟槽120b。

91.可以在第一沟槽120a和第二沟槽120b的侧壁和底部上形成第一填充绝缘图案124,以填充第一沟槽120a和第二沟槽120b。第一填充绝缘图案124可以包括氮化硅和氧化硅中的至少一种或可以由其形成。

92.参考图15至图17,可以蚀刻堆叠结构106a的部分以形成第一开口110和第二开口112。第一开口和第二开口可以穿过堆叠结构106a以暴露硅衬底100的上表面。

93.第一开口110中的每一个可以是具有第一内部宽度的孔形状。第一开口110可以在

第一方向上彼此间隔开,并且可以在第一方向上排成一条直线。

94.每个第二开口112可以具有孔形状,该孔形状具有大于第一内部宽度的第二内部宽度。每个第二开口112可以具有在第二方向上的宽度比在第一方向上的宽度大的形状。第二开口112可以在第一方向上彼此间隔开,并且可以在第一方向上排成一条直线。

95.第一开口110和第二开口112可以彼此间隔开,并且可以在第二方向上对齐。

96.根据第一开口110和第二开口112的顶部形状,可以改变随后形成的字线的侧壁的形状。根据第一开口110和第二开口112的顶部形状,可以改变随后形成的第一柱状绝缘图案和第二柱状绝缘图案的顶部形状(例如,从平面图看)。

97.例如,在平面图中,第一开口110的上部可以具有圆形,并且第二开口112的上部可以具有在第二方向上具有较长宽度的卵形(例如,椭圆形)。

98.又例如,在平面图中,第一开口和第二开口的上部可以是具有倒圆顶点的矩形。在这种情况下,可以通过后续工艺形成图10中所示的三维半导体存储器件。

99.通过后续工艺,可以在相邻的两个第一开口110与两个第二开口112之间的区域中在每个层的硅层104处形成一个存储单元。

100.堆叠结构106a中的硅层104和牺牲层102可以被第一开口110和第二开口112中的每个开口的侧壁暴露。

101.参考图18和图19,可以选择性地去除由第一开口110和第二开口112暴露的每个层的牺牲层102。可以通过各向同性蚀刻工艺去除牺牲层102以形成第一间隙128。第一间隙128可以形成在牺牲层102所形成的位置处。

102.硅层104可以被第一开口110和第二开口112的侧壁以及第一间隙128的上表面和下表面暴露。

103.参考图20和图21,可以在第一开口110和第二开口112的侧壁和底部、第一间隙128的表面以及堆叠结构上共形地形成第二填充绝缘层。第二填充绝缘层可以包括或可以是氮化硅。第二填充绝缘层可以形成在第一间隙128的上表面和下表面中的每一个上,并且可以不完全填充第一间隙128。可以通过后续工艺将第二填充绝缘层的一部分替换为字线。

104.可以在第二填充绝缘层上形成第三填充绝缘层。第三填充绝缘层可以沿第一开口110和第二开口112的侧壁共形地形成,并且可以完全填充第一间隙128。第三填充绝缘层可以包括或可以是氧化硅。

105.此后,可以去除在第一开口110和第二开口112的侧壁和底部以及堆叠结构上形成的第三填充绝缘层和第二填充绝缘层,以形成第二填充绝缘图案130和第三填充绝缘图案132。第二填充绝缘图案130和第三填充绝缘图案132可以填充第一间隙128。第三填充绝缘图案132可以在第一间隙128中介于第二填充绝缘图案130之间。

106.根据上述工艺,每个层的硅层104可以被第一开口110和第二开口112的侧壁暴露。

107.参考图22和图23,可以蚀刻硅层104的由第一开口110和第二开口112的侧壁暴露的部分,以形成硅图案104a。可以从第一开口110和第二开口112的侧壁横向地蚀刻硅层104。硅层104的蚀刻工艺可以是各向异性蚀刻工艺。

108.可以根据硅层104的暴露表面的晶体结构使用具有不同蚀刻速率的蚀刻化学品或蚀刻气体来执行各向异性蚀刻工艺。例如,各向异性工艺可以在硅层104的特定暴露表面处具有高蚀刻速率。在各向异性蚀刻工艺中,可以几乎不蚀刻第二填充绝缘图案130和第三填

充绝缘图案132。

109.取决于硅层104的被第一开口110和第二开口112的侧壁暴露的位置,硅层104可以具有不同的晶体结构。因此,硅层104的蚀刻速率可以取决于硅层104的位置而不同。可以不沿第一开口110和第二开口112的侧壁轮廓蚀刻硅层104,使得硅图案104a可以具有与第一开口110和第二开口112的侧壁轮廓的形状不同的形状。

110.可以从相邻的两个第一开口110的侧壁和相邻的两个第二开口112的侧壁各向异性地蚀刻硅层104。

111.在平面图中,通过蚀刻工艺形成的硅图案104a可以形成在相邻的两个第一开口110与相邻的两个第二开口112之间的区域中。例如,在蚀刻工艺中,硅层104的在第一方向上彼此面对的相邻两个第一开口110之间以及在第一方向上彼此面对的相邻两个第二开口112之间的部分可以以相对较低的蚀刻速率被蚀刻。另一方面,硅层104的在第一开口110和第二开口112之间的部分可以以相对较高的蚀刻速率被蚀刻。

112.因此,通过蚀刻工艺形成的硅图案104a可以具有其中第二方向为纵向的直线形状。在平面图中,硅图案104a的在第一方向上的两个侧壁可以具有基本直线的形状。硅图案104a可以用作存储单元的有源图案。由于硅图案104a的在第一方向上的两个侧壁可以具有直线形状,因此硅图案104a的上表面可以没有其中硅图案104a的面积局部地增加或减少的区域。因此,形成在硅图案104a上的单元器件(例如,晶体管)的电特性可以是均匀的。

113.在示例性实施例中,如图24中所示,在截面图中,硅图案104a的在第一方向上的侧壁可以具有凹部。由于硅层104的蚀刻速率可以取决于其竖直位置而不同,因此硅图案104a的第一方向上的侧壁可以不是竖直的。

114.在一些示例性实施例中,如图25中所示,在截面图中,硅图案104a的在第一方向上的侧壁可以是竖直的而没有凹部。在各向异性地蚀刻硅层之后,还可以执行用于去除硅图案的侧壁的凹部的后蚀刻工艺。

115.在一些示例实施例中,还可以在硅层的蚀刻之前执行预处理工艺。

116.可以在硅图案104a的两侧处形成第二间隙146。

117.参考图26至图28,可以在堆叠结构上形成填充绝缘层以填充第一开口110和第二开口112以及第二间隙146。可以平坦化填充绝缘层以在第一开口110和第二开口112以及第二间隙146中形成填充绝缘图案。填充绝缘图案可以包括氧化硅或由氧化硅形成。在下文中,形成在第一开口110中的填充绝缘图案被称为第一柱状绝缘图案150a,并且形成在第二开口112中的填充绝缘图案被称为第二柱状绝缘图案150b。形成在第二间隙146中的填充绝缘图案被称为第四填充绝缘图案150c。第四填充绝缘图案150c可以分别形成在硅图案104a的每个层的两个(例如,相对的)侧壁上。

118.参考图29和图30,可以去除填充第一沟槽120a的第一填充绝缘图案124。因此,第二填充绝缘图案130、第三填充绝缘图案132、第四填充绝缘图案150c和硅图案104a可以被第一沟槽120a的侧壁暴露。

119.参考图31和图32,可以选择性地去除第二填充绝缘图案130的一部分以形成第三间隙154。第三间隙154可以形成在其中去除了第二填充绝缘图案130的部分处。

120.第三间隙154可以限定用于在后续工艺中形成字线的区域。即,第三间隙154的在第二方向上的一端可以与字线的在第二方向上的一端在相同位置处。

121.在示例实施例中,在蚀刻工艺中,可以蚀刻第二填充绝缘图案130的一部分,使得至少第一柱状绝缘图案150a的整个表面可以被第三间隙154暴露。另外,在蚀刻工艺中,可以去除第二填充绝缘图案130的一部分,使得第二柱状绝缘图案150b的一部分可以被第三间隙154暴露。

122.在一些示例实施例中,在蚀刻工艺中,可以蚀刻第二填充绝缘图案130的一部分,使得至少第一柱状绝缘图案150a的整个表面可以被第三间隙154暴露。然而,在蚀刻工艺之后,第二柱状绝缘图案150b可以不被第三间隙154暴露,或第三间隙154可以仅接触第二柱状绝缘图案150b的最外侧壁的周边。

123.尽管未示出,但可以在硅图案104a的被第三间隙154暴露的表面上共形地形成栅极绝缘层。

124.参照图33至图35,可以在第一沟槽120a的侧壁上形成导电层以填充第三间隙154。导电层可以包括例如钨的金属材料或可以例如钨的金属材料。

125.可以去除导电层的一部分,以在第三间隙154中形成字线160。去除工艺可以包括各向同性蚀刻工艺。在去除工艺中,可以完全去除形成在第一沟槽120a的侧壁上的导电层,并且可以部分地去除第三间隙154中的导电层的与第一沟槽120a的侧壁相邻的部分以形成第四间隙162。第四间隙162可以形成在字线160的侧壁处。

126.字线160可以沿第一方向延伸。字线160可以分别形成在硅图案104a的上表面和下表面上。字线160可以延伸以与硅图案104a交叉。

127.在示例实施例中,字线160的在第二方向上的侧壁可以分别接触第一柱状绝缘图案150a和第二柱状绝缘图案150b。

128.在平面图中,可以沿第一柱状绝缘图案150a和第二柱状绝缘图案150b的侧壁轮廓形成每个层的字线160的侧壁的一部分。

129.在平面图中,字线160可以包括:不接触第一柱状绝缘图案150a和第二柱状绝缘图案150b的第一部分、接触第一柱状绝缘图案150a的第二部分、以及接触第二柱状绝缘图案150b的第三部分。字线160的第一部分可以具有沿第一方向延伸的直线形状。字线160的第二部分和第三部分中的每一个可以具有倒圆的形状。在示例实施例中,字线160的第二部分的曲率和第三部分的曲率可以彼此不同。

130.由于第一柱状绝缘图案150a重复地设置为在第一方向上彼此间隔开,因此字线160的第二部分可以重复地设置为在第一方向上彼此间隔开。由于第二柱状绝缘图案150b重复地设置为在第一方向上间隔开,因此字线160的第三部分可以重复地设置为在第一方向上彼此间隔开。字线160的第二部分和第三部分可以在第二方向上彼此相对。

131.字线160的第一部分可以具有第一宽度。在字线160中,其中第二部分和第三部分在第二方向上彼此相对的区域可以具有小于第一宽度的第二宽度。在这种情况下,第二宽度可以朝第一方向逐渐减小,然后再次逐渐增大。

132.在一些示例实施例中,在平面图中,可以不沿第一柱状绝缘图案150a的侧壁轮廓形成字线160的一个侧壁。例如,字线160的一个侧壁可以具有沿第一方向延伸的直线形状。可以通过控制导电层的蚀刻工艺来改变字线160的顶部形状。

133.第一柱状绝缘图案150a和第二柱状绝缘图案150b的上表面的形状可以改变字线160的第二部分和第三部分的形状。例如,第一柱状绝缘图案150a和第二柱状绝缘图案150b

中的每个柱状绝缘图案的上表面可以具有倒圆顶点的矩形。在这种情况下,可以沿第一柱状绝缘图案150a和第二柱状绝缘图案150b的侧壁轮廓形成字线160的第二部分和第三部分。字线160的第二部分和第三部分可以具有凹形,使得其宽度可以减小。

134.字线160的在第二方向上的两个侧壁中的至少一个可以包括凹部。

135.参考图36和图37,可以形成第五填充绝缘图案164以填充第四间隙162的一部分。第五填充绝缘图案164可以被第一柱状绝缘图案150a分开,使得第五填充绝缘图案164可以在第一方向上彼此间隔开。

136.此后,硅图案104a的由第一沟槽120a暴露的侧壁可以掺杂有杂质以形成第一杂质区170。

137.参考图38和图39,可以在第一沟槽120a中形成位线172以及第六填充绝缘图案174和第七填充绝缘图案178。位线172可以包括金属或可以由金属形成。位线172可以接触每个层的第一杂质区170。

138.位线172可以具有柱形。多条位线172可以重复地形成为在第一方向上彼此间隔开。

139.第六填充绝缘图案174和第七填充绝缘图案178可以包括或可以是氧化硅。

140.参考图40,可以去除填充在第二沟槽120b中的第一填充绝缘图案124。因此,第二填充绝缘图案130、第三填充绝缘图案132、第四填充绝缘图案150c和硅图案104a可以被第二沟槽120b的侧壁暴露。

141.此后,可以选择性地去除第二填充绝缘图案130的一部分。另外,可以去除硅图案104a的侧壁的一部分。

142.硅图案104a的暴露侧壁可以掺杂有杂质以形成第二杂质区190。因此,第一杂质区170可以形成在硅图案104a的第一侧,并且第二杂质区190可以形成在硅图案104a的第二侧。

143.此后,可以在第二杂质区190上形成下电极200。下电极200可以接触第二杂质区190,并且可以从第二杂质区190横向地突出。在示例实施例中,下电极200可以具有圆柱形。

144.可以在下电极200和第三填充绝缘图案132上共形地形成介电层202。可以在介电层202上共形地形成上电极204。可以在上电极204上形成板电极206。板电极206可以沿竖直方向延伸,并且可以完全填充第六间隙182。

145.上电极204可以包括或可以是金属材料。

146.因此,可以在第二杂质区190上形成包括下电极200、介电层202和上电极204的电容器。电容器的下电极200可以接触每个层的第二杂质区190。电容器可以沿水平方向形成在每个层中,以在下电极和上电极之间水平地具有介电层。板电极206可以在竖直方向上与上电极204连接。

147.通过上述工艺,可以制造出竖直堆叠在硅衬底上的存储单元。

148.前述内容是对示例实施例的说明,而不应被解释为对其的限制。虽然已经描述了一些示例实施例,但是本领域技术人员将容易理解,在不实质上脱离本发明构思的新颖教义和优点的情况下,可以在示例实施例中进行多种修改。因此,所有这种修改旨在被包括在如权利要求中限定的本发明构思的范围内。在权利要求中,装置加功能条款旨在包含本文描述的执行所述功能的结构,并且不仅包括结构等同物还包括等同结构。因此,应理解,前

述内容是对各种示例实施例的说明,而不应被解释成限制于所公开的具体示例实施例,并且对所公开的示例实施例的修改以及其他示例实施例旨在被包括在所附权利要求的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。