技术特征:

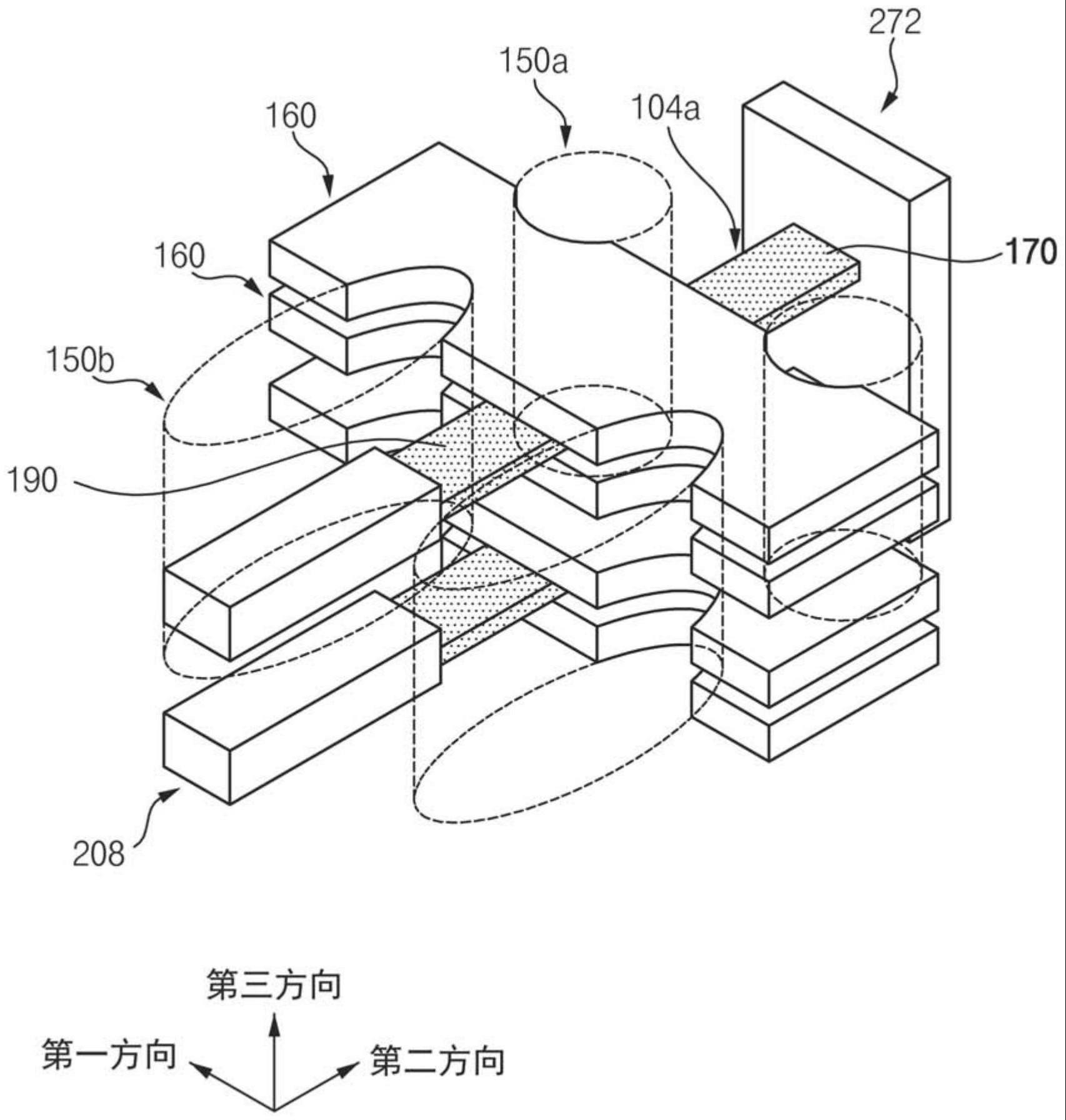

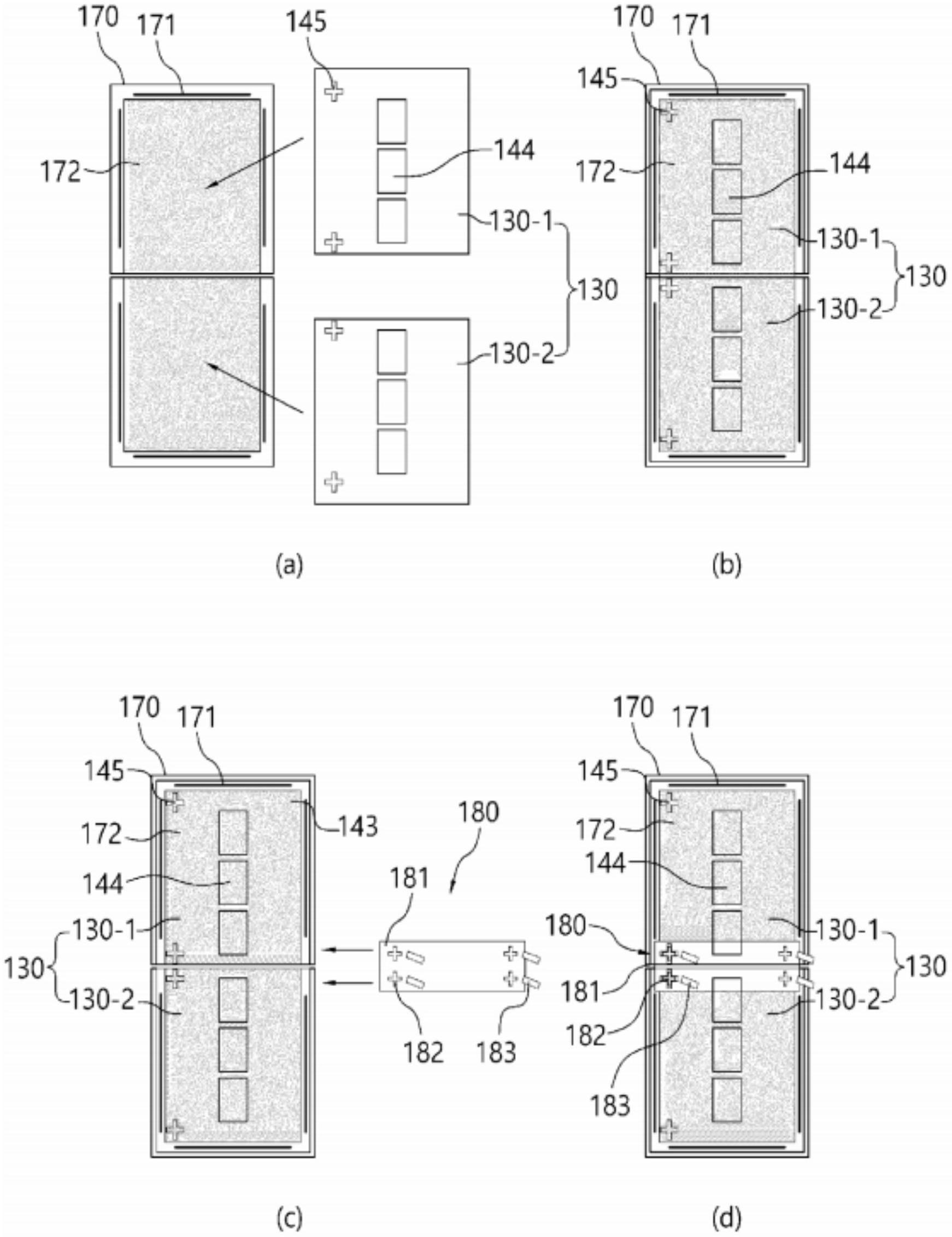

1.一种半导体器件,包括:衬底上的第一柱状绝缘图案,所述第一柱状绝缘图案中的每一个从所述衬底的上表面沿竖直方向延伸,并且所述第一柱状绝缘图案在第一方向上彼此间隔开并排列成行;所述衬底上的第二柱状绝缘图案,所述第二柱状绝缘图案中的每一个沿所述竖直方向延伸,并且所述第二柱状绝缘图案在所述第一方向上彼此间隔开并排列成行,其中,所述第二柱状绝缘图案和所述第一柱状绝缘图案在与所述第一方向垂直的第二方向上彼此重叠;堆叠在所述衬底上以在所述竖直方向上彼此间隔开的硅图案,所述硅图案中的每一个沿所述第二方向延伸并且位于两个第一柱状绝缘图案之间和两个第二柱状绝缘图案之间,并且所述硅图案中的每一个包括在所述第一方向上彼此相对并具有直线形状的两个侧壁;在每个硅图案的上表面和下表面中的每个表面上的字线,每条字线沿所述第一方向延伸以与所述硅图案交叉,并且每条字线接触所述第一柱状绝缘图案中的至少一个绝缘图案和/或所述第二柱状绝缘图案中的至少一个绝缘图案的侧壁;接触所述硅图案中的至少第一硅图案的第一侧壁的位线,所述位线沿所述竖直方向延伸;以及接触所述第一硅图案的第二侧壁的电容器,所述电容器沿水平方向设置以具有水平位于下电极和上电极之间的介电层。2.根据权利要求1所述的半导体器件,其中,沿所述第一柱状绝缘图案或所述第二柱状绝缘图案的侧壁轮廓形成所述字线的至少一个侧壁。3.根据权利要求1所述的半导体器件,其中,所述字线包括具有不接触所述第一柱状绝缘图案和所述第二柱状绝缘图案的侧壁的第一部分、具有接触所述第一柱状绝缘图案的侧壁的第二部分、以及具有接触所述第二柱状绝缘图案的侧壁的第三部分,其中,所述字线的第一部分具有沿所述第一方向延伸的直线形状的边缘,并且所述字线的第二部分和所述字线的第三部分中的每一个具有凹形的边缘。4.根据权利要求3所述的半导体器件,其中,所述字线的第一部分具有第一宽度,并且所述字线的其中所述第二部分和所述第三部分在所述第二方向上彼此重叠的区域具有小于所述第一宽度的第二宽度。5.根据权利要求1所述的半导体器件,其中,每条字线在所述字线与所述硅图案重叠的部分处具有第一宽度,并且在所述字线与所述硅图案不重叠的部分处具有小于所述第一宽度的第二宽度。6.根据权利要求1所述的半导体器件,对于每个硅图案,还包括:所述硅图案的第一端处的第一杂质区,与所述硅图案的第一边缘相邻;以及所述硅图案的第二端处的第二杂质区,与所述硅图案的第二边缘相邻,所述第二边缘与所述第一边缘相对。7.根据权利要求1所述的半导体器件,其中,所述第一柱状绝缘图案的上表面具有第一形状并且所述第二柱状绝缘图案的上表面具有第二形状,并且所述第一形状不同于所述第二形状。8.根据权利要求1所述的半导体器件,其中,每个第二柱状绝缘图案的上表面在所述第二方向上的宽度比每个第一柱状绝缘图案的上表面在所述第二方向上的宽度大。9.根据权利要求1所述的半导体器件,其中,所述第一柱状绝缘图案和所述第二柱状绝

缘图案中的上表面的形状包括椭圆形、圆形或具有倒圆顶点的矩形。10.根据权利要求1所述的半导体器件,其中,每个硅图案与所述第一柱状绝缘图案的侧壁间隔开并且与所述第二柱状绝缘图案的侧壁间隔开。11.一种半导体器件,包括:多层堆叠结构,其中,存储单元层和绝缘层图案交替地堆叠在衬底上;在竖直方向上穿过所述多层堆叠结构的第一柱状绝缘图案,所述第一柱状绝缘图案在第一方向上彼此间隔开并排列成行;以及在所述竖直方向上穿过所述多层堆叠结构的第二柱状绝缘图案,所述第二柱状绝缘图案在所述第一方向上彼此间隔开并排列成行,其中,每个第二柱状绝缘图案和相应的第一柱状绝缘图案在与所述第一方向垂直的第二方向上彼此重叠,其中,每个存储单元层包括:在第一柱状绝缘图案集和第二柱状绝缘图案集之间沿所述第二方向延伸的硅图案,所述硅图案与所述第一柱状绝缘图案集和所述第二柱状绝缘图案集间隔开,其中,所述硅图案的在所述第一方向上彼此相对的侧壁具有直线形状;以及在所述硅图案的上表面和下表面中的每个表面上的字线,每条字线沿所述第一方向延伸以与所述硅图案交叉,其中,每条字线的沿所述第一方向延伸的至少一个侧壁包括凹部。12.根据权利要求11所述的半导体器件,其中,每条字线的至少一个侧壁接触所述第一柱状绝缘图案中的至少一个绝缘图案和/或所述第二柱状绝缘图案中的至少一个绝缘图案的侧壁。13.根据权利要求11所述的半导体器件,还包括:接触每个硅图案的第一侧壁的位线,所述位线沿所述竖直方向延伸;以及对于每个硅图案,接触所述硅图案的第二侧壁的电容器,所述电容器沿水平方向设置。14.根据权利要求11所述的半导体器件,对于每个硅图案,还包括:所述硅图案的第一端处的第一杂质区,与所述硅图案的第一边缘相邻;以及所述硅图案的第二端处的第二杂质区,与所述硅图案的第二边缘相邻,所述第二边缘与所述第一边缘相对。15.根据权利要求11所述的半导体器件,其中,每个第二柱状绝缘图案的上表面在所述第二方向上的宽度比每个第一柱状绝缘图案的上表面在所述第二方向上的宽度大。16.一种半导体器件,包括:与衬底的表面间隔开的硅图案,所述硅图案具有在第一方向上彼此相对的两个侧壁,所述侧壁具有直线形状,并且所述硅图案沿与所述第一方向垂直的第二方向延伸;在所述硅图案的上表面和下表面中的每个表面上的字线,所述字线沿所述第一方向延伸以与所述硅图案交叉;所述硅图案中的第一杂质区,与所述硅图案的第一侧壁相邻;所述硅图案中的第二杂质区,与所述硅图案的第二侧壁相邻,所述第二侧壁与所述第一侧壁相对;所述硅图案的第一侧壁上的位线,所述位线沿竖直方向延伸,并且所述位线接触所述第一杂质区;以及

所述硅图案的第二侧壁上的电容器,所述电容器沿水平方向设置以具有水平位于下电极和上电极之间的介电层,所述电容器接触所述第二杂质区,其中,所述字线的在所述第二方向上彼此相对且与所述硅图案重叠的侧壁具有沿所述第一方向延伸的直线形状,以及其中,所述字线的在所述第二方向上彼此相对且不与所述硅图案重叠的侧壁部分具有使得宽度减小的凹形。17.根据权利要求16所述的半导体器件,还包括:所述衬底上的第一柱状绝缘图案,所述第一柱状绝缘图案中的每一个沿所述竖直方向延伸,所述第一柱状绝缘图案在所述第一方向上彼此间隔开并排列成行;以及所述衬底上的第二柱状绝缘图案,所述第二柱状绝缘图案中的每一个沿所述竖直方向延伸,所述第二柱状绝缘图案在所述第一方向上彼此间隔开并排列成行,其中,所述第二柱状绝缘图案和所述第一柱状绝缘图案在所述第二方向上重叠。18.根据权利要求17所述的半导体器件,其中,所述硅图案设置在第一柱状绝缘图案集和第二柱状绝缘图案集之间,并且所述硅图案与所述第一柱状绝缘图案的侧壁和所述第二柱状绝缘图案的侧壁间隔开。19.根据权利要求17所述的半导体器件,其中,所述字线接触所述第一柱状绝缘图案的至少一个侧壁和/或所述第二柱状绝缘图案的至少一个侧壁。20.根据权利要求17所述的半导体器件,其中,所述第一柱状绝缘图案的上表面具有第一形状并且所述第二柱状绝缘图案的上表面具有第二形状,并且所述第一形状不同于所述第二形状。

技术总结

一种半导体器件可以包括:衬底上的第一柱状绝缘图案,沿竖直方向延伸,在第一方向上间隔开并排列成行;衬底上的第二柱状绝缘图案,沿竖直方向延伸,在第一方向上间隔开并排列成行,第二柱状绝缘图案和第一柱状绝缘图案在与第一方向垂直的第二方向上彼此重叠;堆叠在衬底上以在竖直方向上间隔开的硅图案,沿第二方向延伸并位于两个第一柱状绝缘图案之间和两个第二柱状绝缘图案之间;每个硅图案的上表面和下表面中的每个表面上的字线,沿第一方向延伸,接触第一柱状绝缘图案和/或第二柱状绝缘图案中的至少一个的侧壁;接触硅图案中的至少第一硅图案的第一侧壁的位线,沿竖直方向延伸;及接触第一硅图案的第二侧壁的电容器,沿水平方向设置。水平方向设置。水平方向设置。

技术研发人员:任遂彬 金仁洙 孟瑞贤 朴基钟 朴壬洙 李基硕

受保护的技术使用者:三星电子株式会社

技术研发日:2023.03.06

技术公布日:2023/9/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。