一种fpga内部实现环形振荡器的方法

技术领域

1.本发明涉及可编程振荡器技术领域,特别涉及一种fpga内部实现环形振荡器的方法。

背景技术:

2.环形振荡器在行业中有多种应用,第一个主要应用是锁相环(pll),在锁相环中环形振荡器通常用作主压控振荡器(vco);环形振荡器也广泛应用于测试,包括验证制造效果和新技术;此外,这种振荡器的固有抖动可用于生成随机数序列;最后,环形振荡器可用作温度传感器,因为频率会随芯片温度发生显着变化。

3.fpga内部实现的环形振荡器结构简单,但振荡频率容易受温度、电压等环境因素影响,如果增加温度和电压检测电路和补偿电路,结构相对复杂。

4.在用altera fpga芯片进行项目开发时,某个源同步信号输入fpga,或者输出串行同步信号。由于外部走线不等长等原因,有时会遇到各个信号到达fpga不同步的问题,或输出信号到达外部器件不同步,这时可以通过quartus ii的assignment editor(约束编辑器)对某个输入或输出信号进行时间延迟设置。比如输入时,通过设置输入延迟使得到达fpga内部单元的信号能够同步。xilinx的idelay有同样的功能,每一个io上都包含一个idelay的可编程延迟语句,具有64个tap的环绕延迟单元,具有标定的tap分辨率(如xilinx 7系列每个idelay的tap延迟标定为78ps),其功能比altera cyclone系列programmable ioe delay单元更丰富。上述确定性延时单元经过厂家长期工艺验证和标定,传输延时特性受温度和电压影响很小。

技术实现要素:

5.本发明的目的在于提供一种fpga内部实现环形振荡器的方法,以解决目前环形振荡器的振荡频率容易受温度、电压等环境因素影响的问题。

6.为解决上述技术问题,本发明提供了一种fpga内部实现环形振荡器的方法,包括:

7.将fpga内部可编程延迟单元的输入输出首尾相连,或加入一级反相器,并配置成数据输入反相;或者,

8.利用可编程延迟单元的可编程抽头调节延迟值,串入多个可编程延迟单元,以实现动态调节环形振荡器的振荡频率。

9.在一种实施方式中,所述fpga内部可编程延时单元为xilinx公司fpga内部idelay单元,能直接进行互连;或为altera cyclone系列带programmable ioe delay单元,加一级反相器互连。

10.在一种实施方式中,所有可编程延迟单元的输入输出间都能通过加入反相器,或加入逻辑门电路来增加固定延迟或使能振荡控制,只要满足起振条件,即相位差180

°

。

11.在一种实施方式中,所述环形振荡器的振荡频率通过动态调节可编程延迟单元的延迟值进行控制。

12.本发明提供的一种fpga内部实现环形振荡器的方法,具有以下有益效果:

13.(1)本发明设计的环形振荡频率可动态调整;

14.(2)结构稳定性好,可靠性高,受电压、温度等外部环境因素影响小;

15.(3)结构简单,资源消耗少,fpga内部互连线少,只消耗idelay资源,不占用lut。

附图说明

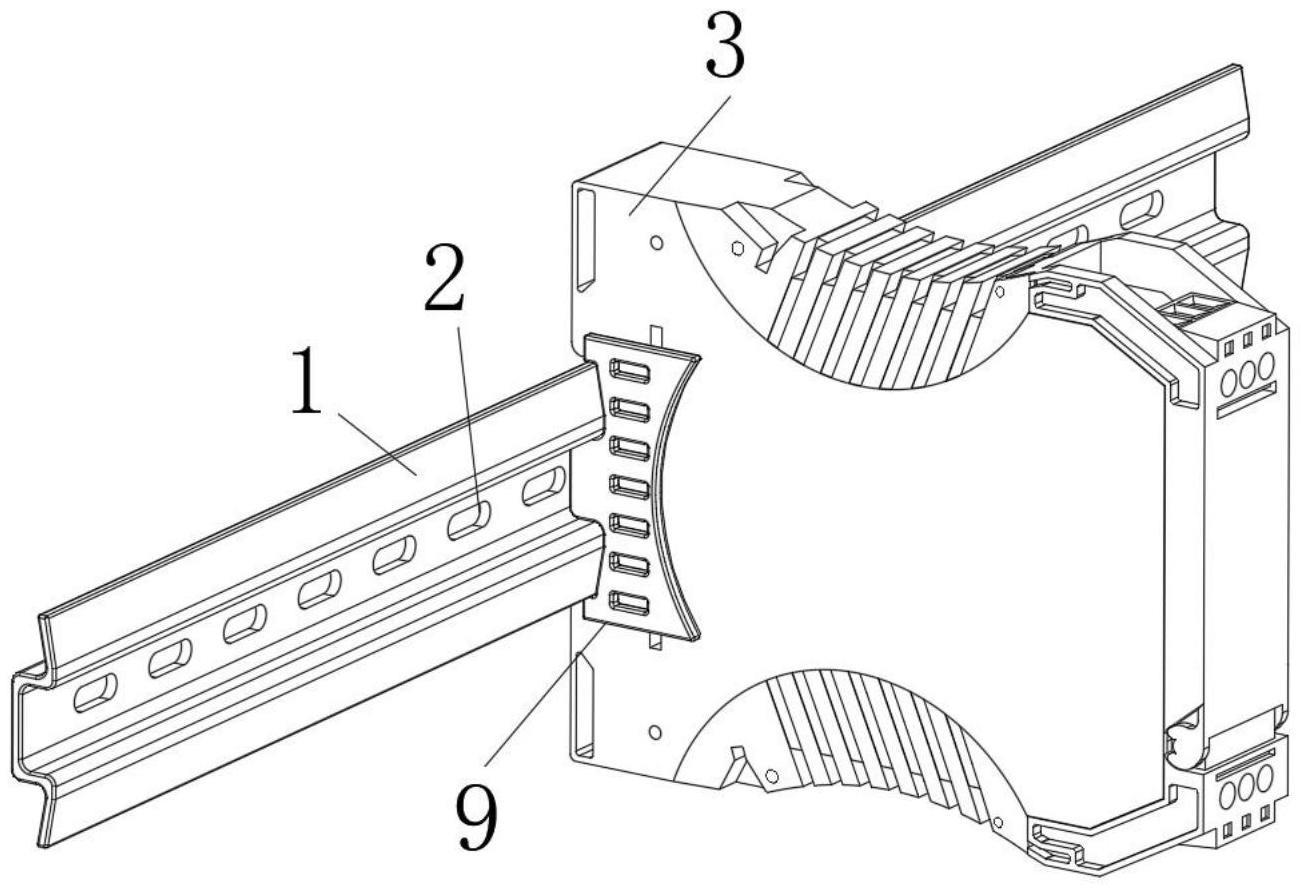

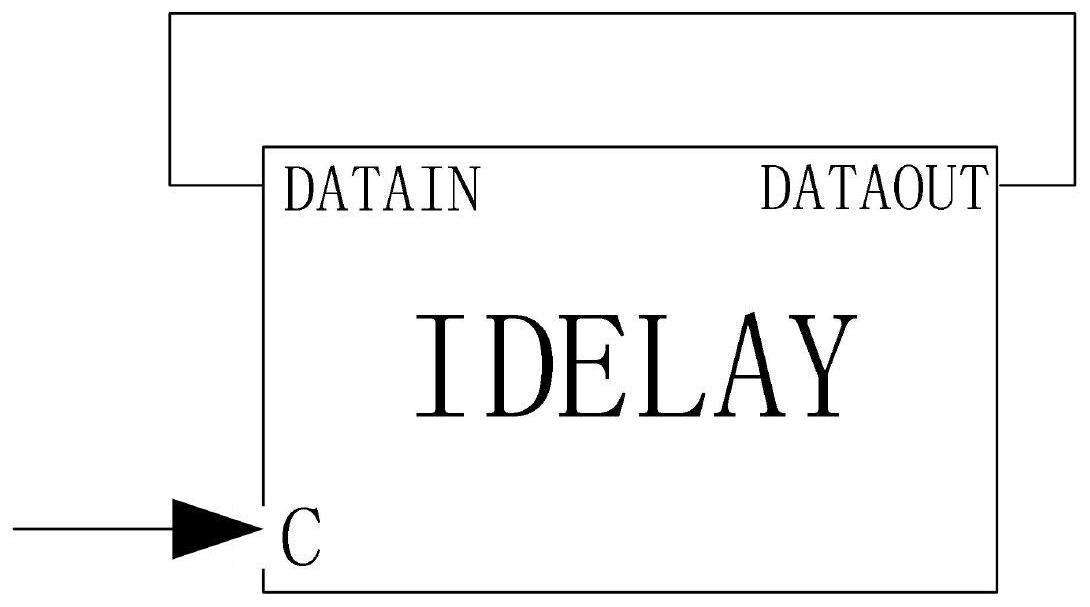

16.图1是fpga内部实现环形振荡器结构原理示意图;

17.图2是基于idelay的环形振荡器加入非门的示意图;

18.图3是基于idelay加入与非门的可控环形振荡器的示意图;

19.图4是若干idelay串联的环形振荡器的示意图。

具体实施方式

20.以下结合附图和具体实施例对本发明提出的一种fpga内部实现环形振荡器的方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

21.以xilinx的系列fpga为例,在fpga的硬件描述语言中,实例化一个idelay单元和配套的idelayctrl单元;首先对其进行初始化,利用idelay内部配置输入数据datain反相,结构最简单,整个环形振荡器延迟最小,振荡频率最高,例化和初始化示例程序见下:

22.[0023][0024]

接着,利用数据流描述将idelay的datain和dataout进行互连;最后,直接利用dataout作为环形振荡器的输出,如图1所示。在振荡器使用过程中,可通过cntvaluein[4:0]对延迟的抽头tap进行调整,从而微调振荡频率。此为本发明的最简单实现形式,可基于此变化出多种结构:

[0025]

不使用idelay内部配置输入数据datain反相功能,在dataout输出到datain的连线中串入一个非门,如图2所示;该结构在环路结构中加入了固定延迟(即反相器的延时),振荡频率降低。

[0026]

不使用idelay内部配置输入数据datain反相功能,在dataout输出到datain的连线中串入与非门,如图3所示;利用与非门的其中一个输入端作为振荡器的振荡使能控制。

[0027]

把多个idelay串起来形成环形振荡器,每一个idelay配成可调延迟的反相器(内部配置datain反相),见如图4所示;结构类似奇数个非门反相器,只是idelay使用更灵活,且延迟可调。

[0028]

以上对本发明及其实施方式进行了描述,该描述没有限制性,例如可以在dataout输出到datain的连线中加入多个非门以降低振荡频率,此时仍可以通过可编程延时单元的抽头调节振荡频率。图中所示的也只是本发明的实施方式之一,实际的结构也并不局限于此。

[0029]

总而言之如果本领域的普通技术人员受其启示,在不脱离本发明创造宗旨的情况下,不经创造性的设计出与该技术方案相似的工作方式及实施例,均应属于本发明的保护范围。

技术特征:

1.一种fpga内部实现环形振荡器的方法,其特征在于,包括:将fpga内部可编程延迟单元的输入输出首尾相连,或加入一级反相器,并配置成数据输入反相;或者,利用可编程延迟单元的可编程抽头调节延迟值,串入多个可编程延迟单元,以实现动态调节环形振荡器的振荡频率。2.如权利要求1所述的fpga内部实现环形振荡器的方法,其特征在于,所述fpga内部可编程延时单元为xilinx公司fpga内部idelay单元,能直接进行互连;或alteracyclone系列带programmableioedelay单元,加一级反相器互连。3.如权利要求2所述的fpga内部实现环形振荡器的方法,其特征在于,所有可编程延迟单元的输入输出间都能通过加入反相器,或加入逻辑门电路来增加固定延迟或使能振荡控制,只要满足起振条件,即相位差180

°

。4.如权利要求1所述的fpga内部实现环形振荡器的方法,其特征在于,所述环形振荡器的振荡频率通过动态调节可编程延迟单元的延迟值进行控制。

技术总结

本发明公开一种FPGA内部实现环形振荡器的方法,属于可编程振荡器领域。将FPGA内部可编程延迟单元的输入输出首尾相连,或加入一级反相器,并配置成数据输入反相;或者,利用可编程延迟单元的可编程抽头调节延迟值,串入多个可编程延迟单元,以实现动态调节环形振荡器的振荡频率。本发明设计的环形振荡频率可动态调整;并且结构稳定性好,可靠性高,受电压、温度等外部环境因素影响小;本发明的FPGA内部实现环形振荡器结构简单,资源消耗少,FPGA内部互连线少,只消耗IDELAY资源,不占用LUT。不占用LUT。不占用LUT。

技术研发人员:毛臻 魏敬和

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:2023.01.10

技术公布日:2023/7/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。