1.本实用新型属于脑电技术领域,具体涉及一种脑机接口感算一体装置。

背景技术:

2.脑电信号(electroencephalogram,eeg)是一种生物电信号,一般能够通过接触头部的电极采集得到,脑电信号能够直接反映大脑的相关活动,可以作为对人体大脑的探索信息来源,反映人的思维过程,也可以反映人在不同状态下的情绪变化等,由于与大脑活动的显著关系,基于脑电信号的开发和应用越来越广。

3.但由于脑电信号的无规则和非稳定性,且较心电信号、肌电信号等更加微弱,脑电信号更容易受到静电干扰、空间中射频耦合产生的高频信号干扰、工频干扰以及线缆的运动伪迹干扰,因此如何获取更优质的脑电信号,进一步提高脑电信号转化为数字信号的精度和信噪比亟待解决。

技术实现要素:

4.为了解决现有技术中存在的上述问题,本实用新型提供了一种脑机接口感算一体装置,包括:采集端、esd二极管、抗混叠滤波器、仪表放大器电路、adc、主控单元和dsp处理器,其中,所述采集端的输出端与所述esd二极管的输入端电连接,所述采集端用于采集大脑皮层发出的脑电信号,并将所述脑电信号传输经过所述esd二极管;

5.所述抗混叠滤波器的输入端与所述esd二极管的输出端电连接,所述抗混叠滤波器用于滤除空间中的电磁信号干扰;

6.所述仪表放大器电路的输入端与所述抗混叠滤波器的输出端电连接,所述仪表放大器电路用于接收所述抗混叠滤波器输出的滤除电磁信号后的脑电信号,将所述滤除电磁信号后的脑电信号进行放大,并输出放大后的模拟脑电信号;

7.所述adc的输入端与所述仪表放大器电路的输出端电连接,所述adc用于将所述放大后的模拟脑电信号转化为数字信号;

8.所述主控单元的输入端与所述adc的输出端电连接,所述主控单元用于接收所述数字信号,并对所述adc进行功能参数配置;

9.所述dsp处理器与所述主控单元电连接,所述dsp处理器用于接收所述数字信号,根据所述数字信号提取出包含脑电特征的数据,并输出所述数字信号和所述包含脑电特征的数据。

10.在本实用新型的一个实施例中,所述dsp处理器为位于所述主控单元外的独立数字信号处理器。

11.在本实用新型的一个实施例中,所述dsp处理器为集成在所述主控单元上的数字信号处理器。

12.在本实用新型的一个实施例中,所述采集端包括电极和屏蔽线,其中,所述屏蔽线的输入端与所述电极电连接,所述屏蔽线的输出端与所述esd二极管的输入端电连接,所述

屏蔽线用于将所述电极获取的所述大脑皮层发出的脑电信号传输经过所述esd二极管。

13.在本实用新型的一个实施例中,所述屏蔽线包括导线和屏蔽层,所述屏蔽层包裹在所述导线外侧。

14.在本实用新型的一个实施例中,所述导线的输入端与所述电极的输出端电连接,所述导线的输出端与所述esd二极管电连接。

15.在本实用新型的一个实施例中,所述电极包括采集电极、参考电极和接地电极,其中,

16.所述采集电极的输入端与头皮电连接,所述参考电极的输入端与皮肤电连接,所述接地电极的输入端与皮肤电连接,所述采集电极、所述参考电极和所述接地电极中的所有输出端均与所述屏蔽线的输入端电连接。

17.在本实用新型的一个实施例中,还包括主动屏蔽电路,所述主动屏蔽电路的输入端与所述抗混叠滤波器的输出端电连接,所述主动屏蔽电路的输出端与所述屏蔽层电连接。

18.在本实用新型的一个实施例中,所述数字信号为多位二进制的数字信号。

19.本实用新型具有如下有益技术效果:

20.1、本实用新型所提供的脑机接口感算一体装置,能够将脑电信号转化为数字信号,并根据该数字信号提取出包含脑电特征的数据,便于用户二次开发,通过屏蔽线、esd二极管和抗混叠滤波器的设置,提升了数字信号以及包含脑电特征的数据的精度和信噪比,同时降低了干扰,进一步提升了用户体验。

21.2、本实用新型采用主动屏蔽的方式能够有效抑制工频干扰以及线缆的运动伪迹,从而能够获取更优质的脑电信号,进一步提升脑电的数字信号的精度和信噪比。

22.3、本实用新型所提供的感算一体装置,电路体积小,功耗低,使用便捷,降低了用户的使用成本。

23.以下将结合附图及实施例对本实用新型做进一步详细说明。

附图说明

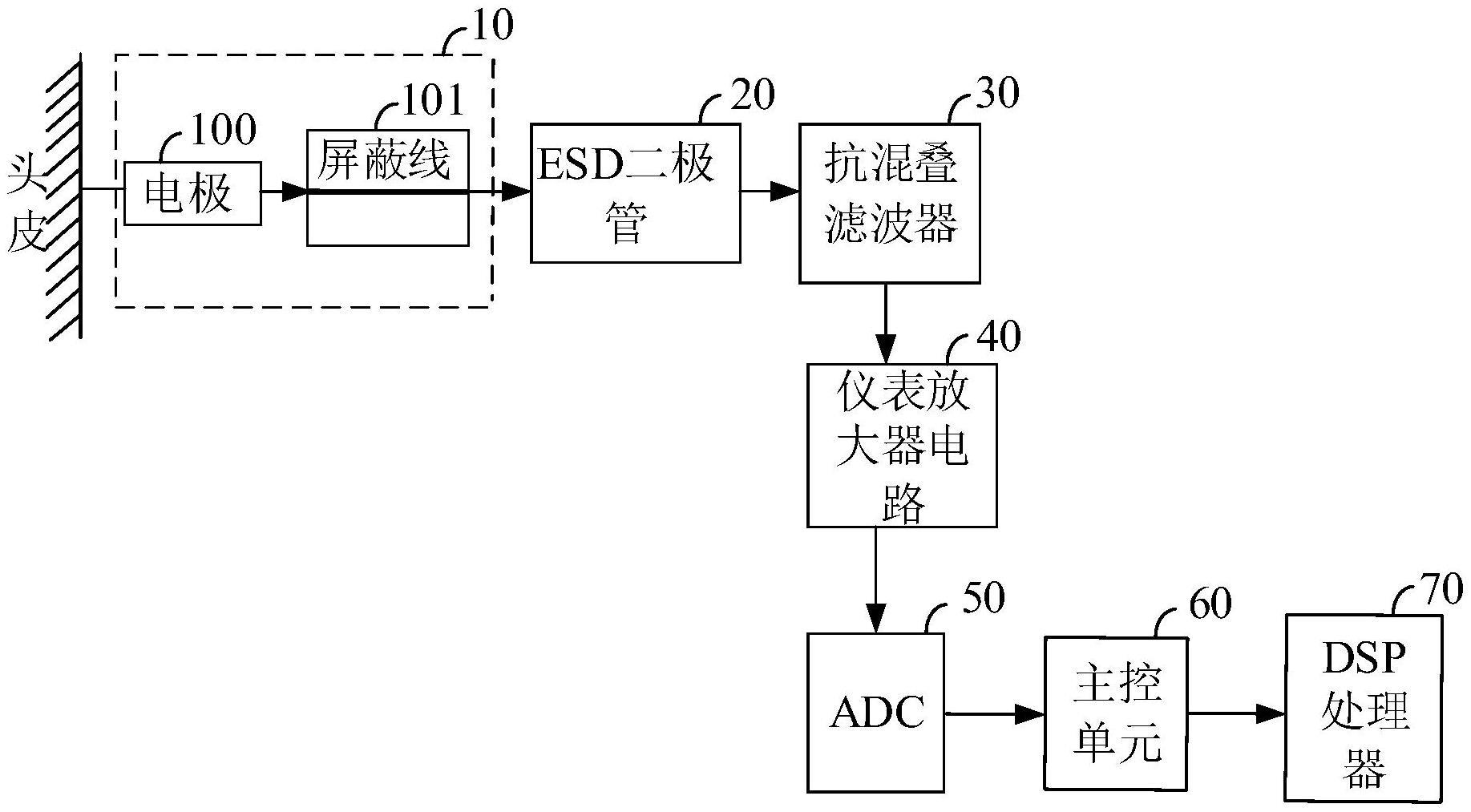

24.图1是本实用新型实施例所提供的一种脑机接口感算一体装置的结构示意图;

25.图2是本实用新型实施例所提供的一种脑机接口感算一体装置中dsp处理器与主控单元之间的位置结构示意图;

26.图3是本实用新型实施例所提供的又一种脑机接口感算一体装置的结构示意图;

27.图4是本实用新型实施例所提供的一种将脑电信号转化为包含脑电特征的数字信号的方法流程图。

28.附图标记说明:

29.10-采集端,100-电极,101-屏蔽线,20-esd二极管,30-抗混叠滤波器,40-仪表放大器电路,50-adc,60-主控单元,70-dsp处理器,80-主动屏蔽电路。

具体实施方式

30.下面结合具体实施例对本实用新型做进一步详细的描述,但本实用新型的实施方式不限于此。

31.在本实用新型的描述中,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“横向”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该申请产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

32.在本实用新型的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本实用新型的至少一个实施例或示例中。在本实用新型中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。此外,本领域的技术人员可以将本实用新型中描述的不同实施例或示例进行接合和组合。

33.尽管在此结合各实施例对本实用新型进行了描述,然而,在实施所要求保护的本实用新型过程中,本领域技术人员通过查看所述附图、公开内容、以及所附权利要求书,可理解并实现所述公开实施例的其他变化。在权利要求中,“包括”(comprising)一词不排除其他组成部分或步骤,“一”或“一个”不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

34.实施例一

35.请参见图1,图1是本实用新型实施例所提供的一种脑机接口感算一体装置的结构示意图,该脑机接口感算一体装置包括采集端10、静电放电(electro-staticdischarge,esd)二极管20、抗混叠滤波器30、仪表放大器电路40、模数转换器(analog-to-digital converter,adc)50、主控单元(master control unit,mcu)60和数字信号处理(digital signal processing,dsp)处理器70。

36.采集端10的输入端与头皮电连接,采集端10的输出端与esd二极管20的输入端电连接,采集端10用于采集大脑皮层发出的脑电信号,并将该脑电信号传输至esd二极管20。

37.具体地,本实施例的采集端10包括电极100和屏蔽线101,该电极100的输入端与头皮电连接,输出端与屏蔽线101电连接,电极100用于获取大脑皮层发出的脑电信号,该脑电信号为几十至几百微伏的低频信号,进一步地,该电极100包括采集电极、参考电极和接地电极,采集电极的输入端与头皮电连接,参考电极的输入端与皮肤电连接,接地电极的输入端与皮肤电连接,采集电极、参考电极和接地电极中所有的输出端均与屏蔽线101的输入端电连接。

38.屏蔽线101的输入端与电极100电连接,屏蔽线101的输出端与esd二极管20电连接,屏蔽线101用于将电极100获取的大脑皮层发出的脑电信号传输经过esd二极管20。

39.具体地,本实施例的屏蔽线101包括导线和屏蔽层,该屏蔽层包裹在该导线外侧,屏蔽线101中导线的输入端与电极100的输出端电连接,该屏蔽线101用于传输电极100获取的脑电信号,并通过屏蔽层消除外来的干扰信号。

40.esd二极管20的输入端与屏蔽线101中导线的输出端电连接,esd二极管20接收屏蔽线101中导线传输的脑电信号,对该脑电信号进行抗静电干扰处理。

41.具体地,esd二极管20能够防止外部的静电输入至该脑机接口感算一体装置中,当

产生静电干扰时能够将静电引入地,以免静电损坏后续电路模块的器件,使得该脑机接口感算一体装置能够承受

±

12kv的接触放电和

±

15kv的空气放电。

42.esd二极管是一种具有两个电极的半导体器件,当加在两极间的电压达到一定值时,在其间产生电场使电子移动而形成电流,相比传统的静电防护器件,esd二极管具有更快的响应时间、更低的电流值和漏电流。

43.在本实施例中,esd二极管可以是任何型号的esd二极管。

44.抗混叠滤波器30的输入端与esd二极管20的输出端电连接,由于空间中存在许多射频干扰信号和工频干扰信号,这些干扰信号会通过采集端10的线缆耦合到脑电信号中,抗混叠滤波器30用于滤除空间中耦合产生的电磁信号干扰,并且不会对脑电信号产生影响。

45.抗混叠滤波器一般指低通滤波器,用以在输出电平中把混叠频率分量降低到微不足道的程度,同时对有效的脑电信号并不会造成信号的改变。在本实施例中,抗混叠滤波器30为rc低通滤波器,在其他实施例中,该抗混叠滤波器30可以是其他类型的低通滤波器。

46.仪表放大器电路40的输入端与抗混叠滤波器30的输出端电连接,用于接收抗混叠滤波器30输出的滤除电磁信号后的脑电信号,将该脑电信号进行放大,并输出放大后的模拟脑电信号。

47.人体大脑皮层产生电信号时,当把大脑看成一个信号源,由于这个信号源输出阻抗很高,并且幅值低,输入电压偏移大,容易受到共模干扰,所以当采集eeg信号时,会使用仪表放大器,仪表放大器电路具有高共模抑制比、高开环增益、低漂移、低直流偏移等特点,在本实施例中,仪表放大器电路40可以是任意一种仪表放大器电路。

48.adc 50的输入端与仪表放大器电路40的输出端电连接,用于接收仪表放大器电路40输出的放大后的模拟脑电信号,并将该放大后的模拟脑电信号转化为多位二进制的数字信号,在本实施例中,该多位二进制的数字信号为二十四位二进制的数字信号,在其他实施例中,该多位二进制的数字信号的位数还可以是二十位、十六位、十二位中的一种。

49.在本实用新型的一个实施例中,adc 50采用三角积分模数转换器。

50.进一步地,主控单元60的输入端与adc 50的输出端电连接,主控单元60用于接收并输出adc 50输出的数字信号,主控单元60还用于对adc50进行功能参数配置,具体地,配置adc 50当前的工作模式。

51.dsp处理器70与主控单元60电连接,在本实施例中该dsp处理器70为位于主控单元60外的独立数字信号处理器,在其他实施例中,如图2所示,该dsp处理器70为集成在主控单元60上的数字信号处理器,将dsp处理器70集成在主控单元60上能够进一步减小该脑机接口感算一体装置的电路体积小。dsp处理器70用于接收主控单元60输出的数字信号,根据该数字信号提取出包含脑电特征的数据,dsp处理器70的输出端用于输出该数字信号和所述包含脑电特征的数据。

52.具体地,本实施例的dsp处理器70能够根据数字信号通过以下事件算法提取出脑电相关的特征指标,如专注度指标、放松度指标等,这些事件算法包括但不限于眨眼检测算法、运动想象算法、视觉诱发电位算法、听觉诱发电位提取算法、事件相关电位算法、错误相关电位算法、专注度算法、放松度算法。dsp处理器70输出的数字信号和包含脑电特征的数据为用户基于脑电信号的进一步开发提供了标准化接口,提高了基于脑电信号开发的工作

效率,提升了用户体验。

53.本实施例所提供的脑机接口感算一体装置,能够将脑电信号转化为数字信号,并根据该数字信号提取出包含脑电特征的数据,便于用户二次开发,通过屏蔽线101、esd二极管20和抗混叠滤波器30的设置,提升了脑电信号转化的数字信号和根据该数字信号提取的包含脑电特征的数据的精度和信噪比,同时降低了干扰,进一步提升了用户体验。

54.此外,本实施例所提供的感算一体装置,电路体积小,功耗低,使用便捷,降低了用户的使用成本。

55.实施例二

56.请参见图3,图3是本实用新型实施例所提供的又一种脑机接口感算一体装置的结构示意图,该脑机接口感算一体装置基于实施例一所提供的脑机接口感算一体装置,还包括主动屏蔽电路80。

57.主动屏蔽电路80的输入端与抗混叠滤波器30的输出端电连接,用于接收抗混叠滤波器30输出的滤除电磁信号后的脑电信号,主动屏蔽电路80的输出端与采集端10电连接,具体地,主动屏蔽电路80的输出端与屏蔽线101的屏蔽层电连接。通过设置主动屏蔽电路80能够将主动屏蔽电路80的输入信号和输出信号隔离开,主动屏蔽电路80将输出的脑电信号作用在屏蔽线101的屏蔽层上,能够有效抑制外接的工频干扰以及线缆的运动伪迹。

58.通过比较发现,在主动屏蔽、不屏蔽、接地屏蔽和屏蔽层接偏置电路的四种场景下,滤除耦合干扰后的脑电信号在主动屏蔽的情况下受工频干扰和运动伪迹干扰的影响最低,本实用新型采用主动屏蔽的方式能够有效抑制工频干扰以及线缆的运动伪迹,从而能够获取更优质的脑电信号,进一步提升了数字信号以及包含脑电特征的数据的精度和信噪比,同时降低了干扰。

59.请参见图4,图4是本实用新型实施例所提供的一种将脑电信号转化为包含脑电特征的数字信号的方法流程图,该方法流程包括:

60.s10、通过电极采集脑电信号;

61.通过采集端10与头皮的接触获取原始的脑电信号,该脑电信号为几十至几百微伏的低频信号。

62.s20、对脑电信号进行抗静电干扰处理;

63.通过esd二极管20对采集端10获取的原始的脑电信号进行抗静电干扰处理,尤其是接触放电和空气放电。

64.s30、滤除空间中射频耦合产生的干扰信号;

65.抗混叠滤波器30能够将空间中射频耦合产生的干扰信号滤除掉,并且不会对脑电信号产生影响,接收抗混叠滤波器30输出滤除耦合干扰后的脑电信号,将该滤除耦合干扰后的脑电信号输出至仪表放大器电路40,然后继续步骤s50。

66.可选地,抗混叠滤波器30将该滤除耦合干扰后的脑电信号输出至仪表放大器电路40的同时将该滤除耦合干扰后的脑电信号输出至主动屏蔽电路80,然后进入步骤s40。

67.s40、抑制外接的工频干扰以及线缆的运动伪迹;

68.主动屏蔽电路80接收抗混叠滤波器30输出的滤除耦合干扰后的脑电信号,将输出的脑电信号作用在屏蔽线101的屏蔽层上,能够有效抑制外接的工频干扰以及线缆的运动伪迹。

69.s50、对脑电信号进行放大处理;

70.仪表放大器电路40接收滤除耦合干扰后的脑电信号,将该滤除耦合干扰后的脑电信号放大后输出。

71.s60、将脑电信号转化为数字信号;

72.adc 50接收仪表放大器电路40输出的放大后的模拟脑电信号,并将该放大后的模拟脑电信号转化为数字信号。

73.s70、根据数字信号提取出包含脑电特征的数据。

74.主控单元60接收adc 50输出的数字信号,并将该数字信号输出至dsp处理器70,dsp处理器70根据该数字信号提取出包含脑电特征的数据,并通过定制的接口和协议输出该数字信号以及包含脑电特征的数据。

75.本实用新型所提供的脑机接口感算一体装置,能够将脑电信号转化为数字信号,并根据该数字信号提取出包含脑电特征的数据,通过定制的接口和协议将数据发送出去,便于用户二次开发,通过屏蔽线、esd二极管和抗混叠滤波器的设置,提升了数字信号以及包含脑电特征的数据的精度和信噪比,同时降低了干扰,进一步提升了用户体验。

76.并且,本实用新型采用主动屏蔽的方式能够有效抑制工频干扰以及线缆的运动伪迹,从而能够获取更优质的脑电信号,进一步提升数字信号以及包含脑电特征的数据的精度和信噪比。

77.此外,本实用新型所提供的感算一体装置,电路体积小,功耗低,使用便捷,降低了用户的使用成本。

78.以上内容是结合具体的优选实施方式对本实用新型所作的进一步详细说明,不能认定本实用新型的具体实施只局限于这些说明。对于本实用新型所属技术领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本实用新型的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。