1.本发明涉及显示装置,涉及具备氧化物晶体管的显示装置。

背景技术:

2.显示装置包括多个像素以及控制多个像素的驱动电路(例如,扫描驱动电路以及数据驱动电路)。多个像素各自包括显示元件以及控制显示元件的像素的驱动电路。像素的驱动电路可以包括有机连接的多个晶体管。

3.扫描驱动电路及/或数据驱动电路可以通过与多个像素相同的工艺而形成。扫描驱动电路及/或数据驱动电路可以包括有机连接的多个晶体管。

技术实现要素:

4.本发明的目的在于提供一种显示质量提高的显示装置。

5.根据本发明的一实施例的显示装置包括:显示面板,包括:多个绝缘层;第一像素,与向第一方向延伸的第一数据线以及向与所述第一方向交叉的第二方向延伸的第一扫描线电连接;以及第二像素,与第二数据线以及所述第一扫描线电连接。可以是,所述第一像素包括:发光二极管,包括与第一节点电接通的第一电极、接收第一电源电压的第二电极以及配置在所述第一电极和所述第二电极之间的发光层;第一晶体管,包括源极、漏极、半导体区域以及与第二节点电连接的栅极,并在接收第二电源电压的第一电压线和所述第一节点之间电接通;第二晶体管,在所述第一数据线和所述第二节点之间电接通;第三晶体管,在所述第二节点和接收第一电压的第二电压线之间电接通;第一电容器,在所述第一节点和所述第二节点之间电接通;第四晶体管,在接收第二电压的第三电压线和所述第一节点之间电接通;第五晶体管,在所述第一电压线和所述第一晶体管的所述漏极或者所述源极之间电接通;以及第二电容器,在所述第一电压线和所述第一节点之间电接通。所述多个绝缘层包括第一绝缘层以及配置在所述第一绝缘层上的第二绝缘层,所述第一晶体管的所述栅极配置在所述第一绝缘层的下侧,定义所述第一电容器的第一电极的第一导电性图案配置在所述第一绝缘层的下侧,定义所述第一电容器的第二电极以及所述第二电容器的第一电极的第二导电性图案配置在所述第一绝缘层和所述第二绝缘层之间,定义所述第二电容器的第二电极的第三导电性图案配置在所述第二绝缘层的上侧,所述第一数据线配置在所述第二绝缘层的上侧。

6.可以是,根据本发明的一实施例,在所述第二方向中,所述第二导电性图案配置在所述第一数据线和所述第二数据线之间,与所述第二导电性图案重叠的所述第三导电性图案的一部分区域配置在所述第一数据线和所述第二数据线之间。

7.可以是,根据本发明的一实施例,在所述第三导电性图案的内侧界定开口部。

8.可以是,根据本发明的一实施例,通过所述开口部的连接电极将所述第二导电性图案和所述发光二极管的所述第一电极电连接。

9.可以是,根据本发明的一实施例,在平面上观察时,所述第一导电性图案和所述第

二导电性图案配置在所述第三导电性图案的内侧。

10.可以是,根据本发明的一实施例,所述第五晶体管的漏极或者源极通过贯穿所述第一绝缘层以及所述第二绝缘层的第一接触孔与所述第三导电性图案连接。

11.可以是,根据本发明的一实施例,所述第三导电性图案包括:电极部分,在平面上观察时,与所述第一导电性图案重叠;以及第一连接部分,从所述电极部分向所述第一方向延伸,并与所述第一接触孔重叠。

12.可以是,根据本发明的一实施例,所述多个绝缘层还包括配置在所述第二绝缘层上的第三绝缘层。可以是,所述第一电压线配置在所述第三绝缘层上,并通过贯穿所述第三绝缘层的第二接触孔与所述第三导电性图案连接。

13.可以是,根据本发明的一实施例,所述第三导电性图案还包括:第二连接部分,从所述电极部分向所述第二方向延伸,并与所述第二接触孔重叠。

14.可以是,根据本发明的一实施例,所述显示面板还包括:导电性图案,与所述第一晶体管的所述半导体区域重叠,并配置在所述第一晶体管的所述半导体区域的下侧。可以是,所述半导体区域包含金属氧化物。

15.可以是,根据本发明的一实施例,所述导电性图案与所述第三导电性图案电连接。

16.可以是,根据本发明的一实施例,所述显示面板还包括多个导电性图案。可以是,所述第二晶体管至所述第五晶体管各自包括漏极、源极、半导体区域以及栅极。可以是,所述半导体区域包含金属氧化物。可以是,所述多个导电性图案配置在所述半导体区域的下侧,所述第二晶体管至所述第五晶体管各自的所述半导体区域与所述多个导电性图案中的相对应的导电性图案重叠。

17.可以是,根据本发明的一实施例,所述第二晶体管至所述第五晶体管各自的所述栅极与所述相对应的导电性图案电连接。

18.可以是,根据本发明的一实施例,所述第一像素还包括:第三电容器,接通在所述发光二极管的所述第一电极和所述第二电极之间。

19.可以是,根据本发明的一实施例,所述显示面板还包括:第四电压线,配置在所述第二绝缘层上,并向所述第二方向延伸且接收所述第一电源电压。可以是,所述第二电压线以及所述第三电压线配置在与所述第四电压线相同的层上。

20.可以是,根据本发明的一实施例,所述显示面板还包括多个导电性图案。可以是,所述第二电压线至所述第四电压线各自与所述多个导电性图案中的相对应的导电性图案重叠,所述多个导电性图案配置在所述第二电压线至所述第四电压线的下侧。

21.可以是,根据本发明的一实施例的显示装置包括:发光二极管,包括第一电极、接收第一电源电压的第二电极以及配置在所述第一电极和所述第二电极之间的发光层;开关晶体管,输出与从数据线接收的数据信号相对应的电压;第一电容器,储存从所述开关晶体管接收的电压;驱动晶体管,控制所述发光二极管的电流量以与储存于所述第一电容器的电压相对应;以及第二电容器,接通在接收比所述第一电源电压高的电平的第二电源电压的电压线和所述驱动晶体管的输出端子之间。

22.可以是,根据本发明的一实施例,所述驱动晶体管的栅极配置在第一绝缘层的下侧,定义所述第一电容器的第一电极的第一导电性图案配置在所述第一绝缘层的下侧,定义所述第一电容器的第二电极以及所述第二电容器的第一电极的第二导电性图案配置在

所述第一绝缘层的上侧,定义所述第二电容器的第二电极的第三导电性图案配置在覆盖所述第二导电性图案的第二绝缘层的上侧,所述数据线配置在所述第二绝缘层的上侧。

23.可以是,根据本发明的一实施例,在平面上观察时,所述第一导电性图案和所述第二导电性图案配置在所述第三导电性图案的内侧。

24.可以是,根据本发明的一实施例,在所述第三导电性图案的内侧界定开口部。

25.可以是,根据本发明的一实施例,所述显示装置还包括与所述第一电容器并联连接的第三电容器。可以是,所述第一导电性图案定义所述第三电容器的第一电极,定义所述第三电容器的第二电极的第四导电性图案配置在所述第一导电性图案的下侧,并与所述第一导电性图案重叠。

26.根据上述情况,在显示面板的厚度方向中驱动晶体管的栅极和数据线之间的距离相对增加。可以减小驱动晶体管的栅极和数据线之间的耦合。

27.接收第二电源电压的第三导电性图案可以阻止驱动晶体管的栅极和数据线的耦合。另外,驱动晶体管的栅极和第三导电性图案之间的距离相对增加,从而可以减小它们之间的寄生电容。

28.随着驱动晶体管的栅极和数据线之间的距离增加,可以防止数据信号引起驱动晶体管的栅极-源极电压变动。可以减小根据像素的位置显示的亮度偏差。

29.第一电容器和第四电容器并联连接。即便发生驱动晶体管的栅极和数据线之间的耦合,由于存储电容器的容量增加,因此减小数据信号引起的驱动晶体管的栅极-源极电压的变动性。

附图说明

30.图1是根据本发明的一实施例的显示装置的框图。

31.图2是根据本发明的一实施例的像素的等效电路图。

32.图3是用于驱动图2中示出的像素的驱动信号的波形图。

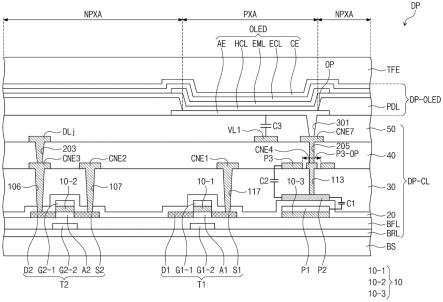

33.图4是与根据本发明的一实施例的像素相对应的显示面板的截面图。

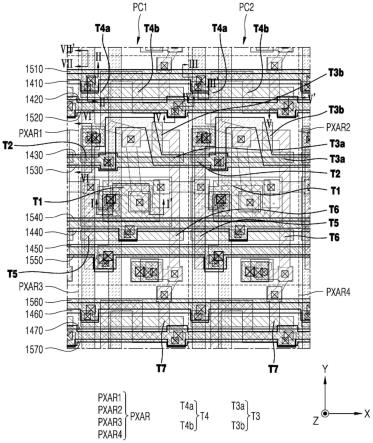

34.图5是根据本发明的一实施例的像素的平面图。

35.图6a至图6h是基于根据本发明的一实施例的像素中包括的图案的叠层顺序的平面图。

36.图7是根据本发明的一实施例的像素的等效电路图。

37.图8是与根据本发明的一实施例的像素相对应的显示面板的截面图。

38.图9a以及图9b是基于根据本发明的一实施例的像素中包括的图案的叠层顺序的平面图。

39.(附图标记说明)

40.dlj:第j个数据线(相当于权利要求书中的第一数据线)

41.dlj 1:第j 1个数据线(相当于权利要求书中的第二数据线)

42.sl1i:第i个扫描线(相当于权利要求书中的第一扫描线)

43.pxij:像素(相当于权利要求书中的第一像素)

44.pxij 1:像素(相当于权利要求书中的第二像素)

45.nd1:第一节点(相当于权利要求书中的第二节点)

46.nd2:第二节点(相当于权利要求书中的第一节点)

47.elvss:第一电源电压

48.oled:发光二极管

49.t1~t5:第一至第五晶体管

50.c1:第一电容器

51.c2:第二电容器

52.vref:第一电压

53.vl2:第二电压线(相当于权利要求书中的第一电压线)

54.vl3:第三电压线(相当于权利要求书中的第二电压线)

55.vl4:第四电压线(相当于权利要求书中的第三电压线)

56.vint:第二电压

57.20:第二绝缘层(相当于权利要求书中的第一绝缘层)

58.30:第三绝缘层(相当于权利要求书中的第二绝缘层)

59.g1-1:第一晶体管的栅极

60.p1:第一导电性图案

61.e1-1:第一电容器的第一电极

62.e1-2:第一电容器的第二电极

63.e2-2:第二电容器的第二电极

64.p2:第二导电性图案

具体实施方式

65.在本说明书中,当提及某构成要件(或者区域、层、部分等)“在”其它构成要件“上”、“连接”或者”结合”于其它构成要件时,其意指某构成要件可以直接配置/连接/结合于其它构成要件上或者也可以在它们之间配置有第三构成要件。

66.相同的附图标记指代相同的构成要件。另外,在附图中,构成要件的厚度、比例以及尺寸是为了技术内容的有效说明而放大的。“及/或”将相关的构成要件所能定义的一个以上的组合全部包括。

67.第一、第二等术语可用于说明各种构成要件,但上述构成要件并不被上述术语所限制。上述术语仅用于将一个构成要件与其它构成要件区分的目的。例如,在不脱离本发明的权利范围的情况下,第一构成要件可以命名为第二构成要件,类似地,第二构成要件也可以命名为第一构成要件。只要在文脉上没有明确表示为不同,单数表述包括复数的表述。

68.另外,“下方”、“下侧”、“上方”、“上侧”等术语用于说明附图中示出的构成要件的关联关系。上述术语是相对性概念,以附图中表示的方向为基准进行说明。

[0069]“包括”或者“具有”等术语应理解为用于指定说明书中所记载的特征、数字、步骤、工作、构成要件、部件或者它们的组合的存在,并不是预先排除一个或其以上的其它特征、或者数字、步骤、工作、构成要件、零部件或者它们的组合的存在或者附加可能性。

[0070]

只要没有不同地定义,本说明书中使用的所有术语(包括技术术语以及科学术语)具有与本发明所属技术领域的技术人员通常所理解的含义相同的含义。另外,通常使用的词典中所定义的术语之类的术语应解释为具有与相关技术的脉络上含义相同的含义,只要

没有解释为理想或过于形式化的含义,则在此明确地定义。

[0071]

以下,参照附图说明本发明的实施例。

[0072]

图1是根据本发明的一实施例的显示装置dd的框图。显示装置dd包括时序控制部tc、扫描驱动电路sdc、数据驱动电路ddc以及显示面板dp。在本实施例中,显示面板dp以发光型显示面板进行说明。发光型显示面板可以包括有机发光显示面板或者无机发光显示面板。

[0073]

时序控制部tc接收输入图像信号,并将输入图像信号的数据格式转换成与数据驱动电路ddc的接口规格匹配,从而生成图像数据d-rgb。时序控制部tc输出图像数据d-rgb和各种控制信号dcs、scs。

[0074]

扫描驱动电路sdc从时序控制部tc接收扫描控制信号scs。扫描控制信号scs可以包括开始扫描驱动电路sdc的工作的垂直起始信号、确定信号的输出时期的时钟信号等。扫描驱动电路sdc生成多个扫描信号,并依次输出至相对应的扫描线sl11~sl1n。另外,扫描驱动电路sdc响应于扫描控制信号scs而生成多个发光控制信号,并将多个发光控制信号输出至相对应的发光信号线el1至eln。

[0075]

在图1中示出为多个扫描信号和多个发光控制信号从一个扫描驱动电路sdc输出的情况,然而本发明不限于此。在本发明的一实施例中,显示装置dd可以包括多个扫描驱动电路。另外,在本发明的一实施例中,生成多个扫描信号进行输出的驱动电路和生成多个发光控制信号进行输出的驱动电路可以分开形成。

[0076]

数据驱动电路ddc从时序控制部tc接收数据控制信号dcs以及图像数据d-rgb。数据驱动电路ddc将图像数据d-rgb转换为数据信号,将数据信号输出至后述的多个数据线dl1~dlm。数据信号为与图像数据d-rgb的灰度值相对应的模拟电压。

[0077]

显示面板dp可以包括多个组的扫描线。图1中示例性示出第一组的扫描线sl11~sl1n。显示面板dp包括发光信号线el1至eln、数据线dl1~dlm、第一电压线vl1、第二电压线vl2、第三电压线vl3、第四电压线vl4以及多个像素px。

[0078]

第一组的扫描线sl11~sl1n可以向第一方向dr1延伸,并向第二方向dr2排列。数据线dl1~dlm可以与第一组的扫描线sl11~sl1n交叉。

[0079]

第一电压线vl1接收第一电源电压elvss。第二电压线vl2接收第二电源电压elvdd。第二电源电压elvdd具有比第一电源电压elvss高的电平。第三电压线vl3接收基准电压vref(以下,第一电压)。第四电压线vl4接收初始化电压vint(以下,第二电压)。第一电压vref具有比第二电源电压elvdd低的电平。第二电压vint具有比第二电源电压elvdd低的电平。在本实施例中,第二电压vint可以具有比第一电压vref以及第一电源电压elvss低的电平。

[0080]

第一电压线vl1、第二电压线vl2、第三电压线vl3以及第四电压线vl4中的至少任一个可以包括向第一方向dr1延伸的线和向第二方向dr2延伸的线中的至少一个。电压线的向第一方向dr1延伸的线和向第二方向dr2延伸的线即便配置在图4中示出的多个绝缘层10~40中的彼此不同的层上,也可以彼此电连接。

[0081]

以上,参照图1说明了根据一实施例的显示装置dd,然而本发明的显示装置dd不限于此。根据像素驱动电路的结构,可以还增加或省略信号线。另外,也可以改变一个像素px和信号线的电连接关系。

[0082]

多个像素px可以包括生成彼此不同的彩色光的多个组。例如,可以包括生成红色光的红色像素、生成绿色光的绿色像素以及生成蓝色光的蓝色像素。红色像素的发光二极管、绿色像素的发光二极管以及蓝色像素的发光二极管可以包括彼此不同的物质的发光层。

[0083]

像素驱动电路可以包括多个晶体管和至少一个电容器。扫描驱动电路sdc和数据驱动电路ddc中的至少任一个可以包括通过与像素驱动电路相同的工艺形成的多个晶体管。

[0084]

可以多次进行光刻工艺和蚀刻工艺,从而在基底基板上形成上述的信号线、多个像素px、扫描驱动电路sdc以及数据驱动电路ddc。

[0085]

可以通过多次的蒸镀工艺或者涂层工艺,在基底基板上形成多个绝缘层。多个绝缘层包括有机层及/或无机层。多个绝缘层中的任一个可以包括多个绝缘图案。多个绝缘层各自与多个像素px重叠。可以在多个绝缘层形成接触孔。多个接触孔可以在多个像素px中的每一个以预定的规则排列。

[0086]

图2是根据本发明的一实施例的像素px

ij

的等效电路图。图3是用于驱动图2中示出的像素px

ij

的驱动信号的波形图。

[0087]

图2中作为代表示出连接至第一组的扫描线sl11~sl1n(参照图1)中的第i个扫描线sl1i,并连接至多个数据线dl1~dlm(参照图1)中的第j个数据线dlj的像素px

ij

。像素px

ij

连接至第二组的扫描线中的第i个扫描线sl2i,并连接至第三组的扫描线中的第i个扫描线sl3i。

[0088]

在本实施例中,像素驱动电路可以包括第一至第五晶体管t1~t5、第一电容器c1至第三电容器c3以及发光二极管oled。在本实施例中,第一至第五晶体管t1~t5以n型进行说明。然而,不限于此,第一至第五晶体管t1~t5中的至少一个可以为p型的晶体管。另外,在本发明的一实施例中,可以省略第一至第五晶体管t1~t5中的至少一个,或者在像素px

ij

还包括附加的晶体管。

[0089]

在本实施例中,示出为第一至第五晶体管t1~t5各自包括2个栅极的情况,然而至少任一个晶体管可以仅包括1个栅极。虽然示出为第二至第五晶体管t2~t5各自的上栅极g2-1、g3-1、g4-1、g5-1和下栅极g2-2、g3-2、g4-2、g5-2彼此电连接的情况,然而不限于此。第二至第五晶体管t2~t5各自的下栅极g2-2、g3-2、g4-2、g5-2也可以为浮置电极。

[0090]

在本实施例中,第一晶体管t1可以为驱动晶体管,第二晶体管t2可以为开关晶体管。可以是,连接有第一晶体管t1的栅极g1-1的节点界定为第一节点nd1,连接有第一晶体管t1的源极s1的节点界定为第二节点nd2。

[0091]

发光二极管oled包括与第二节点nd2电接通的第一电极、接收第一电源电压elvss的第二电极以及配置在第一电极和第二电极之间的发光层。对发光二极管oled的具体说明将后述。

[0092]

第一晶体管t1在接收第二电源电压elvdd的第二电压线vl2和第二节点nd2之间电接通。第一晶体管t1可以包括与第二节点nd2接通的源极s1(以下,第一源极)、漏极d1(以下,第一漏极)、半导体区域以及与第一节点nd1电连接的栅极g1-1(以下,第一上栅极)。第一晶体管t1可以还包括与第二节点nd2连接的栅极g1-2(以下,第一下栅极)。

[0093]

第二晶体管t2在第j个数据线dlj和第一节点nd1之间电接通。第二晶体管t2可以

包括与第一节点nd1接通的源极s2(以下,第二源极)、与第j个数据线dlj接通的漏极d2(以下,第二漏极)、半导体区域以及与第一组的第i个扫描线sl1i连接的栅极g2-1(以下,第二上栅极)。第二晶体管t2可以还包括与第二上栅极g2-1电连接的栅极g2-2(以下,第二下栅极)。后述的第三至第五晶体管t3~t5可以包括分别与第二上栅极g2-1和第二下栅极g2-2相对应的上栅极g3-1、g4-1、g5-1和下栅极g3-2、g4-2、g5-2。

[0094]

第三晶体管t3在第一节点nd1和接收第一电压vref的第三电压线vl3之间电接通。第三晶体管t3可以包括与第一节点nd1接通的漏极d3(以下,第三漏极)、与第三电压线vl3接通的源极s3(以下,第三源极)、半导体区域以及与第二组的第i个扫描线sl2i连接的第三上栅极g3-1。

[0095]

第四晶体管t4在接收第二电压vint的第四电压线vl4和第二节点nd2之间电接通。第四晶体管t4可以包括与第二节点nd2接通的漏极d4(以下,第四漏极)、与第四电压线vl4接通的源极s4(以下,第四源极)、半导体区域以及与第三组的第i个扫描线sl3i连接的第四上栅极g4-1。

[0096]

第五晶体管t5在第二电压线vl2和第一漏极d1或第一源极s1之间电接通。在本实施例中,第五晶体管t5可以包括与第一漏极d1或第一源极s1接通的源极s5(以下,第五源极)、与第二电压线vl2接通的漏极d5(以下,第五漏极)、半导体区域以及与第i个发光信号线eli连接的第五上栅极g5-1。

[0097]

第一电容器c1在第一节点nd1和第二节点nd2之间电接通。第一电容器c1包括与第一节点nd1接通的第一电极e1-1以及与第二节点nd2接通的第二电极e1-2。

[0098]

第二电容器c2在第二电压线vl2和第二节点nd2之间电接通。第二电容器c2包括与第二电压线vl2接通的第一电极e2-1以及与第二节点nd2接通的第二电极e2-2。

[0099]

第三电容器c3在发光二极管oled的第一电极和第二电极之间电接通。第三电容器c3包括与发光二极管oled的第一电极接通的第一电极e3-1以及与发光二极管oled的第二电极接通的第二电极e3-2。

[0100]

参照图2以及图3更加详细说明像素px

ij

的工作。显示装置dd(参照图1)在每一个帧区间显示图像。第一组的扫描线、第二组的扫描线以及第三组的扫描线以及发光信号线各自的信号线在帧区间期间依次被扫描。图3示出了帧区间中的一部分。

[0101]

参照图3,可以是,信号ei、gri、gwi、gii各自在一部分区间期间具有高电平v-high,在一部分区间期间具有低电平v-low。以上说明的n型的第一至第五晶体管t1~t5在相对应的控制信号具有高电平v-high时导通。

[0102]

在初始化区间ip期间,第三晶体管t3和第四晶体管t4导通。第一节点nd1初始化为第一电压vref。第二节点nd2初始化为第二电压vint。第一电容器c1初始化为第一电压vref和第二电压vint的差值。第二电容器c2初始化为第二电源电压elvdd和第二电压vint的差值。第三电容器c3初始化为第一电源电压elvss和第二电压vint的差值。

[0103]

在补偿区间cp期间,第三晶体管t3和第五晶体管t5导通。在第一电容器c1补偿与第一晶体管t1的阈值电压相对应的电压。

[0104]

在写入区间wp期间,第二晶体管t2导通。第二晶体管t2输出与数据信号ds相对应的电压。最终,在第一电容器c1被充电与数据信号ds相对应的电压值。在第一电容器c1被充电与补偿第一晶体管t1的阈值电压的数据信号ds相对应的电压值。每一个像素px(参照图

1)驱动晶体管的阈值电压可以不同,然而,图2以及图3中示出的像素px

ij

与驱动晶体管的阈值电压的偏差无关而可以将与数据信号ds成比例的大小的电流供应至发光二极管oled。

[0105]

然后,在发光区间期间,第五晶体管t5导通。第一晶体管t1将与第一电容器c1中储存的电压值相对应的电流提供至发光二极管oled。发光二极管oled可以以与数据信号ds相对应的亮度发光。

[0106]

图4是根据本发明的一实施例的显示面板dp的截面图。图4示出了与图2中示出的像素px

ij

中的一部分结构相对应的部分的截面。

[0107]

参照图4,显示面板dp可以包括基底层bs、配置在基底层bs上的电路元件层dp-cl、显示元件层dp-oled以及薄膜封装层tfe。显示面板dp可以还包括反射防止层或折射率调节层等之类的功能性层。电路元件层dp-cl至少包括多个绝缘层和电路元件。以下说明的绝缘层可以包括有机层及/或无机层。

[0108]

通过涂层、蒸镀等的工艺,形成绝缘层、半导体层以及导电层。然后,可以通过光刻以及蚀刻工艺,将绝缘层、半导体层以及导电层选择性地图案化。通过这样的工艺,形成半导体图案、导电图案、信号线等。配置在相同的层上的图案通过相同的工艺形成。

[0109]

基底层bs可以包括合成树脂层。合成树脂层可以包含热固化性树脂。尤其是,合成树脂层可以为聚酰亚胺类树脂层,其材料不受特别限制。合成树脂层可以包含丙烯酸类树脂、甲基丙烯酸类树脂、聚异戊二烯、乙烯类树脂、环氧类树脂、氨基甲酸乙酯类树脂、纤维素类树脂、硅氧烷类树脂、聚酰胺类树脂以及苝类树脂中的至少任一种。除此之外,基底层bs可以包括玻璃基板、金属基板或者有机/无机复合材料基板等。

[0110]

在基底层bs的上面形成至少一个无机层。无机层可以包含氧化铝、氧化钛、氧化硅、氮化硅、氮氧化硅、氧化锆以及氧化铪中的至少一种。无机层可以形成为多层。多层的无机层可以构成后述的阻挡层brl及/或缓冲层bfl。阻挡层brl和缓冲层bfl可以选择性地配置。

[0111]

阻挡层brl防止从外部流入杂质。阻挡层brl可以包括氧化硅层以及氮化硅层。它们各自可以提供多个,氧化硅层和氮化硅层可以交替层叠。

[0112]

在阻挡层brl上配置导电层(以下,第一导电层)。第一导电层可以包括多个导电图案。图4中示出了第一导电层的一部分图案。作为第一导电层的导电图案的一例,示出了第一下栅极g1-2以及第二下栅极g2-2。

[0113]

缓冲层bfl可以配置在阻挡层brl上以覆盖第一下栅极g1-2以及第二下栅极g2-2。缓冲层bfl提高基底层bs与半导体图案及/或导电图案之间的结合力。缓冲层bfl可以包括氧化硅层以及氮化硅层。氧化硅层和氮化硅层可以交替层叠。

[0114]

在缓冲层bfl上配置半导体层。半导体层可以包括多个半导体图案。半导体图案可以包含金属氧化物。金属氧化物半导体可以包括晶体或者非晶氧化物半导体。例如,氧化物半导体可以包含锌(zn)、铟(in)、镓(ga)、锡(sn)、钛(ti)等的金属氧化物或者锌(zn)、铟(in)、镓(ga)、锡(sn)、钛(ti)等的金属和它们的氧化物的混合物。氧化物半导体可以包含氧化铟锡(ito)、氧化铟镓锌(igzo)、氧化锌(zno)、氧化铟锌(izo)、氧化铟(ino)、氧化钛(tio)、氧化铟锌锡(izto)、氧化锌锡(zto)等。

[0115]

半导体图案可以包括根据金属氧化物是否被还原进行划分的多个区域。金属氧化物被还原的区域(以下,还原区域)相比金属氧化物未被还原的区域(以下,非还原区域)具

有大的导电性。还原区域实质上具有晶体管的源极/漏极或者信号线的作用。非还原区域实质上相当于晶体管的半导体区域(或者沟道)。换句而言,半导体图案的一部分可以为晶体管的半导体区域,另一部分可以为晶体管的源极/漏极,又一部分可以为信号传输区域。

[0116]

如图4所示,第一晶体管t1的源极s1、半导体区域a1、漏极d1由半导体图案形成。第一晶体管t1的源极s1以及漏极d1从半导体区域a1向彼此相反方向延伸。第二晶体管t2的源极s2、半导体区域a2以及漏极d2也是由半导体图案形成。

[0117]

上述的第一下栅极g1-2以及第二下栅极g2-2具有遮光图案的功能。第一下栅极g1-2以及第二下栅极g2-2分别配置在第一晶体管t1的半导体区域a1以及第二晶体管t2的半导体区域a2的下侧,从而阻挡从外部向它们入射的光。遮光图案防止外部的光改变第一晶体管t1以及第二晶体管t2各自的电压-电流特性。

[0118]

在缓冲层bfl上配置第一绝缘层10。在本实施例中,第一绝缘层10不形成于显示面板dp整个面,而仅与后述的特定导电图案重叠。第一绝缘层10包括多个绝缘图案。图4中示例性示出了第一绝缘图案10-1、第二绝缘图案10-2以及第三绝缘图案10-3。

[0119]

第一绝缘图案10-1和第二绝缘图案10-2分别与后述的第一上栅极g1-1以及第二上栅极g2-1重叠。第三绝缘图案10-3与后述的第一导电性图案p1重叠。

[0120]

在第一绝缘层10上配置导电层(以下,第二导电层)。第二导电层可以包括分别与第一绝缘层10的绝缘图案重叠的多个导电图案。图4中作为第二导电层的导电图案的一例示出了第一上栅极g1-1、第二上栅极g2-1以及第一导电性图案p1。由于第二导电层和第一绝缘层通过相同的工艺进行蚀刻,因此第二导电层的导电图案和第一绝缘层的绝缘图案具有实质上相同的形状。

[0121]

第一导电性图案p1定义图2中示出的第一电容器c1的第一电极e1-1。示出为在截面上第一导电性图案p1与第一晶体管t1的上栅极g1-1隔开的情况,然而第一导电性图案p1可以与第一晶体管t1的上栅极g1-1具有一体的形状。即,可以是,任一个导电性图案的第一部分相当于第一晶体管t1的上栅极g1-1,第二部分相当于第一导电性图案p1。这可以在图6c中确认。

[0122]

在缓冲层bfl上配置覆盖第一上栅极g1-1、第二上栅极g2-1以及第一导电性图案p1的第二绝缘层20。第二绝缘层20可以为无机层及/或有机层,可以具有单层或者多层结构。

[0123]

可以在第二绝缘层20上配置与第一导电性图案p1重叠的第二导电性图案p2。第二导电性图案p2定义图2中示出的第一电容器c1的第二电极e1-2以及第二电容器c2的第二电极e2-2。

[0124]

在第二绝缘层20上配置覆盖第二导电性图案p2的第三绝缘层30。在本实施例中,第三绝缘层30可以为有机层,可以具有单层结构,然而不受特别限制。

[0125]

在第三绝缘层30上配置导电层(以下,第三导电层)。第三导电层可以包括多个导电图案。第三导电层包括定义图2中示出的第二电容器c2的第一电极e2-1的第三导电性图案p3。可以在第三导电性图案p3界定开口部p3-op。

[0126]

第三导电层可以还包括多个连接电极。图4中示例性示出了第一至第四连接电极cne1~cne4。第一连接电极cne1通过贯穿第二以及第三绝缘层20、30的接触孔117与第一源极s1连接,第二连接电极cne2通过贯穿第二以及第三绝缘层20、30的接触孔107与第二源极

s2连接,第三连接电极cne3通过贯穿第二以及第三绝缘层20、30的接触孔106与第二漏极d2连接。

[0127]

第四连接电极cne4通过贯穿第三绝缘层30的接触孔113与第二导电性图案p2连接。第四连接电极cne4配置在开口部p3-op的内侧。第四连接电极cne4将第二导电性图案p2与在上侧配置的第一电极ae电连接。

[0128]

在第三绝缘层30上配置覆盖第三导电层的第四绝缘层40。在本实施例中,第四绝缘层40可以为有机层,可以具有单层结构,然而不受特别限制。

[0129]

在第四绝缘层40上配置导电层(以下,第四导电层)。第四导电层可以包括多个导电图案。第四导电层包括第七连接电极cne7。第七连接电极cne7通过贯穿第四绝缘层40的接触孔205与第四连接电极cne4连接。

[0130]

第四导电层可以还包括第j个数据线dlj和第一电压线vl1。第j个数据线dlj通过贯穿第四绝缘层40的接触孔203与第三连接电极cne3连接。与后述的发光二极管oled的第一电极ae重叠的第一电压线vl1的一部分定义图2中示出的第三电容器c3的第二电极e3-2。发光二极管oled的第一电极ae的一部分定义图2中示出的第三电容器c3的第一电极e3-1。

[0131]

在第四绝缘层40上配置覆盖第四导电层的第五绝缘层50。在本实施例中,第五绝缘层50可以为有机层,可以具有单层结构,然而不受特别限制。

[0132]

发光二极管oled的第一电极ae配置在第五绝缘层50上。第一电极ae可以为阳极。在第五绝缘层50上配置像素界定膜pdl。第一电极ae通过贯穿第五绝缘层50的接触孔301与第七连接电极cne7连接。

[0133]

像素界定膜pdl的开口部op暴露第一电极ae的至少一部分。像素界定膜pdl的开口部op可以界定发光区域pxa。例如,多个像素px(参照图1)可以在显示面板dp(参照图1)的平面上以一定的规则配置。配置有多个像素px的区域可以界定为像素区域,一个像素区域可以包括发光区域pxa和与发光区域pxa相邻的非发光区域npxa。非发光区域npxa可以包围发光区域pxa。

[0134]

空穴控制层hcl可以共同配置在发光区域pxa和非发光区域npxa。空穴控制层hcl之类的共同层可以共同形成在多个像素px。空穴控制层hcl可以包括空穴传输层以及空穴注入层。

[0135]

在空穴控制层hcl上配置发光层eml。发光层eml可以仅配置在与开口部op相对应的区域。发光层eml可以在多个像素px各自中分离形成。

[0136]

在本实施例中,示例性示出了图案化的发光层eml,然而发光层eml可以共同配置在多个像素px。共同配置的发光层eml可以生成白色光或者蓝色光。另外,发光层eml可以具有多层结构。

[0137]

在发光层eml上配置电子控制层ecl。电子控制层ecl可以包括电子传输层以及电子注入层。在电子控制层ecl上配置第二电极ce。电子控制层ecl以及第二电极ce共同配置在多个像素px。

[0138]

在第二电极ce上配置薄膜封装层tfe。薄膜封装层tfe共同配置在多个像素px。在本实施例中,薄膜封装层tfe直接覆盖第二电极ce。在本发明的一实施例中,可以还配置直接覆盖第二电极ce的封盖层。在本发明的一实施例中,发光二极管oled的叠层结构也可以具有在图4中示出的结构中上下颠倒的结构。

[0139]

薄膜封装层tfe至少包括无机层或者有机层。在本发明的一实施例中,薄膜封装层tfe可以包括2个无机层和配置在它们之间的有机层。

[0140]

在本发明的一实施例中,薄膜封装层tfe可以包括交替层叠的多个无机层和多个有机层。

[0141]

图5是根据本发明的一实施例的像素px

ij

、px

ij 1

的平面图。图6a至图6h是基于根据本发明的一实施例的像素px

ij

、px

ij 1

的图案的叠层顺序的平面图。以下,省略对与参照图1至图4说明的结构相同的结构的详细说明。

[0142]

图5中示出了与配置在相同的行的2个像素px

ij

、px

ij 1

相对应的区域和与它相邻的一个虚设区域dma。可以是,虚设区域dma配置在像素行的一侧及/或另一侧,或者将像素行中的多个像素置于中间以一定间隔配置。

[0143]

参照图5以及图6a,在基底层bs(参照图4)上配置第一导电层mp1的导电图案。第一导电层mp1的导电图案可以包括第一虚设电压线vl1-d、第三虚设电压线vl3-d、第四虚设电压线vl4-d、第一组的虚设扫描线sl1i-d、第三组的虚设扫描线sl3i-d、发光虚设信号线eli-d。第一虚设电压线vl1-d、第三虚设电压线vl3-d、第四虚设电压线vl4-d、第一组的虚设扫描线sl1i-d、第三组的虚设扫描线sl3i-d以及发光虚设信号线eli-d可以分别与后述的第一电压线vl1、第三电压线vl3、第四电压线vl4、第一组的第i个扫描线sl1i、第三组的第i个扫描线sl3i以及第i个发光信号线eli重叠。

[0144]

第一导电层mp1的导电图案可以还包括第一、第二、第三以及第五晶体管t1、t2、t3、t5的下栅极g1-2、g2-2、g3-2、g5-2。第四晶体管t4的下栅极g4-2相当于第三组的虚设扫描线sl3i-d的一部分。

[0145]

第一导电层mp1的导电图案包括第二组的第i个扫描线sl2i。第三晶体管t3的下栅极g3-2从第二组的第i个扫描线sl2i延伸。

[0146]

参照图5以及图6b,在缓冲层bfl(参照图4)上配置半导体层scl的半导体图案。可以配置第一半导体图案scp1以及第二半导体图案scp2以与像素px

ij

相对应。

[0147]

第一半导体图案scp1可以包括第二以及第三晶体管t2、t3的源极s2、s3、半导体区域a2、a3以及漏极d2、d3。第二半导体图案scp2可以包括第一、第四以及第五晶体管t1、t4、t5的源极s1、s4、s5、半导体区域a1、a4、a5以及漏极d1、d4、d5。

[0148]

图6b中示出的第一半导体图案scp1和第二半导体图案scp2彼此不区分源极/漏极/半导体区域。将参照图6c说明的上栅极g1-1、g2-1、g3-1、g4-1、g5-1用作掩模进行还原工艺之后,彼此区分源极/漏极和半导体区域。

[0149]

参照图5以及图6c,在第一绝缘层10(参照图4)上配置第一导电层mp1的导电图案。第一导电层mp1的导电图案可以包括第一至第五晶体管t1~t5的上栅极g1-1、g2-1、g3-1、g4-1、g5-1。若将上栅极g1-1、g2-1、g3-1、g4-1、g5-1用作掩模进行还原工艺,则第一半导体图案scp1以及第二半导体图案scp2各自的源极/漏极相比半导体区域具有更大的导电性。若经过还原工艺,则完成具有开关功能的第一至第五晶体管t1~t5。

[0150]

第一导电层mp1的导电图案可以包括第一导电性图案p1。第一导电性图案p1可以与第一晶体管t1的上栅极g1-1具有一体的形状。

[0151]

参照图5以及图6d,在第二绝缘层20(参照图4)上配置第二导电层mp2的导电图案。第二导电层mp2的导电图案可以包括第二导电性图案p2以及中间连接图案cne-m。

[0152]

参照图5以及图6e,在第二绝缘层20(参照图4)上配置第三绝缘层30。图6e中示出了在第三绝缘层30界定的多个接触孔101~123。多个接触孔101~123中的一部分可以贯穿第二绝缘层20和第三绝缘层30全部,另一部分可以仅贯穿第三绝缘层30。参照图6a至图6d说明的导电图案以及后述的图6f中示出的导电图案通过接触孔101~123电连接以构成图2的等效电路。

[0153]

参照图5以及图6f,在第三绝缘层30(参照图4)上配置第三导电层mp3的导电图案。第三导电层mp3可以包括第一电压线vl1、第三电压线vl3、第四电压线vl4、第一组的第i个扫描线sl1i、第三组的第i个扫描线sl3i、第i个发光信号线eli。

[0154]

第一电压线vl1可以通过接触孔101与第一虚设电压线vl1-d连接。第三电压线vl3可以通过接触孔102与第三虚设电压线vl3-d连接。第四电压线vl4可以通过接触孔122与第四虚设电压线vl4-d连接。

[0155]

第一组的第i个扫描线sl1i可以通过接触孔105与第一组的虚设扫描线sl1i-d连接。第三组的第i个扫描线sl3i可以通过接触孔120与第三组的虚设扫描线sl3i-d连接。第i个发光信号线eli可以通过接触孔119与发光虚设信号线eli-d连接。

[0156]

第三导电层mp3可以还包括第一至第六连接电极cne1、cne2、cne3、cne4、cne5、cne6。第五连接电极cne5通过接触孔110、111而将第二组的第i个扫描线sl2i与第三晶体管t3的上栅极g3-1连接。第六连接电极cne6通过接触孔108、109而将中间连接图案cne-m与第三晶体管t3的源极s3连接。

[0157]

第三导电层mp3可以包括第三导电性图案p3。第三导电性图案p3包括与第二导电性图案p2重叠的电极部分p3-e。第三导电性图案p3的一部分区域,即电极部分p3-e配置在后述的第j个数据线dlj和第j 1个数据线dlj 1之间。

[0158]

在平面上观察时,第一导电性图案p1和第二导电性图案p2实质上配置在第三导电性图案p3的内侧。未配置在第三导电性图案p3的内侧的第一导电性图案p1和第二导电性图案p2在图6f中以阴影线表示。

[0159]

第三导电性图案p3可以还包括从电极部分p3-e延伸的连接部分p3-c1、p3-c2、p3-c3。连接部分p3-c1、p3-c2、p3-c3相比电极部分p3-e具有窄的面积和窄的宽度。

[0160]

第一连接部分p3-c1从电极部分p3-e向第二方向dr2延伸。第一连接部分p3-c1通过接触孔114与第五晶体管t5的漏极或者源极(在图6f中为漏极)连接。接触孔114贯穿图4中示出的第二绝缘层20以及第三绝缘层30。

[0161]

第二连接部分p3-c2从电极部分p3-e向第一方向dr1延伸。如图6h所示,第二电压线vl2通过贯穿第四绝缘层40的接触孔204与第二连接部分p3-c2连接。

[0162]

第三连接部分p3-c3从电极部分p3-e向第一方向dr1延伸。在第一方向dr1中,在第三连接部分p3-c3和第二连接部分p3-c2之间配置电极部分p3-e。第三连接部分p3-c3将电极部分p3-e与相邻的像素px

ij 1

的第三导电性图案p3连接。

[0163]

参照图5以及图6g,在第三绝缘层30(参照图4)上配置第四绝缘层40。图6g中示出了在第四绝缘层40界定的多个接触孔201~205。参照图6a至图6f说明的导电图案以及后述的图6h中示出的导电图案通过接触孔201~205电连接以构成图2的等效电路。

[0164]

参照图5以及图6h,在第四绝缘层40(参照图4)上配置第四导电层mp4的导电图案。第四导电层mp4可以包括第一电压线vl1、第二电压线vl2、第三电压线vl3、第j个数据线

dlj、第j 1个数据线dlj 1以及第七连接电极cne7。

[0165]

图7是根据本发明的一实施例的像素px

ij

的等效电路图。图8是与根据本发明的一实施例的像素px

ij

相对应的显示面板dp的截面图。图9a以及图9b是基于根据本发明的一实施例的像素px

ij

中包括的图案的叠层顺序的平面图。图9a与图6a相对应,图9b与图6c相对应。以下,省略对参考图1至图6h说明的结构相同的结构的详细说明。

[0166]

参照图7,像素px

ij

可以还包括第四电容器c1-2。图7的第一电容器c1-1与图2的第一电容器c1相对应。第一电容器c1-1接通在第一晶体管t1的上栅极g1-1和源极s1之间,即第一晶体管t1的控制端子和输出端子之间。第四电容器c1-2与第一电容器c1-1并联连接。最终,像素px

ij

包括容量增加的存储电容器。存储电容器为接收数据信号的电容器。即便发生驱动晶体管的栅极和数据线之间的耦合,由于存储电容器的容量增加,因此减小数据信号引起的驱动晶体管的栅极-源极电压的变动性。

[0167]

参考图8,显示面板dp还包括配置在第一导电性图案p1下侧的第四导电性图案p4。第一导电性图案p1与第四电容器c1-2的第一电极e1-10(参考图7)相对应,第四导电性图案p4与第四电容器c1-2的第二电极e1-20(参考图7)相对应。

[0168]

参考图9a,由于第四导电性图案p4通过与第一下栅极g1-2相同的工艺形成,因此配置在与第一下栅极g1-2相同的层上。第四导电性图案p4可以与第一下栅极g1-2具有一体的形状。

[0169]

参考图9b,第一导电性图案p1与第四导电性图案p4重叠。实质上,第一导电性图案p1可以配置在第四导电性图案p4的内侧。

[0170]

以上,参照本发明的优选实施例进行了说明,然而本技术领域的熟练技术人员或在本技术领域具有通常的知识的人可以理解的是在不脱离所附的权利要求书中记载的本发明的构思以及技术领域的范围内可以对本发明进行各种修改以及变更。

[0171]

因此,本发明的技术范围不限定为说明书的详细说明中记载的内容,仅应通过权利要求书确定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。