1.本公开是有关于一种存储器装置及其操作方法。

背景技术:

2.以人们现代生活而言,电子产品是无所不在。在电子产品中,存储器也是重要元件。以近日而言,高储存密度存储器的需求愈来愈大。为提高储存密度,三维架构存储器已渐成为存储器制造厂商的重点。

3.然而,为符合未来的系统需求,改善存储器性能是至关重要(imperative)。

4.公开内容

5.根据本公开的一实例,提出一种存储器装置,包括:一存储器阵列;一译码电路,耦接至该存储器阵列,该译码电路包括多个第一晶体管、多个第二晶体管,与多个反相器,该多个第一晶体管与该多个第二晶体管为成对;以及一控制器,耦接至该译码电路,其中,成对的该多个第一晶体管与该多个第二晶体管的每对所述第一晶体管与所述第二晶体管分别耦接至该多个反相器之一,以及分别耦接至多条区域位线之一或多条区域源极线之一;该多个第一晶体管耦接至一整体位线;以及该多个第二晶体管耦接至一整体源极线。

6.根据本公开的另一实例,提出一种存储器装置的操作方法,包括:由成对的多个第一晶体管与多个第二晶体管控制多条区域源极线与多条区域位线,其中,该多个第一晶体管与该多个第二晶体管是三极晶体管;该多个第一晶体管耦接至一整体位线;以及该多个第二晶体管耦接至一整体源极线。

7.为了对本公开的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

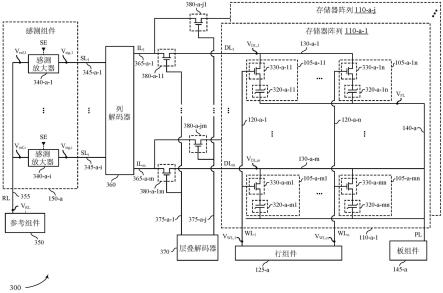

8.图1显示根据本公开一实施例的存储器装置的功能框图。

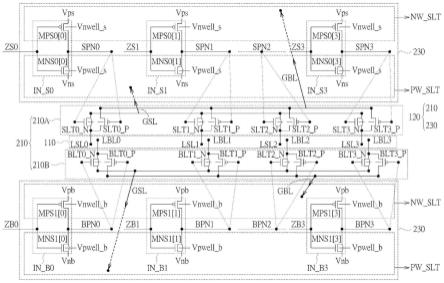

9.图2显示根据本公开一实施例的存储器装置的电路架构图。

10.图3显示根据本公开一实施例的存储器装置的读取操作示意图。

11.图4显示根据本公开一实施例的存储器装置的第一编程操作示意图。

12.图5a与图5b分别显示受选层与未选层的5种单元的示意图。

13.图6显示根据本公开一实施例的存储器装置的第二编程操作示意图。

14.图7显示根据本公开一实施例的存储器装置的字节擦除操作示意图。

15.图8显示根据本公开一实施例的存储器装置的区块擦除操作示意图。

16.附图标记说明

17.100:存储器装置

18.110:存储器阵列

19.120:译码电路

20.130:控制器

21.210:译码单元

22.230:反相器单元

23.210a:区域源极线译码器

24.210b:区域位线译码器

25.blt0_n~blt3_n与blt0_p~blt3_p,slt0_n~slt3_n、slt0_p~slt3_p、mns0[0]~mns0[3]与mps0[0]~mps0[3]、mns1[0]~mns1[3]与mps1[0]~mps1[3]:晶体管

[0026]

in_b0~in_b3与in_s0~in_s3:反相器

[0027]

lbl0~lbl3:区域位线

[0028]

lsl0~lsl3:区域源极线

[0029]

gsl、gsln:整体源极线

[0030]

gbl、gbln:整体位线

[0031]

wl0_0、wl0_1、wl1_0、wl1_1:字线

[0032]

mc:存储器单元

[0033]

smc:目标存储器单元

具体实施方式

[0034]

本说明书的技术用语参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释以本说明书的说明或定义为准。本公开的各个实施例分别具有一或多个技术特征。在可能实施的前提下,本领域的技术人员可选择性地实施任一实施例中部分或全部的技术特征,或者选择性地将这些实施例中部分或全部的技术特征加以组合。

[0035]

图1显示根据本公开一实施例的存储器装置的功能框图。本公开一实施例的存储器装置100包括:存储器阵列110、译码电路120与控制器130。译码电路120耦接至存储器阵列110与控制器130。控制器130控制存储器阵列110与译码电路120以进行读取操作、编程操作、字节擦除(byte erase)操作与区块擦除(sector erase)操作等。其细节将于下文说明。

[0036]

图2显示根据本公开一实施例的存储器装置的电路架构图。译码电路120包括:译码单元210与反相器单元230。

[0037]

译码单元210包括多个位线晶体管与多个源极线晶体管。译码单元210包括区域源极线译码器210a与区域位线译码器210b。在图2中,以译码单元210包括8个位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及8个源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p为例做说明,但当知本公开并不受限于此。区域源极线译码器210a包括源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p。区域位线译码器210b包括位线晶体管blt0_n~blt3_n与blt0_p~blt3_p。

[0038]

在本公开一实施例中,该多个位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及该多个源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p乃是以三井(triple well)技术制造而成。

[0039]

反相器单元230包括多个反相器。在图2中,以反相器单元230包括8个反相器in_b0~in_b3与in_s0~in_s3为例做说明,但当知本公开并不受限于此。该多个反相器in_b0~in_b3与in_s0~in_s3包括晶体管mns0[0]~mns0[3]与mps0[0]~mps0[3]、mns1[0]~mns1

[3]与mps1[0]~mps1[3]。

[0040]

在图2中,该多个位线晶体管blt0_n~blt3_n与blt0_p~blt3_p分别通过区域位线lbl0~lbl3而耦接至存储器阵列110。

[0041]

在图2中,该多个源极线晶体管slt0_n~slt3_n与slt0_p~slt3_p分别通过区域源极线lsl0~lsl3而耦接至存储器阵列110。

[0042]

也就是说,在本公开实施例中,各区域源极线lsl0~lsl3与各区域位线lbl0~lbl3被一对mos晶体管(位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p)所控制。

[0043]

位线晶体管blt0_n具有一端耦接至整体源极线gsl、另一端耦接至区域位线lbl0,以及控制端耦接至反相器in_b0的输出。位线晶体管blt1_n~blt3_n的耦接关系类似,在此不赘述。

[0044]

位线晶体管blt0_p具有一端耦接至整体位线gbl、另一端耦接至区域位线lbl0,以及控制端耦接至反相器in_b0的输出。位线晶体管blt1_p~blt3_p的耦接关系类似,在此不赘述。

[0045]

相似地,源极线晶体管slt0_n具有一端耦接至整体源极线gsl、另一端耦接至区域源极线lsl0,以及控制端耦接至反相器in_s0的输出。源极线晶体管slt1_n~slt3_n的耦接关系类似,在此不赘述。

[0046]

源极线晶体管slt0_p具有一端耦接至整体位线gbl、另一端耦接至区域源极线lsl0,以及控制端耦接至反相器in_s0的输出。源极线晶体管slt1_p~slt3_p的耦接关系类似,在此不赘述。

[0047]

在反相器单元230中,晶体管mns0[0]~mns0[3]的栅极分别接收控制信号zs0~zs3。晶体管mns0[0]~mns0[3]的源极则耦接至偏压vns。晶体管mns0[0]~mns0[3]的漏极则耦接至输出端spn0~spn3。

[0048]

相似地,在反相器单元230中,晶体管mps0[0]~mps0[3]的栅极分别接收控制信号zs0~zs3。晶体管mps0[0]~mnp0[3]的源极则耦接至偏压vps。晶体管mps0[0]~mps0[3]的漏极则耦接至输出端spn0~spn3。

[0049]

在反相器单元230中,晶体管mns1[0]~mns1[3]的栅极分别接收控制信号zb0~zb3。晶体管mns1[0]~mns1[3]的源极则耦接至偏压vnb。晶体管mns1[0]~mns1[3]的漏极则耦接至输出端bpn0~bpn3。

[0050]

相似地,在反相器单元230中,晶体管mps1[0]~mps1[3]的栅极分别接收控制信号zb0~zb3。晶体管mps1[0]~mnp1[3]的源极则耦接至偏压vpb。晶体管mps1[0]~mps1[3]的漏极则耦接至输出端bpn0~bpn3。

[0051]

控制信号zb0~zb3是译码信息。在受选层(tier)中,bpn0~bpn3控制晶体管blt0_n~blt3_n的栅极电压与控制晶体管blt0_p~blt3_p的栅极电压。

[0052]

相似地,控制信号zs0~zs3是译码信息。在受选层中,spn0~spn3控制晶体管slt0_n~slt3_n的栅极电压与控制晶体管slt0_p~slt3_p的栅极电压。

[0053]

晶体管mns0[0]~mns0[3]的基极则耦接至井电压vpwell_s。晶体管mns1[0]~mns1[3]的基极则耦接至井电压vpwell_b。

[0054]

晶体管mps0[0]~mps0[3]的基极则耦接至井电压vnwell_s。晶体管mps1[0]~

mps1[3]的基极则耦接至井电压vnwell_b。

[0055]

在本公开一实施例中,该多个晶体管mns0[0]~mns0[3]共享p井pw_slt;该多个晶体管mps0[0]~mps0[3]共享n井nw_slt;该多个晶体管mns1[0]~mns1[3]共享p井pw_blt;以及,该多个晶体管mps1[0]~mps1[3]共享n井nw_blt。

[0056]

在本公开一实施例中,整体源极线gsl可选择性耦接至井电压vpwell_b。或者是,在本公开一实施例中,整体源极线gsl可选择性耦接至井电压vpwell_s。

[0057]

在本公开一实施例中,整体位线gbl可选择性耦接至井电压vnwell_b。或者是,在本公开一实施例中,整体位线gbl可选择性耦接至井电压vnwell_s。

[0058]

整体位线gbl耦接至该多个pmos晶体管slt0_p~slt3_p与blt0_p~blt3_p。整体源极线gsl耦接至该多个nmos晶体管slt0_n~slt3_n与blt0_n~blt3_n。

[0059]

在本公开一实施例中,为避免正向二极管(forward diode),电压设定条件可如下表1所示:

[0060]

表1

[0061][0062][0063]

在表1的“s/b common”,s代表源极(source),b代表本体(body),“s/b common”代表源极与本体耦接,源极与本体具有相同电压(vsb=0v),以避免本体效应。由表1可知,在本公开实施例中,该多个节点电压原则上都要低于n井电压vnwell_b与vnwell_s,以及,该多个节点电压原则上都要高于p井电压vpwell_b与vnwell_s。或者说,在本公开实施例中,p井电压vpwell_b与vnwell_s要设定为是这些电压中最低的电压,而n井电压vnwell_b与vnwell_s要设定为是这些电压中最高的电压。

[0064]

图3显示根据本公开一实施例的存储器装置的读取操作示意图。在进行读取时,各电压设定条件如下表2。

[0065]

表2

[0066] 电压(v)gbln1gsln0受选字线5~7未选字线0vps1.8vns0

vnwell_s1.8vpwell_s0vpb1.8vnb0vnwell_b1.8vpwell_b0

[0067]

在图3中,以字线wl0_0为受选字线而其他字线(如wl0_1、wl1_0、wl1_1)则为未选字线为例做说明。

[0068]

至于位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p的电压设定则是如后所述。

[0069]

当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为高电位(如1.8v),则nmos源极线晶体管slt0_n~slt3_n为导通;反之,当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为低电位(如0v),则nmos源极线晶体管slt0_n~slt3_n为关闭。

[0070]

当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为高电位(如1.8v),则pmos源极线晶体管slt0_p~slt3_p为关闭;反之,当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为低电位(如0v),则pmos源极线晶体管slt0_p~slt3_p为导通。

[0071]

当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为高电位(如1.8v),则nmos位线晶体管blt0_n~blt3_n为导通;反之,当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为低电位(如0v),则nmos位线晶体管blt0_n~blt3_n为关闭。

[0072]

当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为高电位(如1.8v),则pmos位线晶体管blt0_p~blt3_p为关闭;反之,当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为低电位(如0v),则pmos位线晶体管blt0_p~blt3_p为导通。

[0073]

通过上式电压控制,可以读取目标存储器单元smc。详言之,在进行读取时,位线晶体管blt0_n~blt2_n为导通而位线晶体管blt3_n为关闭;位线晶体管blt0_p~blt2_p为关闭,而位线晶体管blt3_p为导通。借此可以通过导通的位线晶体管blt3_p将整体位线gbln(=1v)的电压传送至目标存储器单元smc。

[0074]

相似地,在进行读取时,源极线晶体管slt0_n~slt3_n为导通;源极线晶体管slt0_p~slt3_p为关闭。借此可以通过导通的源极线晶体管slt3_n将整体源极线gsln(=0v)的电压传送至目标存储器单元smc。

[0075]

在进行读取时,耦接至未选存储器单元的区域位线(如lbl0~lbl2)与区域源极线lsl(如lsl0~lsl2)例如但不受限于为0v;以及,耦接至被选存储器单元的区域位线(如lbl3)例如但不受限于为1v,而耦接至被选存储器单元的区域源极线lsl(如lsl3)例如但不受限于为0v。

[0076]

由于目标存储器单元smc的栅极电压为5v~7v,而其源极电压则为1v(lbl3的电压),vgs=5v~7v,所以,目标存储器单元smc可导通而被读取。另外,由于全部区域源极线

lsl0~lsl3被整体源极线gsl强迫至0v。所以,只有耦接至受选区域位线lbl3与受选字线(wl0_0)的目标存储器单元smc可被存取,至于其他存储器单元mc则无法导通。

[0077]

当电流流通目标存储器单元smc时,电流将流向感应放大器,且被转换成电压信号,该电压信号与一参考电压进行比较。如果该电压信号高于该参考电压,则该目标存储器单元smc被判断为低临界状态。相反地,如果该电压信号低于该参考电压,则该目标存储器单元smc被判断为高临界状态。

[0078]

也就是说,在本公开一实施例中,在进行读取时,区域源极线译码器210a将整体源极线电压传导至该多个存储器单元的一第一目标存储器单元;以及该区域位线译码器210b将一整体位线电压传导至该第一目标存储器单元。

[0079]

图4显示根据本公开一实施例的存储器装置的第一编程操作示意图。在进行第一编程时,各电压设定条件如下表3。

[0080]

表3

[0081][0082][0083]

在图4中,以字线wl0_0为受选字线而其他字线(如wl0_1、wl1_0、wl1_1)则为未选字线为例做说明。

[0084]

至于位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p的电压设定则是如后所述。

[0085]

当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为高电位(如4v),则nmos源极线晶体管slt0_n~slt3_n为导通;反之,当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为低电位(如-10v),则nmos源极线晶体管slt0_n~slt3_n为关闭。

[0086]

当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为高电位

(如4v),则pmos源极线晶体管slt0_p~slt3_p为关闭;反之,当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,没定为低电位(如-10v),则pmos源极线晶体管slt0_p~slt3_p为导通。

[0087]

当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为高电位(如4v),则nmos位线晶体管blt0_n~blt3_n为导通;反之,当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为低电位(如-10v),则nmos位线晶体管blt0_n~blt3_n为关闭。

[0088]

当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为高电位(如4v),则pmos位线晶体管blt0_p~blt3_p为关闭;反之,当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为低电位(如-10v),则pmos位线晶体管blt0_p~blt3_p为导通。

[0089]

通过上式电压控制,可以对目标存储器单元smc进行第一编程操作。详言之,在进行第一编程操作时,位线晶体管blt0_n~blt2_n为关闭而位线晶体管blt3_n为导通;位线晶体管blt0_p~blt2_p为导通,而位线晶体管blt3_p为关闭。因此,导通的位线晶体管blt3_n将整体源极线gsln(=-10v)的电压通过区域位线lbl3而传送至目标存储器单元smc。

[0090]

相似地,在进行第一编程时,源极线晶体管slt0_n~slt2_n为关闭;源极线晶体管slt3_n为导通;源极线晶体管slt0_p~slt2_p为导通而源极线晶体管slt3_p为关闭。因此,导通的源极线晶体管slt3_n将整体源极线gsln(=-10v)的电压通过区域源极线lsl3而传送至目标存储器单元smc。

[0091]

在进行第一编程时,耦接至未选存储器单元的区域位线(如lbl0~lbl2)与区域源极线lsl(如lsl0~lsl2)例如但不受限于为4v;以及,耦接至被选存储器单元的区域位线(如lbl3)例如但不受限于为-10v,而耦接至被选存储器单元的区域源极线lsl(如lsl3)例如但不受限于为-10v。

[0092]

在底下,为方便解说,将存储器单元分类为5种:t单元、a单元、b单元、c单元与d单元。t单元代表耦接至受选字线与受选区域位线/区域源极线的存储器单元。a单元代表耦接至未选字线与受选区域位线/区域源极线的存储器单元(跟t单元位于同一层)。b单元代表耦接至受选字线与未选区域位线/区域源极线的存储器单元。c单元代表耦接至未选字线与受选区域位线/区域源极线的存储器单元(跟t单元位于不同层)。d单元代表耦接至未选字线与未选区域位线/区域源极线的存储器单元。亦即,t单元为受选单元,而a单元、b单元、c单元与d单元则为未选单元。

[0093]

为方便了解,请参照图5a与图5b。图5a与图5b分别显示受选层与未选层的5种单元的示意图。

[0094]

以上述定义来看,在本公开实施例中,在进行第一编程操作时,受选t单元的vgs跨压为23v(13v-(-10v));未选a单元的vgs跨压为9v(-1v-(-10v));未选b单元的vgs跨压为9v(13v-(4v));未选c单元的vgs跨压为9v(-1v-(-10v));以及,未选d单元的vgs跨压为-5v(-1v-(4v))。

[0095]

也就是说,在本公开一实施例中,进行第一编程时,区域源极线译码器210a将整体源极线电压传导至该多个存储器单元的一第二目标存储器单元;以及区域位线译码器210b

将该整体源极线电压传导至该第二目标存储器单元。

[0096]

在本公开实施例中,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),整体源极线可将很低的电压(如-10v)送至受选区域位线与受选区域源极线,而未选区域位线与未选区域源极线的电压则可较高(如4v,只要未高于cmos崩溃电压(14v)即可)。故而,在本公开实施例中,可利用pmos晶体管来传送高电压(且不具本体效应)。相较之下,在现有技术中,由于是利用具有本体效应的nmos晶体管来传送高电压,故而,现有技术的本体效应较为严重。

[0097]

另外,在本公开实施例中,在进行第一编程操作时,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),受选区域位线与受选区域源极线的电压可同时通过晶体管而传送。所以,在本公开一实施例中,编程操作的速度可加快,且在编程脉冲起始时,不会出现短时间的瞬时压力问题(short-time transient stress issue)。

[0098]

图6显示根据本公开一实施例的存储器装置的第二编程操作示意图。在进行第二编程时,各电压设定条件如下表4。

[0099]

表4

[0100] 电压(v)gbln6gsln-8wl0_013other wls-1vps6vns-8vnwell_s6vpwell_s-8vpb6vnb-8vnwell_b6vpwell_b-8

[0101]

在图6中,以字线wl00为受选字线而其他字线(如wl0_1、wl1_0、wl1_1)则为未选字线为例做说明。

[0102]

至于位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p的电压设定则是如后所述。

[0103]

当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为高电位(如6v),则nmos源极线晶体管slt0_n~slt3_n为导通;反之,当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为低电位(如-8v),则nmos源极线晶体管slt0_n~slt3_n为关闭。

[0104]

当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为高电位(如6v),则pmos源极线晶体管slt0_p~slt3_p为关闭;反之,当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为低电位(如-8v),则pmos源极线晶体管slt0_p~

slt3_p为导通。

[0105]

当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为高电位(如6v),则nmos位线晶体管blt0_n~blt3_n为导通;反之,当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为低电位(如-8v),则nmos位线晶体管blt0_n~blt3_n为关闭。

[0106]

当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为高电位(如6v),则pmos位线晶体管blt0_p~blt3_p为关闭;反之,当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为低电位(如-8v),则pmos位线晶体管blt0_p~blt3_p为导通。

[0107]

通过上式电压控制,可以对目标存储器单元smc进行第二编程操作。详言之,在进行第二编程操作时,位线晶体管blt0_n~blt2_n为关闭而位线晶体管blt3_n为导通;位线晶体管blt0_p~blt2_p为导通,而位线晶体管blt3_p为关闭。因此,导通的位线晶体管blt3_n将整体源极线gsln(=-8v)的电压通过区域位线lbl3而传送至目标存储器单元smc。

[0108]

相似地,在进行第二编程时,源极线晶体管slt0_n~slt2_n为关闭;源极线晶体管slt3_n为导通;源极线晶体管slt0_p~slt2_p为导通而源极线晶体管slt3_p为关闭。因此,导通的源极线晶体管slt3_n将整体源极线gsln(=-8v)的电压通过区域源极线lsl3而传送至目标存储器单元smc。

[0109]

在进行第二编程时,耦接至未选存储器单元的区域位线(如lbl0~lbl2)与区域源极线lsl(如lsl0~lsl2)例如但不受限于为6v;以及,耦接至被选存储器单元的区域位线(如lbl3)例如但不受限于为-8v,而耦接至被选存储器单元的区域源极线lsl(如lsl3)例如但不受限于为-8v。

[0110]

以上述定义来看,在本公开实施例中,在进行第二编程操作时,受选t单元的vgs跨压为21v(13v-(-8v));未选a单元的vgs跨压为7v(-1v-(-8v));未选b单元的vgs跨压为7v(13v-(6v));未选c单元的vgs跨压为7v(-1v-(-8v));以及,未选d单元的vgs跨压为-7v(-1v-(6v))。

[0111]

也就是说,在本公开一实施例中,进行第二编程时,区域源极线译码器210a将整体源极线电压传导至该多个存储器单元的一第三目标存储器单元;以及区域位线译码器210b将该整体源极线电压传导至该第三目标存储器单元。

[0112]

在本公开实施例中,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),整体源极线可将很低的电压(如-8v)送至受选区域位线与受选区域源极线,而未选区域位线与未选区域源极线的电压则可较高(如6v,只要未高于cmos崩溃电压(14v)即可)。故而,在本公开实施例中,可利用pmos晶体管来传送高电压(且不具本体效应)。相较之下,在现有技术中,由于是利用具有本体效应的nmos晶体管来传送高电压,故而,现有技术的本体效应较为严重。

[0113]

另外,在本公开实施例中,在进行第二编程操作时,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),受选区域位线与受选区域源极线的电压可同时通过晶体管而传送。所以,在本公开一实施例中,编程操作的速度可加快,且在编程脉冲起始时,不会出现短时间的瞬时压力问题。

[0114]

图7显示根据本公开一实施例的存储器装置的字节擦除操作示意图。在进行字节擦除时,各电压设定条件如下表5。

[0115]

表5

[0116] 电压(v)gbln10gsln-4wl0_0-10other wls4vps10vns-4vnwell_s10vpwell_s-4vpb10vnb-4vnwell_b10vpwell_b-4

[0117]

在图7中,以字线wl0_0为受选字线而其他字线(如wl0_1、wl1_0、wl1_1)则为未选字线为例做说明。

[0118]

至于位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p的电压设定则是如后所述。

[0119]

当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为高电位(如10v),则nmos源极线晶体管slt0_n~slt3_n为导通;反之,当nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为低电位(如-4v),则nmos源极线晶体管slt0_n~slt3_n为关闭。

[0120]

当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为高电位(如10v),则pmos源极线晶体管slt0_p~slt3_p为关闭;反之,当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为低电位(如-4v),则pmos源极线晶体管slt0_p~slt3_p为导通。

[0121]

当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为高电位(如10v),则nmos位线晶体管blt0_n~blt3_n为导通;反之,当nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为低电位(如-4v),则nmos位线晶体管blt0_n~blt3_n为关闭。

[0122]

当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为高电位(如10v),则pmos位线晶体管blt0_p~blt3_p为关闭;反之,当pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为低电位(如-4v),则pmos位线晶体管blt0_p~blt3_p为导通。

[0123]

通过上式电压控制,可以对目标存储器单元smc进行字节擦除操作。详言之,在进行字节擦除操作时,位线晶体管blt0_n~blt2_n为导通而位线晶体管blt3_n为关闭;位线晶体管blt0_p~blt2_p为关闭,而位线晶体管blt3_p为导通。因此,导通的位线晶体管

blt3_p将整体位线gbln(=10v)的电压通过区域位线lbl3而传送至目标存储器单元smc。

[0124]

相似地,在进行字节擦除时,源极线晶体管slt0_n~slt2_n为导通;源极线晶体管slt3_n为关闭;源极线晶体管slt0_p~slt2_p为关闭而源极线晶体管slt3_p为导通。因此,导通的源极线晶体管slt3_p将整体位线gbln(=10v)的电压通过区域源极线lsl3而传送至目标存储器单元smc。

[0125]

在进行字节擦除时,耦接至未选存储器单元的区域位线(如lbl0~lbl2)与区域源极线lsl(如lsl0~lsl2)例如但不受限于为-4v;以及,耦接至被选存储器单元的区域位线(如lbl3)例如但不受限于为10v,而耦接至被选存储器单元的区域源极线lsl(如lsl3)例如但不受限于为10v。

[0126]

以上述定义来看,在本公开实施例中,在进行字节擦除操作时,受选t单元的vgs跨压为-20v(-10v-(10v));未选a单元的vgs跨压为-6v(4v-(10v));未选b单元的vgs跨压为-6v(-10v-(-4v));未选c单元的vgs跨压为-6v(4v-(10v));以及,未选d单元的vgs跨压为8v(4v-(-4v))。

[0127]

也就是说,在本公开一实施例中,进行字节擦除操作时,区域源极线译码器210a将整体位线电压传导至该多个存储器单元的一第四目标存储器单元;以及区域位线译码器210b将该整体位线电压传导至该第四目标存储器单元。

[0128]

在本公开实施例中,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),整体源极线可将很低的电压(如-4v)送至受选区域位线与受选区域源极线,而未选区域位线与未选区域源极线的电压则可较高(如10v,只要未高于cmos崩溃电压(14v)即可)。故而,在本公开实施例中,可利用pmos晶体管来传送高电压(且不具本体效应)。相较之下,在现有技术中,由于是利用具有本体效应的nmos晶体管来传送高电压,故而,现有技术的本体效应较为严重。

[0129]

另外,在本公开实施例中,在进行字节擦除操作时,由于各区域位线与各区域源极线耦接至成对pmos与nmos晶体管(blt0_n~blt3_n与blt0_p~blt3_p、slt0_n~slt3_n、slt0_p~slt3_p),受选区域位线与受选区域源极线的电压可同时通过晶体管而传送。所以,在本公开一实施例中,擦除操作的速度可加快,且在擦除脉冲起始时,不会出现短时间的瞬时压力问题。

[0130]

图8显示根据本公开一实施例的存储器装置的区块擦除操作示意图。在进行字节擦除时,各电压设定条件如下表6。

[0131]

表6

[0132][0133][0134]

在图8中,以字线wl0_0与wl0_1为受选字线而其他字线(如wl1_0、wl1_1)则为未选字线为例做说明。

[0135]

至于位线晶体管blt0_n~blt3_n与blt0_p~blt3_p,以及源极线晶体管slt0_n~slt3_n、slt0_p~slt3_p的电压设定则是如后所述。

[0136]

在进行区块擦除,将nmos源极线晶体管slt0_n~slt3_n的栅极电压例如但不受限于,设定为高电位(如-4v)以关闭nmos源极线晶体管slt0_n~slt3_n;将当pmos源极线晶体管slt0_p~slt3_p的栅极电压例如但不受限于,设定为低电位(如-4v)以导通pmos源极线晶体管slt0_p~slt3_p;将nmos位线晶体管blt0_n~blt3_n的栅极电压例如但不受限于,设定为高电位(如-4v)以关闭nmos位线晶体管blt0_n~blt3_n;以及,将pmos位线晶体管blt0_p~blt3_p的栅极电压例如但不受限于,设定为低电位(如-4v)以导通pmos位线晶体管blt0_p~blt3_p。

[0137]

通过上式电压控制,可以对目标存储器单元smc进行区块擦除操作。详言之,在进行区块擦除操作时,位线晶体管blt0_n~blt3_n为关闭;位线晶体管blt0_p~blt3_p为导通。因此,导通的位线晶体管blt0_p~blt3_p将整体位线gbln(=10v)的电压通过区域位线lbl1~lbl3而传送至该多个目标存储器单元smc。

[0138]

相似地,在进行区块擦除时,源极线晶体管slt0_n~slt3_n为关闭;源极线晶体管slt0_p~slt3_p为导通。因此,导通的源极线晶体管slt0_p~slt3_p将整体位线gbln(=10v)的电压通过区域源极线lsl1~lsl3而传送至该多个目标存储器单元smc。

[0139]

在进行区块擦除时,耦接至被选存储器单元的区域位线(如lbl1~lbl3)例如但不受限于为10v,而耦接至被选存储器单元的区域源极线lsl(如lsl1~lsl3)例如但不受限于为10v。

[0140]

以上述定义来看,在本公开实施例中,在进行区块擦除操作时,受选t单元的vgs跨压为-20v(-10v-(10v));未选a单元的vgs跨压为-6v(4v-(10v));未选b单元的vgs跨压为-20v(-10v-(10v));未选c单元的vgs跨压为-20v(-10v-(10v));以及,未选d单元的vgs跨压为-6v(4v-(10v))。

[0141]

也就是说,在本公开一实施例中,进行区块擦除操作时,区域源极线译码器210a将整体位线电压传导至该多个存储器单元的一至少一个第五目标存储器单元;以及区域位线译码器210b将该整体位线电压传导至该至少一个第五目标存储器单元。

[0142]

下表7显示本公开一实施例中,在各种操作下,该5种单元的vgs跨压。

[0143]

表7

[0144]

操作读取第一编程第二编程字节擦除区块擦除t单元4v~6v23v21v-20v-20va单元-1v9v7v-6v-6vb单元5v~7v9v7v-6v-20vc单元-1v9v7v-6v-20vd单元0v-5v-7v8v-6v

[0145]

从上表7可看出,在本公开实施例中,在第一编程操作中,受选t单元的vgs跨压可被加大(相较于现有技术),故而,本公开实施例可加速编程操作。

[0146]

此外,在第二编程操作中,可减少b单元的最大应力干扰(maximum stress disturbance)。

[0147]

至在字节擦除操作,b单元的应力可被减缓,从-8v减缓至-6v,而且不会受到本体效应的问题。

[0148]

故而,在本公开实施例中,相较于现有技术,编程操作与擦除操作可改善3维and存储器阵列的写入/擦除速度。

[0149]

综上所述,虽然本公开已以实施例公开如上,然其并非用以限定本公开。本公开所属技术领域的本领域技术人员,在不脱离本发明的精神和范围内,当可作各种的更改与修饰。因此,本发明的保护范围当视随附的权利要求书范围所界定的为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。