1.本发明涉及一种写入电压产生器,特别是一种运用于非易失性存储器的写入电压产生器。

背景技术:

2.众所周知,非易失存储器(non

‑

volatile memory)可在停止供电时仍持续地保存数据。非易失性存储器的种类很多。举例来说,磁阻式随机存取存储器(magnetoresistive random access memory,简称mram存储器)与电阻式随机存取存储器(resistive random

‑

access memory,简称rram存储器或者reram存储器)皆属于可编程可抹除的非易失性存储器(programmable

‑

erasable non

‑

volatile memory)。

3.请参照图1,其所绘示为已知mram存储器胞示意图。mram存储器胞110包括一开关晶体管ms与一存储元件(storage element)120,其中存储元件120又被称为磁穿隧接面(magnetic tunnel junction,简称mtj)。

4.mram存储器胞110具有三个端点a、b、s,其中端点s为控制端。开关晶体管ms的第一漏/源端(drain/source terminal)连接至节点c,开关晶体管ms的第二漏/源端连接至端点b,开关晶体管ms的栅极端(gate terminal)连接至端点s。其中,开关晶体管ms为nmos晶体管。

5.存储元件120包括堆迭的(stacked)一自由层(free layer)126、一阻绝层(isolation layer)124与一固定层(pin layer)122。存储元件120的固定层122连接至节点c,存储元件120的自由层126连接至端点a。

6.基本上,当固定层122与自由层126的磁化方向相同时,存储元件120具有较小的阻抗值(impedance)(例如2.0k欧姆),可视为mram存储器胞110的第一存储状态,又称为低阻抗状态(low impedance state)。当固定层122与自由层126的磁化方向不同时,存储元件120具有较大的阻抗值(例如4.0k欧姆),可视为mram存储器胞110的第二存储状态,又称为高阻抗状态(high impedance state)。因此,于写入动作(write operation)时,提供存储元件120不同的写入电压(write voltage)时,即可控制mram存储器胞110为第一存储状态或者第二存储状态。

7.当然,在图1中的mram存储器胞110中,也可以将存储元件120的固定层122连接至端点a,存储元件120的自由层126连接至节点c。

8.请参照图2a与图2b,其所绘示为mram存储器胞进行写入动作成为第一存储状态与第二存储状态的偏压示意图。基本上,于写入动作时,利用写入电压产生器(write voltage generator)提供不同的写入电压(write voltage)至mram存储器胞110即可选择性地控制mram存储器胞110成为第一存储状态或者第二存储状态。

9.如图2a所示,提供第一写入电压vw1至端点a,提供接地电压vss至端点b,提供开启电压(von)至端点s用以开启(turn on)开关晶体管ms。其中,第一写入电压vw1大于接地电压vss,接地电压vss为0v。

10.当开关晶体管ms开启后,存储元件120两端的电压差(voltage difference)vac到达第一转态电压(transition voltage)时,mram存储器胞110改变为第一存储状态,亦即低阻抗状态。

11.如图2b所示,提供第二写入电压vw2至端点b,提供接地电压vss至端点a,提供开启电压(von)至端点s用以开启(turn on)开关晶体管ms。其中,第二写入电压vw2大于接地电压vss,接地电压vss为0v。

12.当开关晶体管ms开启后,存储元件120两端的电压差(voltage difference)vca到达第二转态电压时,mram存储器胞110改变为第二存储状态,亦即高阻抗状态。

13.请参照图2c,其所绘示为存储元件在不同温度下的转态电压(transition voltage)与阻抗(rmtj)关系示意图。在常温下(例如25℃),为了将mram存储器胞110变更为第一存储状态,存储元件120的二端所接收的电压差(voltage difference)vac要大于0.5v时才能够改变状态。换句话说,由第二存储状态转换为第一存储状态的第一转态电压为0.5v。

14.另外,为了将mram存储器胞110变更为第二存储状态,存储元件120的二端所接收的电压差vac要小于

‑

0.4v(亦即,vca要大于0.4v)时才能够改变状态。换句话说,由第一存储状态转换为第二存储状态的第二转态电压为

‑

0.4v。

15.再者,温度越低时,存储元件120的转态电压的绝对值会越高。反之,温度越高时,存储元件120的转态电压的绝对值会越低。举例来说,于

‑

40℃时,第一转态电压会大于0.5v,第二转态电压会小于

‑

0.4v。于85℃时,第一转态电压会小于0.5v,第二转态电压会大于

‑

0.4v。

16.另外,由图2c可知,当存储元件120的二端所接收的电压差的绝对值大于崩溃电压(breakdown voltage,vbk)时,则存储元件120会永久损坏,存储元件120无法再变更存储状态。其中,崩溃电压vbk为0.54v。

17.由于mram存储器胞110中尚有开关晶体管ms,且开关晶体管ms可视为负载(load)。于写入动作时,在开关晶体管ms的二端会产生压降(voltage drop)。因此,于写入动作时,写入电压产生器(未绘示)供应的第一写入电压vw1需要大于第一转态电压。同理,写入电压产生器(未绘示)供应的第二写入电压vw2也要大于第二转态电压。以25℃为例,第一写入电压vw1需要大于0.5v,第二写入电压vw2需要大于0.4v。

18.另外,当多个存储器胞组合成存储器胞阵列(memory cell array)后,写入路径(write path)上会包括更多负载。请参照图3a,其所绘示为mram存储器胞所组成的mram存储器。mram存储器包括一存储器胞阵列300、一位线多工器(bit line multiplexer)310与一源极线多工器(source line multiplexer)320。其中,mram存储器为一种非挥性存储器。

19.存储器胞阵列300中包括m

×

n个mram存储器胞c11~cmn,每个存储器胞的结构相同于图1,此处不再赘述。

20.第一列n个存储器胞c11~c1n的控制端连接至字线wl1,第一列n个存储器胞c11~c1n的第一端连接至对应的位线bl1~bln,第一列n个存储器胞c11~c1n的第二端连接至对应的源极线sl1~sln。第二列n个存储器胞c21~c2n的控制端连接至字线wl2,第二列n个存储器胞c21~c21n的第一端连接至对应的位线bl1~bln,第二列n个存储器胞c11~c1n的第二端连接至对应的源极线sl1~sln,依此类推。第m列n个存储器胞cm1~cmn的控制端连接

至字线wlm,第m列n个存储器胞cm1~cmn的第一端连接至对应的位线bl1~bln,第m列n个存储器胞c11~c1n的第二端连接至对应的源极线sl1~sln。

21.位线多工器310包括n个选择晶体管mb1~mbn。n个选择晶体管mb1~mbn的第一漏/源端连接至第一电压接收端t1,n个选择晶体管mb1~mbn的第二漏/源端连接至对应的位线bl1~bln,n个选择晶体管mb1~mbn的栅极端接收对应的位线选择信号(bit line selecting signal)sb1~sbn。

22.源极线多工器320包括n个选择晶体管ms1~msn。n个选择晶体管ms1~msn的第一漏/源端连接至对应的源极线sl1~sln,n个选择晶体管ms1~msn的第二漏/源端连接至第二电压接收端t2,n个选择晶体管ms1~msn的栅极端接收对应的源极线选择信号(source line selecting signal)ss1~ssn。

23.另外,位线多工器310与源极线多工器320并不限定于图3a中的构造。也可以利用更多的晶体管设计更复杂的位线多工器与源极线多工器运用于mram存储器。

24.在写入动作时,n条字线wl1~wl1中仅有其中之一动作,其他则不动作。n个位线选择信号sb1~sbn中仅有其中之一动作,其他则不动作。n个源极线选择信号ss1~ssn中仅有其中之一动作,其他则不动作。

25.因此,根据动作的字线、位线选择信号与源极线选择信号,即可在存储器胞阵列300中决定一选定存储器胞(selected memory cell)。举例来说,动作字线wl1、位线选择信号sb1与源极线选择信号ss1时,存储器胞c11即为选定存储器胞。再者,提供特定电压至二个电压接收端t1、t2即可控制选定存储器胞为第一存储状态或者第二存储状态。

26.以下以存储器胞c11为选定存储器胞为例来进行说明。请参照图3b与图3c,其所绘示为对选定存储器胞进行写入动作成为第一存储状态与第二存储状态的偏压示意图。

27.如图3b所示,提供第一写入电压vw1至第一电压接收端t1,提供接地电压vss至第二电压接收端t2,提供开启电压(von)至字线wl1以动作字线wl1。其中,第一写入电压vw1大于接地电压vss,接地电压vss为0v。

28.当位线选择信号sb1与源极线选择信号ss1接收开启电压(von)而动作时,第一电压接收端t1与第二电压接收端t2之间形成写入路径。其中,写入路径包括:位线多工器310、位线bl1、选定存储器胞c11、源极线sl1与源极线多工器320。当选定存储器胞c11中存储元件120两端的电压差vac到达第一转态电压时,选定存储器胞c11改变为第一存储状态,亦即低阻抗状态。

29.如图3c所示,提供接地电压vss至第一电压接收端t1,提供第二写入电压vw2至第二电压接收端t2,提供开启电压(von)至字线wl1以动作字线wl1。其中,第二写入电压vw2大于接地电压vss,接地电压vss为0v。

30.当位线选择信号sb1与源极线选择信号ss1接收开启电压(von)而动作时,第一电压接收端t1与第二电压接收端t2之间形成写入路径。其中,写入路径包括:位线多工器310、位线bl1、选定存储器胞c11、源极线sl1与源极线多工器320。当选定存储器胞c11中存储元件120两端的电压差vca到达第二转态电压时,选定存储器胞c11改变为第二存储状态,亦即高阻抗状态。

31.由以上的说明可知,写入路径中除了存储元件120之外,包括更多负载(load),例如开关晶体管mb1、ms1、ms1。因此,写入电压产生器(未绘示)供应的第一写入电压vw1需要

大于第一转态电压,且写入电压产生器(未绘示)供应的第二写入电压vw2也需要大于第二转态电压。

32.然而,由于第一转态电压与崩溃电压vbk非常接近。如果第一写入电压vw1设定太高,可能造成存储元件120的二端所接收的电压大于崩溃电压vbk而损坏。反之,如果第一写入电压vw1设定太低,可能造成存储元件120无法成功转换为第一存储状态。

33.同理,如果第二写入电压vw2设定太高,可能造成存储元件120的二端所接收的电压大于崩溃电压vbk而损坏。反之,如果第二写入电压vw2设定太低,可能造成存储元件120无法成功转换为第二存储状态。

34.另外,由于存储元件120的二个转态电压会随着环境温度改变。再者,写入路径中的开关晶体管mb1、ms1、ms1的电阻值会随着制程角落(process corner)而变化。举例来说,当开关晶体管属于“慢制程角落(slow corner,scorner)”晶体管时,其内阻(internal resistance)较大。当开关晶体管被归类于“快制程角落(fast corner,f corner)”晶体管时,其内阻较小。

35.由以上的说明可知,设计出能够根据环境温度变化以及制程角落不同而产生适当写入电压的写入电压产生器是非常的困难。

技术实现要素:

36.本发明涉及一种写入电压产生器,耦接于一存储器胞阵列,该写入电压产生器在一写入动作时提供一写入电压,用以改变该存储器胞阵列中一写入路径内一选定存储器胞的存储状态,该写入电压产生器包括:一温度补偿电路,该温度补偿电路根据一环境温度产生一转态电压,其中该环境温度越高,该转态电压越低;以及,一制程角落补偿电路,包括一电流镜、一存储元件等效电路与一写入路径等效电路,该电流镜接收该转态电压,该存储元件等效电路连接在该电流镜的一第一端与一接地端之间,该电流镜的一第二端连接至一第一节点,该写入路径等效电路连接在该第一节点与该接地端之间,且该写入电压由该第一节点输出。

37.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

38.图1为已知mram存储器胞示意图;

39.图2a与图2b为mram存储器胞进行写入动作成为第一存储状态与第二存储状态的偏压示意图;

40.图2c为存储元件在不同温度下的转态电压与阻抗关系示意图;

41.图3a为mram存储器胞所组成的mram存储器;

42.图3b与图3c为对选定存储器胞进行写入动作成为第一存储状态与第二存储状态的偏压示意图;

43.图4为本发明运用于mram存储器的写入电压产生器;

44.图5a与图5b为温度补偿电路的第一范例及其转态电压与温度的关系图;

45.图5c与图5d为温度补偿电路的第二范例及其转态电压与温度的关系图;

46.图5e与图5f为温度补偿电路的第三范例及其转态电压与温度的关系图;

47.图6a为制程角落补偿电路的第一范例;

48.图6b为制程角落补偿电路的第二范例,可提供第一写入电压;

49.图6c为制程角落补偿电路的第三范例,可提供第一写入电压;

50.图6d为制程角落补偿电路的第四范例,可提供第二写入电压;以及

51.图6e为制程角落补偿电路的第五范例,可提供第二写入电压。

52.【符号说明】

53.110:mram存储器胞

54.120:存储元件

55.122:固定层

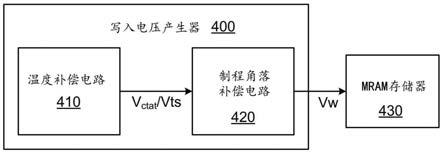

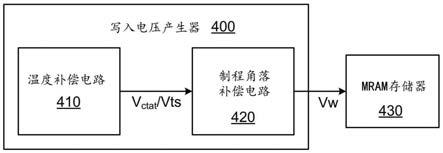

56.124:阻绝层

57.126:自由层

58.300:存储器胞阵列

59.310:位线多工器

60.320:源极线多工器

61.400:写入电压产生器

62.410,410a,410b,410c:温度补偿电路

63.420,420a,420b,420c,420d,420e:制程角落补偿电路

64.430:mram存储器

65.516,532,542,552,642:运算放大器

66.522:第一电压产生器

67.524:第二电压产生器

68.530:下限电压限制电路

69.540:缓冲电路

70.550:上限电压限制电路

71.560:ctat电路

72.610a,610b,610c,610d,610e:电流镜

73.620a,620b,620c,620d,620e:存储元件等效电路

74.630a,630b,630c,630d,630e:写入路径等效电路

75.652:第一参考存储元件

76.662:参考位线多工器

77.664b,664c,664d,664e:参考存储器胞

78.665:第二参考存储元件

79.666:参考源极线多工器

具体实施方式

80.请参照图4,其所绘示为本发明运用于mram存储器的写入电压产生器。写入电压产生器400包括:一温度补偿电路(temperature compensation circuit)410与一制程角落补偿电路(process corner compensation circuit)420。写入电压产生器400连接至mram存

储器430,写入电压产生器400可于写入动作时提供写入电压vw至mram 430。其中,mram存储器430的结构类似于图3a。写入电压vw可为第一写入电压(如图3b中的vw1),用以将mram存储器430内的选定存储器胞由第二存储状态改变为第一存储状态。或者,写入电压vw可为第二写入电压(如图3c中的vw2),用以将mram存储器430内的选定存储器胞由第一存储状态改变为第二存储状态。

81.根据本发明的实施例,温度补偿电路410根据环境温度产生转态电压vts,且环境温度越高,温度补偿电路410产生的转态电压vts越低。再者,制程角落补偿电路420接收转态电压vts,并产生写入电压vw。以下详细介绍温度补偿电路410与制程角落补偿电路420的详细结构。

82.由mram存储器胞的存储元件特性可知,当环境温度越高时,存储元件的转态电压会下降。当环境温度越低时,存储元件的转态电压会上升。因此,温度补偿电路410所产生的转态电压需要符合上述特性。

83.举例来说,温度补偿电路410可为负温度系数电路(complementary to absolute temperature circuit,以下简称ctat电路),其可产生电压v

ctat

作为转态电压vts。而在其他的实施例中,温度补偿电路410可包括ctat电路与辅助电路(auxiliary circuit),使得温度补偿电路410产生转态电压vts。

84.请参照图5a与图5b,其所绘示为温度补偿电路的第一范例及其转态电压与温度的关系图。其中,温度补偿电路410a由ctat电路来实现。

85.温度补偿电路410a由pmos晶体管m1~m3,pnp双载子晶体管(bjt)q1、q2、四个电阻r1、r21、r22、r3与运算放大器(operation amplifier)516所组成。其中,电阻r1的电阻值为r1,电阻r21与r22的电阻值为r2,电阻r3的电阻值为r3。再者,pmos晶体管m1~m3组成电流镜(current mirror)。在此范例中,pmos晶体管m1~m3具有相同的长宽比(aspect ratio,w/l)。其中,pmos晶体管m1~m3的栅极端相互连接,pmos晶体管m1~m3的第一漏/源端连接至供应电压vdd,pmos晶体管m1~m3的第二漏/源端可输出相同大小的电流。

86.另外,运算放大器516的输出端连接至pmos晶体管m1~m3的栅极端,pmos晶体管m1的第二漏/源端连接至运算放大器516的正输入端,pmos晶体管m2的第二漏/源端连接至运算放大器516的负输入端,pmos晶体管m3的第二漏/源端与接地端gnd之间连接电阻r3,pmos晶体管m3的第二漏/源端作为ctat电路的输出端可产生电压v

ctat

,且电压v

ctat

即为转态电压vts(亦即,v

ctat

=vts)。

87.再者,pnp双载子晶体管q1面积为pnp双载子晶体管q2面积的n倍。pnp双载子晶体管q1、q2的基极(base)与集电极(collector)连接至接地端gnd,使得pnp双载子晶体管q1、q2形成二极管式连接(diode connected)。再者,运算放大器516的负输入端连接至pnp双载子晶体管q2的发射极(emitter),运算放大器516的负输入端与接地端gnd之间连接电阻r21。运算放大器516的正输入端与pnp双载子晶体管q1的发射极(emitter)之间连接电阻r1,运算放大器516的正输入端与接地端gnd之间连接电阻r22。

88.基本上,在运算放大器516具有无限大的增益下,运算放大器516的负输入端电压v

‑

与正输入端电压v

会相等。因此,r1

×

i1 v

eb1

=v

eb2

。

89.由于q1与q2形成二极管式连接且q1面积为q2面积的n倍,所以,与

进而推导出v

be1

=v

t

ln(i1/n

·

i

s

)与v

be2

=v

t

ln(i1/i

s

)。其中,i

s

为q2的饱和电流(saturation current),v

t

为热电压(thermal voltage)。

90.因此,可获得i1=v

t

ln(n)/r1,i2=v

eb2

/r2,v

ctat

=vts=(r3/r2)v

eb2

ln(n)(r3/r1)v

t

。

91.由上述的电压v

ctat

的表示式可知,电压v

ctat

(亦即转态电压vts)等于基射电压产生器(base

‑

emitter voltage generator)产生的基射电压v

be2

乘以第一常数(r3/r2)加上热电压产生器(thermal voltage generator)产生的热电压v

t

乘以一第二常数(ln(n)(r3/r1))。

92.如图5b所示,由于v

eb2

=i2

×

r2具有负温度系数,且基射电压v

be2

具有负温度系数(negative temperature coefficient),因此第一常数(r3/r2)乘以v

eb2

的特性曲线i会随着绝对温度上升而下降。另外,第一常数(r3/r2)可以决定特性曲线i的斜率。同理,由于热电压v

t

具有正温度系数(positive temperature coefficient),因此第二常数(ln(n)(r3/r1))乘以热电压v

t

的特性曲线ii会随着绝对温度上升而上升。另外,第二常数(ln(n)(r3/r1))可以决定特性曲线ii的斜率。再者,适当地调整第一常数与第二常数后,即产生电压v

ctat

的特性曲线iii,并且电压v

ctat

随着环境温度上升而下降。

93.基本上,本发明并不限定于图5a的ctat电路来作为温度补偿电路410a。在此领域的技术人员也可以利用其他构造的ctat电路来作为温度补偿电路。

94.请参照图5c与图5d,其所绘示为温度补偿电路的第二范例及其转态电压与温度的关系图。温度补偿电路410b由另一ctat电路来实现。

95.温度补偿电路410b包括一第一电压产生器522与一第二电压产生器524。其中,第一电压产生器522产生具有负温度系数的第一电压v1,第二电压产生器524产生具有正温度系数的第二电压v2。再者,第一电压v1乘上第一常数c1加上第二电压v2乘上第二常数c2即为电压v

ctat

。亦即,温度补偿电路410b的输出端可产生电压v

ctat

,且电压v

ctat

=c1

×

v1 c2

×

v2。

96.以ctat电路为例,第一电压产生器522可视为基射电压产生器,第一电压v1可视为双载子晶体管的基射电压(例如v

eb2

)。第二电压产生器524可视为热电压产生器,第二电压v2可视为热电压v

t

。

97.如图5d所示,i为c1

×

v1的特性曲线,ii为c2

×

v2的特性曲线,iii为电压v

ctat

的特性曲线。由于第一电压v1具有负温度系数,因此c1

×

v1的特性曲线i会随着绝对温度上升而下降。另外,第一常数c1可以决定特性曲线i的斜率。同理,由于第二电压v2具有正温度系数,因此c2

×

v2的特性曲线ii会随着绝对温度上升而上升。另外,第二常数c2可以决定特性曲线ii的斜率。换句话说,适当地调整第一常数c1与第二常数c2后,即产生电压v

ctat

的特性曲线iii,并且电压v

ctat

随着环境温度上升而下降。

98.请参照图5e与图5f,其所绘示为温度补偿电路的第三范例及其转态电压与温度的关系图。温度补偿电路410c包括一ctat电路560、一缓冲电路(buffering circuit)540、一下限电压限制电路(lower voltage limiting circuit)530与一上限电压限制电路(upper voltage limiting circuit)550。其中,ctat电路560可为图5a或者图5c所示的ctat电路,此处不再赘述。

99.ctat电路560的电压输出端连接至缓冲电路540。缓冲电路540包括一运算放大器542,运算放大器542的正输入端连接至ctat电路542的电压输出端以接收电压vctat,运算放大器542的负输入端连接至运算放大器542的输出端,运算放大器542的输出端连接至节点x。

100.下限电压限制电路530包括一运算放大器532与一pmos晶体管mp1。下限电压限制电路530的输入端接收下限电压v

l

,下限电压限制电路530的输出端连接至节点x。运算放大器532的负输入端接收一下限电压v

l

,运算放大器532的正输入端连接至节点x。pmos晶体管mp1的第一漏/源端接收供应电压vdd,pmos晶体管mp1的栅极端连接至运算放大器532的输出端,pmos晶体管mp1的第二漏/源端连接至节点x。

101.上限电压限制电路550包括一运算放大器552与一nmos晶体管mn1。上限电压限制电路550的输入端接收上限电压v

h

,上限电压限制电路550的输出端连接至节点x。运算放大器552的负输入端接收一上限电压v

h

,运算放大器552的正输入端连接至节点x。nmos晶体管mn1的第一漏/源端连接至接地端gnd,nmos晶体管mn1的栅极端连接至运算放大器552的输出端,nmos晶体管mn1的第二漏/源端连接至节点x。其中,上限电压v

h

大于下限电压v

l

。

102.由图5f可知,温度补偿电路410c所提供的转态电压vts会被限制在上限电压v

h

与下限电压v

l

之间,且转态电压vts随着环境温度上升而下降。根据本发明的实施例,上限电压限制电路550中的上限电压v

h

可以设定为低于存储元件的崩溃电压vbk(例如0.53v)。因此,可以防止mram存储器胞内的存储元件所接收的电压超过崩溃电压vbk,以确保mram存储器胞内的存储元件不会损毁。

103.在其他的实施例中,温度补偿电路410c也可以利用二个电压限制电路530与550的其中之一即可。举例来说,温度补偿电路410c中仅利用上限电压限制电路550来限制转态电压vts不会超过崩溃电压vbk。

104.请参照图6a,其所绘示为制程角落补偿电路的第一范例。制程角落补偿电路420a包括一电流镜610a、存储元件等效电路(equivalent circuit of storage element)620a与写入路径等效电路(equivalent circuit of write path)630a。

105.电流镜610a接收温度补偿电路输出的转态电压vts或者电压v

ctat

。电流镜610a包括一第一端与一第二端。存储元件等效电路620a连接在第一端与接地端gnd之间。再者,第二端连接在节点y,且写入路径等效电路630a连接在节点y与接地端gnd之间。其中,写入电压vw由节点y输出。

106.根据本发明的实施例,电流镜610a接收转态电压vts或者电压v

ctat

,并将转态电压vts或者电压v

ctat

提供至第一端。因此,存储元件等效电路620a根据转态电压vts或者电压v

ctat

来产生输入电流ix。

107.再者,根据输入电流ix,电流镜610a的第二端产生镜射电流iy并流至写入路径等效电路630a。因此,镜射电流iy流经写入路径等效电路630a而产生写入电压vw,并由节点y输出写入电压vw。其中,输入电流ix等于镜射电流iy。

108.根据本发明的实施例,制程角落补偿电路在写入动作时可提供不同的写入电压至mram 430。举例来说,制程角落补偿电路提供第一写入电压vw1来将选定存储器胞由第二存储状态改变为第一存储状态。或者,制程角落补偿电路提供第二写入电压vw2来将选定存储器胞由第一存储状态改变为第二存储状态。以下进一步说明之。

109.请参照图6b,其所绘示为制程角落补偿电路的第二范例,其可提供第一写入电压。制程角落补偿电路420b包括一电流镜610b、存储元件等效电路620b与写入路径等效电路630b。

110.电流镜610b接收温度补偿电路输出的转态电压vts。电流镜610b包括:一运算放大器642与pmos晶体管mp2~mp5。其中,pmos晶体管mp2~mp5具有相同的长宽比(w/l)。

111.运算放大器642的负输入端接收转态电压vts,运算放大器642的正输入端连接至节点z,其中节点z为电流镜610b的第一端。

112.pmos晶体管mp2、mp3的第一漏/源端接收供应电压vdd,pmos晶体管mp2、mp3的栅极端连接至运算放大器642的输出端。pmos晶体管mp4、mp5的栅极端接收一偏压电压(bias voltage,vb)。pmos晶体管mp4的第一漏/源端连接至pmos晶体管mp2的第二漏/源端,pmos晶体管mp4的第二漏/源端连接至节点z。pmos晶体管mp5的第一漏/源端连接至pmos晶体管mp3的第二漏/源端,pmos晶体管mp5的第二漏/源端连接至节点y。其中,节点y为电流镜610b的第二端,且第一写入电压vw1由节点y输出。

113.存储元件等效电路620b包括一第一参考存储元件652。第一参考存储元件652的结构相同于图1中的存储元件120,其结构不再赘述。再者,电流镜610b将转态电压vts提供至第一端。因此,第一存储元件652根据转态电压vts产生输入电流ix,而电流镜610b的第二端可以根据输入电流ix来产生镜射电流iy。

114.写入路径等效电路630b包括:参考位线多工器662、参考位线blref、参考存储器胞664b、参考源极线slref与参考源极线多工器666。再者,参考存储器胞664b中包括第二参考存储元件665、一参考选择晶体管mref与参考字线wlref,且参考字线wlref可接收开启电压(von)。基本上,写入路径等效电路630b的结构相同于图3b的写入路径,其结构不再赘述。

115.再者,根据输入电流ix,电流镜610b的第二端产生镜射电流iy并流至写入路径等效电路630b。因此,镜射电流iy流经写入路径等效电路630b而产生第一写入电压vw1,并且第一写入电压vw1由节点y输出。其中,输入电流ix等于镜射电流iy。

116.根据本发明的实施例,由于mram存储器与写入电压产生器会同时制作。因此,mram存储器以及写入电压产生器中的所有晶体管会有相同的制程角落。

117.也就是说,制程角落补偿电路420b中的写入路径等效电路630b与存储器胞阵列中的写入路径有相同的电路结构与电阻值。因此,写入电压产生器400所输出的第一写入电压vw1可使得存储器胞阵列中写入路径的选定存储器胞顺利地改变为第一存储状态。亦即,选定存储器胞中的存储元件可以接收转态电压vts而改变为第一存储状态。

118.举例来说,当第一参考存储元件652与第二参考存储元件665皆为第二存储状态时,制程角落补偿电路420b能够提供第一写入电压vw1。由于第一参考存储元件652、第二参考存储元件665以及选定存储器胞内的存储元件有几乎相等的电阻值,因此存储器胞阵列中的选定存储器胞可成功地由第二存储状态改变为第一存储状态。

119.请参照图6c,其所绘示为制程角落补偿电路的第三范例,其可产生第一写入电压vw1。制程角落补偿电路420c包括一电流镜610c、存储元件等效电路620c与写入路径等效电路630c。其中,电流镜610c的结构相同于图6b的电流镜610b,此处不再赘述。

120.存储元件等效电路620c包括:第一参考电阻r1ref,第一参考电阻r1ref为可变电阻。第一参考电阻r1ref可调整至第二存储状态的电阻值(例如4k欧姆)。相同地,电流镜

610c将转态电压vts提供至第一端。因此,第一参考电阻r1ref产生输入电流ix,而电流镜610b的第二端可以根据输入电流ix来产生镜射电流iy。

121.写入路径等效电路630c包括:参考位线多工器662、位线等效电阻r

bl

、参考存储器胞664c、源极线等效电阻r

sl

与参考源极线多工器666。再者,参考存储器胞664c中包括第二参考电阻r2ref、一参考选择晶体管mref与参考字线wlref,且参考字线wlref可接收开启电压(von)。

122.相较于图6b的写入路径等效电路630b,图6c的写入路径等效电路630c中以位线等效电阻r

bl

与源极线等效电阻r

sl

来取代参考位线blref以及参考源极线slref。并且,以第二参考电阻r2ref来取代第二参考存储元件665。再者,第二参考电阻r2ref为可变电阻。第二参考电阻r2ref可调整至第二存储状态的电阻值(例如4k欧姆)。

123.相同地,根据输入电流ix,电流镜610b的第二端产生镜射电流iy并流至写入路径等效电路630c。因此,镜射电流iy流经写入路径等效电路630c而产生第一写入电压vw1,且第一写入电压vw1由节点y输出。其中,输入电流ix等于镜射电流iy。

124.举例来说,当第一参考电阻r1ref与第二参考电阻r2ref皆为4k欧姆(第二存储状态)时,制程角落补偿电路420c能够提供第一写入电压vw1。由于第一参考电阻r1ref与第二参考电阻r2ref以及选定存储器胞内的存储元件有几乎相等的电阻值,因此存储器胞阵列中的选定存储器胞可成功地由第二存储状态改变为第一存储状态。

125.请参照图6d,其所绘示为制程角落补偿电路的第四范例,其可提供第二写入电压。制程角落补偿电路420d包括一电流镜610d、存储元件等效电路620d与写入路径等效电路630d。其中,电流镜610d与存储元件等效电路620d的结构相同于图6b的电流镜610b与存储元件等效电路620b,此处不再赘述。

126.写入路径等效电路630d包括:参考位线多工器662、参考位线blref、参考存储器胞664d、参考源极线slref与参考源极线多工器666。再者,参考存储器胞664d中包括第二参考存储元件665、一参考选择晶体管mref与参考字线wlref,且参考字线wlref可接收开启电压(von)。

127.在写入路径等效电路630d中,参考源极线多工器666连接在节点y与参考源极线slref之间。参考位线多工器662连接在接地端gnd与参考位线blref之间。参考选择晶体管mref连接至参考位线blref、参考源极线slref与参考字线wlref。

128.相同地,根据输入电流ix,电流镜610d的第二端产生镜射电流iy并流至写入路径等效电路630d。因此,镜射电流iy流经写入路径等效电路630d而产生第二写入电压vw2,并且第二写入电压vw2由节点y输出。其中,输入电流ix等于镜射电流iy。

129.根据本发明的实施例,制程角落补偿电路420d中的写入路径等效电路630d与存储器胞阵列中的写入路径有相同的电路结构与电阻值。因此,写入电压产生器400所输出的第二写入电压vw2可使得存储器胞阵列中写入路径的选定存储器胞顺利地改变为第二存储状态。亦即,选定存储器胞中的存储元件可以接收转态电压vts而改变为第二存储状态。

130.举例来说,当第一参考存储元件620d与第二参考存储元件665皆为第一存储状态时,制程角落补偿电路420d能够提供第二写入电压vw2。由于第一参考存储元件620d、第二参考存储元件665以及选定存储器胞内的存储元件有几乎相等的电阻值,因此存储器胞阵列中的选定存储器胞可成功地由第一存储状态改变为第二存储状态。

131.请参照图6e,其所绘示为制程角落补偿电路的第五范例,其可产生第二写入电压vw2。制程角落补偿电路420e包括一电流镜610e、存储元件等效电路620e与写入路径等效电路630e。其中,电流镜610e与存储元件等效电路620e的结构相同于图6c的电流镜610c与存储元件等效电路620c,此处不再赘述。

132.写入路径等效电路630e包括:参考位线多工器662、位线等效电阻r

bl

、参考存储器胞664e、源极线等效电阻r

sl

与参考源极线多工器666。再者,参考存储器胞664e中包括第二参考电阻r2ref、一参考选择晶体管mref与参考字线wlref,且参考字线wlref可接收开启电压(von)。

133.相较于图6d的写入路径等效电路630d,图6e的写入路径等效电路630e中以位线等效电阻r

bl

与源极线等效电阻r

sl

来取代参考位线blref以及参考源极线slref。并且,以第二参考电阻r2ref来取代第二参考存储元件665。再者,第二参考电阻r2ref为可变电阻。第二参考电阻r2ref可调整至第一存储状态的电阻值(例如2.0k欧姆)。

134.相同地,根据输入电流ix,电流镜610e的第二端产生镜射电流iy并流至写入路径等效电路630e。因此,镜射电流iy流经写入路径等效电路630e而产生第二写入电压vw2,且第二写入电压vw2由节点y输出。其中,输入电流ix等于镜射电流iy。

135.举例来说,当第一参考电阻r1ref与第二参考电阻r2ref皆为2k欧姆(第一存储状态)时,制程角落补偿电路420e能够提供第二写入电压vw2。由于第一参考电阻r1ref与第二参考电阻r2ref以及选定存储器胞内的存储元件有几乎相等的电阻值,因此存储器胞阵列中的选定存储器胞可成功地由第一存储状态改变为第二存储状态。

136.再者,上述图6a至图6e的制程角落补偿电路420a~420e中更可包括一稳压器(voltage regulator)。稳压器的输入端连接在节点y,接收写入电压vw。稳压器的输出端可以产生相同的写入电压vw。稳压器的功能类似于缓冲电路用以提升写入电压产生器的驱动能力(driving strength)。

137.根据本发明的实施例,由于mram存储器与写入电压产生器是同时制造完成,因此所有的晶体管会属于相同的制程角落。在本发明中,电流镜610a~610e的功能在于提供镜射电流iy,用以确保写入路径等效电路630a~630e中的第二存储元件能够接收到转态电压vts,且写入路径等效电路630a~630e能够产生正确的写入电压。再者,由于写入路径等效电路630a~630e的结构几乎相同于mram存储器中的写入路径。因此,当mram存储器接收到写入电压产生器400输出的写入电压时,写入路径中选定存储器胞的存储元件即可接收到转态电压vts而成功地改变存储状态。

138.当然,运用本发明所公开的技术,在此领域的技术人员也可以制作二个写入电压产生器,并提供至mram存储器。其中,第一个写入电压产生器产生第一写入电压,第二个写入电压产生器产生第二写入电压。

139.由以上的实施例可知,本发明的写入电压产生器是运用于mram存储器。当然,本发明的技术也可以运用于其他种类的非易失性存储器。举例来说,本发明的写入电压产生器是运用于rram存储器或者reram存储器。

140.由以上的说明可知,本发明提出一种运用于非易失性存储器的写入电压产生器。写入电压产生器包括一温度补偿电路与一制程角落补偿电路。温度补偿电路可根据环境温度的变化产生一转态电压,制程角落补偿电路可根据存储器胞阵列的制程角落来产生写入

电压至写入路径。如此,在写入动作时,将可以确保存储器胞阵列内写入路径中的选定存储器胞能够改变存储状态。

141.综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属领域技术人员在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视所附权利要求书界定范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。