技术特征:

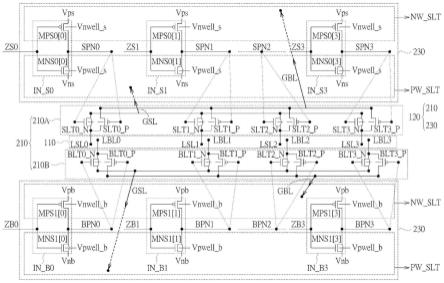

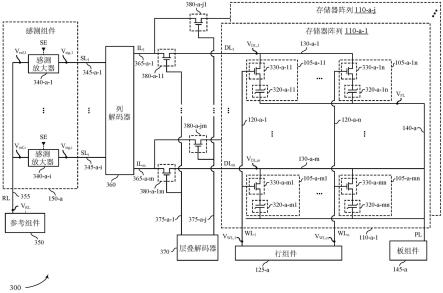

1.一种存储器装置,包括:一存储器阵列;一译码电路,耦接至该存储器阵列,该译码电路包括多个第一晶体管、多个第二晶体管,与多个反相器,所述多个第一晶体管与所述多个第二晶体管为成对的;以及一控制器,耦接至该译码电路,其中,成对的所述多个第一晶体管与所述多个第二晶体管的每对系分别耦接至这些反相器之一,以及分别耦接至多条区域位线之一或多条区域源极线之一;所述多个第一晶体管耦接至一整体位线;以及所述多个第二晶体管耦接至一整体源极线。2.根据权利要求1所述的存储器装置,其中,所述多个第一晶体管与所述多个第二晶体管组成一区域源极线译码器与一区域位线译码器;所述多个第一晶体管与所述多个第二晶体管分别通过所述多个区域位线或所述多个区域源极线而耦接至该存储器阵列;以及所述多个区域源极线与所述多个区域位线被成对的所述多个第一晶体管与所述多个第二晶体管所控制。3.根据权利要求2所述的存储器装置,其中,在进行一读取操作时,该区域源极线译码器将一整体源极线电压传导至所述多个存储器单元的一第一目标存储器单元;以及该区域位线译码器将一整体位线电压传导至该第一目标存储器单元。4.根据权利要求2所述的存储器装置,其中,在进行一第一编程操作时,该区域源极线译码器将一整体源极线电压传导至所述多个存储器单元的一第二目标存储器单元;以及该区域位线译码器将该整体源极线电压传导至该第二目标存储器单元。5.根据权利要求2所述的存储器装置,其中,在进行一第二编程操作时,该区域源极线译码器将一整体源极线电压传导至所述多个存储器单元的一第三目标存储器单元;以及该区域位线译码器将该整体源极线电压传导至该第三目标存储器单元。6.根据权利要求2所述的存储器装置,其中,在进行一字节擦除操作时,该区域源极线译码器将一整体位线电压传导至所述多个存储器单元的一第四目标存储器单元;以及该区域位线译码器将该整体位线电压传导至该第四目标存储器单元。7.根据权利要求2所述的存储器装置,其中,在进行一区块擦除操作时,该区域源极线译码器将一整体位线电压传导至所述多个存储器单元的一至少一个第五目标存储器单元;以及该区域位线译码器将该整体位线电压传导至该至少一个第五目标存储器单元。8.一种存储器装置的操作方法,包括:由成对的多个第一晶体管与多个第二晶体管控制多条区域源极线与多条区域位线,

其中,所述多个第一晶体管与所述多个第二晶体管是三极晶体管;所述多个第一晶体管耦接至一整体位线;以及所述多个第二晶体管耦接至一整体源极线。9.根据权利要求8所述的存储器装置的操作方法,其中,所述多个第一晶体管与所述多个第二晶体管组成一区域源极线译码器与一区域位线译码器;以及所述多个第一晶体管与所述多个第二晶体管分别通过所述多个区域位线或所述多个区域源极线而耦接至该存储器阵列。10.根据权利要求9所述的存储器装置的操作方法,其中,在进行一读取操作时,该区域源极线译码器将一整体源极线电压传导至多个存储器单元的一第一目标存储器单元;以及该区域位线译码器将一整体位线电压传导至该第一目标存储器单元。11.根据权利要求9所述的存储器装置的操作方法,其中,在进行一第一编程操作时,该区域源极线译码器将一整体源极线电压传导至多个存储器单元的一第二目标存储器单元;以及该区域位线译码器将该整体源极线电压传导至该第二目标存储器单元。12.根据权利要求9所述的存储器装置的操作方法,其中,在进行一第二编程操作时,该区域源极线译码器将一整体源极线电压传导至多个存储器单元的一第三目标存储器单元;以及该区域位线译码器将该整体源极线电压传导至该第三目标存储器单元。13.根据权利要求9所述的存储器装置的操作方法,其中,在进行一字节擦除操作时,该区域源极线译码器将一整体位线电压传导至多个存储器单元的一第四目标存储器单元;以及该区域位线译码器将该整体位线电压传导至该第四目标存储器单元。14.根据权利要求9所述的存储器装置的操作方法,其中,在进行一区块擦除操作时,该区域源极线译码器将一整体位线电压传导至多个存储器单元的一至少一个第五目标存储器单元;以及该区域位线译码器将该整体位线电压传导至该至少一个第五目标存储器单元。

技术总结

本公开提供了一种存储器装置与其操作方法。存储器装置包括:一存储器阵列;一译码电路,耦接至该存储器阵列,该译码电路包括多个第一晶体管、多个第二晶体管,与多个反相器,所述多个第一晶体管与所述多个第二晶体管为成对;以及一控制器,耦接至该译码电路,其中,成对的所述多个第一晶体管与所述多个第二晶体管的每对所述第一晶体管与所述第二晶体管分别耦接至所述多个反相器之一,以及分别耦接至多条区域位线之一或多条区域源极线之一;所述多个第一晶体管耦接至一整体位线;以及所述多个第二晶体管耦接至一整体源极线。个第二晶体管耦接至一整体源极线。个第二晶体管耦接至一整体源极线。

技术研发人员:林永丰 罗思觉 叶腾豪 吕函庭

受保护的技术使用者:旺宏电子股份有限公司

技术研发日:2021.05.28

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。