具有二次相位生成电路的电子设备

1.本技术要求2021年9月7日提交的美国专利申请第17/468482号的优先权,该专利申请据此全文以引用方式并入本文。

技术领域

2.本公开整体涉及电子设备,并且更具体地涉及具有无线电路的电子设备。

背景技术:

3.电子设备常具备无线能力。具有无线能力的电子设备具有包括一个或多个天线的无线电路。无线电路有时用于执行空间测距操作,其中使用射频信号来估计电子设备与外部对象之间的距离。

4.设计准确估计该距离的无线电路可能是具有挑战性的。为了执行空间测距操作,无线电路有时生成恒幅零自相关(cazac)序列,诸如zadoff-chu序列。然而,zadoff-chu序列的常规生成仍会产生具有量化误差的结果,因此估计距离不准确。

技术实现要素:

5.电子设备可包括无线电路。无线电路可以包括空间测距电路和天线。在本文中作为示例描述的一个实施方案中,空间测距电路包括雷达电路,诸如频率调制的连续波(fmcw)雷达电路。雷达电路可在发射路径中包括二次相位发生器。二次相位发生器可输出内插恒幅零自相关(cazac)序列,该内插恒幅零自相关序列可通过一个或多个数模转换器(dac)反馈以产生最终由天线发射的模拟信号。由于数模转换器具有有限带宽,并且频带边缘始终被干扰(例如,被抗混叠电路干扰),因此必须对cazac序列进行内插。二次相位发生器可包括开关、用于控制该开关的数控振荡器、被配置为从该开关接收信号的第一积分器级和与该第一积分器级串联连接的第二积分器级。当数控振荡器输出小于或等于阈值水平的值时,开关可向第一积分器级输出与啁啾计数q成比例的第一值。当数控振荡器输出超过阈值水平的值时,开关可另选地输出与啁啾计数q和字长m的差值成比例的第二值。使用加权系数b可调整cazac序列的内插量,因此,在固定dac采样频率下,可发射具有可变带宽的啁啾。以这种方式生成的内插cazac序列表现出q个啁啾,每个啁啾具有不同的二次相位响应,该不同的二次相位响应转化为线性瞬时频率响应,啁啾之间没有频率异常值。

6.本公开的一个方面提供了一种无线电路,该无线电路包括:至少一个数模转换器,该至少一个数模转换器具有耦接到天线的输入端和输出端;和二次相位发生器,该二次相位发生器具有:耦接到该至少一个数模转换器的该输入端的输出端口,具有输入端和输出端的第一积分器级,具有耦接到该第一积分器级的该输出端的输入端并且具有连接到该输出端口的输出端的第二积分器级,和具有第一输入端、第二输入端和耦接到该第一积分器级的该输入端的输出端的开关。二次相位发生器可被配置为在输出端口处输出恒幅零自相关(cazac)序列。cazac序列在几乎所有实际应用程序中完全内插,因此有时称为内插cazac序列。开关的第一输入端可接收第一值,该第一值是定义cazac序列中啁啾数目的啁啾计数

q的函数。开关的第二输入端可接收第二值,该第二值是啁啾计数q和定义cazac序列中样本数目的字长m的函数。第一值和第二值可任选地乘以缩放系数b以降低二次相位发生器的带宽。二次相位发生器可包括用于控制开关的数控振荡器,该开关被配置为当由该数控振荡器输出的值小于或等于阈值时将该开关的第一输入端连接到该开关的输出端,并且当由该数控振荡器输出的该值大于阈值时将该开关的第二输入端连接到该开关的输出端。

7.本公开的一个方面提供了一种用于操作无线电路的方法。该方法可包括在数模转换器处接收数字信号并且将该数字信号转换为用于经由天线发射的模拟信号,并且从二次相位发生器输出内插恒幅零自相关(cazac)序列。基于从二次相位发生器输出的内插cazac序列可生成在数模转换器处接收的数字信号。操作二次相位发生器可涉及:控制开关以选择性地输出第一值和第二值到第一积分器级、在第二积分器级处从该第一积分器级接收信号以及从该第二积分器级输出内插cazac序列。

8.该方法还可包括:基于从数控振荡器输出的值控制开关,周期性地递增从该数控振荡器输出的值,以及确定从该数控振荡器输出的值是否超过阈值。响应于确定从该数控振荡器输出的该值不超过该阈值,该开关可将第一值输出到第一积分器级。响应于确定从该数控振荡器输出的该值超过该阈值,该开关可将第二值输出到第一积分器级,其中第二值小于第一值。

9.本公开的一个方面提供了一种电子设备,该电子设备包括:具有被配置为输出内插恒幅零自相关(cazac)序列的二次相位发生器的基带发射器,具有被配置为接收基于内插cazac序列生成的信号的输入端和耦接到第一天线的输出端的数模转换器,插置在基带发射器与数模转换器的输入端之间的第一信道滤波器,具有耦接到第二天线的输入端并且具有在其上生成数字信号的输出端的模数转换器,具有被配置为接收基于从该模数转换器输出的数字信号生成的信号的输入端的基带接收器,和插置在模数转换器的输出端与基带接收器的输入端之间的第二信道滤波器。第一信道滤波器和第二信道滤波器可具有与二次相位发生器相同的带宽。该电子设备还可包括插置在模数转换器的输出端与第二信道滤波器之间的偏移校正电路和耦接在基带发射器与基带接收器之间的延迟补偿电路。

附图说明

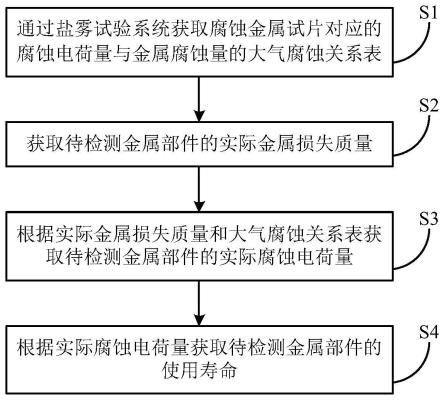

10.图1是根据一些实施方案的具有无线电路的例示性电子设备的功能框图。

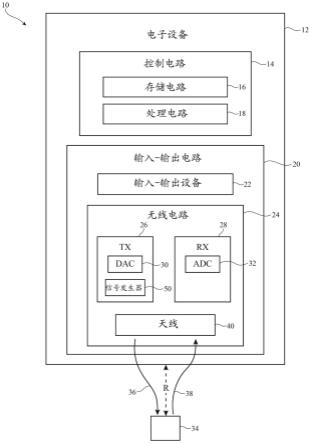

11.图2是根据一些实施方案的具有二次相位发生器的例示性数字极性发射器电路的电路图。

12.图3是根据一些实施方案的具有二次相位发生器的例示性iq发射器电路的电路图。

13.图4是根据一些实施方案的例示性全带宽二次相位发生器的框图。

14.图5a是根据一些实施方案的绘制图4的全带宽二次相位发生器的输出相位的图示。

15.图5b是根据一些实施方案的绘制图4的全带宽二次相位发生器的瞬时频率的图示。

16.图5c是根据一些实施方案的绘制图4的全带宽二次相位发生器的瞬时频率差值的图示。

17.图6是根据一些实施方案的例示性带限二次相位发生器的框图。

18.图7a是根据一些实施方案的绘制图6的带限二次相位发生器的输出相位的图示。

19.图7b是根据一些实施方案的绘制图6的带限二次相位发生器的瞬时频率的图示。

20.图7c是根据一些实施方案的绘制图6的带限二次相位发生器的瞬时频率差值的图示。

21.图8是根据一些实施方案的没有数控振荡器的例示性二次相位发生器的框图。

22.图9a是根据一些实施方案的绘制具有四个啁啾和101字长的二次相位发生器的瞬时频率的图示。

23.图9b是根据一些实施方案的绘制具有五个啁啾和101字长的二次相位发生器的瞬时频率的图示。

24.图9c是根据一些实施方案的绘制具有负七个啁啾和101字长的二次相位发生器的瞬时频率的图示。

25.图10a是根据一些实施方案的绘制所有啁啾计数的排序瞬时频率的图示。

26.图10b是根据一些实施方案的绘制所有啁啾计数的排序瞬时频率差值的图示。

27.图11是根据一些实施方案的用于操作二次相位发生器的例示性步骤的流程图。

28.图12是根据一些实施方案的具有配置有与二次相位发生器相同带宽的信道滤波器的无线电路的图示。

具体实施方式

29.图1的电子设备10可以是:计算设备,诸如膝上型计算机、台式计算机、包含嵌入式计算机的计算机监视器、平板电脑、蜂窝电话、媒体播放器或者其他手持式或便携式电子设备;较小的设备,诸如腕表设备、挂式设备、耳机或听筒设备、嵌入在眼镜中的设备;或者佩戴在用户头部上的其他装备;或者其他可佩戴式或微型设备、电视机、不包含嵌入式计算机的计算机显示器、游戏设备、导航设备、嵌入式系统(诸如其中具有显示器的电子装备安装在信息亭或汽车中的系统)、连接无线互联网的语音控制的扬声器、家庭娱乐设备、遥控设备、游戏控制器、外围用户输入设备、无线基站或接入点、实现这些设备中的两个或更多个设备的功能的装备;或者其他电子装备。

30.如图1中的功能框图所示,设备10可包括位于电子设备外壳诸如外壳12上或其内的部件。外壳12(有时可称为外部壳体)可由塑料、玻璃、陶瓷、纤维复合材料、金属(例如,不锈钢、铝、金属合金等)、其他合适的材料或这些材料的组合形成。在一些情况下,外壳12的部分或全部可由介电或其他低电导率材料(例如,玻璃、陶瓷、塑料、蓝宝石等)形成。在其他情况下,外壳12或构成外壳12的结构中的至少一些结构可由金属元件形成。

31.设备10可包括控制电路14。控制电路14可包括存储装置,诸如存储电路16。存储电路16可包括硬盘驱动器存储装置、非易失性存储器(例如,被配置为形成固态驱动器的闪存存储器或其他电可编程只读存储器)、易失性存储器(例如,静态随机存取存储器或动态随机存取存储器)等。存储电路16可包括集成在设备10内的存储装置和/或可移动存储介质。

32.控制电路14可包括处理电路,诸如处理电路18。处理电路18可用于控制设备10的操作。处理电路18可包括一个或多个微处理器、微控制器、数字信号处理器、主机处理器、基带处理器集成电路、专用集成电路、中央处理单元(cpu)等。控制电路14可被配置为使用硬

件(例如,专用硬件或电路)、固件和/或软件在设备10中执行操作。用于在设备10中执行操作的软件代码可以存储在存储电路16(例如,存储电路16可以包括存储软件代码的非暂态(有形)计算机可读存储介质)上。该软件代码可有时被称为程序指令、软件、数据、指令、或代码。存储在存储电路16上的软件代码可由处理电路18来执行。

33.控制电路14可用于运行设备10上的软件,诸如卫星导航应用程序、互联网浏览应用程序、互联网语音协议(voip)电话呼叫应用程序、电子邮件应用程序、媒体回放应用程序、操作系统功能等。为了支持与外部装备进行交互,控制电路14可用于实现通信协议。可使用控制电路14实现的通信协议包括:互联网协议、无线局域网(wlan)协议(例如,ieee 802.11协议——有时称为)、用于其他短距离无线通信链路的协议诸如协议或其他无线个人区域网(wpan)协议、ieee 802.11ad协议(例如,超宽带协议)、蜂窝电话协议(例如,3g协议、4g(lte)协议、5g协议等)、天线分集协议、卫星导航系统协议(例如,全球定位系统(gps)协议、全球导航卫星系统(glonass)协议等)、基于天线的空间测距协议(例如,在毫米和厘米波频率下传送的信号的无线电探测与测距(radar)协议或其他期望的距离检测协议)或任何其他期望的通信协议。每种通信协议可与对应的无线电接入技术(rat)相关联,该无线电接入技术指定用于实现该协议的物理连接方法。

34.设备10可包括输入-输出电路20。输入-输出电路20可包括输入-输出设备22。输入-输出设备22可用于允许将数据供应给设备10并且允许将数据从设备10提供给外部设备。输入-输出设备22可包括用户接口设备、数据端口设备和其他输入-输出部件。例如,输入-输出设备22可包括触摸传感器、显示器(例如,触敏显示器和/或力敏显示器)、发光部件诸如没有触摸传感器能力的显示器、按钮(机械、电容、光学等)、滚轮、触摸板、小键盘、键盘、麦克风、相机、按钮、扬声器、状态指示器、音频插孔和其他音频端口部件、数字数据端口设备、运动传感器(加速度计、陀螺仪和/或检测运动的罗盘)、电容传感器、接近传感器、磁传感器、力传感器(例如,耦接到显示器以检测施加到显示器的压力的力传感器)等。在一些配置中,键盘、耳机、显示器、指向设备诸如触控板、鼠标和操纵杆以及其他输入-输出设备可使用有线或无线连接耦接至设备10(例如,输入-输出设备22中的一些可为经由有线或无线链路耦接至设备10的主处理单元或其他部分的外围设备)。

35.输入-输出电路20可包括无线电路24以支持无线通信。无线电路24(在本文中有时称为无线通信电路24)可包括两个或更多个天线40。无线电路24还可包含基带处理器电路、收发器电路、放大器电路、滤波器电路、切换电路、射频传输线和/或用于使用天线40发射和/或接收射频信号的任何其他电路。

36.无线电路24可以在无线电频率(在本文中有时称为通信频带或简称为“带”)的对应频带内发射和/或接收射频信号。由无线电路24处理的频带可以包括无线局域网(wlan)频带(例如,(ieee 802.11)或其他wlan通信频带)诸如2.4ghz wlan频带(例如,2400mhz至2480mhz)、5ghz wlan频带(例如,5180mhz至5825mhz)、6e频带(例如,5925mhz至7125mhz)和/或其他频带(例如,1875mhz至5160mhz);无线个人区域网(wpan)频带诸如2.4ghz频带或其他wpan通信频带;蜂窝电话频带(例如,约600mhz至约5ghz的频带、3g频带、4g lte频带、低于10ghz的5g新空口频率范围1(fr1)频带、在20ghz和60ghz之间的5g新空口频率范围2(fr2)频带等);10ghz至300ghz之间的其他厘米

或毫米波频带;近场通信频带(例如,13.56mhz);卫星导航频带(例如,1565mhz至1610mhz的gps频带、全球卫星导航系统(glonass)频带、北斗卫星导航系统(bds)频带等);在ieee 802.15.4协议和/或其他超宽带通信协议下工作的超宽带(uwb)频带;在3gpp无线通信标准族下的通信频带;在ieee 802.xx标准族下的通信频带,和/或任何其他期望的感兴趣的频带。

37.可使用任何期望的天线结构来形成天线40。例如,天线40可包括具有谐振元件的天线,该天线由环形天线结构、贴片天线结构、倒f形天线结构、隙缝天线结构、平面倒f形天线结构、螺旋形天线结构、单极子天线、偶极子、这些设计的混合等形成。可调节滤波器电路、切换电路、阻抗匹配电路和/或其他天线调谐部件以调节天线40随时间的频率响应和无线性能。

38.由天线40处理的射频信号可以用于在设备10与外部无线通信设备(例如,一个或多个其他设备诸如设备10)之间传送无线通信数据。无线通信数据可以由无线电路24双向或单向传送。无线通信数据可例如包括已编码到对应数据包中的数据,诸如与电话呼叫相关联的无线数据、流媒体内容、互联网浏览、与在设备10上运行的软件应用程序相关联的无线数据、电子邮件消息等。

39.无线电路24可以附加地或另选地使用天线40执行空间测距操作。在无线电路24既传送无线通信数据又执行空间测距操作的情况下,相同天线40中的一者或多者可以用于既传送无线通信数据又执行空间测距操作。在另一具体实施中,无线电路24可以包括仅传送无线通信数据的一组天线40和仅用于执行空间测距操作的一组天线40。

40.当执行空间测距操作时,天线40可以发射射频信号36。无线电路24可在对应射频频带(例如,包括大于约10ghz、大于约20ghz、小于10ghz等的频率的频带)中发射射频信号36。射频信号36可以从设备10外部的对象(诸如外部对象34)反射离开。外部物体34可以是例如地面、建筑物、墙壁、家具、天花板、人、身体部位、动物、车辆、景观或地理特征、障碍物或设备10外部的任何其他对象或实体。天线40可以接收反射的射频信号38。反射信号38可以是发射的射频信号36的反射版本,这些反射信号从外部对象34反射离开并传输返回设备10。

41.控制电路14可处理发射的射频信号36和接收的反射信号38以检测或估计设备10与外部对象34之间的范围(距离)r。如果需要,控制电路14还可以处理发射信号和接收信号以识别外部对象34的两维或三维空间位置(方位)、外部对象34的速度和/或反射信号38的到达角。在本文中作为示例描述的一个实施方案中,无线电路24使用频率调制的连续波(fmcw)雷达方案执行空间测距操作。这仅仅是例示性的,并且通常可以使用其他雷达方案或空间测距方案(例如,ofdm雷达方案、fscw雷达方案、相位编码雷达方案等)。

42.如图1所示,无线电路24可包括发射(tx)电路26。发射电路26可包括发射信号发生器,诸如信号发生器50。发射信号发生器50可生成用于通过天线40发射的信号。在本文中作为示例描述的一些具体实施中,发射信号发生器50包括啁啾发生器,该啁啾发生器生成用于通过天线40发射的啁啾信号(例如,在其中无线电路24使用fmcw雷达方案的实施方案中)。因此,发射信号发生器50在本文中有时可称为啁啾发生器。发射电路26还可包括数模转换器(dac)电路,诸如dac 30。数模转换器30可将发射信号(例如,啁啾信号)在由天线40发射之前从数字域转换到模拟域。

43.无线电路24还可包括接收(rx)电路28。接收电路28可包括模数转换器(adc)电路,诸如adc 32。模数转换器32可将从天线40接收的射频信号从模拟域转换到数字域以用于由控制电路14后续处理。虽然为了清楚起见,在图1的示例中,控制电路14被示出为与无线电路24分开,但是无线电路24可包括处理电路和/或存储电路,该处理电路形成处理电路18的一部分,该存储电路形成控制电路14的存储电路16的一部分(例如,控制电路14的各部分可在无线电路24上实现)。例如,无线电路24包括基带处理器,该基带处理器可被认为是处理电路18的一部分。

44.使用多种不同的射频发射器架构可实现发射电路26。图2示出了实现为数字极性发射器的电路26。如图2所示,数字极性发射器电路26可包括:被配置为输出发射信号的发射信号发生器50、被配置为相对于时间微分或计算发射信号的导数的微分器52、上采样电路54和上采样电路58、振荡电路(诸如数字控制振荡器56、数据转换器(诸如数模转换器(dac)30))、滤波电路(诸如带通滤波器60)和一个或多个功率放大器62。

45.根据一些实施方案,发射信号发生器50可被配置为生成恒幅零自相关(cazac)序列。顾名思义,cazac序列具有两种识别特性。任何cazac序列的第一特性是序列具有恒幅。换句话说,当cazac序列中的数字在复平面上绘制时将全部位于一个圆上。任何cazac序列的第二特性是给定序列和该给定序列的偏移版本的相关性将约等于零。换句话说,该两个序列是正交的。生成具有恒幅的正交序列可用于雷达和许多无线应用中。为了实现高质量传输,可能优选使用发射信号发生器50生成内插cazac序列。

46.生成cazac序列的一种方式是使用可输出具有二次相位的信号的信号发生器。此类类型的cazac序列发生器有时称为二次相位发生器。图2的发射信号发生器50可以是能够输出一个或多个cazac序列的二次相位发生器。从二次相位发生器50输出的信号可经由上采样电路58反馈到数模转换器30。上采样电路58可执行上采样或上转换操作。从二次相位发生器50输出的信号还可经由微分器52和上采样电路54反馈到数字控制振荡器56。微分器52可被配置为计算具有二次相位波形的信号关于时间的导数,这产生作为时间的线性函数的瞬时频率。因此,信号发生器50有时还称为线性频率发生器或线性瞬时频率发生器。在由数字控制振荡器56接收之前,此线性瞬时频率可由上采样电路54上采样或上转换。数字控制振荡器56可具有耦接到数模转换器30的控制输入端的输出端。

47.数模转换器30可输出可使用带通滤波器60滤波的对应模拟信号。然后可在由天线40辐射之前由一个或多个功率放大器62放大滤波的信号。在发射路径中至少包括上采样电路、数模转换器、带通滤波器和功率放大器的该示例仅仅是例示性的。如果需要,发射器电路26可包括:耦接到dac 30或插入在该dac之前的附加数字部件、较少的数字部件、耦接到dac 30或插入在该dac之后的附加模拟前端部件、较少的模拟前端部件和/或附加滤波器、切换或耦接电路。由于dac具有有限带宽并且频带边缘几乎始终被干扰(例如,被相关联的抗混叠电路干扰),因此由二次相位发生器50生成的cazac序列应在几乎所有实际应用程序中完全内插。

48.图2的数字极性发射器架构仅仅是例示性的。图3示出了实现为iq发射器的电路26。如图3所示,iq发射器电路26可包括:被配置为输出具有二次相位的信号的二次相位发生器50、被配置为输出同相(i)信号和正交(q)信号的iq转换电路(诸如iq转换器70)、被配置为将同相信号转换到模拟域的第一数模转换器(dac)74-1、被配置为将正交信号转换到

模拟域的第二数模转换器(dac)74-2、用于控制该两个dac 74-1和dac 74-2的数字控制振荡器72、求和电路(诸如组合器76)、滤波电路(诸如带通滤波器78)和一个或多个功率放大器80。dac 74-1和dac 74-2可由图1中的框30共同表示。

49.在一些实施方案中,上采样电路可插置在iq转换器70与dac 74-1和dac 74-2之间。在此类情况下,附加上采样电路可被配置为在数模转换步骤之前上采样或上转换iq信号。在又一些实施方案中,滤波电路(诸如低通滤波器)可插置在dac与组合器76之间。如果需要,附加混频器可插置在dac与组合器76之间。例如,这些附加混频器可用于将模拟信号调制到基带频率与发射射频之间的中间频率范围。在此类情况下,又一组混频器可插置在带通滤波器78与功率放大器之间并且用于进一步将模拟信号从中间频率范围调制到发射射频。

50.在发射路径中至少包括iq转换器、多个dac、dco、求和电路、带通滤波器和功率放大器的图3的示例仅仅是例示性的。如果需要,iq发射器电路26可包括:耦接到dac 74或插入在该dac之前的附加数字部件、较少的数字部件、耦接到dac 74或插入在该dac之后的附加模拟前端部件、较少的模拟前端部件和/或附加滤波器、切换或射频耦接电路。通常,二次相位发生器50可结合到任何雷达、模拟前端或无线通信架构中。

51.图4是示出二次相位发生器50的一个具体实施的框图。如图4所示,二次相位发生器50可包括:开关(诸如开关98)、控制电路(诸如数控振荡器(nco)100)、加法器电路(诸如加法器102和104)和延迟电路(诸如延迟电路106和108)。

52.二次相位发生器50通常是两个输入的函数:(1)啁啾计数q和(2)字长m。该啁啾计数q表示每个序列中的啁啾总数。字长m表示每个cazac序列的为时间函数的被采样元素的数目(例如,m等于每个序列的样本数目)。通常,啁啾计数q可以是任何正整数或负整数,诸如

±

3、

±

4、

±

5、

±

6、

±

7、

±

8、

±

9、

±

(10至100)或更多。字长m的值应是整数,使得q和m的最大公约数等于1。通常,字长m至少大于10、10至100、至少100或更多、100至200、至少200或更多等。这些值仅仅是示例性的,并非旨在限制本实施方案的范围。

53.数控振荡器(nco)100可具有:被配置为接收啁啾计数q的绝对值的第一输入端、被配置为接收字长m的第二输入端和耦接到开关98的输出端。振荡器100可在其输出端上输出确定开关98的状态的积分器值。开关98可具有:被配置为接收啁啾计数q的两倍的第一开关输入端口、被配置为接收啁啾计数q的量减去符号啁啾计数q和字长m的乘积之差的两倍的第二开关输入端口,以及开关输出端口。当数控振荡器100输出小于或等于阈值的积分器值时,则开关98可将第一开关输入端口连接到开关输出端口(例如,使得加法器102接收2*q)。当数控振荡器100输出大于阈值的积分器值时,则开关98可将第二开关输入端口连接到开关输出端口(例如,使得加法器102接收2*(q

–

符号(q)*m))。预先确定的阈值可等于m(作为示例)。阈值可以是固定数字或可以是可编程的。

54.加法器102可具有耦接到开关输出端口的第一加法器输入端、第二加法器输入端和加法器输出端。延迟电路106可具有:耦接到加法器102的加法器输出端的第一输入端、被配置为接收预设信号的第二输入端,以及经由反馈路径110反馈回到加法器102的第二加法器输入端的输出端。预设信号可帮助将延迟电路106重置(初始化)为某个预先确定的(预设)值。以这种方式耦接,加法器102、延迟电路106和反馈路径110可作为第一积分器(累加器)级操作。

55.加法器104可具有耦接到延迟电路106的输出端的第一加法器输入端、第二加法器输入端和加法器输出端。延迟电路108可具有:耦接到加法器104的加法器输出端的第一输入端、被配置为接收起始信号的第二输入端,以及经由反馈路径112反馈回到加法器104的第二加法器输入端的输出端。起始信号可帮助将延迟电路106重置(初始化)为零(作为示例)。以这种方式耦接,加法器104、延迟电路108和反馈路径112可作为第二积分器(累加器)级操作。延迟电路108的输出端耦接到二次相位发生器50的最终输出端口out,在该最终输出端口上生成具有二次相位的信号。通常,可将预设信号和起始信号设置为用于初始化或重置二次相位发生器50的任何合适的值。

56.如此配置,因此图4的二次相位发生器50能够在一个符号m样本内用两个瞬时频率增量求和,如以下等式1中所示:

[0057][0058]

零的加权和确保二次相位发生器50产生最小量化误差。

[0059]

图5a是针对一个序列绘制结合图4描述的类型的二次相位发生器50的输出相位的图示,其中啁啾计数q等于3并且其中字长m等于100。输出相位按系数π归一化(即,划分)。如图5a所示,序列可被划分为三个啁啾(由于q=3),每个啁啾具有二次相位轮廓。序列的相位环绕三次,并以相同的相位值开始和结束。与输出多个完全相同啁啾的常规cazac序列发生器不同,由二次相位发生器50生成的不同的啁啾略微不同(例如,每个啁啾表现出不同的相应的量值响应)。因此将二次相位发生器定义为被配置为输出具有一个或多个啁啾的信号的电路,该一个或多个啁啾各自具有二次相位响应,如图5a的示例中所示。

[0060]

图5b是绘制对应于图5a的二次相位轮廓的瞬时频率的图示。换句话说,通过微分或计算图5a中的样本的导数来获得图5b的曲线。如图5b所示,再次将序列划分为三个啁啾(由于q=3),在环绕到-π之前每个啁啾表现出从约-π延伸到约 π的线性瞬时频率。啁啾之间没有频率异常值。

[0061]

图5c是绘制对应于图5b的线性瞬时频率轮廓的瞬时频率差值的图示。类似地,通过微分或计算图5b中的样本的导数来获得图5c的曲线。如图5c所示,瞬时频率差值可以是两个恒定值:等于q的绝对值的较高值和等于q减去m的绝对值的较低值。因此,在开关的第一输入端处的较高值与在开关的第二输入端处的第二值之间的差值与字长m成比例。当序列在啁啾之间环绕时(例如,当从第一啁啾环绕到第二啁啾以及从第二啁啾卷绕到第三啁啾时),该瞬时频率差值仅切换到较低值。这两个恒定值可对应于在开关98的输入端处的值(参见图4)。

[0062]

较高值和较低值之间的δ等于2π。因此结合图4、图5a、图5b和图5c描述的二次相位发生器50有时称为“全带宽”二次相位发生器。仅需要在两个恒定瞬时频率差值之间切换的全带宽二次相位发生器在硬件中实现起来相当简单(参见例如图4的拓扑),因此消耗少量电路面积。与常规cazac序列发生器相比,图4的二次相位发生器具体实施还消耗较少的功率并且提供增强的性能。

[0063]

与全带宽二次相位发生器相关的图4至图5的实施方案仅仅是例示性的。在其他实

施方案中,可期望限制或降低二次相位发生器50的操作带宽。图6示出了具有有限带宽同时还递送内插cazac序列的二次相位发生器50的另一具体实施。为了正确缩放带宽,可将缩放(加权)系数b应用于nco开关的两个输入端。具体地,缩放系数b可以是具有对两个开关输入值加权的分子值和缩放积分器(累加器)级中求和电路的位宽的分子值的分数。

[0064]

如图6所示,开关98可具有第一开关输入端口,该第一开关输入端口被配置为接收两倍缩放系数b乘以的啁啾计数q的量减去符号啁啾计数q和字长m的乘积,当数控振荡器100输出大于阈值的积分器值时,则开关98可将第一开关输入端口连接到开关输出端口(例如,使得加法器102接收2*b*q)。当数控振荡器100输出小于或等于阈值的积分器值时,则开关98可将第二开关输入端口连接到开关输出端口(例如,使得加法器102接收2*b*(q

–

符号(q)*m))。预先确定的阈值可等于m(作为示例)。阈值可以是固定数字或可以是可编程的。图6的二次相位发生器50的剩余结构可类似于已经相对于图4描述的结构,并且不必详细地重复以避免模糊本实施方案。

[0065]

如此配置,因此图6的二次相位发生器50能够在一个符号m样本内用两个瞬时频率增量求和,如以下等式2和等式3中所示:

[0066][0067][0068]

等式2表示当q为正时和的表达式,而等式3表示当q为负时和的表达式。在任一情况下零的加权和确保二次相位发生器50即使采用带限缩放系数b也产生最小量化误差。

[0069]

图7a是针对一个序列绘制结合图6描述的类型的二次相位发生器50的输出相位的图示,其中啁啾计数q等于3并且其中字长m等于100。输出相位按系数π归一化(即,划分)。如图7a所示,序列可被划分为三个啁啾(由于q=3),每个啁啾具有二次相位轮廓。序列的相位环绕三次,并以相同的相位值开始和结束。与输出多个完全相同啁啾的常规cazac序列发生器不同,由二次相位发生器50生成的不同的啁啾再次略微不同(例如,每个啁啾在其相位表示中略微偏移)。

[0070]

图7b是绘制对应于图7a的二次相位轮廓的瞬时频率的图示。换句话说,通过微分图7a中的样本来获得图7b的曲线。如图7b所示,再次将序列划分为三个啁啾(由于q=3),在环绕返回之前每个啁啾表现出从约-0.625π延伸到约 0.625π的线性瞬时频率。啁啾之间没有频率异常值。

[0071]

图7c是绘制对应于图7b的线性瞬时频率轮廓的瞬时频率差值的图示。类似地,通过区分图7b中的样本来获得图7c的曲线。如图7c所示,瞬时频率差值可以是两个恒定值:等于按系数b缩放的q的绝对值的较高值和等于q减去m的绝对值(同样按系数b缩放)的较低值。当序列在啁啾之间环绕时(例如,当从第一啁啾环绕到第二啁啾以及从第二啁啾环绕到第三啁啾时),该瞬时频率差值仅切换到较低值。这两个恒定值可对应于在开关98的输入端

处的值(参见图6)。

[0072]

在该特定示例中,较高值与较低值之间的δ可等于1.25π,该δ对应于缩放系数b=1.25/2。通常,缩放系数b可以是任何小于1的分数或值。作为示例,缩放系数b可等于0.5、0.6、0.7、0.8、0.6-0.7、0.5-0.8、小于0.99、小于0.9、小于0.8、小于0.7、小于0.6和小于0.5等。因此结合图6、图7a、图7b和图7c描述的二次相位发生器50有时称为“带限”或“降低带宽”二次相位发生器。仅需要在两个恒定瞬时频率差值之间切换的此类带限二次相位发生器在硬件中实现起来相当简单(参见例如图6的拓扑),因此消耗少量电路面积。图6的降低带宽二次相位发生器具体实施在没有任何近似的情况下生成全带宽cazac序列的精确带限版本。

[0073]

示出了具有数控振荡器和相关联的开关的降低带宽二次相位发生器的图6的实施方案仅仅是例示性的。图8示出了不包括开关98和数控振荡器100的降低带宽二次相位发生器50的另一实施方案。当满足以下条件时可使用此类类型的二次相位发生器50:

[0074]

|b*q-b*m|∈2mꢀꢀ

(4)

[0075]

|b*q b*m|∈2mꢀꢀ

(5)

[0076]

条件4用于啁啾计数q的正值,而条件5用于啁啾计数q的负值。如果满足条件4或条件5,则求和电路102可始终接收乘积b*q,从而不需要单独的nco积分器开关。这可帮助进一步最小化二次相位发生器50的电路面积。以这种方式操作,积分器级的环绕执行期望的减法函数。图8的二次相位发生器50的剩余结构可类似于已经相对于图4描述的结构,并且不必详细地重复以避免模糊本实施方案。

[0077]

如上所述,啁啾计数q可以是任何正整数或负整数。对字长m的值的唯一限制是q与m之间的最大公约数应等于1。图9a至图9c绘制了具有不同的q值和m值的带限二次相位发生器50的瞬时频率。图9a是绘制具有四个啁啾(例如,q=4)和101字长m的带限二次相位发生器的瞬时频率的图示。4和101的最大公约数是1。如图9a所示,将序列划分为四个啁啾,在环绕返回之前每个啁啾表现出从约-0.625π延伸到约 0.625π的略微不同的线性瞬时频率响应。啁啾之间没有频率异常值。

[0078]

图9b是绘制具有五个啁啾(例如,q=5)和101字长m的带限二次相位发生器的瞬时频率的图示。5和101的最大公约数是1。如图9b所示,将序列划分为五个啁啾,在环绕返回之前每个啁啾表现出从约-0.625π延伸到约 0.625π的略微不同的线性瞬时频率响应。啁啾之间没有频率异常值。

[0079]

具有正啁啾计数值q的图9a和图9b的示例仅仅是例示性的。图9c是绘制具有七个啁啾(例如,q=-7)和101字长m的带限二次相位发生器的瞬时频率的图示。7和101的最大公约数是1。如图9c所示,将序列划分为七个啁啾,在环绕返回之前每个啁啾表现出从约-0.625π延伸到约 0.625π的略微不同的线性瞬时频率响应。连续啁啾之间没有频率异常值。将图9c与图9a和图9b进行比较,显然正q产生增大的线性瞬时频率响应,而负q产生减小的线性瞬时频率响应(例如,图9a和图9b的线性响应表现出向上的斜率,而图9c的线性响应具有向下的斜率)。

[0080]

图10a是绘制具有101字长m的所有啁啾计数的排序瞬时频率的图示。换句话说,将所有来自图9a的瞬时频率样本点排序将产生图10a的排序曲线。类似地,将所有来自图9b的瞬时频率样本点排序将产生图10a的排序曲线。将所有来自图9c的瞬时频率样本点排序将

类似地产生图10a的排序曲线。换句话说,从带限二次相位发生器输出的排序瞬时频率样本与q的量值无关。

[0081]

图10b是再次绘制所有啁啾计数的排序瞬时频率差值的图示。如图10b所示,样本之间的频率步长大小是与q的量值无关的恒定值。

[0082]

图11是控制二次相位发生器50所涉及的例示性操作的流程图。在框200处,可将数控振荡器100初始化为某个起始积分器值。在框202处,数控振荡器100可在每个积分器循环内通过q的绝对值减去字长m再减去(q,2)的绝对值的模与1之差来递增积分器值。

[0083]

在框204处,数控振荡器100可确定积分器值是否大于字长m。响应于确定当前积分器值小于或等于m,则振荡器可指示对应开关98将第一开关输入端处的较高值输出到加法器102(参见框206的操作)。然后该值可由第一积分器级累加,在一些延迟之后该值可传播到第二积分器级。

[0084]

响应于确定当前积分器值大于m(例如,如果已检测到积分器溢出事件),则振荡器100可指示对应开关98将第二开关输入端处的较低值输出到加法器102(参见框208的操作)。然后该值可由第一积分器级累加,在一些延迟之后该值可传播到第二积分器级。然后可递减nco值(例如,递减2*m),以执行环绕。

[0085]

图11的操作仅仅是例示性的。可修改或省略所描述的操作中的至少一些操作;可并行执行所描述的操作中的一些操作;可在所描述的操作之间添加或插入附加过程;某些操作的顺序可颠倒或改变;可调整所描述的操作的时序,使得它们在略微不同的时间发生,或者所描述的操作可分布在系统中。

[0086]

图12示出了使用二次相位发生器50实现频率调制的连续波(fmcw)雷达方案的无线电路24的示例。如图12所示,无线电路24可具有发射路径和接收路径。发射路径可包括:基带(bb)发射器(诸如基带发射器150)、iq转换电路(诸如iq转换器152)、滤波电路(诸如重建滤波器154)、上采样电路(诸如上采样器156)、数据转换器(诸如数模转换器(dac)158)和发射天线40-1。基带发射器150可包括用于将内插cazac序列输出到iq转换器的二次相位发生器50(例如,图4所示类型的全带宽二次相位发生器、图6所示类型的降低带宽二次相位发生器或图8所示类型的简化二次相位发生器)。

[0087]

iq转换器152(有时称为iq调制器)可被配置为输出对应的同相(i)信号和正交(q)信号。重建滤波器154可插置在iq转换器150与上采样器156之间。具体地,重建滤波器154可具有与二次相位发生器50的带宽匹配的相同带宽,并且有时称为信道滤波器。在二次相位发生器50表现出全带宽的情况下,滤波器154应具有与发生器50的全带宽匹配的带宽。在二次相位发生器50表现出降低带宽的情况下,滤波器154应具有与发生器50的较小带宽匹配的相对较小带宽。从重建滤波器154输出的信号可经由上采样电路156反馈到数模转换器158。上采样电路156可执行上采样或上转换操作。数模转换器158可输出可被反馈到天线40-1的用于发射的对应模拟信号。

[0088]

在发射路径中至少包括iq转换器、重建滤波器、上采样电路和数模转换器的该示例仅仅是例示性的。如果需要,发射路径可包括:耦接到dac 30或插入在该dac之前的附加数字部件、较少的数字部件、耦接到dac 30或插入在该dac之后的附加模拟前端部件(例如,一个或多个带通滤波器、一个或多个功率放大器和一个或多个混频器等)、较少的模拟前端部件和/或附加滤波器、切换或耦接电路。

[0089]

接收路径可包括:天线40-2、数据转换器(诸如模数转换器160)、偏移校正电路(诸如偏移校正电路162)、下采样电路(诸如下采样器164)、滤波电路(诸如重建滤波器166)、iq转换电路(诸如iq转换器168)和基带接收器170。在无线电路24通过使用第一天线40-1发射射频信号以及使用第二不同天线40-2接收对应反射射频信号来执行空间测距操作的该示例仅仅是例示性的。在其他实施方案中,发射路径和接收路径可耦接到相同天线40中的一个或多个天线。

[0090]

继续图12的示例,由天线40-2接收的射频信号可被反馈到模数转换器(adc)160用于转换。adc 160可将模拟射频信号转换为它们的数字等效物。偏移校正电路162可插置在adc 1600与下采样器164之间。偏移校正电路162可提供精细延迟调整,以帮助减轻在下采样操作之前可能发生的任何潜在偏移或拖尾。下采样器164可执行下采样或下转换操作。

[0091]

重建滤波器166可插置在下采样器164与iq转换器168之间。具体地,重建滤波器166可具有与二次相位发生器50匹配的相同带宽,并且有时还称为信道滤波器。在二次相位发生器50表现出全带宽的情况下,滤波器166应具有与发生器50的全带宽匹配的带宽。在二次相位发生器50表现出降低带宽或有限带宽的情况下,滤波器154应具有与发生器50的有限带宽匹配的相对较小带宽。从重建滤波器166输出的信号可被反馈到iq转换器168。iq转换器168(有时称为iq解调器)将同相(i)和正交(q)信号转换为可由基带接收器170接收和处理的基带信号。

[0092]

在接收路径中至少包括iq转换器、重建滤波器、下采样电路、偏移校正电路(例如,延迟调整电路)和模数转换器的该示例仅仅是例示性的。如果需要,接收路径可包括:耦接到adc 160或插入在该adc之前的附加模拟前端部件(例如,附加滤波器、切换或耦接电路)、较少的模拟前端部件、耦接到adc 160或插入在该adc之后的附加数字部件和/或较少的数字部件。

[0093]

延迟电路172可耦接在基带发射器150和基带接收器170之间。延迟电路172可被配置为提供固定或可调延迟量以帮助补偿发射路径和接收路径之间的任何内部延迟。因此,延迟电路172有时可称为内部延迟补偿电路。基带发射器150和基带接收器170有时统称为基带处理器,该基带处理器可看作是无线电路24和处理电路18的一部分(参见例如图1)。

[0094]

上文结合图1-图12所述的方法和操作可以由设备10的部件使用软件、固件和/或硬件(例如,专用电路或硬件)来执行。用于执行这些操作的软件代码可存储在非暂态计算机可读存储介质(例如,有形计算机可读存储介质)上,该非暂态计算机可读存储介质存储在设备10的部件中的一个或多个部件上(例如,图1的存储电路16)。该软件代码有时可被称为软件、数据、指令、程序指令或代码。非暂态计算机可读存储介质可包括驱动器、非易失性存储器诸如非易失性随机存取存储器(nvram)、可移动闪存驱动器或其他可移动介质、其他类型的随机存取存储器等。存储在非暂态计算机可读存储介质上的软件可由设备10的部件中的一个或多个部件上的处理电路(例如,图1的处理电路18等)来执行。处理电路可包括微处理器、中央处理单元(cpu)、具有处理电路的专用集成电路或其他处理电路。图2、图3、图4、图6、图8和图12的部件可使用硬件(例如,电路部件、数字逻辑门等)和/或使用适用的软件实现。

[0095]

根据实施方案提供了一种无线电路,该无线电路包括:至少一个数模转换器,该至少一个数模转换器具有耦接到天线的输入端和输出端;和二次相位发生器,该二次相位发

生器具有:耦接到该至少一个数模转换器的该输入端的输出端口,具有输入端和输出端的第一积分器级,具有耦接到该第一积分器级的该输出端的输入端并且具有连接到该输出端口的输出端的第二积分器级,和具有第一输入端、第二输入端和耦接到该第一积分器级的该输入端的输出端的开关。

[0096]

根据另一实施方案,第一积分器级包括:具有第二输入端、输出端和耦接到开关的输出端的第一输入端的第一加法器,以及具有耦接到该第一加法器的该输出端的输入端和经由第一反馈路径耦接到该第一加法器的该第二输入端的输出端的第一延迟电路。

[0097]

根据另一实施方案,第二积分器级包括:具有耦接到第一延迟电路的输出端的第一输入端、第二输入端和输出端的第二加法器,以及具有耦接到该第二加法器的该输出端的输入端和经由第二反馈路径耦接到该第二加法器的该第二输入端的输出端的第二延迟电路。

[0098]

根据另一实施方案,将第一延迟电路重置为预设值,并且将第二延迟电路重置为与该预设值不同的起始值。

[0099]

根据另一实施方案,开关的第一输入端被配置为接收第一值,该第一值是在输出端口处定义啁啾数目的啁啾计数q的函数;并且该开关的第二输入端被配置为接收与该第一值不同的第二值。

[0100]

根据另一实施方案,二次相位发生器被配置为在输出端口处输出内插恒幅零自相关(cazac)序列;开关的第一输入端被配置为接收第一值,该第一值是定义内插cazac序列中啁啾数目的啁啾计数q的函数;并且开关的第二输入端被配置为接收第二值,该第二值是啁啾计数q和定义内插cazac序列中样本数目的字长m的函数。

[0101]

根据另一实施方案,二次相位发生器还包括用于控制开关的数控振荡器,该开关被配置为当由该数控振荡器输出的值小于或等于阈值时将该开关的第一输入端连接到该开关的输出端,并且当由该数控振荡器输出的该值大于阈值时将该开关的第二输入端连接到该开关的输出端。

[0102]

根据另一实施方案,二次相位发生器被配置为在输出端口处输出内插恒幅零自相关(cazac)序列;开关的第一输入端被配置为接收第一值,该第一值是以下各项的函数:(1)定义内插cazac序列中啁啾数目的啁啾计数q和(2)用于限制二次相位发生器的带宽的缩放系数b;并且该开关的第二输入端被配置为接收第二值,该第二值是以下各项的函数:(1)啁啾计数q、(2)缩放系数b和(3)定义内插cazac序列中样本数目的字长m。

[0103]

根据另一实施方案,二次相位发生器被配置为在输出端口处输出内插恒幅零自相关(cazac)序列;开关的第一输入端被配置为接收第一值,该第一值是定义内插cazac序列中啁啾数目的啁啾计数q的函数;该开关的第二输入端被配置为接收:第二值,该第二值是啁啾计数q、定义内插cazac序列中样本数目的字长m的函数,并且在该开关的第一输入端处的第一值与在该开关的第二输入端处的第二值之间的差值与该字长m成比例。

[0104]

根据另一实施方案,二次相位发生器被配置为在输出端口处输出内插恒幅零自相关(cazac)序列,并且该二次相位发生器包括耦接到开关的数控振荡器,该数控振荡器具有被配置为接收定义内插cazac序列中啁啾数目的啁啾计数q以及接收定义内插cazac序列中样本数目的字长m的第一输入端,该啁啾计数q是正整数或负整数,并且该啁啾计数q和该字长m具有等于1的最大公约数。

[0105]

根据另一实施方案,二次相位发生器被配置为在输出端口处生成具有多个啁啾的序列,并且该序列中每个啁啾具有与该序列中其他啁啾不同的二次相位响应。

[0106]

根据实施方案,提供了一种用于操作无线电路的方法,该方法包括:在数模转换器处接收数字信号并将该数字信号转换为用于经由天线发射的模拟信号;以及从二次相位发生器输出内插恒幅零自相关(cazac)序列,在该数模转换器处接收的数字信号基于从该二次相位发生器输出的该内插cazac序列生成,并且从该二次相位发生器输出该内插cazac序列包括:控制开关以将第一值和第二值选择性地输出到第一积分器级,在第二积分器级处接收来自该第一积分器级的信号,以及从该第二积分器级输出该内插cazac序列。

[0107]

根据另一实施方案,从二次相位发生器输出内插cazac序列包括:在第一积分器级中的第一加法器处接收第一值和第二值、延迟从第一加法器输出的信号以及将该延迟信号反馈回到第一加法器。

[0108]

根据另一实施方案,从二次相位发生器输出内插cazac序列包括:在第二积分器级中的第二加法器处接收延迟信号、延迟从第二加法器输出的信号以及将从第二加法器输出的延迟信号反馈回到第二加法器。

[0109]

根据另一实施方案,从二次相位发生器输出内插cazac序列包括:基于从数控振荡器输出的值控制开关,周期性地递增从该数控振荡器输出的该值,以及确定从该数控振荡器输出的该值是否超过阈值。

[0110]

根据另一实施方案,从二次相位发生器输出内插cazac序列包括:响应于确定从数控振荡器输出的值不超过阈值,控制开关将第一值输出到第一积分器级;以及响应于确定从该数控振荡器输出的值超过阈值,控制开关将第二值输出到第一积分器级,第二值小于第一值。

[0111]

根据另一实施方案,第一值与定义内插cazac序列中啁啾数目的啁啾计数q成比例,并且第二值与啁啾计数q和定义内插cazac序列中元素总数的字长m之间的差值成比例。

[0112]

根据另一实施方案,该方法包括通过将第一值和第二值乘以小于1的缩放系数来降低二次相位发生器的带宽。

[0113]

根据实施方案,提供了一种电子设备,该电子设备包括:具有被配置为输出恒幅零自相关(cazac)序列的二次相位发生器的发射器;具有被配置为接收基于该cazac序列生成的信号的输入端和耦接到第一天线的输出端的数模转换器;插置在该发射器与该数模转换器的该输入端之间的第一信道滤波器,该第一信道滤波器具有与该二次相位发生器相同的带宽;具有耦接到第二天线的输入端并且具有在其上生成数字信号的输出端的模数转换器;具有被配置为接收基于从该模数转换器输出的该数字信号生成的信号的输入端的接收器;和插置在该模数转换器的该输出端与该接收器的该输入端之间的第二信道滤波器,该第二信道滤波器具有与该二次相位发生器相同的带宽。

[0114]

根据另一实施方案,电子设备包括:插置在模数转换器的输出端与第二信道滤波器之间的偏移校正电路和耦接在发射器与接收器之间的延迟补偿电路。

[0115]

前述内容仅为示例性的并且可对所述实施方案作出各种修改。前述实施方案可独立实施或可以任意组合实施。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。