能够补偿电流泄漏的半导体集成电路器件及操作其的方法

1.相关申请的交叉引用

2.本技术要求于2021年9月7日在韩国知识产权局提交的申请号为10-2021-0118894的韩国申请的优先权,该申请通过引用被整体合并于此。

技术领域

3.各个实施例可以总体上涉及半导体集成电路器件,具体地涉及电压发生器,更具体地,涉及使用电压发生器的半导体器件。

背景技术:

4.电子设备可以包括多个电子部件。计算机系统可以包括多个半导体器件。计算机系统中的半导体器件可以包括恒流源,该恒流源被配置为接收各种电源电压以及从电源电压生成各种电流。

5.恒流源可以接收具有电压电平的偏置电压以生成恒定电流。为了生成恒定电流,可能需要维持偏置电压的电压电平。

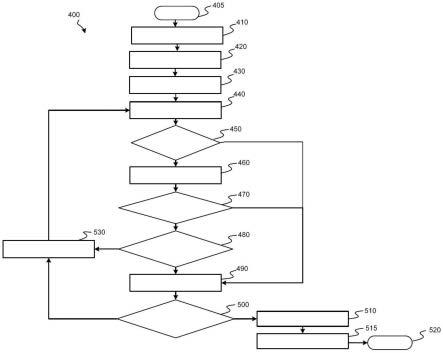

技术实现要素:

6.在本公开的示例实施例中,半导体集成电路器件可以包括电流泄漏检测器、泄漏补偿脉冲发生器和泄漏补偿电压发生器。电流泄漏检测器可以被配置为将内部电压信号与具有不同电平的多个参考电压信号相比较以生成电流泄漏状态信号。泄漏补偿脉冲发生器可以被配置为基于电流泄漏状态信号和温度状态信号来生成偏置电平补偿信号。泄漏补偿电压发生器可以被配置为基于来自泄漏补偿脉冲发生器的偏置电平补偿信号生成内部电压信号。

7.在本公开的示例实施例中,半导体集成电路器件可以包括泄漏补偿电压发生器、电流泄漏检测器和泄漏补偿脉冲发生器。泄漏补偿电压发生器可以被配置为在激活模式中生成内部电压信号。泄漏补偿电压发生器可以被配置为在掉电(备用)模式中基于偏置电平补偿信号的时钟脉冲来生成内部电压信号。电流泄漏检测器可以被配置为接收参考电压信号和内部电压信号。电流泄漏检测器可以被配置为将内部电压信号与参考电压信号相比较以生成电流泄漏状态信号。泄漏补偿脉冲发生器可以被配置为接收电流泄漏状态信号和温度状态信号。泄漏补偿脉冲发生器可以被配置为控制偏置电平补偿信号的时钟脉冲的宽度和周期。

8.在本公开的示例实施例中,根据补偿半导体集成电路器件的电流泄漏的方法,可以将内部电压信号和参考电压信号彼此相比较以生成电流泄漏状态信号。可以基于电流泄漏状态信号和温度状态信号来控制偏置电平补偿信号的时钟脉冲的宽度和周期。可以基于偏置电平补偿信号而生成内部电压。

附图说明

9.根据结合附图所进行的以下详细描述,将更清楚地理解本公开的主题的以上和其他方面、特征以及优势,在附图中:

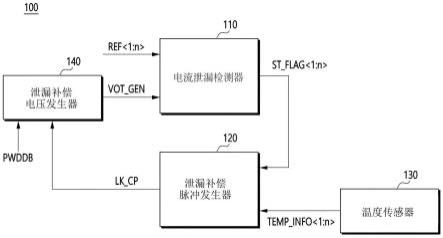

10.图1是示出根据示例实施例的半导体集成电路器件的视图;

11.图2是示出根据示例实施例的电流泄漏检测器的视图;

12.图3是示出图2中的比较器的电路图;

13.图4是示出内部电压和参考电压的分布以及根据参考电压电平的电流泄漏状态信号的时序的视图;

14.图5是示出根据示例实施例的泄漏补偿脉冲发生器的视图;

15.图6是示出根据示例实施例的时钟脉冲选择器的视图;以及

16.图7是示出根据示例实施例的泄漏补偿电压发生器的视图。

具体实施方式

17.将参照附图更详细地描述本发明的各种实施例。附图是各个实施例(和中间结构)的示意图示。因此,可以预期由例如制造技术和/或公差所导致的图示配置和形状的变化。因而,所描述的实施例不应当被理解为限于在本文图示的特定配置和形状,而是可以包括不背离如所附权利要求所限定的本发明的精神和范围的配置和形状的偏差。

18.在本文中参照本发明的理想实施例的剖面图和/或平面图来描述本发明。然而,本发明的实施例不应解释为限制本发明构思。尽管示出和描述了本发明的少许实施例,但本领域技术人员将理解,可以在不背离本发明的原理和精神的情况下在这些实施例中作出改变。

19.图1是示出根据示例实施例的半导体集成电路器件的视图。

20.参考图1,示例实施例的半导体集成电路器件100可以接收参考电压信号ref《1:n》和内部电压信号vot_gen。半导体集成电路器件100可以将参考电压信号ref《1:n》与内部电压信号vot_gen相比较以生成电流泄漏状态信号st_flag《1:n》。

21.为了确定所接收的数据信号是处于高逻辑电平还是低逻辑电平,可能需要提供具有参考电压的参考电压信号ref《1:n》。参考电压可以对应于与高逻辑电平相对应的电压和与低逻辑电平相对应的电压之间的中间值。中间值可以用作用于确定输入信号是处于高逻辑电平还是低逻辑电平的绝对电压。

22.根据示例实施例,可以从泄漏补偿电压发生器140生成内部电压信号vot_gen。泄漏补偿电压发生器140可以接收供电电源电压和接地电源电压以生成具有各种电压电平的内部电压信号vot_gen。可以根据目标电压电平来设计泄漏补偿电压发生器140的配置。泄漏补偿电压发生器140可以通过泵浦操作生成内部电压信号vot_gen。泄漏补偿电压发生器140可以包括泵浦电路(未示出),该泵浦电路生成高于供电电源电压并且低于接地电源电压的内部电压。

23.当半导体集成电路器件100进入掉电(备用)模式时,泄漏补偿电压发生器140可能经历电流泄漏。电流泄漏可能在掉电模式之后的激活模式中引起集成电路器件的异常操作。

24.可以通过检测在掉电模式中产生的电流泄漏来生成电流泄漏状态信号st_flag《

1:n》。

25.电流泄漏检测器110可以将参考电压信号ref《1:n》与内部电压信号vot_gen相比较。当参考电压信号ref《1:n》低于内部电压信号vot_gen时,电流泄漏检测器110可以生成具有高逻辑电平的电流泄漏状态信号st_flag《1:n》。

26.相比之下,当参考电压信号ref《1:n》高于内部电压信号vot_gen时,电流泄漏检测器110可以生成具有低逻辑电平的电流泄漏状态信号st_flag《1:n》。

27.当电流泄漏状态信号st_flag《1:n》处于高逻辑电平时,泄漏补偿脉冲发生器120可以控制时钟脉冲的宽度。

28.在掉电模式中,可以通过刷新操作在半导体集成电路器件中从温度传感器130周期性地向泄漏补偿脉冲发生器120传送温度状态信号temp_info《1:n》,以向泄漏补偿脉冲发生器120提供温度信息。泄漏补偿脉冲发生器120可以基于温度状态信号temp_info《1:n》来生成偏置电平补偿信号lk_cp,以控制时钟脉冲的周期。

29.半导体集成电路器件100可以包括电流泄漏检测器110、泄漏补偿脉冲发生器120、温度传感器130和泄漏补偿电压发生器140。

30.电流泄漏检测器110可以接收参考电压信号ref《1:n》和内部电压信号vot_gen。电流泄漏检测器110可以将参考电压信号ref《1:n》与内部电压信号vot_gen相比较以生成电流泄漏状态信号st_flag《1:n》。当内部电压信号vot_gen的电平低于参考电压信号ref《1:n》的电平时,电流泄漏检测器110可以输出具有高逻辑电平的电流泄漏状态信号st_flag《1:n》。相比之下,当内部电压信号vot_gen的电平高于参考电压信号ref《1:n》的电平时,电流泄漏检测器110可以输出具有低逻辑电平的电流泄漏状态信号st_flag《1:n》。

31.泄漏补偿脉冲发生器120可以接收电流泄漏状态信号st_flag《1:n》和温度状态信号temp_info《1:n》以输出偏置电平补偿信号lk_cp。

32.泄漏补偿脉冲发生器120可以接收电流泄漏状态信号st_flag《1:n》。泄漏补偿脉冲发生器120可以基于电流泄漏状态信号st_flag《1:n》来控制偏置电平补偿信号lk_cp的时钟脉冲的宽度。

33.泄漏补偿脉冲发生器120可以接收温度状态信号temp_info《1:n》。泄漏补偿脉冲发生器120可以基于温度状态信号temp_info《1:n》来控制偏置电平补偿信号lk_cp的时钟脉冲的周期。

34.温度传感器130的温度状态信号temp_info《1:n》可以对应于半导体集成电路器件100的温度。例如,温度状态信号temp_info《1:n》可以包括半导体集成电路器件100的第一温度、第二温度和第三温度中的任一个。第一温度可以低于第二温度。第三温度可以高于第二温度。第一温度可以是低温。第二温度可以是室温。第三温度可以是高温。当半导体集成电路器件100具有第一温度时,可以产生最小量的电流泄漏。相比之下,当半导体集成电路器件100具有第三温度时,可以产生最大量的电流泄漏。

35.温度传感器130可以在掉电模式中通过刷新操作来周期性地向泄漏补偿脉冲发生器120传送温度状态信号temp_info《1:n》。温度传感器130可以包括通用温度传感器,该通用温度传感器被配置为输出对应于检测到的温度水平的、具有高逻辑电平的温度选择信号。

36.温度传感器130可以包括在由jedec(电子器件工程联合会)规定的ddr3中使用的

片上热传感器(odts;on die thermal sensor)。在美国公开专利no.2021/0156746中可能公开了温度传感器130的示例。该美国公开专利no.2021/0156746可以通过引用整体被合并于此。

37.泄漏补偿电压发生器140可以在激活模式中周期性地生成处于恒定电平的内部电压。在示例实施例中,泄漏补偿电压发生器140可以在掉电模式中维持在浮置状态中,在浮置状态中,泄漏补偿电压发生器140可以不被施加电力。例如,当在掉电模式中生成内部电压信号vot_gen时,可以确定泄漏补偿电压发生器140中存在电流泄漏源。泄漏补偿电压发生器140可以接收偏置电平补偿信号lk_cp。泄漏补偿电压发生器140然后可以基于偏置电平补偿信号lk_cp来生成经补偿的内部电压信号vot_gen。

38.图2是示出根据示例实施例的电流泄漏检测器的视图。

39.参考图2,电流泄漏检测器110可以包括多个比较器,多个比较器被配置为将参考电压信号ref《1:n》与内部电压信号vot_gen相比较。

40.图2可以描绘三个参考电压信号ref1~ref3,但不限于此。例如,当内部电压信号vot_gen低于参考电压信号ref《1:n》时,电流泄漏检测器110可以输出具有高逻辑电平的电流泄漏状态信号st_flag《1:3》。相比之下,当内部电压信号vot_gen高于参考电压信号ref《1:n》时,电流泄漏检测器110可以输出具有低逻辑电平的电流泄漏状态信号st_flag《1:3》。

41.电流泄漏检测器110可以包括第一至第三比较器111、113和115。

42.第一比较器111可以接收第一参考电压信号ref1和内部电压信号vot_gen。

43.第二比较器113可以接收第二参考电压信号ref2和内部电压信号vot_gen。

44.第三比较器115可以接收第三参考电压信号ref3和内部电压信号vot_gen。

45.第一至第三参考电压信号ref1、ref2和ref3可以具有不同的电压电平。例如,第一参考电压信号ref1的电压电平可以高于第二参考电压信号ref2的电压电平。第二参考电压信号ref2的电压电平可以高于第三参考电压信号ref3的电压电平。

46.可以在泄漏补偿电压发生器140中生成内部电压信号vot_gen。例如,可以以模拟信号形式生成内部电压信号vot_gen。内部电压信号vot_gen可以被同时地输入到第一至第三比较器111、113和115中。在示例实施例中,第一至第三比较器111、113和115可以具有基本上相同的配置。因此,在本文可以参考图3仅对第一比较器111详细说明。

47.第一比较器111可以包括第一p沟道mos晶体管p1、第二p沟道mos晶体管p2、第一n沟道mos晶体管n1以及第二n沟道mos晶体管n2。

48.第一p沟道mos晶体管p1的源极可以连接到电源电压vdd。第一p沟道mos晶体管p1的栅极可以连接到第二p沟道mos晶体管p2的栅极。第一p沟道mos晶体管p1的漏极可以连接到第一n沟道mos晶体管n1的漏极。

49.第二p沟道mos晶体管p2的源极可以连接到电源电压vdd。第二p沟道mos晶体管p2的栅极可以连接到第一p沟道mos晶体管p1的栅极。第二p沟道mos晶体管p2的漏极可以连接到第二n沟道mos晶体管n2的漏极。

50.第一n沟道mos晶体管n1的栅极可以接收第一参考电压信号ref1。第一n沟道mos晶体管n1的漏极可以连接到第一p沟道mos晶体管p1的漏极。第一n沟道mos晶体管n1的源极可以连接到接地电压。

51.第二n沟道mos晶体管n2的栅极可以接收内部电压信号vot_gen。第二n沟道mos晶

体管n2的漏极可以连接到第二p沟道mos晶体管p2的漏极。第二n沟道mos晶体管n2的源极可以连接到接地电压。

52.第一比较器111可以将输入到第一n沟道mos晶体管n1中的第一参考电压信号ref1与输入到第二n沟道mos晶体管n2中的内部电压信号vot_gen相比较。

53.当内部电压信号vot_gen的电压电平高于第一参考电压信号ref1的电压电平时,第一p沟道mos晶体管p1的漏极电压可以低于第二p沟道mos晶体管p2的漏极电压以输出具有低逻辑电平的第一电流泄漏状态信号st_flag《1》。相比之下,当内部电压信号vot_gen的电压电平低于第一参考电压信号ref1的电压电平时,第一p沟道mos晶体管p1的漏极电压可以高于第二p沟道mos晶体管p2的漏极电压以输出具有高逻辑电平的第一电流泄漏状态信号st_flag《1》。

54.示例实施例的比较器111、113和115可以使用电流镜类型比较电路,该电流镜类型比较电路被配置为检测表示电流泄漏值的内部电压信号vot_gen的改变,但不限于此。

55.图4是示出内部电压和参考电压的分布以及根据参考电压电平的电流泄漏状态信号的时序的视图。

56.参考图4,当在t1中内部电压信号vot_gen的电压电平高于第一至第三参考电压信号ref1、ref2和ref3的电压电平时,第一至第三比较器111、113和115可以输出具有低逻辑电平的电流泄漏状态信号st_flag《1:3》。

57.当在t2中内部电压信号vot_gen的电压电平低于第一参考电压信号ref1的电压电平并且高于第二参考电压信号ref2和第三参考电压信号ref3的电压电平时,第一比较器111可以输出具有高逻辑电平的第一电流泄漏状态信号st_flag《1》,并且第二比较器113和第三比较器115可以输出具有低逻辑电平的第二电流泄漏状态信号和第三电流泄漏状态信号st_flag《2:3》。

58.当在t3中内部电压信号vot_gen的电压电平低于第一参考电压信号ref1和第二参考电压信号ref2的电压电平并且高于第三参考电压信号ref3的电压电平时,第一比较器111和第二比较器113可以输出具有高逻辑电平的第一电流泄漏状态信号和第二电流泄漏状态信号st_flag《1:2》,并且第三比较器115可以输出具有低逻辑电平的第三电流泄漏状态信号st_flag《3》。

59.当在t4中内部电压信号vot_gen的电压电平低于第一至第三参考电压信号ref1、ref2和ref3的电压电平时,第一至第三比较器111、113和115可以输出具有高逻辑电平的电流泄漏状态信号st_flag《1:3》。

60.当在t5中内部电压信号vot_gen的电压电平低于第一参考电压信号ref1和第二参考电压信号ref2的电压电平并且高于第三参考电压信号ref3的电压电平时,第一比较器111和第二比较器113可以输出具有高逻辑电平的第一电流泄漏状态信号和第二电流泄漏状态信号st_flag《1:2》,并且第三比较器115可以输出具有低逻辑电平的第三电流泄漏状态信号st_flag《3》。

61.当在t6中内部电压信号vot_gen的电压电平低于第一参考电压信号ref1的电压电平并且高于第二参考电压信号ref2和第三参考电压信号ref3的电压电平时,第一比较器111可以输出具有高逻辑电平的第一电流泄漏状态信号st_flag《1》,并且第二比较器113和第三比较器115可以输出具有低逻辑电平的第二电流泄漏状态信号和第三电流泄漏状态信

号st_flag《2:3》。

62.当在t7中内部电压信号vot_gen的电压电平高于第一至第三参考电压信号ref1、ref2和ref3的电压电平时,第一至第三比较器111、113和115可以输出具有低逻辑电平的电流泄漏状态信号st_flag《1:3》。

63.图5是示出根据示例实施例的泄漏补偿脉冲发生器的视图。图5可以描绘所述三个参考电压信号ref1~ref3,但不限于此。

64.参考图5,泄漏补偿脉冲发生器120可以接收电流泄漏状态信号st_flag《1:3》和温度状态信号temp_info《1:n》以输出偏置电平补偿信号lk_cp。

65.泄漏补偿脉冲发生器120可以包括时钟脉冲发生器121、计数器122和时钟脉冲选择器123。

66.时钟脉冲发生器121可以被配置为生成时钟脉冲。从时钟脉冲发生器121生成的时钟可以用作用于控制其他半导体集成电路的操作的同步信号,诸如用于将电压增大为目标电压的电压泵浦电路的输入信号等。

67.时钟脉冲发生器121可以接收电流泄漏状态信号st_flag《1:3》以改变时钟脉冲的宽度并输出时钟脉冲信号oscw。

68.在示例实施例中,时钟脉冲发生器121可以包括环形振荡器。

69.环形振荡器可以包括彼此串联连接的多个反相器121-1~121-3和多个电容器阵列121-4。环形振荡器可以根据电容器阵列121-4的充电量来控制时钟脉冲的宽度。

70.时钟脉冲发生器121可以根据电流泄漏状态信号st_flag《1:3》与增加的被使能的电容器阵列121-4的数量成比例地增加时钟脉冲的宽度。例如,当第一至第三电流泄漏状态信号st_flag《1:3》被禁止为低逻辑电平时,时钟脉冲信号oscw的脉冲宽度可以是1。当第一电流泄漏状态信号st_flag《1》被使能为高逻辑电平时,时钟脉冲信号oscw的脉冲宽度可以变为两倍宽(2x)。当第二电流泄漏状态信号st_flag《2》被使能为高逻辑电平时,时钟脉冲信号oscw的脉冲宽度可以变为四倍宽(4x)。当第三电流泄漏状态信号st_flag《3》被使能为高逻辑电平时,时钟脉冲信号oscw的脉冲宽度可以变为八倍宽(8x)。

71.计数器122可以包括分频器。图5可以描绘三个计数器。然而,本发明不限于此,并且可以结合附加的计数器。

72.计数器122可以接收时钟脉冲发生器121的时钟脉冲信号oscw。计数器122然后可以将时钟脉冲信号oscw分频以输出第一至第三时钟脉冲信号oscw1、oscw2和oscw3。从计数器输出的时钟脉冲信号oscw1、oscw2和oscw3可以被输入到时钟脉冲选择器123中。

73.时序图a、b和c可以示出从计数器输出的时钟脉冲信号oscw的周期。

74.时序图a可以示出时钟脉冲信号oscw的增加为两倍的脉冲周期。时序图b可以示出时钟脉冲信号oscw的增加为四倍的脉冲周期。时序图c可以示出时钟脉冲信号oscw的增加为八倍的脉冲周期。

75.时钟脉冲选择器123可以接收时钟脉冲信号oscw1、oscw2和oscw3。时钟脉冲选择器123可以对时钟脉冲信号oscw1、oscw2和oscw3执行与运算。时钟脉冲选择器123可以根据温度状态信号temp_info《1:n》选择时钟脉冲信号以输出偏置电平补偿信号lk_cp。

76.时序图中的情况1至3可以示出通过对时钟脉冲信号oscw1、oscw2和oscw3的与运算所控制的时钟脉冲的周期。

77.情况1可以示出当对第一至第三时钟脉冲信号oscw1、oscw2和oscw3执行与运算时的时钟脉冲的周期。

78.情况2可以示出当对第一时钟脉冲信号oscw1和第二时钟脉冲信号oscw2执行与运算时的时钟脉冲的周期。

79.情况3可以示出与第一时钟脉冲信号oscw1同步的时钟脉冲的周期。

80.时钟脉冲选择器123可以对具有受控时钟周期的时钟脉冲信号oscw1、oscw2和oscw3执行与运算。时钟脉冲选择器123可以基于温度状态信号temp_info《1:n》来输出时钟脉冲信号oscw1、oscw2和oscw3中的任一个作为偏置电平补偿信号lk_cp。

81.当半导体集成电路器件100的温度升高时,时钟脉冲选择器123可以选择情况1~情况3的时钟信号。例如,温度状态信号temp_info《1:n》可以包括第一至第三温度状态信号temp_info《1》、temp_info《2》和temp_info《3》。第一温度状态信号temp_info《1》可以指示最低温度。第三温度状态信号temp_info《3》可以指示最高温度。

82.时钟脉冲选择器123可以基于温度状态信号temp_info《1:3》仅选择情况1至3之一。当时钟脉冲选择器123接收第一温度状态信号temp_info《1》时,时钟脉冲选择器123可以仅选择情况1中的时钟信号。当时钟脉冲选择器123接收第二温度状态信号temp_info《2》时,时钟脉冲选择器123可以仅选择情况2中的时钟信号。当时钟脉冲选择器123接收第三温度状态信号temp_info《3》时,时钟脉冲选择器123可以仅选择情况3中的时钟信号。因此,尽管情况1至3中的时钟信号可以被应用于多路复用器123-3(见图6),但可以响应于温度状态信号temp_info《1:3》而仅输出时钟信号之一作为偏置电平补偿信号lk_cp。因此,泄漏补偿电压发生器140可以基于偏置电平补偿信号lk_cp来稳定地生成半导体集成电路器件100的内部电压。

83.图6是示出根据示例实施例的时钟脉冲选择器的视图。

84.参考图6,时钟脉冲选择器123可以接收计数器122的时钟脉冲信号oscw1、oscw2和oscw3以及温度状态信号temp_info《1:3》。时钟脉冲选择器123可以对时钟脉冲信号oscw1、oscw2和oscw3执行与运算。时钟脉冲选择器123可以基于温度状态信号temp_info《1:3》来输出时钟脉冲信号oscw1、oscw2和oscw3中的任一个作为偏置电平补偿信号lk_cp。

85.时钟脉冲选择器123可以包括第一与门123-1和第二与门123-2以及多路复用器123-3。第一与门123-1和第二与门123-2可以被配置为控制时钟脉冲的周期。多路复用器123-3可以被配置为基于温度状态信号temp_info《1:3》选择时钟信号中的任一个。

86.第一与门123-1可以对第一时钟脉冲信号oscw1和第二时钟脉冲信号oscw2执行与运算以生成情况2的时钟信号。

87.第二与门123-2可以对第一至第三时钟脉冲信号oscw1、oscw2和oscw3执行与运算以生成情况1的时钟信号。

88.当温度状态信号temp_info《1:3》基于低温(例如,温度状态信号temp_info《1》处于高逻辑电平)时,多路复用器123-3可以输出情况1的时钟信号作为偏置电平补偿信号lk_cp。当温度状态信号temp_info《1:3》基于室温(例如,温度状态信号temp_info《2》处于高逻辑电平)时,多路复用器123-3可以输出情况2的时钟信号作为偏置电平补偿信号lk_cp。当温度状态信号temp_info《1:3》基于高温(例如,温度状态信号temp_info《3》处于高逻辑电平)时,多路复用器123-3可以输出情况3的时钟信号作为偏置电平补偿信号lk_cp。

89.图7是示出根据示例实施例的泄漏补偿电压发生器的视图。

90.参考图7,泄漏补偿电压发生器140可以在激活模式中周期性地生成处于恒定电平的内部电压信号vot_gen。相比之下,泄漏补偿电压发生器140可以在掉电模式中被维持在浮置(备用)状态中。

91.泄漏补偿电压发生器140可以包括电压发生器140-1以及或门140-2。

92.电压发生器140-1可以包括通用电压发生器。电压发生器140-1可以在激活模式中周期性地生成处于恒定电平的内部电压信号vot_gen。电压发生器140-1可以在掉电模式中生成其中电流泄漏可以被补偿的内部电压信号vot_gen。

93.或门140-2可以对作为第一输入的掉电信号的互补信号pwddb以及作为第二输入的偏置电平补偿信号lk_cp执行或运算。当掉电信号的互补信号pwddb或偏置电平补偿信号lk_cp处于高逻辑电平时,泄漏补偿电压发生器140可以被使能,以在电压发生器140-1的掉电模式中生成其中电流泄漏被补偿的内部电压信号vot_gen。

94.在下文中,可以参考图2至图7详细地说明半导体集成电路器件100的操作。

95.泄漏补偿电压发生器140可以在激活模式中周期性地生成处于恒定电平的内部电压信号vot_gen。泄漏补偿电压发生器140可以在掉电模式中维持在浮置状态中。当偏置电平补偿信号lk_cp被输入时,泄漏补偿电压发生器140可以基于偏置电平补偿信号lk_cp来生成内部电压信号vot_gen。

96.图2和图3中的电流泄漏检测器110可以接收参考电压信号ref《1:3》和内部电压信号vot_gen。电流泄漏检测器110然后可以将参考电压信号ref《1:3》与内部电压信号vot_gen相比较以生成电流泄漏状态信号st_flag《1:3》。

97.当参考电压信号ref《1:3》的电压电平高于内部电压信号vot_gen的电压电平时,可以输出图4中的具有高逻辑电平的电流泄漏状态信号st_flag《1:3》。当参考电压信号ref《1:3》的电压电平低于内部电压信号vot_gen的电压电平时,可以输出具有低逻辑电平的电流泄漏状态信号st_flag《1:3》。

98.如图5中所示,泄漏补偿脉冲发生器120可以基于电流泄漏状态信号st_flag《1:3》来控制偏置电平补偿信号lk_cp的时钟脉冲的宽度。泄漏补偿脉冲发生器120可以基于温度状态信号temp_info《1:3》来控制偏置电平补偿信号lk_cp的时钟脉冲的周期。

99.以上描述的本发明的实施例意图进行说明并且不对本发明进行限制。各种替换方式和等同方式是可能的。本发明不限于在本文描述的实施例。本发明也不受限于任何特定类型的半导体器件。考虑本公开,其他添加、减少或修改是明显的,并且其旨在落入所附权利要求的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。