1.本文所描述的主题的实施例大体上涉及半导体装置,包括双极结晶体管(bjt)和异质结双极晶体管(hbt)。

背景技术:

2.半导体装置应用于广泛多种电子部件和系统。此外,适用于射频(rf)、微波和毫米波应用的半导体装置可包括bjt型、hbt型和相关装置。具体地说,hbt型装置由于其快速传送时间、高截止频率、高增益和良好线性特性而适用于高频率应用。这些hbt型装置充当有源增益元件并且在rf、微波和毫米波功率放大器、振荡器以及其它有用的电子部件中用作有源装置。在用于这些装置的这些和其它应用中,需要减小集电极结电容(c

jc

)。减小c

jc

对于实现更高的最高震荡频率(f

max

)和改善这些应用的频率响应来说是重要的。f

max

的值与c

jc

成反比。常规bjt和hbt结构在集电极结电容c

jc

与断开状态集电极-基极击穿电压(bv

cbo

)之间进行权衡。因此,需要改进bjt和hbt装置中的性能。

技术实现要素:

3.根据本发明的第一方面,提供一种半导体装置,包括:

4.半导体基板;

5.第一半导体类型的第一半导体区,其形成于所述半导体基板内,其中所述第一半导体区包括形成于所述第一半导体区的下部部分中的第一掺杂区和形成于所述第一半导体区的上部部分中的处于所述第一掺杂区上方的第二掺杂区,以及形成于所述第一掺杂区的上部部分中的具有上表面的缺陷层;以及

6.第二半导体类型的第二半导体区,其形成于所述第一半导体区上方。

7.在一个或多个实施例中,所述缺陷层包括在所述缺陷层的所述上表面下方聚结的位错环,并且其中所述缺陷层的所述上表面接触所述第二掺杂区。

8.在一个或多个实施例中,所述第一半导体类型是n型,并且所述第二半导体类型是p型。

9.在一个或多个实施例中,所述第二掺杂区具有大于1e19cm-3

的掺杂剂浓度。

10.在一个或多个实施例中,所述半导体装置另外包括形成于所述第二半导体区上方的第三半导体区,其中所述第一半导体区被配置为集电极区,所述第二半导体区被配置为基极区,并且所述第三半导体区被配置为发射极区。

11.在一个或多个实施例中,所述半导体装置另外包括发射器层,所述发射器层包括设置在所述集电极区与所述基极区之间的具有5e16cm-3

与1e18cm-3

之间的掺杂剂浓度的所述第一半导体类型的半导体材料。

12.在一个或多个实施例中,所述半导体装置另外包括形成于所述第二半导体区下方并且在所述第一掺杂区、所述第二掺杂区与侧向邻近所述第一掺杂区和所述第二掺杂区形成的隔离区侧壁之间的第四半导体区,其中所述第四半导体区包括低于所述第二掺杂区的

掺杂度的掺杂度。

13.在一个或多个实施例中,所述第一掺杂区和所述第二掺杂区包括预非晶化掺杂剂。

14.在一个或多个实施例中,所述预非晶化掺杂剂选自由锗、氙和锡组成的群组。

15.根据本发明的第二方面,提供一种双极晶体管装置,包括:

16.半导体基板,其包括硅;

17.集电极区,其形成于所述半导体基板内,其中所述集电极区包括形成于所述集电极区的下部部分中的第一掺杂区、形成于所述集电极区的上部部分中的处于所述第一掺杂区上方的第二掺杂区,以及形成于所述第一掺杂区的上部部分中的具有上表面的缺陷层;

18.基极区,其形成于所述集电极区上方,其中所述基极区包括硅和锗;以及

19.发射极区,其形成于所述基极区上方,其中所述发射极区包括硅。

20.在一个或多个实施例中,所述第二掺杂区具有大于1e19cm-3

的掺杂剂浓度。

21.在一个或多个实施例中,所述第一掺杂区和所述第二掺杂区包括预非晶化掺杂剂。

22.在一个或多个实施例中,所述双极晶体管装置另外包括形成于所述基极区下方并且在所述第一掺杂区、所述第二掺杂区与侧向邻近所述第一掺杂区和所述第二掺杂区形成的集电极区侧壁之间的间隔区,其中所述间隔区包括低于所述第二掺杂区的掺杂度的掺杂度。

23.根据本发明的第三方面,提供一种用于形成双极晶体管装置的方法,所述方法包括:

24.形成半导体基板;

25.在所述半导体基板内形成集电极区,其中形成所述集电极区包括在所述集电极区的下部部分中形成第一掺杂区、在所述集电极区的上部部分中在所述第一掺杂区上方形成第二掺杂区,以及在所述第一掺杂区与所述第二掺杂区之间形成缺陷区;

26.形成基极区,所述基极区形成于所述集电极区上方;以及

27.形成发射极区,所述发射极区形成于所述基极区上方。

28.在一个或多个实施例中,形成所述集电极区包括将掺杂剂物种注入所述集电极区中以产生非晶层。

29.在一个或多个实施例中,所述半导体基板包括硅,并且所述掺杂剂物种包括砷。

30.在一个或多个实施例中,所述方法另外包括使所述非晶层的至少一部分再结晶以形成所述第一掺杂区、所述第二掺杂区和所述缺陷区。

31.在一个或多个实施例中,使所述非晶层再结晶包括选自由快速热退火、炉退火和激光退火组成的群组的方法。

32.在一个或多个实施例中,注入掺杂剂物种包括注入预非晶化掺杂剂物种。

33.在一个或多个实施例中,形成所述集电极区包括在所述基极区下方在集电极侧壁与所述第一掺杂区和所述第二掺杂区之间形成间隔区,其中所述间隔区的掺杂剂浓度低于所述第二掺杂区的掺杂剂浓度。

34.本发明的这些和其它方面将根据下文中所描述的实施例显而易见,且参考这些实施例予以阐明。

附图说明

35.通过参考结合以下图式考虑的具体实施方式和权利要求书可得到对主题的更完整理解,图中类似附图标记在各图中指代类似元件。

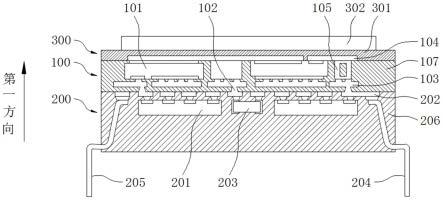

36.图1是常规装置的横截面侧视图。

37.图2是根据实施例的半导体装置的横截面侧视图;

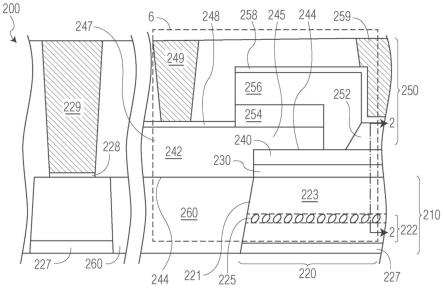

38.图3是掺杂剂浓度与沿图1和2中所示的切割线1-1和2-2的距离的图;

39.图4是根据实施例的半导体装置的横截面侧视图;

40.图5是根据实施例的半导体装置的横截面侧视图;

41.图6是根据实施例的具有描述用于制造图2的半导体装置的方法的对应横截面图的过程流程图;

42.图7是根据实施例的具有描述用于制造图4的半导体装置的方法的对应横截面图的过程流程图;以及

43.图8是根据实施例的具有描述用于制造图5的半导体装置的方法的对应横截面图的过程流程图。

具体实施方式

44.本文中描述了半导体装置的实施例。在一个方面,半导体装置的实施例可包括半导体基板和形成于所述半导体基板内的第一半导体类型的第一半导体区。根据实施例,所述第一半导体区可包括:第一掺杂区,其形成于所述第一半导体区的下部部分中;第二掺杂区,其形成于所述第一半导体区的上部部分中,处于所述第一掺杂区上方;以及具有上表面的缺陷层,其形成于所述第一掺杂区的上部部分中。在实施例中,第二半导体类型的第二半导体区可形成于所述第一半导体区上方。

45.在实施例中,所述缺陷层可包括在所述缺陷层的上表面下方聚结的位错环,其中所述缺陷层的上表面可接触第二掺杂区。根据实施例,第一半导体类型可以是n型,并且第二半导体类型可以是p型。在实施例中,第二掺杂区可具有大于1e19cm-3

的掺杂剂浓度。

46.根据实施例,所述半导体装置可包括形成于第二半导体区上方的第三半导体区。在实施例中,第一半导体区可被配置为集电极区,第二半导体区可被配置为基极区,并且第三半导体区可被配置为发射极区。根据实施例,包括第一半导体类型的半导体材料的发射器层可具有在5e16cm-3

与1e18cm-3

之间的掺杂剂浓度,并且可设置在集电极区与基极区之间。

47.在其它实施例中,第四半导体区可形成于第二半导体区下方且在第一掺杂区、第二掺杂区与侧向邻近所述第一掺杂区和所述第二掺杂区形成的隔离区侧壁之间。根据实施例,第四半导体区可包括低于第二掺杂区的掺杂度的掺杂度。

48.在其它实施例中,第一掺杂区和第二掺杂区可包括预非晶化掺杂剂。根据实施例,所述预非晶化掺杂剂可包括锗、氙或锡。

49.在另一方面,本发明主题的实施例可包括硅锗异质结双极晶体管装置,所述硅锗异质结双极晶体管装置包括可包括硅的半导体基板。根据实施例,集电极区可形成于半导体基板内,其中所述集电极区可包括形成于所述集电极区的下部部分中的第一掺杂区、形成于所述集电极区的上部部分中的处于所述第一掺杂区上方的第二掺杂区,以及形成于所

述第一掺杂区的上部部分中的具有上表面的缺陷层。在实施例中,基极区可形成于集电极区上方,其中所述基极区可包括硅和锗。发射极区可形成于基极区上方,其中所述发射极区可包括硅。在实施例中,第二掺杂区可具有大于1e19cm-3

的掺杂剂浓度。

50.在其它实施例中,硅锗异质结双极晶体管装置可包括形成于基极区下方且在第一掺杂区、第二掺杂区与侧向邻近第一掺杂区和第二掺杂区形成的集电极区侧壁之间的间隔区。根据实施例,间隔区可具有低于第二掺杂区的掺杂度的掺杂度。

51.在其它实施例中,第一掺杂区和第二掺杂区可包括预非晶化掺杂剂。

52.在另一方面,公开一种用于形成双极晶体管的方法。在实施例中,所述方法可包括形成半导体基板以及在所述半导体基板内形成集电极区。根据实施例,形成集电极区可包括:在所述集电极区的下部部分中形成第一掺杂区;在第一掺杂区上方在所述集电极区的上部部分中形成第二掺杂区;以及在第一掺杂区的上部部分中形成缺陷区。在实施例中,所述方法可包括在集电极区上方形成基极区以及形成发射极区,所述发射极区形成于所述基极区上方。根据实施例,形成集电极区可包括将掺杂剂物种注入集电极区中以产生非晶层。在实施例中,所述半导体基板可包括硅,并且和掺杂剂物种包括砷。根据实施例,所述方法可包括使所述非晶层的至少一部分再结晶以形成第一掺杂区、第二掺杂区和缺陷区。在实施例中,使非晶层再结晶可包括快速热退火、炉退火和激光退火中的一种或多种退火。在其它实施例中,注入掺杂剂物种可包括注入预非晶化掺杂剂物种。

53.在其它实施例中,形成集电极区可包括在基极区下方在集电极侧壁与第一掺杂区和第二掺杂区之间形成间隔区。在这些实施例中,间隔层的掺杂剂浓度可低于第二掺杂区的掺杂剂浓度。

54.图1是常规装置100的横截面侧视图。根据实施例,常规装置100可包括半导体基板110、在半导体基板110内形成的集电极区120、设置在集电极区120上方的基极区140、耦合到基极区140的非本征基极区142,以及形成于基极区140上方的发射极区150。与本文中呈现的其它图一样,图1描绘了常规装置100对称的一半。如同本文公开的半导体装置(例如,图2、4、5中的半导体装置200、400、500),可通过围绕发射极区150的竖直轴线镜像处理或旋转所描绘的常规装置100的元件来实现常规装置100的全视图。

55.再次参考图1,并且在实施例中,半导体基板110可包括数个半导体区。如本文中所使用,术语“半导体区”可指单个或多个半导体区,所述半导体区可包括通过注入(例如,离子注入)形成的区或通过外延生长而生长的层。在实施例中,集电极区120可形成于半导体基板110内或形成于基板110上的外延生长层中。基极区140可在集电极区120上方形成,并且与集电极区120接触。非本征基极区142通常用于将基极区140耦合到接触层148和基电极149。

56.在常规装置100中,半导体基板110可包括硅(si)、碳(c)和/或锗(ge)。在常规装置中,集电极区120在半导体基板110的上部部分中形成。基极区140形成于集电极区120的上方。集电极区120、基极区140和发射极区150可包括si、c和/或ge中的一种或多种。常规装置100通常被配置为npn晶体管,使得集电极区120和发射极区150包括n型半导体,并且基极区140包括p型半导体。集电极区120通常在半导体基板110内形成。子集电极区127通常在半导体基板110内的集电极区120下方形成,并且用于提供到将子集电极区127与集电极129耦合的接触层128的电路径。在实施例中,子集电极区127的掺杂度通常高于集电极区120的掺杂

浓度。介电材料区160通常用于在装置之间提供隔离。

57.在常规装置100中,基极区140通常使用si或si与ge的混合晶体合金sige形成。在常规npn装置中,使用p型半导体形成基极区140。基极区140通常掺杂有硼(b)。在pnp常规装置中,使用n型半导体形成基极区140。非本征基极区142可在半导体基板110上方形成,并且提供到基极149的低电阻连接。集电极区120上方的在基极区140与非本征基极区142之间的重叠区144在基极区140与非本征基极区142之间提供低接触电阻以便提供较低的总基极电阻rb。

58.在常规装置100中,发射极区150可在基极区140上方形成。根据实施例,发射极区150包括本征发射极区152、发射极间隔层154和形成于本征发射极区152上方的发射极接触层158。根据实施例,发射极区150通常还包括在发射极接触层158上方形成的发射极159。

59.图2是根据实施例的示例性半导体装置200的横截面侧视图。根据实施例,半导体装置可包括:半导体基板210;集电极区220,其形成于半导体基板210内;基极区240,其形成于集电极区220上方;发射极区250,其形成于基极区240上方;非本征基极区242,其耦合到基极区240;以及隔离介电区260,其形成于非本征基极区242下方并且邻近于集电极区220和基极区240。

60.再次参考图2,并且在实施例中,半导体基板210可包括数个半导体区。如本文中所使用,术语“半导体区”可指单个或多个半导体区,所述半导体区可包括通过注入(例如,离子注入)形成的区或通过外延生长而生长的层。在实施例中,集电极区220可形成于半导体基板210内。根据实施例,基极区240可在集电极区220上方形成并且与集电极区220接触。

61.在实施例中,半导体基板210可包括硅(si)、锗(ge)、硅锗(sige)、砷化镓(gaas)、磷化镓(gap)、磷化铟镓(ingap)、磷化铟(inp)、氮化镓(gan)、氮化铝(aln)、氮化铟(inn)、碳化硅(sic)、蓝宝石或其它合适的材料中的一种或多种。在其它实施例中,半导体基板210可包括绝缘体上si(soi)。在实施例中,集电极区220可在半导体基板210的上部部分中形成。根据实施例,基极区240可在集电极区220上方形成。在实施例中,集电极区220、基极区240和发射极区250可包括si、ge、sige和sigec中的一种或多种。在其它实施例中,集电极区220、基极区240和发射极区250可包括gaas、gan、aln、inn、ingap和/或其它合适的材料中的一种或多种。在实施例中,半导体装置200可被配置为npn晶体管,使得集电极区220和发射极区250包括n型半导体并且基极区240可包括p型半导体。在其它实施例中,半导体装置200可被配置为pnp晶体管,使得集电极区220和发射极区250可包括p型半导体并且基极区240可包括n型半导体。如本文中所使用,术语“n型半导体”是指净电子浓度在约1e15cm-3

到约1e20cm-3

范围内的半导体材料,但可使用其它更高或更低的电子浓度。如本文中所使用,术语“p型半导体”是指空穴浓度在约1e15cm-3

到约1e20cm-3

范围内的半导体材料,但可包括其它更高或更低的空穴浓度。

62.在实施例中,集电极区220(即,“第一半导体区”)可形成于半导体基板210内。根据实施例,集电极区220可包括:集电极侧壁(即,“隔离侧壁”)221;第一掺杂区222,其形成于集电极区220的下部部分中并且邻近集电极侧壁221;第二掺杂区223,其形成于第一掺杂区222上方;以及缺陷层225,其形成于第一掺杂区222的上部部分中。在实施例中,缺陷层225的上表面可终止第一掺杂区222,并且可接触第二掺杂区223。在实施例中,可选择第一掺杂区222和第二掺杂区223的厚度和掺杂剂浓度以满足特定装置设计和应用的需要。

63.在实施例中,缺陷层225可包括范围末端(eor)缺陷、位错环、称为“{311}缺陷”的缺陷(由于所述缺陷在{311}晶面族中可观察到而命名)以及在第一掺杂区的上部部分中聚结的其它晶体缺陷。根据实施例,缺陷区225由于第一掺杂区222和第二掺杂区223的相对高注入剂量和后续再结晶退火而形成。

64.在实施例中,发射器层230可设置在集电极区220上方。根据实施例,发射器层可包括低掺杂或未掺杂材料(例如,si)。根据实施例,发射器层230可被配置成最大化注入到集电极区220中的电子的速度。

65.在一些实施例(例如,npn晶体管装置)中,可使用n型半导体形成集电极区220。在其它实施例(pnp晶体管装置)中,可使用p型半导体形成集电极区220。在实施例中,集电极区220的总厚度可具有约1000埃与3000埃之间的总厚度。在其它实施例中,集电极区220可具有在约100埃与约10000埃之间的总厚度,但也可使用其它厚度。在实施例中,第一掺杂区222可具有在约500埃与约2000埃之间的厚度。在其它实施例中,第一掺杂区222可具有在约50埃与约9000埃之间的厚度,但也可使用其它更厚以及更薄的值。在实施例中,第二掺杂区223可具有在约500埃与约2000埃之间的厚度。在其它实施例中,第二掺杂区223可具有在约50埃与约9000埃之间的厚度,但也可使用其它更厚以及更薄的值。在实施例中,缺陷层225可具有在约500埃与约1500埃之间的厚度。在其它实施例中,缺陷层225可具有在约100埃与约5000埃之间的厚度,但也可使用其它厚度。在实施例中,发射器层230可具有在约100埃与约300埃之间的厚度。在其它实施例中,发射器层230可具有在约50埃与约1000埃之间的厚度,但也可使用其它更厚以及更薄的值。

66.在包括n型集电极区的实施例(例如,npn晶体管)中,集电极区220可掺杂有磷(p)、砷(as)、锑(sb)、锂(li)或其它合适的掺杂剂中的一种或多种。在一些npn实施例(n型集电极掺杂)中,第一掺杂区222的掺杂剂浓度可在约5e18cm-3

与约5e20cm-3

掺杂剂浓度之间。在这些npn实施例中,第二掺杂区223的掺杂剂浓度可在约1e18cm-3

与约2e20cm-3

掺杂剂浓度之间。在其它npn实施例中,第一掺杂区222可具有在约2e18cm-3

与约2e21cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。在npn实施例中,第二掺杂区223可具有在约1e19cm-3

与5e20cm-3

之间的掺杂剂浓度。在其它npn实施例中,第二掺杂区223可具有在约1e17cm-3

与2e21cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。此外,在这些npn实施例中,发射器层230的掺杂剂浓度可在约5e16cm-3

与约1e18cm-3

掺杂剂浓度之间。在其它npn实施例中,发射器层230可具有在约1e16cm-3

与约5e19cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。

67.在包括p型集电极区220的实施例(例如,pnp晶体管)中,集电极区220可掺杂有碳(c)、硼(b)、氧(o)或铟(in)中的一种或多种,但可使用其它的掺杂剂物种。在一些pnp实施例(p型集电极掺杂)中,第一掺杂区222的掺杂剂浓度可在约1e18cm-3

与约2e20cm-3

掺杂剂浓度之间。在其它pnp实施例中,第一掺杂区222可具有在约2e18cm-3

与约5e20cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。在这些pnp实施例中,第二半导体区的掺杂剂浓度可在约1e18cm-3

与约5e20cm-3

掺杂剂浓度之间。在其它pnp实施例中,第二掺杂区223可具有在约5e17cm-3

与约2e21cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。此外,在这些pnp实施例中,发射器层230的掺杂剂浓度可在约5e16cm-3

与约1e19cm-3

掺杂剂浓度之间。在其它pnp实施例中,第三掺杂区224可具有在约1e16cm-3

与

5e19cm-3

之间的掺杂剂浓度,但可使用其它更高或更低的掺杂剂浓度。

68.根据实施例,子集电极区227可在半导体基板210内的集电极区220下方形成,并且可通过接触层228提供到集电极229的低电阻连接。在实施例中,子集电极区227可具有与集电极区220相同的掺杂极性,但可以更高的掺杂浓度掺杂。在一些实施例中,与集电极区220相比,子集电极227可以类似或更低的浓度掺杂。在npn实施例中,子集电极区227的掺杂浓度可在约5e18cm-3

到1e21cm-3

的范围内。在实施例中,子集电极区227可以比集电极区220的掺杂浓度高10到100倍的掺杂浓度掺杂。根据实施例,子集电极区227可以比集电极区220的第二掺杂区223高10到1000倍的浓度掺杂。

69.在实施例中,基极区240可在集电极区220上方形成。根据实施例,可使用p型半导体形成基极区240。在实施例中,基极区240可掺杂有碳(c)。在其它实施例(例如,pnp晶体管)中,可使用n型半导体形成基极区240。在实施例中,可使用si

1-x

ge

x

形成基极区240,其中x是ge摩尔分数。在实施例中,基极区240的一个或多个部分可具有比发射极区250和集电极区220更窄的带隙。在实施例中,可通过改变ge摩尔分数来调整基极区240的一个或多个部分的带隙。在实施例中,ge摩尔分数x可在约0.05与约0.3之间变化,但可使用其它更大或更小的x值。在实施例中,ge摩尔分数的值在整个基极区240中可以是恒定的。在其它实施例中,基极区240的带隙可连续分级。在这些实施例中,例如si

1-x

ge

x

的基极材料的分级可包括形成基极区240的上部部分,所述上部部分具有较宽带隙并连续减小到基极区240中的下部部分中的较窄带隙。在p型基极区(例如,npn晶体管装置)的实施例中,基极区240可掺杂有c、b、o或in中的一种或多种,但可使用其它掺杂剂物种。在n型基极区的实施例(例如,pnp晶体管装置)中,基极区240可掺杂有p、li、as、sb中的一种或多种,但可使用其它掺杂剂物种。在实施例中,基极区240的掺杂浓度可在约5e17cm-3

到1e20cm-3

的范围内。在其它实施例中,基极区240的掺杂浓度可在约1e17cm-3

到1e20cm-3

的范围内,但可使用其它更高或更低的掺杂浓度。

70.在实施例中,非本征基极区242可形成于半导体基板210上方。在实施例中,可使用多晶硅形成非本征基极区242。在包括p型基极区240的实施例(例如,npn晶体管装置)中,非本征基极区242可掺杂有b、o、in或al中的一种或多种,但可使用其它掺杂剂物种。在包括n型基极区240的实施例(例如,pnp晶体管装置)中,非本征基极区242可掺杂有p、li、as或sb中的一种或多种,但可使用其它掺杂剂物种。在实施例中,非本征基极区242可包括与基极区240相同的掺杂剂物种。例如,基极区240和非本征基极区242均可包括b掺杂。在实施例中,非本征基极区242可包括形成于集电极区220和基极区240上方的第一部分245,以及形成于隔离介电区260上方的邻近集电极区220和基极区240的装置区域中的第二部分247。在实施例中,非本征基极区242可耦合到本征基极240的上表面244。在实施例中,基极249可通过基极接触层248耦合到非本征基极区242的第一部分245。

71.在实施例中,发射极区250可形成于基极区240上方。根据实施例,发射极区250可包括本征发射极区252、发射极间隔层254、非本征发射极区256以及形成于本征发射极区252上方的发射极接触层258。根据实施例,发射极区250还可包括形成于发射极接触层258上方的发射极259。

72.在实施例中,本征发射极区252可形成于基极区240上方,而非本征发射极区256可形成于发射极间隔层254上方。在实施例中,发射极间隔层254可包括一个或多个介电层,所

述一个或多个介电层包括相同或不同的介电类型。在实施例中,发射极间隔层254可包括二氧化硅、正硅酸乙酯(teos)、氮化硅(sin)、氧氮化硅(sion)、氧化铝(al2o3)、氮化铝(aln)、聚酰亚胺、苯并环丁烯(bcb)、旋涂式玻璃或其它合适的介电材料中的一种或多种。

73.在实施例中,可使用n型半导体形成本征发射极区252。在其它实施例中,可使用p型半导体形成本征发射极区252。根据实施例,本征发射极区252可包括单晶半导体。在实施例中,本征发射极区252可具有在约100埃与1000埃之间的厚度。在其它实施例中,本征发射极区252可具有在约50埃与约5000埃之间的厚度,但也可使用其它厚度。在包括p型发射极区250的实施例(例如,pnp晶体管装置)中,发射极区252可掺杂有b、o、al或in中的一种或多种,但可使用其它掺杂剂物种。在p型发射极区的实施例(例如,pnp晶体管装置)中,基极区240可掺杂有p、li、as或sb中的一种或多种,但可使用其它掺杂剂物种。在实施例中,本征发射极区252的掺杂浓度可在约5e17cm-3

到5e21cm-3

的范围内。

74.在实施例中,非本征发射极区256可形成于发射极间隔层254上方。在实施例中,非本征发射极区256可包括多晶半导体材料。在其它实施例中,非本征发射极区256可使用单晶半导体材料形成。在实施例中,非本征发射极区256可掺杂有与本征发射极相同的掺杂剂。

75.根据实施例,发射极接触层258可形成于非本征发射极区256和本征发射极区252上方。在实施例中,可使用钛钨(tiw)、氮化钛钨(tiwn)、硅化钨(wsi)、硅化钴(cosi)、硅化铂(ptsi)、硅化镍铂(niptsi)或其它合适的材料形成发射极接触层258。根据实施例,发射极259可在发射极接触层258上方形成。在实施例中,发射极259可由铜、铝、钨或其它合适的导电材料之一形成。

76.在实施例中,隔离介电区260可设置成侧向邻近基极区240并在非本征基极区242下方。隔离介电区260可包括多个介电层(未示出)。根据实施例,隔离介电区260的多个介电层中的每个介电层的一部分可设置在集电极区220的一部分与非本征基极区242之间。根据实施例,隔离介电区260可邻近集电极区220、基极区240和子集电极区227的一部分形成。在实施例中,隔离介电区260可包括一个或多个介电层,所述一个或多个介电层包括相同或不同介电类型。在实施例中,隔离介电区260可包括二氧化硅(sio2)、teos、sin、sion、al2o3、aln、聚酰亚胺、苯并环丁烯(bcb)、旋涂式玻璃或其它合适的介电材料中的一种或多种。例如,隔离介电区260可包括teos和sin。在其它实施例中,隔离介电区260可包括sin。在实施例中,隔离介电区260的总厚度可在约1500埃与约5000埃之间,但也可使用其它更厚或更薄的厚度。

77.图3是模拟的掺杂剂浓度与沿图1和2中所示的切割线1-1和2-2的距离的图。轨迹310表示沿图1的常规装置100中的切割线1-1的掺杂剂浓度。轨迹312表示沿图2的半导体装置200的切割线2-2的掺杂剂浓度。在实施例中,区320中表示常规装置100和半导体装置200的集电极区120、220的掺杂差314,集电极区220中的半导体装置200可高于集电极区120中的常规装置100的掺杂剂浓度约三倍与十倍之间。在其它实施例中,常规装置100与半导体装置200之间的掺杂浓度差314可能更高或更低而无限制。对于此比较,由区340和350表示的基极区240和发射极区250中的掺杂剂浓度极为类似。

78.具有图3中所描述的掺杂剂浓度分布的图2的半导体装置200相比于常规装置可具有改进的性能,因为集电极-发射极击穿电压更高并且集电极电阻更低。下表概述图2的半

导体装置200与常规装置100之间的模拟性能的差异。在表中,“常规装置”是指图1的常规装置100,“示例装置”是指图2的半导体装置200。表中列出的装置度量包括集电极-发射极电压为1.3v时按千兆赫(ghz)计的峰值单位栅极电流截止频率(f

t

)、集电极-发射极电压为1.3v时按ghz计的峰值最大振荡频率(f

max

)、作为无量纲的峰值基极-发射极电流增益(β)值、660毫伏(mv)基极-发射极电压下按微安(μa)计的集电极电流、按毫微微法拉(ff)计的集电极结电容(c

jc

)、按ff计的发射极结电容(c

je

)、按伏(v)计的集电极-基极击穿电压(bv

cbo

)。如从表所见,这些实施例中的每一个实施例可具有改进的f

max

值,这部分地归因于本文中呈现的装置改进引起的c

jc

值的减小。根据f

t

、f

max

、bv

cbo

、bv

cbe

之间所要的权衡,可选择本文中呈现的本发明主题的特定实施例。

[0079][0080]

图4和5分别描绘在半导体装置400和500中具有缺陷层的半导体装置的其它实施例。在这些实施例中,可调整集电极区的形成以允许晶体管的性能权衡。图4和5中编号的图式具有相似的编号,并且可与和图2相关联的描述和附图标记进行比较。例如,图2中的半导体基板210对应于图4、5中的半导体基板410和510。另外,为简洁起见,如果结合图2的描述给出了充分的描述,则可不重复与每个编号项目相关联的编号参考和制造细节的描述。

[0081]

图4是根据实施例的示例性半导体装置400的横截面侧视图。半导体装置400可包括半导体基板410,半导体基板410包括用以限定具有缺陷层425的集电极区420、基极区440、非本征基极区440、发射极区450和隔离介电区460的半导体区,如上文所描述。可用与图2的晶体管装置200的配置方式类似的方式来配置半导体装置400的数个其它部件。例如,半导体基板410和其相关联半导体区(例如,集电极区420、基极区440等)可按与图2的半导体基板210中形成的那些对应区类似的方式形成。

[0082]

再次参考图4并且在实施例中,集电极区420可包括集电极侧壁421、形成于集电极区420的下部部分中的第一掺杂区422、形成于第一掺杂区422上方的第二掺杂区423,以及形成于第一掺杂区的上部部分内的缺陷层425,其中缺陷层425可接触第二掺杂区423。根据实施例,可在集电极侧壁421与第一掺杂区422、第二掺杂区423和缺陷层425之间形成间隔区426(即,“第四半导体区”)。通过控制间隔件426的间隔侧向尺寸480,可定制第一掺杂区、第二掺杂区和缺陷层425的有效集电极侧向尺寸482以实现集电极电容(c

jc

)的更低值,从而实现c

bc

与集电极电阻(r

jc

)之间的所要折衷。根据实施例,间隔件侧向尺寸480可在约50与1500nm之间。在实施例中,有效集电极侧向尺寸482可在约50与1500nm之间。在其它实施例中,间隔件侧向尺寸480可在约10与3000nm之间,但根据实施例,可使用其它更大或更小的值。在这些其它实施例中,有效集电极侧向尺寸482可在约10与3000nm之间,但可使用其它更大或更小的值。

[0083]

图5是根据实施例的示例性半导体装置500的横截面侧视图。半导体装置500可包

括半导体基板510,半导体基板510包括半导体区,所述半导体区用以限定包括缺陷层525的第一掺杂区522、第二掺杂区523的集电极区520、基极区540、非本征基极区542、发射极区550和隔离介电区560,如上文所描述。可用与图2的晶体管装置200的配置方式类似的方式来配置半导体装置500的数个其它部件。例如,半导体基板510和其相关联半导体区(例如,集电极区520、基极区540等)可按与图2的半导体基板210中形成的那些对应区类似的方式形成。

[0084]

再次参考图5并且在实施例中,集电极区520可包括集电极侧壁521、形成于集电极区520的下部部分中的第一掺杂区522、形成于第一掺杂区522上方的第二掺杂区523,以及在第一掺杂区522的上部部分内形成第一掺杂区522与第二掺杂区523之间的边界的缺陷层525。在实施例中,第一掺杂区522和第二掺杂区523可包括预非晶化物种。在示例性半导体装置500中,预非晶化物种可包括注入到可包括si的集电极区520中的ge。在其它实施例中,预非晶化物种可包括氙(xe)或锡(sn)。在实施例中,p可用作集电极区520的第一掺杂区522和第二掺杂区523中的掺杂剂。在其它实施例中,as、sb、li或其它适合的掺杂剂可用作集电极区520中的掺杂剂。

[0085]

图6、7和8描绘根据示例实施例方法的描绘用于产生图2和4到5的双极晶体管装置200、400和500的一系列制造步骤的过程流程图以及对应的横截面图。所述方法包括一系列步骤,为说明方便起见,仅示出最重要的步骤。例如,所述方法可包括涉及针对所述制造方法制备半导体基板210的数个动作。在其它实施例中,动作的排序可改变。

[0086]

图6是根据实施例的详述图2的区域6的部分形成以及描述用于制造图2的双极晶体管装置200的方法的过程流程图和对应横截面侧视图。

[0087]

在实施例中,在图6所示的步骤之前进行的制造步骤可包括通过使用离子注入(未示出)而注入掺杂剂物种(例如磷)来对子集电极区227进行注入。干式或湿式蚀刻可用于形成半导体区,所述半导体区在额外处理之后将变为集电极区220(步骤未示)。在实施例中,介电材料(例如,teos)可沉积在集电极台面周围以形成用于例如浅沟槽隔离(sti)的隔离介电层260,以在邻近装置之间提供隔离。在实施例中,包括隔离介电区260的一个或多个层可使用等离子体增强化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)、化学气相沉积(cvd)、热氧化物生长技术或其它适合的沉积技术来形成。

[0088]

参考图6,在框602中,所述方法可包括图案化集电极区220。在实施例中,图案化集电极区220可包括在半导体基板210上方形成底部抗反射涂层(barc)层620。在实施例中,barc层620可使用已优化折射率和厚度以抑制用于光刻的光波长处的反射的有机化合物形成。在实施例中,可在半导体基板210和覆盖半导体基板210的隔离介电区260的部分上施配和旋涂barc层620。在其它实施例中,barc层620可包括一个或多个介电层,例如sion。在这些实施例中,barc层620可使用lpcvd、pecvd、cvd、热氧化物生长技术或其它合适的沉积技术沉积。在实施例中,barc层620可具有在约50纳米与约200纳米之间的厚度,但可使用其它厚度。在实施例中,可将抗蚀剂层622施配在半导体基板210上方。在实施例中,抗蚀剂层622可被配置成用于通过光刻(光致抗蚀剂)进行图案化。在其它实施例中,抗蚀剂层622可使用被配置成用于通过电子束光刻(电子束抗蚀剂)进行图案化的抗蚀剂形成。在实施例中,抗蚀剂层622可具有在约300纳米与约600纳米之间的厚度。在其它实施例中,抗蚀剂层622可具有在约100纳米与约10000纳米之间的厚度,但可使用其它更薄或更厚的厚度。

[0089]

现参考图6,框604,所述方法的实施例可包括将一种或多种掺杂剂物种注入到集电极区220中。在实施例中,可使用离子注入用剂640注入一种或多种掺杂剂物种。在实施例中,as可注入集电极区220中。在示例性实施例中,离子注入用剂640中包括的as注入计划可包括其中包括第一剂、第二剂和第三剂的注入计划。在实施例中,第一剂可包括约4e14cm-2

与约8e14cm-2

之间的面积浓度以及约300千电子伏(kev)与约500kev之间的能量。根据实施例,第二剂可包括约1e14cm-2

与约3e14cm-2

之间的面积浓度,以及约100kev与约180kev之间的能量。在实施例中,第三剂可包括约0.5e14cm-2

与约1.5e14cm-2

之间的面积浓度以及约50kev与约150kev之间的能量。在其它实施例中,非限制性地,可使用更多或更少数目的用剂和/或具有更高或更低面积浓度和能量的用剂,以实现任何具体实施例的要求。在其它实施例中,可使用在集电极区220的外延生长期间引入的杂质将掺杂剂并入集电极区220中。在实施例中,掺杂剂物种的注入接近半导体基板210中的掺杂剂物种(例如,si)的溶解度极限。在实施例中,相对高的注入剂量在半导体基板的晶格中产生足够的点缺陷,所述点缺陷可将该区转变为集电极区220内的非晶区644。

[0090]

现参考图6,在框606中,所述方法的实施例可包括剥离在框602中形成和图案化的抗蚀剂或掩蔽层。在实施例中,剥离抗蚀剂可包括使抗蚀剂经历以下中的一者或多者:使用适当的抗蚀剂剥离化学品、灰化(例如氧等离子体)或二者的组合对抗蚀剂进行湿式剥离。在一个实施例中,barc层620可使用与抗蚀剂层相同的化学物质剥离。在其它实施例中,额外化学处理(例如,在例如介电材料用于形成barc层620的情况下对介电体进行蚀刻的干式或湿式化学处理)可用于移除barc层620。

[0091]

参考图6,在框608中,所述方法还可包括对注入的集电极区220进行再结晶退火。在实施例中,再结晶退火可包括低温退火。再结晶退火可使用快速热退火(rta)、激光和/或炉中的一种或多种实现。根据实施例,可在约500摄氏度(℃)与约650℃之间的温度下进行再结晶退火。在其它实施例中,可在约400摄氏度(℃)与约1000℃之间的温度下进行再结晶退火,但根据实施例,可使用更高或更低的温度。在实施例中,再结晶退火的持续时间可在约10秒与约100秒之间。在其它实施例中,再结晶退火的持续时间可在约5秒与约500秒之间,但可使用更短或更长的持续时间。在实施例中,可在氮气环境中进行低温退火。在其它实施例中,低温退火可与集电极区220的激光照射或“尖峰”组合。在这些实施例中,可扫描激光束以提供局部加热集电极区220的激光尖峰。在一些实施例中,激光尖峰可熔融非晶区以使形成于集电极区220中的非晶层再结晶。在实施例中,再结晶退火可使集电极区220中的非晶层再结晶。在实施例中,由于再结晶退火,可在第一掺杂区222的上部部分中形成缺陷层225。在一些实施例中,再结晶退火可仅使第二掺杂区223再结晶,并且使非晶区保留在第一掺杂区222的一部分内(未示)。

[0092]

参考图6,在框610中,所述方法的实施例可包括形成发射器层230。根据实施例,形成发射器层230可包括在集电极区220上方形成例如si的半导体层外延层生长。在形成发射器层之前,可使用干式(例如,反应性离子蚀刻(rie)或电感耦合等离子体(icp)蚀刻)和/或湿式蚀刻移除集电极区220上方的一部分隔离介电区260以暴露集电极区220(未示)。在实施例中,可使用例如金属有机化学气相外延法(mocvd)、化学气相沉积(cvd)、分子束外延法(mbe)或其它合适的方法等外延生长来形成发射器层230。在其它实施例中,发射器层230可通过在集电极区220上方的半导体区中进行离子注入而形成(未示)。

[0093]

参考图6,在框612中,所述方法可包括在发射器层230和集电极区220上方形成基极区240、形成发射极区250,以及与集电极区220、基极区240和发射极区250相关联的触点。在实施例中,基极区240可形成于发射器层230的暴露上表面650上。在实施例中,cvd或mocvd可用于使用选择性外延生长来使基极区240外延地生长。在实施例中,可通过允许外延材料仅在暴露半导体区(例如,发射器层230,或在其它实施例中,集电极区220(未示出))上成核来促进选择性外延生长。根据实施例,外延材料可能不会在周围半导体区域上成核并且在所述周围半导体区域上方生长。在实施例中,非选择性外延可促进发射器层230和基极区240在暴露的集电极区223上的外延(单晶)生长,同时在介电区260(未示)上沉积多晶材料。

[0094]

仍参考图6,框612,根据实施例,在形成基极区240之后,非本征基极区242可形成于基极区240的至少一部分上方以将基极区240电耦合到非本征基极区242。在实施例中,可使用cvd或mocvd或其它合适的方法沉积p 多晶si或p 单晶si来形成非本征基极区242。在其它实施例中,可在形成基极区240之前形成非本征基极区242,并且可形成作为沉积第二基极区层的一部分而形成的单独基极连接,以将非本征基极区电耦合到基极区(未示)。

[0095]

仍参考图6,框612,根据实施例,在形成非本征基极区242并将其电耦合到基极区240之后,所述方法可包括在基极区240上方形成发射极区250。在实施例中,形成发射极区250可包括在基极区240上方在发射极窗口652内形成本征发射极区252。在实施例中,发射极间隔层254可形成于非本征基极区242上方。在实施例中,发射极间隔件254可包括例如sin或teos,但可使用其它材料。可使用pecvd、lpcvd或cvd沉积来形成发射极间隔层。可利用各向异性竖直蚀刻移除基极区240上的介电体来在发射极间隔层254中形成发射极窗口652。在一些实施例中,各向异性蚀刻可用于保留发射极窗口652的侧壁上的介电层(未示)。在间隔形成之后,可形成本征发射极区252。在实施例中,cvd或mocvd可用于使用选择性外延生长来使本征发射极区252外延地生长。根据实施例,可在生长本征发射极区252的同时在发射极间隔层上方生长非本征发射极区256。

[0096]

仍参考图6,框612,在实施例中,可通过形成基极接触层248、发射极接触层258、集电极接触层228(未示)、基极249、发射极259和集电极229(未示)来完成装置处理。根据实施例,可使用物理气相沉积(pvd)或其它合适的技术形成接触层228、248、258。在实施例中,可使用物理气相沉积(pvd)或其它合适的技术形成集电极229、基极249和发射极259。然后,取决于装置应用和要求,可进行其它处理,例如介电沉积、额外金属化、平面化和其它部件的制造(未示)。

[0097]

图7和8分别描绘了根据图4和图5的双极晶体管装置400和500的实施例的用于形成双极晶体管装置的各种方法。这些图中编号的图式具有类似的编号,并且可与和图7到8相关联的描述以及图4到5中的对应编号进行比较。例如,图2中的半导体基板210对应于图4到5和图7到8中的半导体基板410和510。另外,为简洁起见,如果结合图6和图2的描述给出了充分的描述,则可不重复与每个编号项目相关联的编号参考和制造细节的描述。

[0098]

例如,图2中的半导体基板210对应于图4-5和图7-8中的半导体基板410和510。此外,为了简洁起见,如果结合图6和图2的描述给出了充分的描述,则可以不重复与每个编号项目或步骤相关的编号参考和制造细节的描述。

[0099]

图7描绘根据实施例的详述形成图4的区域7并且描述用于制造图4的双极晶体管

装置400的方法的过程流工艺流程图和对应横截面侧视图。现参考图7,框702,并且在实施例中,图案化集电极层420可包括在硬掩模层724上方形成barc层720和抗蚀剂层722。根据实施例,硬掩模层724可使用例如通过lpcvd或pecvd沉积的sin形成。在实施例中,使用硬掩模层724可允许使用更小的尺寸来产生间隔层426以及集电极区420的有效部分的更小侧向尺寸(例如,图4的集电极有效侧向尺寸482)。可用与结合图6的框604到612描述的那些步骤类似的方式来执行框704到712中详述的其余制造步骤。

[0100]

图8描绘了过程流工艺流程图和对应横截面侧视图,详述形成图5的区域8。参考图8的框804,在图案化图8的框802中所描绘的集电极区之后,集电极区520可被注入离子注入用剂840。离子注入用剂840可包括预非晶化注入物841和掺杂剂注入物842。预非晶化注入物841可包括例如ge、xe或sn。在预非晶化注入物841之后,掺杂注入物842(例如p)可用于实现集电极区520的掺杂。在其它实施例中,li、as或sb可用于实现集电极区520的掺杂。作为预非晶化注入物841和注入物842的结果,可形成非晶区844。在完成离子注入用剂840之后,可类似于结合图6的框604到612所述的那些步骤来执行框804到812中详述的其余制造步骤。

[0101]

以下详细描述本质上仅为说明性的,并不意图限制主题的实施例或此类实施例的应用和使用。如本文所使用,词语“示例性”或“示例”意指“充当例子、实例或图解说明”。本文中描述为示例性或例子的任何实施方案未必应理解为比其它实施方案优选或有利。此外,并不意欲受到前述技术领域、背景技术或所附的具体实施方式中呈现的任何明确或暗示的理论束缚。

[0102]

出于简洁起见,本文中可能未详细描述常规的半导体制造技术。另外,本文中还可仅出于参考的目的使用某些术语,因此这些术语并不意图具有限制性,并且除非上下文清楚地指示,否则指代结构的术语“第一”、“第二”和其它此类数值术语并不暗示顺序或次序。

[0103]

前文描述提及元件或节点或特征“连接”或“耦合”在一起。如本文所使用,除非以其它方式明确地陈述,否则“连接”意指一个元件直接连接到另一元件(或与另一元件直接连通),且不必以机械方式。同样,除非以其它方式明确地陈述,否则“耦合”意指一个元件直接或间接连接到另一元件(或直接或间接与另一元件连通),且不必以机械方式。因此,虽然图中示出的示意图描绘元件的一个示例性布置,但额外的居间元件、装置、特征或部件可存在于所描绘主题的实施例中。

[0104]

尽管前文具体实施方式中已呈现至少一个示例性实施例,但应了解,存在大量变型。还应了解,本文中描述的一个或多个示例性实施例并非旨在以任何方式限制所要求保护的主题的范围、适用性或配置。实际上,前述具体实施方式将向本领域的技术人员提供用于实施所描述的一个或多个实施例的方便指南。应理解,可在不脱离由权利要求书所限定的范围的情况下对元件的功能和布置作出各种改变,权利要求书所限定的范围包括在提交本专利申请时的已知等同物和可预见的等同物。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。