1.本公开涉及半导体技术领域,尤其是涉及一种封装结构及其制作方法。

背景技术:

2.目前,采用在芯片上堆叠芯片(chip on chip)的方式形成的封装结构,其堆叠后的良率要比采用在晶圆上堆叠晶圆(wafer on wafer)的方式形成的封装结构的良率高很多,但是,采用chip on chip方式形成封装结构的产量比wafer on wafer低很多,且在制作过程中,芯片容易发生翘曲现象,从而限制了芯片的堆叠。

技术实现要素:

3.本公开的目的在于提供一种封装结构及其制作方法,以缓解现有技术中存在的在采用chip on chip方式形成封装结构的过程中,芯片容易发生翘曲现象的技术问题。

4.基于上述目的,本公开提供了一种封装结构的制作方法,包括以下步骤:

5.提供初始晶圆;

6.在所述初始晶圆上键合第一已知合格裸片,并形成第一芯片单元;

7.在所述第一芯片单元上键合中介层晶圆;

8.在远离所述初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元,其中,所述第一芯片单元包括多个间隔设置的第一已知合格裸片以及填充于相邻两个第一已知合格裸片之间的封装材料,所述第二芯片单元包括多个间隔设置的第二已知合格裸片以及填充于相邻两个第二已知合格裸片之间的封装材料。

9.在本公开的一个实施例中,在所述初始晶圆上键合第一已知合格裸片,并形成第一芯片单元的步骤包括:

10.提供多个第一晶圆,将所述多个第一晶圆键合以形成第一键合晶圆;

11.切割所述第一键合晶圆,以形成多个第一单颗裸片,从所述多个第一单颗裸片中选取多个第一已知合格裸片;

12.将多个所述第一已知合格裸片键合于所述初始晶圆上,在相邻两个所述第一已知合格裸片之间的间隙内填充封装材料,以形成第一芯片单元。

13.在本公开的一个实施例中,所述第一晶圆的数量为两个。

14.在本公开的一个实施例中,将多个所述第一已知合格裸片键合于初始晶圆上,在相邻两个所述第一已知合格裸片之间的间隙内填充封装材料,以形成第一芯片单元的步骤之后,还包括:

15.平坦化所述第一芯片单元的背面;

16.在平坦化后的所述第一芯片单元的背面制作第一金属化结构。

17.在本公开的一个实施例中,所述第一金属化结构包括焊垫。

18.在本公开的一个实施例中,在所述第一芯片单元上键合的所述中介层晶圆的厚度不小于200μm。

19.在本公开的一个实施例中,在远离所述初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元的步骤之前,还包括:

20.将所述中介层晶圆的厚度减薄;

21.在减薄后的中介层晶圆上制作第二金属化结构。

22.在本公开的一个实施例中,将所述中介层晶圆的厚度减薄至50μm以下。

23.在本公开的一个实施例中,所述第二金属化结构包括硅通孔和焊垫;所述在减薄后的中介层晶圆上制作第二金属化结构的步骤包括:

24.在减薄后的中介层晶圆中制作所述硅通孔;

25.在减薄后的中介层晶圆的上表面制作所述焊垫。

26.在本公开的一个实施例中,在远离所述初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元的步骤包括:

27.提供多个第二晶圆,将所述多个第二晶圆键合以形成第二键合晶圆;

28.切割所述第二键合晶圆,以形成多个第二单颗裸片,从所述多个第二单颗裸片中选取多个第二已知合格裸片;

29.将多个所述第二已知合格裸片混合键合于所述焊垫上,在相邻两个所述第二已知合格裸片之间的间隙内填充封装材料,以形成第二芯片单元。

30.在本公开的一个实施例中,在远离所述初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元的步骤之前,还包括:

31.在所述中介层晶圆上键合第一已知合格裸片,并形成第一芯片单元;

32.在所述第一芯片单元上键合中介层晶圆;

33.重复上述步骤,以形成堆叠设置的多个第一芯片单元,且所述第一芯片单元的远离所述初始晶圆的一侧均设置有中介层晶圆。

34.基于上述目的,本公开还提供了一种封装结构,所述封装结构采用所述的封装结构的制作方法制备。

35.基于上述目的,本公开还提供了一种封装结构,包括:

36.初始晶圆;

37.第一芯片单元,所述第一芯片单元位于所述初始晶圆上;

38.中介层晶圆,所述中介层晶圆位于所述第一芯片单元的远离所述初始晶圆的一侧;

39.第二芯片单元,所述第二芯片单元位于所述中介层晶圆的远离所述初始晶圆的一侧;

40.其中,所述第一芯片单元包括多个间隔设置的第一已知合格裸片以及填充于相邻两个第一已知合格裸片之间的封装材料,所述第二芯片单元包括多个间隔设置的第二已知合格裸片以及填充于相邻两个第二已知合格裸片之间的封装材料。

41.在本公开的一个实施例中,所述第一芯片单元的数量为多个,多个所述第一芯片单元沿垂直于所述初始晶圆的表面的方向堆叠设置,多个所述第一芯片单元的远离所述初始晶圆的一侧均设置有所述中介层晶圆。

42.在本公开的一个实施例中,所述中介层晶圆的厚度不大于50μm。

43.在本公开的一个实施例中,所述第一已知合格裸片和所述第二已知合格裸片均从

切割键合晶圆所形成的多个单颗裸片中选取,其中,所述键合晶圆包括键合在一起的两个晶圆。

44.本公开的有益效果主要在于:

45.本公开提供的封装结构的制作方法,能够在增加堆叠层数的同时,提高堆叠良率和产量。在本公开提供的封装结构的制作方法中,通过在初始晶圆上键合第一已知合格裸片,并形成第一芯片单元,即实现了芯片在晶圆上(chip on wafer)堆叠,从而将第一芯片单元重构成晶圆,然后在第一芯片单元上键合中介层晶圆,即实现了wafer on wafer堆叠,提高了产量。由于中介层晶圆能够对位于其下方的第一芯片单元进行压持,在堆叠过程中,能够减小因第一芯片单元翘曲带来的堆叠难度,从而能够实现更多层数的chip on chip堆叠。然后再在远离初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元,即再次实现了chip on wafer堆叠,提高了所制作的封装结构的良率。

附图说明

46.为了更清楚地说明本公开具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本公开的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

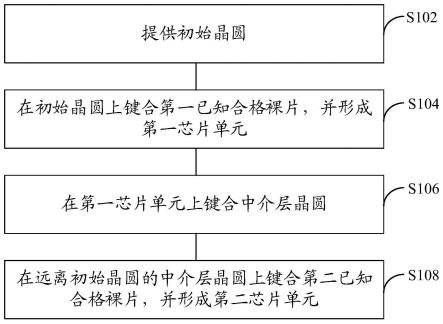

47.图1为本公开实施例提供的封装结构的制作方法的流程图;

48.图2a至图2f为对应图1中流程图所示的封装结构制作方法的示意图;

49.图3为本公开实施例提供的封装结构的制作方法中的步骤s104的流程图;

50.图4a和图4b为对应图3中流程图所制备的第一芯片单元的示意图;

51.图5为本公开实施例提供的封装结构的制作方法另一流程图;

52.图6为根据本公开实施例提供的封装结构的制作方法制备的封装结构的结构示意图;

53.图7为本公开实施例提供的封装结构的制作方法的又一流程图。

54.图标:100-初始晶圆;200-第一芯片单元;210-第一已知合格裸片;220-封装材料;300-中介层晶圆;400-第一晶圆;410-介质层;420-第二晶圆;500-第一键合晶圆;510-第一单颗裸片;520-第二键合晶圆;530-第二单颗裸片;610-焊垫;620-硅通孔;700-第二芯片单元;710-第二已知合格裸片。

具体实施方式

55.下面将结合实施例对本公开的技术方案进行清楚、完整地描述,显然,所描述的实施例是本公开一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

56.在本公开的描述中,需要说明的是,如出现术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等,其指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本公开和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。此外,如出现术

语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

57.在本公开的描述中,需要说明的是,除非另有明确的规定和限定,如出现术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本公开中的具体含义。

58.第一方面,本实施例提供了一种封装结构的制作方法。下面将参考图1所示出的内容,并结合图2a至图2f所示出的结构,对本实施例提供的封装结构的制作方法进行详细说明。

59.本实施例提供了一种封装结构的制作方法,包括以下步骤:

60.s102:提供初始晶圆100;

61.s104:在初始晶圆100上键合第一已知合格裸片210,并形成第一芯片单元200;

62.s106:在第一芯片单元200上键合中介层晶圆300;

63.s108:在远离初始晶圆的中介层晶圆上键合第二已知合格裸片710,并形成第二芯片单元700,其中,第一芯片单元200包括多个间隔设置的第一已知合格裸片210以及填充于相邻两个第一已知合格裸片210之间的封装材料220,第二芯片单元700包括多个间隔设置的第二已知合格裸片710以及填充于相邻两个第二已知合格裸片710之间的封装材料220。

64.本实施例提供的封装结构的制作方法,能够在增加堆叠层数的同时,提高堆叠良率和产量。在本实施例提供的封装结构的制作方法中,通过在初始晶圆100上键合第一已知合格裸片210,并形成第一芯片单元200,即实现了芯片在晶圆上(chip on wafer)堆叠,从而将第一芯片单元重构成晶圆,然后在第一芯片单元上键合中介层晶圆300,即实现了wafer on wafer堆叠,提高了产量。由于中介层晶圆300能够对位于其下方的第一芯片单元100进行压持,在堆叠过程中,能够减小因第一芯片单元翘曲带来的堆叠难度,从而能够实现更多层数的chip on chip堆叠。然后再在远离初始晶圆的中介层晶圆300上键合第二已知合格裸片710,并形成第二芯片单元700,即再次实现了chip on wafer堆叠,提高了所制作的封装结构的良率。

65.在一个实施例中,参见图2a所示,步骤s102中,提供的初始晶圆100的厚度可以根据实际需要进行设定,该初始晶圆100可以作为基底,在初始晶圆100的上表面制作焊垫610,以便于在初始晶圆100上键合第一已知合格裸片210。

66.在一个实施例中,步骤s104中,在初始晶圆100上键合第一已知合格裸片210,并形成第一芯片单元200,在一些实施例中,参见图2b所示,在初始晶圆100上形成一个第一芯片单元200。示例性的,在初始晶圆100上混合键合第一已知合格裸片。混合键合,也称为“金属/电介质混合键合”,是直接键合技术(例如,在不使用焊料或键合剂作为中间层的情况下在表面之间形成键合),并可以同时获得金属-金属键合和电介质-电介质键合。

67.在其他实施例中,也可以在初始晶圆100上堆叠形成多个(至少两个)第一芯片单元200,当在初始晶圆100上堆叠形成多个(至少两个)第一芯片单元200时,可以在每次堆叠形成一个第一芯片单元200后,进行一次步骤s106,具体而言,先在初始晶圆100上堆叠形成第一个第一芯片单元200,然后在第一个第一芯片单元200上键合中介层晶圆300,然后在中介层晶圆300上继续堆叠形成第二个第一芯片单元200,然后再在第二个第一芯片单元200

上键合中介层晶圆300,重复堆叠多个第一芯片单元200且形成中介层晶圆300后,最后再进行步骤s108,在远离初始晶圆100的第一芯片单元200上的中介层晶圆300上形成第二芯片单元700,也就是说,在最后一次形成的中介层晶圆300上形成第二芯片单元700。

68.需要说明的是,当在初始晶圆100上堆叠形成多个(至少两个)第一芯片单元200时,也可以先沿垂直于初始晶圆的表面的方向连续堆叠多个(至少两个)第一芯片单元200,然后再进行步骤s106,具体而言,在最后一次形成的第一芯片单元200上键合中介层晶圆300,最后再进行步骤s108。

69.当在初始晶圆100上堆叠形成的第一芯片单元200的数量可以为多个(至少两个)时,多个第一芯片单元200沿垂直于初始晶圆的表面的方向堆叠设置。

70.在一个实施例中,参见图3以及图4a和图4b所示出的结构,步骤s104中,在初始晶圆上键合第一已知合格裸片,并形成第一芯片单元200的步骤包括:

71.步骤s1041:提供多个第一晶圆400,将多个第一晶圆400键合以形成第一键合晶圆500;所形成的第一键合晶圆500的结构参见图4a所示。

72.步骤s1042:切割第一键合晶圆500,以形成多个第一单颗裸片510,从多个第一单颗裸片510中选取多个第一已知合格裸片210;

73.步骤s1043:将多个第一已知合格裸片210键合于初始晶圆100上,在相邻两个第一已知合格裸片210之间的间隙内填充封装材料220,以形成第一芯片单元200。所形成的结构参见图2b所示,该结构包括初始晶圆100以及形成于初始晶圆100上的第一芯片单元200。

74.示例性的,封装材料220可以包括高强度高热应力(高耐热)密封剂材料,该材料也可以具有高散热特性。此外,可能希望封装材料220的热膨胀系数(cte)小于20,以辅助对于芯片的翘曲度的控制。

75.所提供的晶圆可以使用各种技术来形成,以包括衬底和介质层410。例如,衬底可以包括硅、锗、玻璃、石英、介电表面、直接或间接间隙半导体材料等。介质层410沉积在衬底上,并且可以由无机介电材料层构成,诸如氧化物、氮化物、氮氧化物、碳氧化物、碳化物、金刚石、陶瓷等。

76.示例性的,第一晶圆400可以包括硅通孔620(tsv)和焊垫610。

77.应当理解的是,要在硅片上实现垂直的电互连,一般需要在上面制作微孔;在微孔的侧壁沉积绝缘材料;在微孔中填充导电材料等制造步骤。其中最具挑战的是微孔的批量刻蚀和导电化。先在硅片把需要刻蚀微孔的位置的硅裸露出来,用各向同性的腐蚀气体在硅片上刻蚀下去一薄层,然后在刻蚀出来的坑的表面沉积保护层,再用等离子打掉坑底的保护层打掉,再用各向同性的腐蚀气体刻蚀一薄层,通过这样多次微小的各向同性腐蚀循环就可以在硅片上实现批量的高深宽比微孔的刻蚀。硅通孔620不仅赋予了芯片纵向维度的集成能力,而且具有最短的电传输路径以及优异的抗干扰性能。

78.硅通孔620被直接耦合到相邻的晶圆的焊垫610,以提供到相邻的键合晶圆的连接。例如,硅通孔620的端面可以在晶圆的键合表面处暴露,以形成用于键合到相邻晶圆上的焊垫610的接触表面。在其他实施例中,晶圆可以包括在键合表面上的焊垫610,其中硅通孔620被耦合到焊垫610,这些焊垫610可以键合到相邻晶圆上的焊垫610或其他导电结构。

79.将多个第一晶圆400以混合键合的方式键合形成第一键合晶圆500,也就是说,第一键合晶圆500包括多层第一晶圆400。示例性的,假设两层晶圆的良率分别是95%,则两层

晶圆键合后的良率为90.25%,良率只降低了不到5%。如果采用三层以上晶圆键合在一起,则良率会降低至85.7%以下。因此,为了减少wafer on wafer堆叠导致的良率降低太多,本实施例中选择两片第一晶圆400进行键合,所形成的第一键合晶圆500的结构参见图4a所示,这样的方式能够大幅提高产量。

80.在一些实施例中,在多个第一单颗裸片510中选取第一已知合格裸片的方法可以包括以下步骤:

81.对晶圆进行晶圆测试,获取与晶圆对应的晶圆图,晶圆图用于表征裸片(die)在晶圆中的映射关系,其中记录有晶圆中每个die的位置和对应的测试结果;

82.每个第一单颗裸片510包含两个die,当第一单颗裸片510中的两个die所对应的晶圆图均显示合格时,则可以认为该第一单颗裸片510为已知合格裸片(know good die,kgd)。

83.如果单颗裸片中至少有一个die所对应的晶圆图显示不合格,则认为该单颗裸片为不合格芯片,需要将其剔除。

84.在一个实施例中,将多个第一已知合格裸片键合于初始晶圆上,在相邻两个第一已知合格裸片之间的间隙内填充封装材料,以形成第一芯片单元的步骤之后,还包括:

85.平坦化第一芯片单元200的背面;

86.在平坦化后的第一芯片单元200的背面制作第一金属化结构。

87.采用化学机械抛光(chemical mechanical polishing,cmp)工艺平坦化第一芯片单元200的背面,直至能够在该背面上制作第一金属化结构。

88.应理解,化学机械抛光是集成电路制造过程中实现晶圆表面平坦化的关键工艺。与传统的纯机械或纯化学的抛光方法不同,cmp工艺是通过表面化学作用和机械研磨的技术结合来实现晶圆表面微米/纳米级不同材料的去除,从而达到晶圆表面纳米级平坦化,使下一步的光刻工艺得以进行。

89.cmp工艺的主要工作原理是在一定压力下及抛光液的存在下,被抛光的晶圆对抛光垫做相对运动,借助纳米磨料的机械研磨作用与各类化学试剂的化学作用之间的高度有机结合,使被抛光的晶圆表面达到高度平坦化、低表面粗糙度和低缺陷的要求。

90.采用化学机械抛光方式平坦化第一芯片单元200的方式,使得平坦化后的结构平坦度高、表面粗糙度低以及缺陷少,便于后续工艺中制备其他膜层结构。

91.平坦化第一芯片单元200的背面,能够保证第一芯片单元200的背面(图示的顶面)的总厚度变化(total thickness variation,ttv)较小,满足wafer on wafer的要求。

92.在一个实施例中,参见图2b所示,第一金属化结构包括焊垫610。焊垫610与第一芯片单元200内的tsv导通。

93.在一个实施例中,参见图2c所示,在第一芯片单元200上键合形成的中介层晶圆300的厚度h1不小于200μm。

94.如果在第一芯片单元200上键合形成的中介层晶圆300的厚度过大,会导致成本高较高,如果在第一芯片单元200上键合形成的中介层晶圆300的厚度过小,则会导致中介层晶圆300对其下方的第一芯片单元200的压持效果较弱,防翘曲的效果不好,导致翘曲度无法得到有效控制。

95.因此,在第一芯片单元200上键合形成的中介层晶圆300的厚度不小于200μm,由于

中介层晶圆300的厚度较厚,这样既能够增强中介层晶圆300对其下方的第一芯片单元200的压持效果,又能够降低生产成本。

96.在一个实施例中,在远离初始晶圆的中介层晶圆上键合第二已知合格裸片,并形成第二芯片单元700的步骤之前,还包括:

97.将中介层晶圆300的厚度减薄;

98.在减薄后的中介层晶圆300上制作第二金属化结构。

99.为了便于在中介层晶圆300上制作第二金属化结构,需要将中介层晶圆300做减薄处理,从而有利于后续工艺的进行。

100.示例性的,减薄处理的方式有多种,例如,可以采用cmp工艺进行减薄处理。

101.具体而言,参见图2c和图2d所示,图2c中的中介层晶圆300的厚度h1是减薄之前的厚度,图2d中的中介层晶圆300的厚度h2是减薄后的厚度,其中,h2小于h1。

102.在一个实施例中,将中介层晶圆300的厚度减薄至50μm以下。也就是说,减薄后的中介层晶圆300的厚度h2为50μm以下,这样的方式有利于在中介层晶圆300内形成硅通孔620。

103.需要说明的是,中介层晶圆300的减薄后的厚度由硅通孔620工艺水平决定,当硅通孔620工艺水平能够穿透50μm以上的厚度时,也可以将中介层晶圆300的厚度减薄至50μm以上,也就是说,可以减少中介层晶圆300的减薄量。

104.在一个实施例中,参见图2e所示,第二金属化结构包括硅通孔和焊垫610;在减薄后的中介层晶圆300的表面制作第二金属化结构的步骤包括:

105.在减薄后的中介层晶圆300中制作硅通孔;

106.在减薄后的中介层晶圆300的上表面制作焊垫610。

107.在减薄后的中介层晶圆300中制作硅通孔620,有利于硅通孔620的制作,在减薄后的中介层晶圆300的上表面制作焊垫610,焊垫610与中介层晶圆300中硅通孔620导通。

108.在一个实施例中,在步骤s108中,在远离初始晶圆100的中介层晶圆300上键合第二已知合格裸片,并形成第二芯片单元700的步骤包括:

109.如图4a所示,提供多个第二晶圆420,将多个第二晶圆420键合以形成第二键合晶圆520;

110.切割第二键合晶圆520,以形成多个第二单颗裸片530,从多个第二单颗裸片530中选取多个第二已知合格裸片710;

111.将多个第二已知合格裸片710混合键合于焊垫上,在相邻两个第二已知合格裸片710之间的间隙内填充封装材料,以形成第二芯片单元700。

112.将多个第二已知合格裸片混合键合于焊垫上,能够使得第二芯片单元700与减薄后的中介层晶圆300的上表面的焊垫610进行导通。

113.当第一芯片单元200的数量为一个时,该第一芯片单元200即为远离初始晶圆100的第一芯片单元200,因此,可以直接在该第一芯片单元200上的中介层晶圆300上混合键合第二已知合格裸片710,在相邻两个第二已知合格裸片710之间的间隙内填充封装材料220,以形成第二芯片单元700,所得到的结构如图2f所示。

114.需要说明的是,第二芯片单元700中的芯片的制作方法与第一芯片单元200中的芯片的制作方法大体相同,在此不再赘述。应理解的是,形成第二键合晶圆所采用的第二晶圆

与形成第一键合晶圆所采用的第一晶圆的大小、厚度等可以相同,也可以不同,但两者的本质均为晶圆,因此,如无明确说明,本实施例中出现的“晶圆”,既适用于对第一晶圆的描述,也适用于对第二晶圆的描述。

115.在一个实施例中,参见图5所示,在远离初始晶圆的中介层晶圆上键合第二已知合格裸片710,并形成第二芯片单元700的步骤之前,还包括:

116.步骤s502:在中介层晶圆300上键合第一已知合格裸片210,并形成第一芯片单元200;

117.步骤s504:在第一芯片单元200上键合中介层晶圆300;

118.步骤s506:重复上述步骤,以形成堆叠设置的多个第一芯片单元,且第一芯片单元的远离初始晶圆的一侧均设置有中介层晶圆。

119.通过重复进行步骤s502和步骤s504,能够形成堆叠设置的多个第一芯片单元,多个第一芯片单元沿垂直于初始晶圆的表面的方向堆叠设置,且第一芯片单元的远离初始晶圆的一侧均设置有中介层晶圆,从而形成多个第一芯片单元200和多个中介层晶圆300交替堆叠的结构。然后在最后一次形成的中介层晶圆300上形成第二芯片单元。

120.需要说明的是,步骤s502中的中介层晶圆和步骤s504中的中介层晶圆是两个膜层,该两个中介层晶圆的厚度可以相同,也可以不同。

121.应当理解的是,在中介层晶圆上形成第一芯片单元以及在中介层晶圆上形成第二芯片单元之前,需要将中介层晶圆减薄,并在减薄后的中介层晶圆上制作第二金属化结构。

122.示例性的,进行一次步骤s502和步骤s504,最终形成的封装结构即可包括沿垂直于初始晶圆100的表面的方向堆叠设置的两个第一芯片单元200,且两个第一芯片单元200之间设置有中介层晶圆300,远离初始晶圆100的第一芯片单元200上也设置有中介层晶圆,第二芯片单元形成于该中介层晶圆上。所形成的结构如图6所示。

123.进行n次步骤s502和步骤s504,最终形成的封装结构即可包括沿垂直于初始晶圆100的表面的方向堆叠设置的n 1个第一芯片单元200,其中,n为大于等于1的整数。

124.采用这种方式能够形成多个第一芯片单元200和多个中介层晶圆300交替堆叠的结构,从而能够有效控制chip on chip的翘曲度,增加了堆叠层数,同时,提高了堆叠良率,也减少了封装的次数。

125.下面以在初始晶圆100上堆叠形成两个第一芯片单元200为例,对本实施例提供的封装结构的制作方法进行说明。

126.参见图7所示,本实施例提供的封装结构的制作方法,包括以下步骤:

127.步骤s702:提供初始晶圆100;

128.步骤s704:提供多个第一晶圆400,将多个第一晶圆键合以形成第一键合晶圆;切割第一键合晶圆,以形成多个第一单颗裸片,从多个第一单颗裸片中选取多个第一已知合格裸片;将多个第一已知合格裸片键合于初始晶圆上,在相邻两个第一已知合格裸片之间的间隙内填充封装材料220,以形成第一层第一芯片单元200;

129.步骤s706:在第一层第一芯片单元200上键合第一层中介层晶圆300;

130.步骤s708:将第一层中介层晶圆300的厚度减薄;在减薄后的第一层中介层晶圆上制作第二金属化结构;

131.步骤s710:重复进行步骤s704,将选取的多个第一已知合格裸片作为用于形成第

二层第一芯片单元200的多个第一已知合格裸片,将多个第一已知合格裸片键合于步骤s708形成的减薄后的第一层中介层晶圆300上,在相邻两个第一已知合格裸片之间的间隙内填充封装材料220,以形成第二层第一芯片单元200;

132.步骤s712:在第二层第一芯片单元200上键合第二层中介层晶圆300;

133.步骤s714:将第二层中介层晶圆300的厚度减薄;在减薄后的第二层中介层晶圆300上制作第二金属化结构;

134.步骤s716:提供多个第二晶圆,将多个第二晶圆键合以形成第二键合晶圆;切割第二键合晶圆,以形成多个第二单颗裸片,从多个第二单颗裸片中选取多个第二已知合格裸片;将多个第二已知合格裸片键合于第二层中介层晶圆300上,在相邻两个第二已知合格裸片之间的间隙内填充封装材料220,以形成第二芯片单元700。

135.第二方面,本实施例还提供了一种封装结构,该封装结构采用本实施例提供的封装结构的制作方法制备。

136.本实施例提供的封装结构,由于采用了本实施例提供的封装结构的制作方法制备,能够减小因第一芯片单元200翘曲带来的堆叠难度,使得chip on chip堆叠的层数更多,同时也提高了封装结构的产量和良率。

137.示例性的,参见图6所示,封装结构中的第一芯片单元200的数量为两个,图6所示的封装结构可以采用图7所示的封装结构的制作方法制备。

138.第三方面,本实施例还提供了一种封装结构,也可参考图2f和图6,包括:

139.初始晶圆100;

140.第一芯片单元200,第一芯片单元200位于初始晶圆100上;

141.中介层晶圆300,中介层晶圆300位于第一芯片单元200的远离初始晶圆100的一侧;

142.第二芯片单元700,第二芯片单元700位于中介层晶圆300的远离初始晶圆100的一侧;

143.其中,第一芯片单元包括多个间隔设置的第一已知合格裸片以及填充于相邻两个第一已知合格裸片之间的封装材料,第二芯片单元包括多个间隔设置的第二已知合格裸片以及填充于相邻两个第二已知合格裸片之间的封装材料。

144.本实施例提供的封装结构,通过将第一芯片单元200设置在初始晶圆100上,实现了chip on wafer堆叠,将第一芯片单元200重构成晶圆,由于中介层晶圆300位于第一芯片单元200的远离初始晶圆100的一侧,实现了wafer on wafer堆叠,提高了产量。由于中介层晶圆300能够对位于其下方的第一芯片单元200进行压持,在堆叠过程中,能够减小因第一芯片单元200翘曲带来的堆叠难度,从而能够实现更多层数的chip on chip堆叠。再在中介层晶圆300的远离初始晶圆100的一侧设置第二芯片单元700,即再次实现了chip on wafer堆叠,提高了封装结构的良率。

145.需要说明的是,第一芯片单元200与中介层晶圆300之间通过第一金属化结构连接。示例性的,第一金属化结构包括焊垫610,焊垫610位于第一芯片单元200的背面,即焊垫610位于第一芯片单元200的朝向中介层晶圆300的一侧。

146.中介层晶圆300与第二芯片单元700之间通过第二金属化结构连接。示例性的,第二金属化结构包括硅通孔620和焊垫610,硅通孔620设置于中介层晶圆300内,焊垫610位于

中介层晶圆300的朝向第二芯片单元700的一侧。

147.在一个实施例中,第一芯片单元200的数量为多个,多个第一芯片单元沿垂直于初始晶圆的表面的方向堆叠设置,多个第一芯片单元的远离初始晶圆的一侧均设置有中介层晶圆。

148.示例性的,参见图6所示,第一芯片单元200的数量为两个,每个第一芯片单元200的远离初始晶圆100的一侧均设置有中介层晶圆300,第二芯片单元700设置在与初始晶圆100的距离最远的中介层晶圆300上,所形成的结构如图6所示。

149.本实施例提供的封装结构包括多个第一芯片单元200和多个中介层晶圆300沿垂直于初始晶圆的表面的方向交替堆叠的结构,从而能够有效控制chip on chip的翘曲度,增加了堆叠层数,同时,提高了堆叠良率,也减少了封装的次数。

150.需要说明的是,当第一芯片单元200的数量为多个时,位于两个第一芯片单元200之间的中介层晶圆300与该中介层晶圆300两侧的第一芯片单元200均通过第一金属化结构连接。

151.需要说明的是,一种实施方式中,参见图2f所示,封装结构中的第一芯片单元200的数量也可以为一个。

152.在一个实施例中,中介层晶圆300的厚度不大于50μm。

153.中介层晶圆300的厚度过大,不利于形成硅通孔620,因此,本实施例中的中介层晶圆300的厚度不大于50μm,以增强多层芯片单元之间的导通性,从而改善封装结构的整体性能。

154.在一个实施例中,第一已知合格裸片和第二已知合格裸片均从切割键合晶圆所形成的多个单颗裸片中选取,其中,键合晶圆包括键合在一起的两个晶圆。

155.采用两个堆叠设置的晶圆键合形成键合晶圆,并切割形成多个单颗裸片,从多个单颗裸片中选取多个第一已知合格裸片和多个第二已知合格裸片,能够缓解wafer on wafer堆叠导致的良率降低太多的问题,同时也能够大幅提高产量。

156.综上,本实施例提供的封装结构的制作方法及封装结构,利用wafer on wafer的高产量优势以及翘曲度更易控制的原理,并结合chip on wafer的高良率优势,实现了更多层数的chip on chip堆叠,从而在增加堆叠层数的同时,提高了封装结构的堆叠良率和产量。

157.最后应说明的是:以上各实施例仅用以说明本公开的技术方案,而非对其限制;尽管参照前述各实施例对本公开进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本公开各实施例技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。