1.本公开有关于三维半导体装置与存储装置,且特别有关于使用栅极全环架构的三维半导体装置与存储装置。

背景技术:

2.目前对电子电路,特别是在半导体工艺中制成集成电路的电子电路,的常见需求为存储储存元件阵列。这些元件可提供为静态随机存取存储器(static random access memory,sram)单元(cell)以形成静态随机存取存储器。虽然静态随机存取存储器具有比动态随机存取存储器(dynamic random-access memory,dram)更快的存取时间,但每一静态随机存取存储器单元需要多个晶体管,因此静态随机存取存储器比动态随机存取存储器更加昂贵。例如,6t静态随机存取存储器单元包含六个晶体管。而且,比起动态随机存取存储器单元,静态随机存取存储器单元占据的面积大很多,导致静态随机存取存储器具有比动态随机存取存储器更小的密度。然而,由于可能需要先进的互补式金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)技术,生产小尺寸静态随机存取体单元是具有挑战性的。

技术实现要素:

3.本公开提供了一种三维(three-dimensional,3d)半导体装置、半导体装置的制造方法以及存储装置,例如是使用堆叠的垂直栅极全环(gate-all-around,gaa)晶体管架构以形成静态随机存取存储器单元结构。

4.本公开的一方面提供了一种于半导体装置。半导体装置包含半导体基板、沿着垂直方向垂直地堆叠于半导体基板上的多个导电层、以及多个晶体管;多个导电层包含依序堆叠在一起的第一导电层、第二导电层与第三导电层,多个晶体管包含在第一导电层中的第一晶体管与第二晶体管、及在第三导电层中的第三晶体管,每一晶体管包含第一端点(terminal)、第二端点与栅极端(gate terminal)。第一晶体管的第一端点、第二晶体管的第一端点与第三晶体管的第一端点导电地耦接(conductively coupled)至第二导电层中的第一导电节点(node)。

5.在一些实施例中,第一导电层与一三导电层由第一导电材料制成,且第二导电层由第二导电材料制成,第二导电材料不同于第一导电材料。

6.在一些实施例中,多个晶体管还包含第四晶体管、第五晶体管与第六晶体管,第四晶体管与第六晶体管在第一导电层中,第五晶体管在第三导电层中,第四晶体管的第一端点、第五晶体管的第一端点与第六晶体管的第一端点导电地耦接至第二导电层中的第二导电节点。

7.在一些实施例中,半导体装置还包含阶梯区(staircase region),阶梯区装配以使第一导电层、第二导电层与第三导电层分开为彼此电性绝缘(conductively insulated)的两部位(parts)。第一晶体管与第二晶体管可在第一导电层的第一部位,第四晶体管与第

六晶体管可在第一导电层的第二部位。第一导电节点可在第二导电层的第一部位,且第二导电节点可在第二导电层的第二部位。第三晶体管可在第三导电层的第一部位,且第五晶体管可在第三导电层的第二部位。

8.在一些实施例中,阶梯区包含彼此对称的第一阶梯子区(sub-region)与第二阶梯子区。半导体装置还包含:第一组穿孔(via)与第二组穿孔。第一组穿孔垂直地贯穿第一阶梯子区且分别耦接至第一导电层、第二导电层与第三导电层的多个第一部位上的多个导电接垫(pad)。第二组穿孔垂直地贯穿第二阶梯子区且分别耦接至第一导电层、第二导电层与第三导电层的多个第二部位上的多个导电接垫。

9.在一些实施例中,半导体装置还包含在第一导电层、第二导电层与第三导电层上的第一金属层。第一金属层中的第一导电线(conductive line)可装配以使第一导电节点导电地耦接至第一导电层中的第四晶体管的栅极端与第三导电层中的第五晶体管的栅极端,第一金属层中的第二导电线可装配以使第二导电节点导电地耦接至第一导电层中的第二晶体管的栅极端与第三导电层中的第三晶体管的栅极端。

10.在一些实施例中,第一导电层中的第一晶体管与第六晶体管的多个第二端点耦接至形成于第二金属层中的一对第一信号线(signal line),第一导电层中的第一晶体管与第六晶体管的多个栅极端耦接至形成于第三金属层中的第二信号线,且第一金属层、第二金属层与第三金属层在多个导电层上垂直地堆叠在一起。

11.在一些实施例中,第一导电线与第二导电线在第一金属层中彼此电性绝缘且沿着水平方向延伸,水平方向垂直于垂直方向。第一金属层中的第一导电线通过沿着垂直方向贯穿第一阶梯子区的第一组穿孔分别耦接至第一导电层中的第四晶体管的栅极端、第二导电层中的第一导电节点、以及第三导电层中的第五晶体管的栅极端。第一金属层中的第二导电线通过沿着垂直方向贯穿第二阶梯子区的第二组穿孔分别耦接至第一导电层中的第二晶体管的栅极端、第二导电层中的第二导电节点、以及第三导电层中的第三晶体管的栅极端。

12.在一些实施例中,半导体装置包含一对反相器(inverters),一对反相器包含第一反相器与第二反相器,第一反相器具有第一晶体管、第二晶体管与第三晶体管,第二反相器具有第四晶体管、第五晶体管与第六晶体管。第一晶体管和第六晶体管分别为第一反相器和第二反相器中的传送栅极晶体管(pass gate transistor),第二晶体管和第四晶体管分别为第一反相器和第二反相器中的上拉晶体管(pull up transistor),且第三晶体管和第五晶体管分别为第一反相器和第二反相器中的下拉晶体管(pull down transistor)。

13.在一些实施例中,第一导电层中的第二晶体管与第四晶体管的多个第二端点导电地耦接至第一供应电压(supply voltage),第三导电层中的第三晶体管与第五晶体管的多个第二端点导电地耦接至第二供应电压。

14.在一些实施例中,多个晶体管还包含在第三导电层中的另一第二晶体管、以及在第三导电层中的另一第四晶体管,另一第二晶体管共享第三晶体管的栅极端,另一第四晶体管共享第五晶体管的栅极端。

15.在一些实施例中,第一晶体管与第二晶体管的多个栅极端通过一第一绝缘狭缝(slit)彼此电性绝缘,第一绝缘狭缝沿着垂直方向延伸通过第一导电层且延伸至第二导电层上,第四晶体管与第六晶体管的多个栅极端通过第二绝缘狭缝彼此电性绝缘,第二绝缘

狭缝沿着垂直方向延伸通过第一导电层且延伸至第二导电层上。

16.在一些实施例中,半导体装置装配为6t静态随机存取存储器单元。6t静态随机存取存储器单元可耦接至栅极全环晶体管架构中的非易失性存储器单元。

17.在一些实施例中,第一晶体管与第三晶体管具有第一掺杂类型,第二晶体管具有第二掺杂类型,第一掺杂类型不同于第二掺杂类型。第一掺杂类型可为n型,且第二掺杂类型可为p型。

18.在一些实施例中,半导体基板包含具有第一掺杂类型的第一掺杂区与具有第二掺杂类型的第二掺杂区,第一掺杂区与第二掺杂区彼此电性绝缘,且半导体装置包含多个半导体柱(pillar),多个半导体柱延伸通过多个导电层且延伸至半导体基板上,且多个半导体柱包含延伸至第一掺杂区上的第一半导体柱与延伸至第二掺杂区上的第二半导体柱。

19.在一些实施例中,第一半导体柱与第二半导体柱皆被第一导电层与第三导电层中的栅极介电结构环绕,且第一半导体柱与第二半导体柱皆被第二导电层中的金属结构环绕。

20.在一些实施例中,第一半导体柱包含在多个导电层上的第一部分(portion)、以及被第二导电层中的金属结构环绕的第二部分,且第一半导体柱的第一部分与第二部分被掺杂为具有第一掺杂类型。在一些实施例中,第二半导体柱包含在多个导电层上的第三部分、以及被第二导电层中的金属结构环绕的第四部分,且第二半导体柱的第三部分与第四部分被掺杂为具有第二掺杂类型。

21.在一些实施例中,第一晶体管包含第一导电层的一第一部分、被第一导电层中的第一栅极介电结构环绕的第二半导体柱的第一部分、以及第一栅极介电结构,第二晶体管包含第一导电层的第二部分、被第一导电层中的第二栅极介电结构环绕的第一半导体柱的第一部分、以及第二栅极介电结构,且第三晶体管包含第三导电层的一部分、被第三导电层中的第三栅极介电结构环绕的第二半导体柱的第二部分、以及第三栅极介电结构。

22.在一些实施例中,半导体装置装配于相邻的多个导电狭缝之间,多个导电狭缝沿着垂直方向延伸通过多个导电层且延伸至半导体基板上。

23.本公开的另一方面的提供了一种半导体装置。半导体装置包含半导体基板、垂直地堆叠于半导体基板上的多个导电层、第一半导体柱、以及多个栅极介电结构;多个导电层包含依序堆叠在一起的底导电层、中间导电层与顶导电层;第一半导体柱垂直地贯穿底导电层、中间导电层与顶导电层至半导体基板上,第一半导体柱包含被底导电层环绕的第一底部、被中间导电层环绕的第一中间部、以及被顶导电层环绕的第一顶部;多个栅极介电结构包含被第一栅极介电结构与第二栅极介电结构,第一栅极介电结构被第一底部与底导电层环绕、第二栅极介电结构被第一顶部与顶导电层环绕。第一半导体柱的第一中间部导电地耦接至中间导电层。

24.在一些实施例中,半导体装置还包含第二半导体柱,第二半导体柱垂直地贯穿多个导电层至半导体基板上,第二半导体柱包含被底导电层环绕的第二底部、被中间导电层环绕的第二中间部、以及被顶导电层环绕的第二顶部。在一些实施例中,多个栅极介电结构包含被第二底部与底导电层环绕的第三栅极介电结构、以及被第二顶部与顶导电层环绕的第四栅极介电结构。在一些实施例中,第二半导体柱的第二中间部导电地耦接至中间导电层。

25.在一些实施例中,半导体基板包含第一掺杂类型区与第二掺杂类型区,且第一半导体柱垂直地延伸至第一掺杂类型区上,且第二半导体柱垂直地延伸至第二掺杂类型区上。

26.在一些实施例中,半导体装置还包含在中间导电层中的多个金属结构。在一些实施例中,多个金属结构包含第一金属结构与第二金属结构,第一金属结构被第一半导体柱的第一中间部与中间导电层环绕,第二金属结构被第二半导体柱的第二中间部与中间导电层环绕。

27.在一些实施例中,底导电层包含:第一导电部与第二导电部,第一导电部环绕第一栅极介电结构与第一半导体柱,第二导电部环绕第三栅极介电结构与第二半导体柱,第一导电部与第二导电部在第一栅极介电结构与第二栅极介电结构之间至少部分地彼此重叠。在一些实施例中,顶导电层包含第三导电部与第四导电部,第三导电部环绕第二栅极介电结构与第一半导体柱,第四导电部环绕第四栅极介电结构与第二半导体柱,第三导电部与第四导电部在第三栅极介电结构与第四栅极介电结构之间彼此分离且绝缘。

28.在一些实施例中,半导体装置还包含第三半导体柱,第三半导体柱垂直地贯穿多个导电层至半导体基板上,第三半导体柱包含在底导电层中的第三底部、被中间导电层环绕的第三中间部、以及被顶导电层环绕的第三顶部,其中多个栅极介电结构包含第五栅极介电结构与第六栅极介电结构,第五栅极介电结构被第三底部与底导电层环绕,第六栅极介电结构被第三顶部与顶导电层环绕,且其中第三半导体柱的第三中间部导电地耦接至中间导电层。

29.在一些实施例中,半导体装置还包含第四半导体柱,第四半导体柱垂直地贯穿多个导电层至半导体基板上,第四半导体柱包含在底导电层中的第四底部、被中间导电层环绕的第四中间部、以及被顶导电层环绕的第四顶部,其中多个栅极介电结构包含第七栅极介电结构与第八栅极介电结构,第七栅极介电结构被第四底部与底导电层环绕,第八栅极介电结构被第四顶部与顶导电层环绕,且其中第四半导体柱的第四中间部导电地耦接至中间导电层。

30.在一些实施例中,半导体装置还包含在多个导电层上的金属层。中间导电层包含第一部分与第二部分,第一半导体柱与第二半导体柱贯穿第一部分,第三半导体柱与第四半导体柱贯穿第二部分,第一部分与第二部分彼此绝缘。金属层中的第一导电线装配以使中间导电层的第一部分导电地耦接至顶导电层中环绕第四半导体柱与第八栅极介电结构的一部分与底导电层中环绕第三半导体柱与第五栅极介电结构的一部分。金属层中的二导电线装配以使中间导电层的第二部分导电地耦接至顶导电层中环绕第一半导体柱与第三栅极介电结构的一部分与底导电层中环绕第二半导体柱与第二栅极介电结构的一部分。

31.本公开的另一方面的提供了一种存储装置。存储装置包含在半导体基板上的多个存储器单元、以及形成于多个存储器单元上的金属层。多个存储器单元的每一者包含多个导电层与多个晶体管,多个导电层垂直地堆叠在半导体基板上,多个导电层包含依序堆叠在一起的第一导电层、第二导电层与第三导电层;多个晶体管包含第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管与第六晶体管,第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管与第六晶体管的每一个包含第一端点、第二端点与栅极端。第一晶体管、第二晶体管、第四晶体管和第六晶体管在第一导电层中,第三晶体管和第五晶

体管在第三导电层中,且其中第一晶体管的第一端点、第二晶体管的第一端点和第三晶体管的第一端点导电地耦接至第二导电层中的第一导电节点,第四晶体管的第一端点、第五晶体管的第一端点和第六晶体管的第一端点导电地耦接至第二导电层中的第二导电节点。金属层中的第一导电线装配以使第一导电节点导电地耦接至第一导电层中的第四晶体管的栅极端与第三导电层中的第五晶体管的栅极端。金属层中的第二导电线装配以使第二导电节点导电地耦接至第一导电层中的第二晶体管的栅极端与第三导电层中的第三晶体管的栅极端。

32.本公开的另一方面提供了一种半导体装置。半导体装置包含基板与配置于基板上的垂直堆叠。垂直堆叠包含底导电层、在底导电层上的中间导电层、以及在中间导电层上的顶导电层。半导体装置还包含第一半导体柱,第一半导体柱垂直地贯穿垂直堆叠且包含被底导电层环绕的第一底部、被中间导电层环绕的第一中间部、以及被顶导电层环绕的第一顶部。半导体装置还包含多个栅极介电结构,多个栅极介电结构位于第一底部与底导电层之间且位于第一顶部与顶导电层之间。第一中间部导电地耦接(或电性连接)至中间导电层。

33.在一些实施例中,顶导电层包含彼此分离的第一顶片段(segment)、第二顶片段、第三顶片段与第四顶片段。中间导电层包含彼此分离的第一中间片段与第二中间片段。底导电层包含彼此分离的第一底片段与第二底片段。第一半导体柱的第一顶部被顶导电层的第一顶片段环绕,第一半导体柱的第一中间部被中间导电层的第一中间片段环绕,且第一半导体柱的第一底部被底导电层的第一底片段环绕。

34.在一些实施例中,半导体装置还包含垂直地贯穿垂直堆叠的第二半导体柱。第二半导体柱包含被底导电层的第一底片段环绕的第二底部、被中间导电层环绕的第二中间部、以及被顶导电层的第二顶片段环绕的第二顶部。多个栅极介电结构位于第二半导体柱的第二底部与底导电层的第一底片段之间,且位于第二半导体柱的第二顶部与顶导电层的第二顶片段之间。第二半导体柱的第二中间部导电地耦接至中间导电层的第一中间片段。

35.在一些实施例中,基板包含第一掺杂类型井区(例如具有第一掺杂类型的第一掺杂区)与第二掺杂类型井区(例如具有第二掺杂类型的第二掺杂区),第一半导体柱导电地耦接至第一掺杂类型井区,第二半导体柱导电地耦接至第二掺杂类型井区。

36.在一些实施例中,半导体装置还包含第三半导体柱,第三半导体柱垂直地贯穿垂直堆叠且导电地耦接至第一掺杂类型井区。第三半导体柱包含被底导电层的第二底片段环绕的第三底部、被中间导电层的第二中间片段环绕的第三中间部、以及被顶导电层的第三顶片段环绕的第三顶部。多个栅极介电结构位于第三半导体柱的第三底部与底导电层的第二底片段之间,且位于第三半导体柱的第三顶部与顶导电层的第三顶片段之间;第三半导体柱的第三中间部导电地耦接至中间导电层的第二中间片段。

37.在一些实施例中,半导体装置还包含第四半导体柱,第四半导体柱垂直地贯穿该垂直堆叠且导电地耦接至第二掺杂类型井区。该第四导体柱包含被底导电层的第二底片段环绕的第四底部、被中间导电层的第二中间片段环绕的第四中间部、以及被顶导电层的第四顶片段环绕的第四顶部。多个栅极介电结构位于第四半导体柱的第四底部与底导电层的第二底片段之间,且位于第四半导体柱的第四顶部与顶导电层的第四顶片段之间。第四半导体柱的第四中间部导电地耦接至中间导电层的第二中间片段。

38.在一些实施例中,半导体装置还包含布线层(wiring layer),布线层包含第一布线连接器,第一布线连接器导电地耦接至底导电层的第一底片段、中间导电层的第二中间片段和顶导电层的第二顶片段。

39.在一些实施例中,布线层包含第二布线连接器,第二布线连接器导电地耦接至底导电层的第二底片段、中间导电层的第一中间片段和顶导电层的第四顶片段。

40.在一些实施例中,半导体装置还包含多个金属硅化物(metal silicide)结构,多个金属硅化物结构位于第一半导体柱的第一中间部和中间导电层的第一中间片段的交叉处、位于第二半导体柱的第二中间部和中间导电层的第一中间片段之间、位于第三半导体柱的第三中间部和中间导电层的第二中间片段之间、且位于第四半导体柱的第四中间部和中间导电层的第二中间片段之间。

41.在一些实施例中,第一半导体柱导电地耦接至第一信号线,且第三半导体柱导电地耦接至第二信号线,第二半导体柱与第四半导体柱导电地耦接至耦接供应电压vcc的电源线(power line)。

42.在一些实施例中,半导体装置形成6t(六晶体管)静态随机存取存储器装置。在一些实施例中,半导体装置的单元尺寸小于或等于0.032平方微米(μm2)。

43.本公开的另一方面的提供了根据上述的半导体装置的制造方法。

44.本公开的另一方面的提供了一种半导体装置,半导体装置包含6t静态随机存取存储器单元与快闪存储器单元。6t静态随机存取存储器单元与快闪存储器单元皆为栅极全环架构。

45.半导体装置的个别元件可根据上述实施例且可为任意合理的组合。

46.一或更多的所公开实施方式的多个细节阐述于附图和以下叙述中。通过叙述、附图与权利要求书范围,本公开的其他特征、方面与益处将是显而易见的。

附图说明

47.图1为包含存储器的系统的示例;

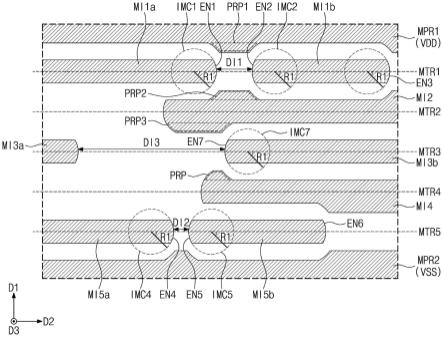

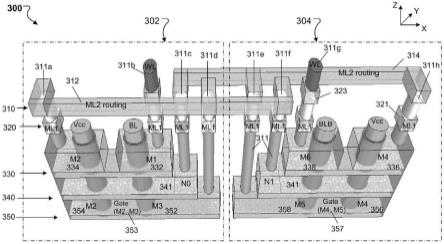

48.图2为示例6t静态随机存取存储器单元电路;

49.图3a-3d为示例三维静态随机存取存储器单元结构;

50.图4a-4c为使用三维静态随机存取存储器单元结构的示例静态随机存取存储器装置;

51.图5a-5n为用以制造三维静态随机存取存储器单元结构的方法的多个示例步骤;

52.图6为用以形成三维静态随机存取存储器单元结构的方法示例的流程图;及

53.图7为整合示例静态随机存取存储器单元结构与示例快闪存储器单元结构的半导体装置。

54.多个附图中相同元件符号与名称代表相同元件。应理解的是,图式示出的各种示例性实施方式仅为说明性表示且不一定依比例绘制。

55.附图标记说明

56.100:系统

57.110:装置

58.112:装置控制器

59.113:处理器

60.114:内部存储器

61.116:存储器

62.120:主机

63.200:电路

64.210,220:反相器

65.212,226,332,338,m1,m6:传送栅极晶体管

66.214,222,334,336,354,356,m2,m4:上拉晶体管

67.216,224,352,358,m3,m5:下拉晶体管

68.300:静态随机存取存储器单元结构

69.301:狭缝

70.302:第一反相器

71.303:绝缘材料

72.304:第二反相器

73.306,508:阶梯区

74.310,320,ml1,ml2:金属层

75.311,311a~311h:穿孔

76.312,314:导电布线

77.313a,313b,313c,313d:半导体柱

78.321:中间导电接垫

79.322,324:顶部

80.323:导电接垫

81.330,340,350:层

82.331,341,351:导电材料

83.333:栅极介电结构

84.343:栅极金属结构

85.353,357:栅极端

86.362:p 区

87.363:浅沟道隔离结构

88.364:n 区

89.400:静态随机存取存储器装置

90.401,500:基板

91.402:字线

92.410,410-1,410-2,410-3:区块

93.411:p型掺杂区

94.412:n型掺杂区

95.413,503:浅沟道隔离结构

96.414:接地

97.420:静态随机存取存储器单元

98.430,512:狭缝

99.431:导电线

100.432,438:供应电压线

101.434,436:位线

102.501:p 硅区

103.502:n 硅区

104.504,505,506:层

105.507:绝缘层

106.509:孔洞

107.510:绝缘层

108.511:半导体柱

109.513,522,524:开放空间

110.514:第一屏蔽

111.515,519:p连接部

112.516:第二屏蔽

113.517,520:n连接部

114.518:导电层

115.521:切口

116.523:栅极氧化物层

117.526,528:导电层

118.530:p 连接部

119.532:n 连接部

120.540:成型结构

121.600:方法

122.602,604,606,608,610,612:步骤

123.700:半导体装置

124.701:接地线

125.702:电源线

126.703:字线

127.704:储存线

128.705:操作线

129.706:重新呼叫线

130.707:电源线

131.708,709,bl,blb:位线

132.710:静态随机存取存储器单元结构

133.720:快闪存储器单元结构

134.722,724:三栅极晶体管结构

135.c0,c1,n0,n1:节点

136.t1,t3,t6:金属氧化物硅晶体管

137.t2,t4,t5:硅-氧化硅-氮化硅-氧化物-硅晶体管

138.vcc:供应电压

139.vcs:供应电压

140.vss:第二供应电压

141.wl:字线

142.x,y,z:方向

具体实施方式

143.在本公开中,使用6t静态随机存取存储器单元作为示例以说明多个特征,其并非限制实施例或随附权利要求书范围。本公开的多个实施方式可进一步扩展为具有多于六个晶体管的静态随机存取存储器单元,例如8t静态随机存取存储器单元、10t静态随机存取存储器单元、以及任意内容可定址存储器(content addressable memory,cam)单元。

144.实现于本公开的技术可提供具有小尺寸但高性能的静态随机存取存储器单元。技术使用堆叠的垂直栅极全环晶体管结构,其不仅可大幅节省晶体管面积,而且可大幅节省接触面积(contact areas),从而降低静态随机存取存储器单元面积。此外,单元面积缩小通常受限于非主动阶梯接触区域。这代表一旦工艺视窗(process window)控制(例如阶梯设计规则或接触规则)改良,静态随机存取存储器单元尺寸可进一步缩小至远小于先进的互补式金属氧化物半导体可提供的尺寸,而不会出现互补式金属氧化物半导体晶体管问题。例如,6t静态随机存取存储器单元尺寸可缩小为小于0.032平方微米(等同于n7节点)或甚至缩小为0.006平方微米(等同于n1节点)。

145.技术可提供高性能的静态随机存取存储器。例如,静态随机存取存储器可达成低的每位能量(energy per bit)(例如在单一6t静态随机存取存储器单元中~10fj/bit)、低的操作电压(例如小于等于1v)、无限的耐久性(endurance)、以及存取时间快速(~ns)。静态随机存取存储器可实现为具有合理的晶体管开关比(on/off ratio)且不具有可能难以预测的开发中的不稳定新材料(例如用于其他存储器)。静态随机存取存储器亦可达成非常低的原始位错误率(raw bit error rate,rber)并具有良好控制的晶体管临界电压vth,例如使用栅极全环架构。静态随机存取存储器可装配以进行先进运算以产生~pb/s频宽。静态随机存取存储器亦可作为暂存器或工作数据储存器,例如在用于处理器的快取存储器中。举例而言,使用系统单晶片(system on a chip,soc)设计可整合静态随机存取存储器和一或更多的处理器核心(例如微控制器或微处理器)。处理器核心可和静态随机存取存储器单元的一阶(level one,l1)快取存储器一起配置以使非常快的处理操作成为可能,静态随机存取存储器单元的一阶快取存储器配置于或相邻于半导体基板上的处理器。

146.实现于本公开的技术可使用现行制造技术制造静态随机存取存储器单元,其可避免缩小静态随机存取存储器单元的特征引起的问题,例如接触电阻(contact resistance)增加、接触孔洞尺寸下降、以及光刻工艺(photolithography)中的误差容忍度下降。技术亦可减少光刻工艺所需的多个图案化步骤,以降低成本并改善工艺的量产能力(throughput)。

147.实现于本公开的技术可应用于包含多个晶体管或其他半导体元件(例如储存元件或电路)的任意其他结构。实现于本公开的技术可应用于各种存储器类型,例如单阶储存单

元(single-level cell,slc)装置、多阶储存单元(multi-level cell,mlc)装置,多阶储存单元装置例如是二阶储存单元(2-level cell)装置、三阶储存单元(triple-level cell,tlc)装置或四阶储存单元(quad-level cell,qlc)装置。技术可应用于各种维度的存储装置或系统,例如三维存储装置或系统。技术可应用于各种类型的易失性或非易失性存储装置或系统或其任意合适的组合。例如,静态随机存取存储器可和非易失性存储装置(例如快闪存储装置)整合,其中非易失性储存单元结构(例如电子擦除式可复写只读存储器(electrically erasable programmable read-only memory,eeprom)单元结构)可和使用栅极全环架构的静态随机存取存储器单元结构整合于相同或相似的制造流程中。

148.额外地或可替代地,技术可应用于各种类型的装置与系统,例如安全数字卡(secure digital cards,sd cards)、嵌入式多媒体卡(embedded multimedia cards,emmc)或固态硬盘(solid-state drives,ssds)、嵌入式系统、媒体播放器、行动装置等。

149.图1为系统100的示例。系统100包含装置110与主机120。装置110包含装置控制器112与存储器116。装置控制器112包含处理器113与内部存储器114。在一些实施方式中,装置110包含耦接至装置控制器112的多个存储器116。

150.在一些实施方式中,装置110为储存装置。例如,装置110可为嵌入式多媒体卡、安全数字卡、固态硬盘或一些其他合适的储存装置。在一些实施方式中,装置110为智能型手表、数字相机或媒体播放器。在一些实施方式中,装置110为耦接至主机120的客户端装置(client device)。例如,装置110为数字相机或媒体播放器中的安全数字卡,数字相机或媒体播放器为主机120。

151.装置控制器112为通用微处理器(general-purpose microprocessor)或特殊应用微控制器(application-specific microcontroller)。在一些实施方式中,装置控制器112为用于装置110的存储器控制器。以下内容描述各种技术,这些技术是基于装置控制器112为存储器控制器的实施方式。然而,以下内容描述的多种技术亦可应用于装置控制器112为不同于存储器控制器的其他类型控制器的实施方式。

152.处理器113装配以执行多个指令(instruction)与处理数据。多个指令包含固件指令和/或在辅助存储器(secondary memory)中储存为固件编码和/或其他程序编码的其他程序指令。数据包含对应于固件和/或由处理器执行的其他程序的程序数据、以及其他合适的数据。在一些实施方式中,处理器113为通用微处理器或特殊应用微控制器。处理器113也被称为中央处理器(central processing unit,cpu)。

153.处理器113从内部存储器114存取多个指令与数据。在一些实施方式中,内部存储器114为静态随机存取存储器或动态随机存取存储器。例如,在一些实施方式中,当装置110为嵌入式多媒体卡、安全数字卡或智能型手表,内部存储器114为静态随机存取存储器。静态随机存取存储器可由例如图3a-3d为静态随机存取存储器单元制成,且可包含例如图4a-4c为静态随机存取存储器单元阵列。在一些实施方式中,当装置110为数字相机或媒体播放器,内部存储器114为动态随机存取存储器。

154.在一些实施方式中,内部存储器为被包含于装置控制器112的快取存储器,如图1所示。内部存储器114储存多个指令编码和/或在运行期间处理器113请求的数据,多个指令编码对应于由处理器113执行的多个指令。

155.装置控制器112将指令编码和/或数据从存储器116传送至内部存储器114。存储器

116可为半导体装置。在一些实施方式中,存储器116为装配以长期储存多个指令和/或数据的非易失性存储器,例如nand快闪存储装置或一些其他合适的非易失性存储装置。在一些实施方式中,存储器116为nand快闪存储装置,装置110为例如快闪存储卡的快闪存储装置,且装置控制器112为nand快闪控制器。例如,在一些实施方式中,当装置110为嵌入式多媒体卡或安全数字卡,存储器116为nand快闪存储器;在一些实施方式中,当装置110为数字相机,存储器116为安全数字卡;在一些实施方式中,当装置110为媒体播放器,存储器116为硬盘(hard disk)。在一些实施方式中,存储器116为装配为快取存储器的易失性存储器。在一些实施方式中,存储器116包含非易失性存储单元阵列与易失性存储单元阵列。

156.图2为6t静态随机存取存储器单元的示例电路200。电路200具有6t配置,6t配置包含配置于一对反相器210和220中的六个晶体管,每一反相器包含三个晶体管。

157.如图2所示,一对传送栅极晶体管212、226(标示为m1和m6)使一对位线bl和blb分别耦接至节点n0和n1。传送栅极晶体管m1和m6可由金属氧化物硅(metal-oxide-silicon,mos)晶体管形成。在此示例中,传送栅极晶体管m1和m6可实现为n型金属氧化物硅晶体管,例如nmos晶体管。图中的正的供应电压vcc(和vcs)可为0.3v至3.0v或更多,取决于工艺技术。上拉晶体管214、222(标示为m2和m4)形成为p型晶体管(例如pmos晶体管),且依据静态随机存取存储器单元的状态使正的供应电压vcc耦接至一或其他数据节点。图中的第二供应电压vss,例如负电压或接地电压,通过下拉晶体管216、224(标示为m3和m5)耦接至多个数据节点。

158.两个下拉晶体管m3和m5使第二供应电压vss耦接至一或其他节点n0和n1,取决于储存于静态随机存取存储器单元中的数据状态。静态随机存取存储器单元为闩锁器(latch),只要供应电力足以正确操作电路,闩锁器可无限期地保持其数据状态。包含上拉晶体管m2与下拉晶体管m3的反相器210、以及包含上拉晶体管m4与下拉晶体管m5的反相器220为交叉耦接的,且操作以连续加强节点no和n1上的储存电荷。例如,如图2所示,反相器210中的节点n0耦接至反相器220中的节点c1,而反相器220中的节点n1耦接至反相器210中的节点c0。两个节点n0和n1彼此反相(inverted)。当节点n0为逻辑“1”,例如处于高电压,此时节点n1为逻辑“0”,例如处于低电压,反之亦然。

159.当静态随机存取存储器单元被写入,互补写入数据信号被置于位线对bl和blb上。字线(wl)上的正控制信号耦接至传送栅极晶体管m1和m6的栅极。上拉晶体管m2、下拉晶体管m3、上拉晶体管m4、下拉晶体管m5、以及传送栅极晶体管m1和m6装配以使位在线的写入信息可复写节点n0和n1的储存数据,从而使静态随机存取存储器位单元(bit cell)写入所需状态。

160.当静态随机存取存储器单元被读取,正电压被置于字线wl上,传送栅极晶体管m1和m6使位线bl和blb耦接至节点n0和n1且从节点n0和n1接收数据。和动态存储器单元或动态随机存取存储器单元不同的是,静态随机存取存储器单元在读取期间不会遗失其储存的状态,因此在读取之后不需要“回写(write back)”操作。

161.位线bl和blb形成一对互补的数据线(data line)。成对的数据线可耦接至差动感测放大器(differential sense amplifier),且从静态随机存取存储器单元读取的差分电压(differential voltage)可被感测与放大。接着,可将处于逻辑电平电压(logic level voltage)的放大的感测信号作为读取数据输出至装置中的其他逻辑电路。

162.如同以下更详细讨论的,图2的静态随机存取存储器单元可形成为三维结构,例如使用堆叠的垂直栅极全环晶体管架构,其可大幅降低静态随机存取存储器单元的尺寸。

163.图3a-3d为示例三维静态随机存取存储器单元结构300。静态随机存取存储器单元结构300可实现为静态随机存取存储器单元。静态随机存取存储器单元结构300对应于图2的电路200。图3a-3b示出三维静态随机存取存储器单元结构300的透视图。图3c示出三维静态随机存取存储器单元结构300的剖面图。图3d示出三维静态随机存取存储器单元结构300的俯视图。

164.相似于图2中的电路200,静态随机存取存储器单元结构300包含一对反相器,一对反相器包含第一反相器302与第二反相器304。第一反相器302包含传送栅极晶体管m1 332(例如图2的传送栅极晶体管m1 212)、上拉晶体管m2 334(例如图2的上拉晶体管m2 214)、以及下拉晶体管m3 352(例如图2的下拉晶体管m3 216)。第二反相器304包含传送栅极晶体管m6 338(例如图2的传送栅极晶体管m6 226)、上拉晶体管m4 336(例如图2的上拉晶体管m4 222)、以及下拉晶体管m5 358(例如图2的下拉晶体管m5 224)。在一些示例中,传送栅极晶体管m1、下拉晶体管m3、下拉晶体管m5、传送栅极晶体管m6为n型晶体管,例如nmos晶体管,而上拉晶体管m2、上拉晶体管m4为p型晶体管,例如pmos晶体管。

165.由于nmos晶体管可达成比pmos晶体管更高的电流,可能会发生nmos晶体管与pmos晶体管之间的不匹配(mismatch),例如下拉晶体管m3 352与上拉晶体管m2 334之间或下拉晶体管m5 358与上拉晶体管m4 336之间。如图3a-3c所示,第一反相器302还包含第二上拉晶体管m2 354,且第二反相器304还包含第二上拉晶体管m4 356。两个上拉晶体管(例如m2 334和354或m4 336和356)可装配为并联连接,以获得比单一晶体管(例如m2 or m4)高两倍的电流。通过这样的方式,nmos晶体管与pmos晶体管之间的不匹配可被减少或最小化。

166.第一反相器302、第二反相器304交叉耦接于导电的节点n0和n1(例如图2的节点n0和n1)。例如,如图3c所示,第一反相器302中的节点n0通过导电布线314耦接至第二反相器304中的节点c1(例如图2的节点c1),而第二反相器304中的节点n1通过导电布线312耦接至第一反相器302中的节点c0(例如图2的节点c0)。

167.在一些实施方式中,传送栅极晶体管m1 332、m6 338的源极端装配以分别耦接至一对位线bl和blb。传送栅极晶体管m1 332、m6 338的栅极端可装配以分别耦接至字线,且可耦接至相同字线,例如如图4a-4b所示。传送栅极晶体管m1 332、上拉晶体管m2 334、上拉晶体管m2 354、下拉晶体管m3 352的汲极端耦接至节点n0。上拉晶体管m2 334、354、m4 336、356的源极端耦接至供应电压vcc或vcs。下拉晶体管m3 352、m5 358的源极端耦接至接地(例如如图3c或图4b所示)。上拉晶体管m2 354与下拉晶体管m3 352共享相同栅极端353。上拉晶体管m4 356与下拉晶体管m5 358共享相同栅极端357。

168.如图3a-3c所示,静态随机存取存储器单元结构300可形成为层330、340、350的垂直堆叠,层330、340、350依序配置于基板360上,例如沿着z方向。堆叠的层330、340、350可为导电层,每一个层330、340、350可包含导电材料331、341、351。导电材料331和351可相同于或不同于导电材料341。在一些示例中,导电材料331和351由钨(tungsten,w)制成,且导电材料341由钛(titanium,ti)制成。堆叠的层330、340、350可通过绝缘材料303制成的绝缘层彼此电性绝缘,绝缘材料303可例如是介电材料,例如氧化硅(silicon oxide)(或可简化为氧化物或ox)。第一反相器302和第二反相器304亦可通过绝缘材料303而彼此分离。

169.基板360可包含任意下层材料或装置、电路、外延层或半导体可形成于其上的材料。基板360可包含多个层,多个层可在半导体装置的之下或甚至形成半导体装置的基底层。基板360可包含硅(silicon)、掺杂硅(doped silicon)、锗(germanium)、硅锗(silicon germanium)、半导体化合物或其他半导体材料中的一者或任意组合。在一些示例中,如图3c所示,基板360包含三个掺杂(或注入)区,两个p 区362与例如沿着x方向在两个p 区之间的n 区364。浅沟道隔离结构(shallow trench insulation,sti)363使相邻的掺杂区电性绝缘,浅沟道隔离结构由绝缘材料制成,例如氧化物。

170.静态随机存取存储器单元结构300可例如沿着x方向形成于两相邻的导电的狭缝301。也就是说,狭缝301使相邻的静态随机存取存储器单元分开。导电的狭缝301可垂直地(例如沿着z方向)贯穿多个层至基板360上,例如在p 区362上。多个狭缝301导电地耦接至电源供应器,例如供应电压vcc。p型晶体管m2 334、354、m4 336、356可导电地耦接至多个狭缝301,以例如在源极端接收供应电压vcc。形成于静态随机存取存储器单元结构300中的多个晶体管m1至m6通过绝缘材料303而和多个狭缝301绝缘。

171.静态随机存取存储器单元结构300包含垂直地贯穿层330、层340、层350的垂直堆叠至基板360上的多个半导体柱,例如半导体柱313a、313b、313c、313d(通常被称为多个半导体柱313,且被单独称为半导体柱313)。半导体柱313可被半导体材料填充,半导体材料例如是多晶硅或外延成长制成的硅(或外延硅)。在一些实施例中,半导体柱313a、313d单独耦接至p 区362,且装配以形成p连接部(junction)和/或p型晶体管m2 334、354。半导体柱313b、313c耦接至n 区364,且装配以形成n连接部和/或n型晶体管m1 332、m3 352、m6 338和m5 358。

172.如图3c所示,每一半导体柱313被导电的层330、350中的栅极介电结构333(例如栅极氧化物(gox))环绕,且被导电层340中的栅极金属结构343(例如硅化物(silicide)或锗化物(germanide))环绕。在一些实施例中,导电层340包含装配为第一反相器302中的节点n0的第一部分与装配为第二反相器304中的节点n1的第二部分。导电层340的第一部分与第二部分通过绝缘材料303而彼此分离与彼此绝缘。

173.半导体柱313a、313d包含在导电层340中的中间部分,装配为p连接部,p连接部可由p型材料制成,例如如图5h所示。半导体柱313a、313d还包含在导电的层330上的顶部322。顶部322装配为p连接部,p连接部可由p型材料制成,例如如图5n所示。相似地,半导体柱313b、313c包含导电层340中的中间部分,且中间部分装配为n连接部,n连接部可由n型材料制成,例如如图5i所示。半导体柱313b、313c还包含在导电的层330上的顶部324,且顶部324装配为n连接部,n连接部可由n型材料制成,例如如图5n所示。如上所述,n连接部装配以形成n型晶体管m1、m3、m5、m6,且p连接部装配以形成p型晶体管m2、m4。在导电的层330中,p型晶体管m2、m4通过绝缘材料303而和n型晶体管m1、m6绝缘。在导电层350中,p型晶体管m2和n型晶体管m3共享相同栅极端353,且p型晶体管m4和n型晶体管m5共享相同栅极端357。栅极端353和357可由导电材料制成,例如金属钨。

174.如图3a、3b、3d所示(且进一步示出于图4c),静态随机存取存储器单元结构300中的多个元件通过多个穿孔(或通孔)311a~311h(通常被称为多个穿孔311,且被单独称为穿孔311)导电地连接,多个穿孔311a~311h通过层330、340、350的垂直堆叠上的不同金属层ml1 320、ml2 310而连接。

175.如上所述,第一反相器302、第二反相器304交叉耦接于节点n0和n1。第二反相器304中的节点n1通过对应穿孔311f、311d和311a导电地耦接至第一反相器302中的节点c0、n型晶体管m3 352的栅极端、以及p型晶体管m2 334、354的栅极端,穿孔311f、311d和311a在金属层ml2 310中以导电布线312导电地连接。相似地,第一反相器302中的节点n0通过对应穿孔311c、311e和311h导电地耦接至第二反相器304中的节点c1、n型晶体管m5 358的栅极端、以及p型晶体管m4 336、356的栅极端,穿孔311c、311e和311h在金属层ml2 310中以导电布线314导电地连接。为了便于连接,如图3a-3c所示,阶梯区306形成于第一反相器302、第二反相器304之间,其中穿孔311b、311c、311d、311e、311f、311g通过垂直地贯穿填充于阶梯区306的绝缘材料303至对应的层330、340、350来形成。如图3a、3d所示,用于静态随机存取存储器单元结构300的多个穿孔311可例如沿着x方向配置于相同列(row)中。

176.如图3a-3c所示,第一反相器302、第二反相器304彼此对称,例如沿着x方向上的中线或沿着xy平面上的中间层。导电的层330、340、350的堆叠可在阶梯区306中形成两个对称阶梯子区,例如沿着相同中线或相同中间层,两个对称阶梯子区分别用于第一反相器302、第二反相器304。穿孔311b、311c、311d形成于用于第一反相器302的阶梯子区中,且穿孔311e、311f、311g形成于用于第二反相器304的阶梯子区中。

177.如图3a所示(且进一步示出于图4a-4b),传送栅极晶体管m1 332、m6 338的源极端分别耦接至形成于金属层ml1 320中的一对位线bl、blb。每一穿孔311在金属层ml1 320中电性绝缘,且在金属层ml1 320中导电地连接至金属层ml1 320中的中间导电接垫321(例如金属接垫)。在一些实施例中,如图3a所示(且进一步示出于图4a-4b),第三金属层可形成于金属层ml2 310上,其中字线(在图4a-4b中标示为402)可耦接至静态随机存取存储器单元结构300中的传送栅极晶体管m1 332、m6 338的栅极端。如图3a-3b所示,穿孔311b、311g可和导电布线312电性绝缘,但可通过中间导电接垫323(例如金属接垫)导电地连接金属层ml2 310。连接供应电压vcc和/或位线bl和blb的第一电源线可形成于金属层ml1 320中。连接第二供应电压vss(例如接地)的第二电源线可形成于金属层ml1 320中或形成于方向不同于金属层ml1 320的金属层中。跨越整个静态随机存取存储器单元结构300的多条电源线可形成于第三金属层中或更高的金属层中。

178.静态随机存取存储器单元结构300可缩小为小尺寸。在一些示例中,静态随机存取存储器单元结构300具有100纳米(nm)量级的长度(例如沿着x方向),例如在100纳米至1000纳米的范围内,且具有10纳米量级的宽度(例如沿着y方向),例如在10纳米至100纳米的范围内。在一示例中,静态随机存取存储器单元结构300具有长度150纳米、宽度40纳米与面积0.006平方微米的尺寸。在另一示例中,静态随机存取存储器单元结构300具有长度400纳米、宽度80纳米与面积0.032平方微米的尺寸。每一导电的层,例如330、340、350,可具有20纳米的厚度(例如沿着z方向)。相邻导电层之间的空间可为10纳米。垂直半导体柱,例如313,可具有30纳米的直径。栅极介电结构,例如333,可具有1纳米的厚度(例如沿着x方向)。在一些示例中,相较于上述示例,静态随机存取存储器单元结构300中的元件的尺寸或厚度(例如导电的层330、340、350的厚度、或者静态随机存取存储器单元结构300的长度和/或宽度)可在10%的范围内调整。

179.图4a-4c为使用多个三维静态随机存取存储器单元420的示例静态随机存取存储器装置400。三维静态随机存取存储器单元420可具有和图3a-3d的静态随机存取存储器单

元结构300相同(或实质相似)的结构。

180.如图4a所示,静态随机存取存储器装置400包含沿着x方向和y方向配置的三维静态随机存取存储器单元420的阵列。沿着x方向,静态随机存取存储器装置400可包含多个区块(sections)410-1、410-2、410-3(通常被称为多个区块410,且被单独称为区块410)。如图4b和4c所示,每一区块410包含沿着y方向配置的多个三维静态随机存取存储器单元420。

181.区块410可形成于基板401上(例如图3c的基板360)。基板401可包含多个p型掺杂区411与介于两个p型掺杂区之间的n型掺杂区412。浅沟道隔离结构413(例如图3c的浅沟道隔离结构363)可形成于p型掺杂区411与n型掺杂区412之间。这些掺杂区可沿着y方向延伸以用于区块410中的静态随机存取存储器单元420。n型掺杂区412耦接至接地414,接地414沉积于n型掺杂区412上。用于多个区块410的基板401可为单一基板或整合基板(integrated substrate)。

182.如上所述,例如如图3a-3c所示,静态随机存取存储器单元420中的传送栅极晶体管m1和m6装配以耦接对应的字线402。静态随机存取存储器装置400包含沿着x延伸且沿着y方向依序配置的多条字线402。每一字线402可耦接多个区块410中的对应静态随机存取存储器单元420。每一区块410定义于两相邻的导电的狭缝430之间。导电的狭缝430与具有p连接部的半导体柱,例如图3c的313a、313d,形成于p型掺杂区411上,而具有n连接部的半导体柱,例如图3c的313b、313c,形成于n型掺杂区412上。

183.静态随机存取存储器装置400可包含垂直地堆叠在静态随机存取存储器单元420上的三个金属层。第一金属层,例如图3a-3b的金属层ml1 320,形成于静态随机存取存储器单元420上,其中位线bl 434、blb 436形成为沿着y方向延伸且沿着x方向依序配置。在一些实施例中,供应电压线432、438可形成于第一金属层中且耦接至静态随机存取存储器单元420中的上拉晶体管m2、m4的源极端。供应电压线432、438可通过导电线431耦接至狭缝430,因此供应电压线432、438可提供供应电压vcc。第二金属层,例如图3a-3b的金属层ml2 310,可形成于第一金属层上且装配以交叉耦接静态随机存取存储器单元420中的两个反相器,例如如图3a、3c、3d所示。第三金属层可形成于第二金属层上且装配以形成多条字线402。在一些示例中,耦接供应电压vcc和第二供应电压vss(例如接地)的电源供应线亦可形成于第三金属层中。

184.图5a-5n为用以制造三维静态随机存取存储器单元结构的方法的多个步骤的示例,例如图3a-3d的静态随机存取存储器单元结构300或图4a-4c的静态随机存取存储器单元420。方法可用互补式金属氧化物半导体技术来实现。为了说明,一些附图包含上图(1)与下图(2),其中上图(1)示出在处理步骤后形成的结构的透视图,下图(2)示出在处理步骤后形成的结构的剖面图。

185.图5a示出用以形成三维静态随机存取存储器单元结构的基板500。基板500可为图3c的基板360或图4b的基板401。为了说明,基板500由硅制成。基板500被掺杂(或注入)以形成三个掺杂(或注入)区,两个p 硅区501(例如图3c的p 区362或图4b-4c的p型掺杂区411)与例如沿着x方向在两个p 硅区之间的n 硅区502(例如图3c的n 区364或图4b-4c的n型掺杂区412)。相邻的掺杂区501、502通过浅沟道隔离结构503(例如图3c的浅沟道隔离结构363)电性绝缘,浅沟道隔离结构503由绝缘材料制成,例如氧化物。在一些示例中,基板500具有沿着x方向的长度400纳米与沿着y方向的宽度80纳米。

186.图5b示出垂直地堆叠在基板500上的三个半导体层,例如,通过使用有机化学气相沉积(metal-organic chemical vapor deposition,mocvd)、分子束外延(molecular beam epitaxy,mbe)、原子层沉积(atomic layer deposition,ald)、物理气相沉积(physical vapor deposition,pvd)、化学气相沉积(chemical vapor deposition,cvd)的沉积方法或在真空腔室中以某温度进行任意其他合适的沉积方法来形成。堆叠的层包含底部的层504、中间中层505、以及顶部的层506。底部的层504与顶部的层506皆由第一材料制成,例如氮化硅(silicon nitride,sin)(或简称nitride),而中间的层505由第二材料制成,例如多晶硅(或简称poly)。相邻的层504、505和505、506通过对应绝缘层507而彼此绝缘,例如,绝缘层507可由绝缘材料例如氧化物制成。在一些示例中,沿着z方向,每一半导体层504、505、506具有20纳米的厚度,且绝缘层507具有10纳米的厚度。在本实施例中为了说明,第一材料为氮化硅,且第二材料为多晶硅。在一些其他实施例中,第一材料或第二材料可选择不同的材料,且第一材料或第二材料的蚀刻速率可不同。

187.图5c示出形成阶梯区508以使三个堆叠的层分开为两部位,以形成静态随机存取存储器单元结构的一对反相器(例如图3a-3c的第一反相器302、第二反相器304)。

188.在阶梯区508形成之后,绝缘材料,例如氧化物,被填入阶梯区508中,且在半导体层506上形成绝缘层510。接着,如图5d所示,形成四个垂直孔洞509,四个垂直孔洞509通过绝缘层507、510与堆叠的层504、505、506至基板500。两个孔洞509对p 硅区501开放,且两个孔洞509对n 硅区502开放。多个孔洞509可通过沿着垂直方向(例如z方向)进行非等向蚀刻(anisotropic etching)来形成,例如可使用反应离子蚀刻(reactive ion etching,rie)或空穴蚀刻(plasma etching)。在一些示例中,孔洞509具有30纳米的直径。

189.图5e示出将半导体材料填入多个垂直孔洞509中以形成半导体柱(或垂直通道)511。在一些示例中,可通过在多个垂直孔洞509中外延成长硅(例如外延硅)以形成多个半导体柱511。在一些实施例中,可通过多晶硅沉积以形成多个半导体柱511。中间层505可使用和半导体柱511不同的材料。

190.图5f示出形成两个狭缝512以定义单一静态随机存取存储器单元结构。狭缝512可通过蚀刻穿过基板500上的多个层来形成。狭缝512亦提供通道以蚀刻绝缘层510下方的多个半导体层。

191.如图5g所示,中间层505被选择性蚀刻以移除中间层505中的多晶硅材料,以形成开放空间513,并在阶梯区中保留绝缘材料例如氧化物,在开放空间513中保留半导体柱511。

192.在填充开放空间513之前,多个半导体柱511被处理以个别地形成多个p连接部和多个n连接部。如图5h所示,使用第一屏蔽514以覆盖两个中间的半导体柱511,没有被第一屏蔽514覆盖的左边的半导体柱511的中间部位、以及右边的半导体柱511的中间部位被掺杂入p连接部515,例如通过空穴掺杂。

193.接着,如图5i所示,形成第二屏蔽516以覆盖包含p连接部515的左边的半导体柱511与右边的半导体柱,然后,没有被第二屏蔽516覆盖的两个半导体柱511的中间部位被掺杂入n连接部517,例如通过空穴掺杂。

194.图5i示出将金属材料,例如钛,填入开放空间513以形成导电层518。导电层518被阶梯区中的绝缘材料分开为两部位,左边部位被用作第一节点n0(例如图3a-3c的节点n0),

右边部位被用作第二节点n1(例如图3a-3c的节点n1)。半导体柱511中的p连接部515与n连接部517和金属材料反应且转变为导电层518中的p连接部519与n连接部520。例如,p连接部515与n连接部517为外延硅,其和填充金属钛反应成为钛硅化物(tisi)。在一些实施例中,在填充例如钛的金属材料之前,金属硅化物,金属硅化物在开放空间513中的半导体柱511的周围成长,例如如图3c所示。

195.为了形成不同的晶体管,可垂直蚀刻顶部的层510、506、507至导电层518,以形成两个切口(cut)521,如图5k所示。接着,选择性地蚀刻掉半导体层504和506(例如由氮化物制成),以形成开放空间522和524,如图5l所示。

196.接着,在开放空间522和524中的半导体柱511的周围成长栅极氧化物材料,以形成薄的栅极氧化物层523,例如如图5m所示。在这之后,将导电材料,例如金属钨,填入开放空间522和524中,以分别形成导电层526和528(例如导电的层330和350)。接着,导电层526和528被回蚀(etched back)以被限制于开放空间522和524内。切口52保持不变,且栅极氧化物层523被例如钨的导电材料环绕,如图5m和图3c所示。

197.接着,半导体柱511的顶部被掺杂以分别形成p 连接部530与n 连接部532。图5n示出图5a-5n的处理步骤得到的成型结构540。接着,绝缘材料,例如氧化物,可被填入成型结构540中,例如填入多个切口521中,以形成多个绝缘狭缝,且导电材料(例如金属钨)可被沉积至多个狭缝512内并电性连接多个p 硅区501(例如,以形成图3c的多个狭缝301),以得到可实现为静态随机存取存储器单元结构的最终结构。

198.可进一步进行多个后处理步骤,例如形成多个穿孔(例如图3a-3d的穿孔311)、以及形成具有多条导电布线(例如图3a、3b、3d的导电布线312和314)、多条位线(例如图4b的位线bl 434和blb 436)、多条电源供应线(例如图4b的供应电压线432和438)、和/或多条字线(例如图4a-4c的字线402)的多个金属层(例如图3a-3b的金属层ml1 320和ml2 310),以形成包含静态随机存取存储器单元阵列的静态随机存取存储器装置(例如图4a-4c的静态随机存取存储器装置400)。

199.图6为用以形成三维半导体结构的方法600的示例的流程图,三维半导体结构例如是图3a-3d所示的静态随机存取存储器单元结构300或图4a-4c所示的静态随机存取存储器单元420。方法600可相似于图5a-5n所示的方法。

200.在步骤602中,多个半导体层形成于半导体基板上。半导体基板可为图5a的基板500、图3c的基板360、或图4b的基板401。半导体基板500可被掺杂(或注入)以形成一对具有第一掺杂类型的第一掺杂区(例如图5a的两个p 硅区501)与具有第二掺杂类型的第二掺杂区(例如图5a的两个n 硅区502)。相邻的掺杂区可电性绝缘,例如可通过浅沟道隔离结构以电性绝缘,浅沟道隔离结构例如是图5a的浅沟道隔离结构503。

201.多个半导体层可包含沿着垂直方向依序堆叠在一起的第一半导体层、第二半导体层与第三半导体层(例如图5b的半导体层504、505、506)。第一半导体层与第三半导体层可由第一材料制成,例如氮化硅,而第二半导体层可由第二材料制成,例如多晶硅。相邻的半导体层可通过对应绝缘层以彼此绝缘,绝缘层例如是图5b的绝缘层507。三个半导体层可垂直地堆叠在半导体基板500上,例如,通过使用有机化学气相沉积、分子束外延、原子层沉积、物理气相沉积、化学气相沉积的沉积方法或在真空腔室中以某温度进行任意其他合适的沉积方法来形成。

202.在步骤604中,形成阶梯区以使多个半导体层的每一者分开为彼此电性绝缘的第一部位和第二部位。如图5c和图5d所示,可通过蚀刻多个半导体层的第一部位和第二部位之间的材料、且在多个半导体层的第一部位和第二部位之间的蚀刻区域中沉积绝缘材料(例如氧化物),以形成阶梯区。

203.在步骤606中,形成第一半导体柱、第二半导体柱、第三半导体柱与第四半导体柱,第一半导体柱与第二半导体柱垂直地贯穿多个半导体层的第一部位至半导体基板上,第三半导体柱与第四半导体柱垂直地贯穿多个半导体层的第二部位至半导体基板上。第一半导体柱、第二半导体柱、第三半导体柱与第四半导体柱沿着水平方向依序配置,水平方向垂直于垂直方向。

204.如图5d-5e所示,可先形成四个垂直孔洞(例如图5d的孔洞509),四个垂直孔洞通过多个半导体层与多个半导体层之间的多个绝缘层至半导体基板。两个孔洞对第一掺杂区开放(例如图5d的p 硅区501),且两个孔洞对第二掺杂区开放(例如图5d的n 硅区502)。多个孔洞可通过沿着垂直方向进行非等向蚀刻来形成,例如可使用反应离子蚀刻或空穴蚀刻。接着,可通过将半导体材料填入四个垂直孔洞中以形成四个半导体柱(例如图5的半导体柱511)。在一些示例中,可通过在多个垂直孔洞中外延成长硅(例如外延硅)以形成多个半导体柱。在一些实施例中,可通过多晶硅沉积以形成多个半导体柱。第二半导体层的第二材料可不同于半导体柱的半导体材料。

205.在步骤608中,以第一导电材料取代第二半导体层的第一部位与第二部位以形成第二导电层(例如图5j的导电层518)。

206.在一些实施例中,如图5f所示,可通过对多个半导体层进行蚀刻且蚀刻至半导体基板上以形成两个开放狭缝(例如图5f的狭缝512),且第一半导体柱、第二半导体柱、第三半导体柱与第四半导体柱介于两个开放狭缝之间。两个开放狭缝被用以第应单一静态随机存取存储器单元结构。可通过对多个半导体层进行蚀刻且蚀刻至半导体基板上以形成两个开放狭缝。开放狭缝可提供通道以选择性蚀刻多个半导体层。

207.如图5g所示,通过两个开放狭缝蚀刻掉第二半导体层的第一部位与第二部位,以得到第一开放空间,例如如图5g的开放空间513。在以第一导电材料填充第一开放空间以形成第二导电层之前,如图5h所示,在第一半导体柱与第四半导体柱的部分中的具有第一掺杂类型的第一连接部(例如图5h的p连接部515)形成于第一开放空间中;而且,如图5i所示,在第二半导体柱与第三半导体柱的部分中的具有第二掺杂类型的第二连接部(例如图5i的n连接部517)可形成于第一开放空间中。

208.接着,如图5j所示,将第一导电材料,例如钛,填入第一开放空间中以形成第二导电层(例如图5j的导电层518)。四个半导体柱中的第一连接部(例如图5h的p连接部515)与第二连接部(例如图5i的n连接部517)和第一导电材料反应,且转变为第二导电层中的新的第一连接部(例如图5j的p连接部519)与新的第二连接部(例如图5j的n连接部520)。

209.在步骤610中,第一半导体层与第三半导体层的第一部位与第二部位被蚀刻掉以形成第二开放空间,且形成围绕第二开放空间中的每一半导体柱的部分的介电结构。

210.为了形成不同的晶体管,可形成两个顶部狭缝(例如图5k的切口521),其中第一顶部狭缝形成于第一半导体柱与第二半导体柱之间,第二顶部狭缝形成于第三半导体柱与第四半导体柱之间。第一顶部狭缝与第二顶部狭缝沿着垂直方向延伸通过第一半导体层,且

延伸至第二导电层上,如图5k所示。接着,通过开放狭缝与两个顶部狭缝对第一半导体层与第三半导体层进行选择性蚀刻,以形成第二开放空间(例如图5l的开放空间522和524)。

211.接着,如图5m所示,介电材料,例如栅极氧化物材料,可成长于第二开放空间中的半导体柱周围,以形成对应的介电结构,例如图5m的薄的栅极氧化物层523。介电结构被用作栅极介电结构,例如图3c的栅极介电结构333。

212.在步骤612中,在开放空间中沉积第二导电材料,以形成第一导电层与第三导电层。第二导电材料可为金属钨。多个介电结构分别被第一半导体柱、第二半导体柱、第三半导体柱、第一导电层与第三导电层环绕。

213.在一些实施例中,方法600可还包含对多个半导体柱的顶部进行掺杂以分别形成具有第一掺杂类型的另一第一连接部(例如图5n的p 连接部530)与具有第二掺杂类型的另一第二连接部(例如图5n的n 连接部532)。

214.在一些实施例中,方法600还包含在顶部第一狭缝与顶部第二狭缝中沉积绝缘材料(例如氧化物)。方法600可还包含在开放狭缝中沉积导电材料(例如金属钨)以得到电性连接第一掺杂区的两个导电狭缝。通过方法600获得的最终结构可实现为静态随机存取存储器单元结构。

215.方法600亦可包含一或更多的后处理步骤,例如形成多个穿孔(例如图3a-3d的穿孔311)、以及形成具有多条导电布线(例如图3a、3b、3d的导电布线312和314)、多条位线(例如图4b的位线bl 434和blb 436)、多条电源供应线(例如图4b的供应电压线432和438)和/或多条字线(例如图4a-4c的字线402)的多个金属层(例如图3a-3b的金属层ml1 320和ml2 310),可进一步进行多个后处理步骤以形成包含静态随机存取存储器单元阵列的静态随机存取存储器装置(例如图4a-4c的静态随机存取存储器装置400)。

216.图7为整合示例静态随机存取存储器单元结构710与示例非易失性存储器单元结构的半导体装置700。静态随机存取存储器单元结构710与非易失性存储器单元结构皆可由栅极全环架构制成三维结构,其可将静态随机存取存储器单元结构710与非易失性存储器单元结构组合成相同或相似的方法流程。为了说明,将快闪存储器单元结构720作为非易失性存储器单元结构的示例。快闪存储器单元结构720可为电子擦除式可复写只读存储器单元结构。

217.静态随机存取存储器单元结构710可相似于图3a-3d的静态随机存取存储器单元结构300或图4a-4c的静态随机存取存储器单元420。静态随机存取存储器单元结构710可具有和图2的电路200相似的电路。如图7所示,静态随机存取存储器单元结构710包含第一反相器与第二反相器,第一反相器包含晶体管m1、m2、m3(例如图2的m1 212、m2 214、m3 216或图3a-3d的m1 332、m2 334/354、m3 352),第二反相器包含晶体管m4、m5、m6(例如图2的m4 222、m5 224、m6 226或图3a-3d的m4 336/356、m5 358、m6 338)。通过使节点n0耦接至节点c1以及使节点n1耦接至节点c0,第一反相器与第二反相器彼此交叉耦接。晶体管m3和m5的源极端耦接至接地线701(例如图4a-4c的接地414)。晶体管m2和m4的源极耦接至电源线702(例如图4a-4c的供应电压线438)提供的供应电压vcc。晶体管m1和m6的栅极耦接至字线703(例如图4a-4c的字线402)。晶体管m1和m6的源极分别耦接至位线708和709。

218.如图7所示,快闪存储器单元结构720可为包含一对三栅极晶体管结构722、724的电子擦除式可复写只读存储器单元结构。三栅极晶体管结构722包含串联式耦接于静态随

机存取存储器单元结构710中的节点n0的一硅-氧化硅-氮化硅-氧化物-硅(silicon-oxide-nitride-oxide-silicon,sonos)晶体管t2与两个金属氧化物硅(mos)晶体管t1、t3;三栅极晶体管结构724包含串联式耦接于静态随机存取存储器单元结构710中的节点n1的一sonos晶体管t5与两个金属氧化物硅(mos)晶体管t4、t6。通过这样的方式,快闪存储器单元结构720与静态随机存取存储器单元结构710耦接在一起。金属氧化物硅晶体管t3和t6的栅极耦接至储存线(store line)704。sonos晶体管t2和t5的栅极耦接至操作(编程/擦除)线705。金属氧化物硅晶体管t1和t4的栅极耦接至重新呼叫线(recall line)706。金属氧化物硅晶体管t1、t3与sonos晶体管t2串联式耦接至电源线707,而金属氧化物硅晶体管t4、t6与sonos晶体管t5亦串联式耦接至电源线707。

219.在一些示例中,sonos晶体管t2或t4的每一者被调谐(tuned)为开启或关闭状态其中之一,且静态随机存取存储器单元结构710可直接重新呼叫sonos晶体管t2、t4的储存状态而不需要总线(bus)。

220.尽管本公开可能描述许多细节,这些不应被理解为限制请求保护的本发明的范围或可能请求保护的内容,而是对特定实施例的特定特征的描述。在本公开中,描述于不同实施例中的某些特征也可合并实现于单一实施例中。相反地,在本公开中,描述于单一实施例的各种特征也可单独或以任意合适的次组合实现于多个实施例中。此外,虽然多个特征可能被描述为在某些组合中作用,且甚至最初是以这样的方式请求保护,但在一些情况下,来自所请组合的一或更多的特征可从组合中删除,且所请组合可指向此组合或次组合的变化。相似地,虽然在附图中以特定顺序描述多个操作,但此不应理解为这些操作必须以所示的特定顺序进行或依序进行、或必须进行所有示出的操作,以达成期望的功效。

221.仅公开一些示例与实施方式。基于所公开的内容,可对所述的示例与实施方式与其他实施方式进行多种改变、修饰和强化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。