集成有工程化衬底的电子功率器件

1.本技术是申请日为2017年8月23日递交的申请号为2017800623979以及发明名称为“集成有工程化衬底的电子功率器件”的中国发明专利申请的分案申请。

2.相关申请的交叉引用

3.本技术要求2016年8月23日提交的申请号为62/378,382的美国临时专利申请的优先权,其内容以全文引用的方式并入本文,以用于所有目的。

背景技术:

4.通常,基于氮化镓的功率器件在蓝宝石衬底上外延生长。由于衬底和外延层由不同的材料组成,因此这种基于氮化镓的功率器件在蓝宝石衬底上的生长是一种异质外延生长的过程。由于这种异质外延的生长过程,外延生长材料会呈现出各种负面影响,包括均匀性的降低以及与外延层的电子/光学特性相关联的度量指标(metrics)的降低。因此,本领域需要与外延生长过程和衬底结构有关的改进的方法和系统。

技术实现要素:

5.本发明大体上涉及一种形成在工程化衬底结构上的功率器件。更具体地,本发明涉及一种涉及适用于利用外延生长过程来制造功率器件的方法和系统。如本文所描述的,本发明的实施例已应用于通过外延生长而在衬底结构上制造功率器件和半导体二极管的方法和系统,其中,所述衬底结构的特征在于该衬底结构的热膨胀系数(coefficient of thermal expansion,cte)与形成功率器件的外延层的热膨胀系数实质上匹配。所述方法和技术可以应用于各种半导体工艺操作中。

6.根据本发明的实施例,提供一种功率器件。所述功率器件包括衬底,该衬底包括:多晶陶瓷芯、耦合至所述多晶陶瓷芯的第一粘附层、耦合至所述第一粘附层的阻挡层、耦合至所述阻挡层的键合层以及耦合至所述键合层的实质单晶层。所述功率器件还包括:耦合至所述实质单晶层的缓冲层以及耦合至所述缓冲层的沟道区。所述沟道区包括:第一端、第二端以及设置在所述第一端与第二端之间的中心部。所述沟道区还包括耦合至所述缓冲层的沟道区阻挡层。所述功率器件进一步包括:设置在沟道区的第一端处的源极接触(contact)、设置在沟道区的第二端处的漏极接触、以及耦合至所述沟道区的栅极接触。

7.根据本发明的另一个实施例,提供一种形成功率器件的方法。所述方法包括:通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。所述方法还包括:在所述实质单晶层上形成缓冲层;以及通过在所述缓冲层上形成外延沟道区阻挡层而在所述缓冲层上形成沟道区。所述沟道区具有第一端、第二端以及在第一端与第二端之间的中心部。所述方法还包括:在所述沟道区的第一端处形成源极接触;在所述沟道区的第二端处形成漏极接触;以及在所述沟道区上形成栅极接触。

8.根据本发明的特定的实施例,提供一种半导体二极管。所述半导体二极管包括衬底,该衬底包括:多晶陶瓷芯、耦合至所述多晶陶瓷芯的第一粘附层、耦合至所述第一粘附

层的阻挡层、耦合至所述阻挡层的键合层以及耦合至所述键合层的实质单晶层。所述半导体二极管还包括:耦合至所述实质单晶层的缓冲层、耦合至所述缓冲层的半绝缘层以及耦合至所述半绝缘层的第一n型氮化镓层。所述第一外延n型氮化镓层具有第一掺杂浓度。所述半导体二极管进一步包括耦合至所述第一n型氮化镓层的第二n型氮化镓层。所述第二n型氮化镓层具有比所述第一掺杂浓度小的第二掺杂浓度。此外,所述半导体二极管包括:耦合至所述第二n型氮化镓层的p型氮化镓层、耦合至所述p型氮化镓层的阳极接触以及耦合至所述第一n型氮化镓层的一部分的阴极接触。

9.根据本发明的另一个特定的实施例,提供一种形成半导体二极管的方法。所述方法包括:通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。所述方法还包括:在所述实质单晶层上形成缓冲层;在所述缓冲层上形成半绝缘层;以及在所述半绝缘层上形成第一外延n型氮化镓层。所述第一外延n型氮化镓层具有第一掺杂浓度。所述方法进一步包括:在所述第一外延n型氮化镓层上形成第二外延n型氮化镓层。所述第二外延n型氮化镓层具有比所述第一掺杂浓度小的第二掺杂浓度。此外,所述方法包括:在所述第二外延n型氮化镓层上形成外延p型氮化镓层;移除第二外延n型氮化镓层的一部分以及外延p型氮化镓的一部分层,以暴露第一外延n型氮化镓层的一部分;在所述外延p型氮化镓层的剩余部分上形成阳极接触;以及在所述第一外延n型氮化镓层的已暴露的部分上形成阴极接触。

10.根据本发明的具体的实施例,提供一种形成半导体二极管的方法。所述方法包括:通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。所述方法还包括:在所述实质单晶层上形成第一外延n型氮化镓层;并且在所述第一外延n型氮化镓层上形成第二外延n型氮化镓层。所述第一外延n型氮化镓层具有第一掺杂浓度,并且所述第二外延n型氮化镓层具有小于所述第一掺杂浓度的第二掺杂浓度。所述方法包括:在所述第二外延n型氮化镓层上形成外延p型氮化镓层;移除一部分衬底,以暴露所述第一外延n型氮化镓层的表面;在所述外延p型氮化镓层上形成阳极接触;以及在所述第一外延n型氮化镓层的已暴露的表面上形成阴极接触。

11.根据本发明的另一个具体的实施例,提供一种功率器件。所述功率器件包括衬底,该衬底包括:多晶陶瓷芯、耦合至所述多晶陶瓷芯的第一粘附层、耦合至所述第一粘附层的阻挡层、耦合至所述阻挡层的键合层以及耦合至所述键合层的实质单晶层。所述功率器件还包括:耦合至所述实质单晶层的缓冲层以及耦合至所述缓冲层的沟道区。所述沟道区包括:第一端、第二端以及设置在所述第一端与第二端之间的中心部。所述沟道区包括耦合至所述缓冲层的沟道区阻挡层以及设置在所述沟道区的第一端处的源极接触。所述器件进一步包括:设置在沟道区的第二端处的漏极接触以及耦合至所述沟道区的栅极接触。作为示例,所述缓冲层可以包括iii-v族半导体材料、锗硅、氮化铝镓、氮化铟镓或者氮化铟铝镓中的至少一种。

12.与传统技术相比,本发明可以获得许多优点。例如,本发明的实施例提供一种形成在工程化衬底上的功率器件和半导体二极管,所述工程化衬底的热膨胀系数(cet)与器件的外延层的热膨胀系数实质上匹配。将生长的衬底的热膨胀特性与外延层相匹配,可以减

少外延层和/或工程化衬底中的应力。这种应力是导致各种类型的缺陷的原因。例如,这种应力可能增加外延层中的位错密度,这损害了外延层的电特性和光学特性。应力也可能导致外延层或者衬底中的残余应变,这可能导致在后续的步骤中出现的额外的处理问题,例如应力开裂、位错滑动、滑移(slip)、弯曲和翘曲。由热膨胀导致的衬底的弯曲和翘曲可能会在自动化设备中出现材料处理的问题,并且限制设备制造、衬底开裂和材料蠕变所需的执行额外的光刻步骤的能力。此外,受应力材料的器件的性能寿命减少。应力释放和应力诱导的裂纹扩展、位错滑动和由热失配引起的其他晶格运动可能导致一系列模式的早期故障,从降低的器件性能到器件与器件层的断裂或剥离。

13.结合下文和附图更详细地描述本发明的这些和其它实施例及其许多优点和特征。

附图说明

14.图1为示出了根据本发明的实施例的工程化衬底结构的简化的截面示意图。

15.图2a为示出了根据本发明的实施例的工程化结构的物质浓度随深度变化的sims分布图。

16.图2b为示出了根据本发明的实施例的退火之后的工程化结构的物质浓度随深度变化的sims分布图。

17.图2c为示出了根据本发明的实施例的退火之后的具有氮化硅层的工程化结构的物质浓度随深度变化的sims分布图。

18.图3为示出了根据本发明的另一个实施例的工程化衬底结构的简化的截面示意图。

19.图4为示出了根据本发明的又一个实施例的工程化衬底结构的简化的截面示意图。

20.图5为示出了根据本发明的实施例的制造工程化衬底的方法的简化的流程图。

21.图6为示出了根据本发明的另一个实施例的制造工程化衬底的方法的简化的流程图。

22.图7为示出了根据本发明的实施例的用于rf和功率应用的外延/工程化衬底结构的简化的截面示意图。

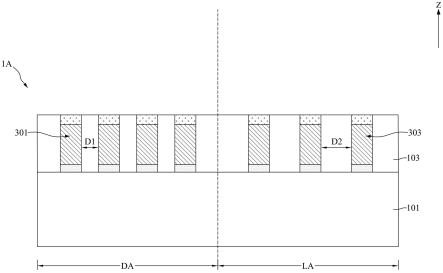

23.图8a为示出了根据本发明的实施例的在工程化衬底结构上的iii-v族外延层的简化的示意图。

24.图8b为示出了根据本发明的另一个实施例的形成在工程化衬底上的半导体器件的过孔配置的简化的平面示意图。

25.图9为示出了根据本发明的实施例的形成在工程化衬底上的横向功率器件的简化的截面示意图。

26.图10为示出了根据本发明的实施例的在工程化衬底上制造横向功率器件的方法的简化的流程图。

27.图11a为示出了根据本发明的另一个实施例的形成在工程化衬底上的横向功率器件的简化的截面示意图。

28.图11b为示出了根据本发明的另一个实施例的形成在工程化衬底上的横向功率器件的简化的截面示意图。

29.图11c为示出了根据本发明的实施例的p型氮化镓结构的分解视图的简化的截面示意图。

30.图12为示出了根据本发明的另一个实施例的在工程化衬底上制造横向功率器件的方法的简化的流程图。

31.图13为示出了根据本发明的实施例的形成在工程化衬底上的垂直半导体二极管的简化的截面示意图。

32.图14为示出了根据本发明的另一个实施例的在工程化衬底上制造垂直半导体二极管的方法的简化的流程图。

33.图15为示出了根据本发明的另一个实施例的形成在工程化衬底上的垂直半导体二极管的简化的截面示意图。

34.图16为示出了根据本发明的另一个实施例的在工程化衬底上制造垂直半导体二极管的方法的简化的流程图。

35.图17为示出了根据本发明的实施例的形成在工程化衬底上的半导体器件的简化的截面示意图。

具体实施方式

36.本发明通常涉及一种形成在工程化衬底结构上的功率器件。更具体地,本发明涉及一种适用于利用外延生长工艺来制造功率器件的方法和系统。仅仅是通过示例的方式,本发明可以应用于通过外延生长在衬底结构上制造功率器件的方法和系统,其中,所述衬底结构的特征在于具有与形成功率器件的外延层实质上匹配的热膨胀系数(cte)。所述方法和技术可以应用于各种半导体的工艺操作中。

37.图1为示出了根据本发明的实施例的工程化衬底结构的简化的截面示意图。图1中示出的工程化衬底100适用于各种电子和光学应用。所述工程化衬底100包括芯110,芯110可以具有与将要生长在工程化衬底100上的外延材料的热膨胀系数实质上匹配的cte。所述外延材料130被示出为可选的,因为其并不需要作为工程化衬底100的组成部分,但是会通常地生长在工程化衬底100上。

38.对于包括基于氮化镓(gallium nitride,gan)的材料(包括基于gan的层的外延层)的生长的应用,所述芯110可以为多晶陶瓷材料,例如,多晶氮化铝(aluminum nitride,aln),其可以包括粘结材料,例如氧化钇。其他材料也可以应用在芯110中,包括:多晶氮化镓(gan)、多晶氮化铝镓(algan))、多晶碳化硅(sic)、多晶氧化锌(zno)、多晶三氧化二镓(ga2o3)等。

39.芯的厚度可以大约为100μm至1500μm,例如,为725μm。芯110可以封装在粘附层112中,该粘附层112可以被称为壳或者封装壳。在一个实施例中,所述粘附层112包括正硅酸乙酯(tetraethyl orthosilicate,teos)氧化层,该氧化层的厚度大约为(埃)。在其他的实施例中,所述粘附层的厚度是变化的,例如在到的范围内变化。虽然在一些实施例中使用teos氧化物用于粘附层,但是根据本发明的实施例,也可以使用在随后的沉积层与下面的层或材料(例如,陶瓷,特别的,多晶陶瓷)之间提供粘附的其他材料。例如,二氧化硅(sio2)或者其他硅氧化物(si

x

oy)很好地粘附到陶瓷材料并且为随后的沉积(例如,导电材料的沉积)提供合适的表面。在一些实施例中,所述粘附层112完全地围绕芯110,以

形成完全封装的芯。可以利用lpcvd(low-pressure chemical vapor deposition,低压化学汽相沉积)工艺来形成粘附层112。所述粘附层提供有这样的表面:随后的层粘附在该表面上,以形成工程化衬底100结构的组成部分。

40.根据本发明的实施例,除了使用lpcvd工艺、基于熔炉的工艺等来形成封装的第一粘附层之外,也可以使用其他半导体工艺,包括cvd(chemical vapor deposition,化学汽相沉积)工艺或者类似的沉积工艺。作为示例,可以使用涂覆芯的一部分的沉积工艺,所述芯可以被翻转,并且可以重复所述沉积过程,以涂覆芯的其他部分。因此,虽然在一些实施例中使用lpcvd技术来提供完全封装的结构,但是根据特定应用,也可以使用其他膜形成技术。

41.形成围绕所述粘附层112的导电层114。在一个实施例中,由于多晶硅表现出对于陶瓷材料的粘附性很差,所述导电层114是围绕第一粘附层112形成的多晶硅(polysilicon)(即,多晶硅(polycrystalline silicon))壳。在导电层114是多晶硅的实施例中,多晶硅层的厚度可以大约为至例如为在一些实施例中,所述多晶硅层可以形成为壳以完全地包围第一粘附层112(例如,teos氧化层),从而形成了完全封装的第一粘附层,并且其可以利用lpcvd工艺来形成。在其他的实施例中,如下面所讨论的,导电材料可以形成在粘附层的一部分上,例如,形成在衬底结构的下半部分。在一些实施例中,所述导电材料可以形成为完全封装层,并且随后在衬底结构的一侧上移除。

42.在一个实施例中,所述导电层114可以为掺杂的多晶硅层,以提供高导电材料,例如,掺杂硼以提供p型多晶硅层。在一些实施例中,硼的掺杂在1

×

10

19

cm-3

到1

×

10

20

cm-3

的水平,以提供高导电性。可以使用不同掺杂剂浓度的其他掺杂剂(例如,掺杂剂浓度在1

×

10

16

cm-3

到5

×

10

18

cm-3

范围内的磷、砷、铋等)来提供适用于导电层114使用的n型或p型半导体材料。本领域普通技术人员可以意识到多种变化、修改和替代。

43.在将工程化衬底100静电吸附到半导体处理工具(例如具有静电放电(electrostatic discharge,esd)吸盘(chuck)的工具)期间,所述导电层114的存在是有用的。导电层114可以实现在半导体处理工具中进行处理之后的快速去吸附。因此,本发明的实施例提供了一种可以用传统硅片所使用的方式来进行处理的衬底结构。本领域普通技术人员可以意识到多种变化、修改和替代。

44.围绕所述导电层114形成第二粘附层116(例如,厚度大约为的teos氧化层)。在一些实施例中,所述第二粘附层116完全地包围导电层114,以形成完全封装的结构。可以利用lpcvd工艺、cvd工艺、或者其他合适的沉积工艺(包括沉积旋涂电介质(spin-on dielectric))来形成第二粘附层116。

45.围绕第二粘附层116形成阻挡层118,例如,氮化硅层。在一个实施例中,所述阻挡层为厚度大约为至的氮化硅层118。在一些实施例中,阻挡层118完全包围第二粘附层116,以形成完全封装的结构,并且可以利用lpcvd工艺来形成该阻挡层118。除了氮化硅层,也可以使用非晶态材料(包括碳氮化硅(sicn)、氮氧化硅(sion)、氮化铝(aln)、碳化硅(sic)等)作为阻挡层。在一些实施例中,所述阻挡层由被构建以形成阻挡层的多个子层组成。因此,术语“阻挡层”并不旨在表示单层或者单一材料,而是涵盖以复合方式分层的一种或多种材料。本领域技术人员可以意识到多种变化、修改和替代。

46.在一些实施例中,所述阻挡层(例如,氮化硅层)防止(例如在高温(例如,1000℃)

外延生长过程期间)存在于芯110中的元素的扩散和/或放气进入可以存在工程化衬底100的半导体处理室的环境中。芯110中存在的元素可以包括,例如,氧化钇(yttrium oxide)(即,钇氧化物(yttria))、氧、金属杂质、其他微量元素等。从芯110扩散的元素会导致工程化层120/122中的非故意掺杂。从芯110排出的元素会行进穿过腔室并且吸附在晶片的一些位置上,导致了工程化层120/122和外延材料130中产生杂质。通过使用在本文描述的封装层,可以在半导体工艺流程和洁净的室环境中使用陶瓷材料,所述陶瓷材料包括被设计用于非洁净的室环境的多晶氮化铝。

47.图2a为示出了根据本发明的实施例的工程化结构的物质浓度随深度变化的二次离子质谱(sims)分布图。x轴表示从工程化层120/122的表面到芯110的深度202。线208表示工程化层120/122与芯110之间的界面。第一y轴表示每立方厘米原子为单位的组分浓度204。第二y轴表示以每秒计数为单位的离子的信号强度206。图2a中的工程化结构不包括阻挡层118。参见图2a,陶瓷芯110中存在的几种物质(例如,钇、钙和铝)在工程化层120/122中降至可忽略的浓度。钙210、钇220和铝230的浓度分别下降了三个、四个和六个数量级。

48.图2b为示出了根据本发明的实施例的退火之后的不具有阻挡层的工程化结构的物质浓度随深度变化的sims分布图。如上面所讨论的,在半导体处理操作期间,由本发明的实施例提供的工程化衬底结构可以例如在基于氮化镓的层的外延生长期间在高温(大约1100℃)下暴露数小时。对于图2b中示出的分布图,所述工程化衬底结构在1100℃下退火四小时。如图2b所示,在工程化层中最初以低浓度存在的钙210、钇220和铝230已扩散到工程化层120/122中,从而达到了与其他元素近似的浓度。

49.因此,本发明的实施例集成有阻挡层(例如,氮化硅层),以防止来自多晶陶瓷材料(例如aln)的背景元素扩散到工程化层120/122和外延材料130(例如可选的gan层)中。封装着下面的层和材料的所述氮化硅层提供了所需的阻挡层118功能。

50.图2c为示出了根据本发明的实施例的退火之后的具有阻挡层118(由虚线240表示)的工程化结构的物质浓度随深度变化的sims分布图。将扩散阻挡层118(例如,氮化硅层)集成到工程化衬底结构中,防止在退火过程期间钙、钇和铝扩散到工程化层中,而在不存在阻挡层时会发生上述扩散。如图2c所示,存在于陶瓷芯中的钙210、钇220和铝230在退火后的工程化层中保持低浓度。因此,使用阻挡层118(例如,氮化硅层)可以防止这些元素扩散通过该扩散阻挡物,并因此防止它们释放到工程化衬底周围的环境中。类似地,包含在大量的陶瓷材料中的其他杂质都被该阻挡层牵制。

51.典型地,用于形成芯110的陶瓷材料在大约1800℃的温度下进行烧制。可以预计的是,该过程可以祛除陶瓷材料中存在的大量杂质。这些杂质可以包括钇(这是由于使用钇作为烧结剂)、钙以及其他元素和化合物。随后,在外延生长过程中(其在800℃到1100℃的非常低的温度范围内进行),原本会预料这些杂质的随后扩散将是微不足道的。但是,与传统预期相反的是,发明人已确定,即使在远小于陶瓷材料的烧制温度的温度下的外延生长过程中,也存在元素穿过工程化衬底层的显著扩散。因此,本发明的实施例将阻挡层118集成到工程化衬底110中,以防止这种不期望的扩散。

52.再次参见图1,键合层120(例如氧化硅层)设置在阻挡层118的一部分上,例如,设置在阻挡层的上表面,并且随后在键合单晶层122期间进行使用。在一些实施例中,所述键合层120的厚度可以为大约1.5μm。所述单晶层122可以包括,例如,硅(si)、碳化硅(sic)、蓝

宝石(sapphire)、氮化镓(gan)、氮化铝(aln)、锗硅(sige)、锗(ge)、金刚石(diamond)、三氧化二镓(ga2o3)、氮化铝镓(algan)、氮化铟镓(ingan)、氮化铟(inn)和/或氧化锌(zno)。在一些实施例中,所述单晶层可以具有0至0.5μm的厚度。单晶层122适用于在用于形成外延材料130的外延生长过程期间用作生长层。外延材料130的晶体层是与单晶层122相关联的下面的半导体晶格的延伸。工程化衬底100的独特的cte匹配特性使得能够比现有技术生长更厚的外延材料130。在一些实施例中,所述外延材料130包括厚度为2μm至10μm的氮化镓层,该氮化镓层可以被用作在光电器件、功率器件等中使用的多个层中的一层。在一个实施例中,所述键合层120包括单晶硅层,利用层转移工艺将该单晶硅层贴附至氧化硅阻挡层118

53.图3为示出了根据本发明的实施例的工程化衬底结构的简化的截面示意图。图3中示出的工程化衬底300适用于各种电子和光学应用。所述工程化衬底300包括芯110,其可以具有与将要生长在工程化衬底300上的外延材料的热膨胀系数实质上匹配的cte。所述外延材料130被示出为可选的,因为其并不需要作为工程化衬底100的组成部分,但是会通常地生长在工程化衬底100上。

54.对于包括基于氮化镓(gan)的材料(包括基于gan的层的外延层)的生长的应用,所述芯110可以为多晶陶瓷材料,例如,多晶氮化铝(aln)。芯的厚度可以大约为100μm至1500μm,例如,为725μm。芯110可以封装在粘附层112中,该粘附层112可以被称为壳或者封装壳。在该实施方式中,所述粘附层112完全封装芯,但是如图4中进一步详细讨论的,这不是本发明所必需的。

55.在一个实施例中,所述粘附层112包括正硅酸乙酯(teos)氧化层,该氧化层的厚度大约为在其他的实施例中,所述粘附层的厚度是变化的,例如在到的范围内变化。虽然在一些实施例中使用teos氧化物用于粘附层,但是根据本发明的实施例,也可以使用在之后沉积的层与下面的层或材料之间提供粘附的其他材料。例如,sio2、sion等很好地粘附到陶瓷材料并且为随后的沉积(例如,导电材料的沉积)提供合适的表面。在一些实施例中,粘附层112完全包围芯110,以形成完全封装的芯,并且可以利用lpcvd工艺来形成该粘附层112。所述粘附层112提供这样的表面:随后的层粘附在该表面上,以形成工程化衬底结构的组成部分。

56.根据本发明的实施例,除了使用lpcvd工艺、基于熔炉的工艺等来形成封装的粘附层112,也可以使用其他半导体工艺。作为示例,可以使用涂覆芯110的一部分的沉积工艺(例如,cvd、pecvd等等),所述芯110可以被翻转,并且可以重复所述涂覆工艺,以涂覆芯110的其他部分。

57.在粘附层112的至少一部分上形成有导电层314。在一个实施例中,所述导电层314包括多晶硅(polysilicon)(即,多晶硅(polycrystalline silicon)),其通过沉积工艺形成在由芯110和粘附层112形成的结构的下部(例如,下半部或者背侧)上。在导电层314是多晶硅的实施例中,多晶硅层的厚度可以大约为几千埃(angstrom),例如为在一些实施例中,可以利用lpcvd工艺形成所述多晶硅层。

58.在一个实施例中,所述导电层314可以为被掺杂的多晶硅层,以提供高导电材料,例如,所述导电层314可以掺杂硼以提供p型多晶硅层。在一些实施例中,硼的掺杂范围在大约1

×

10

19

cm-3

到1

×

10

20

cm-3

的水平,以提供高导电性。在将工程化衬底100静电吸附到半导体处理工具(例如,具有静电放电(esd)吸盘的工具)期间,所述导电层314的存在是有用的。

导电层314可以实现处理之后的快速去吸附。因此,本发明的实施例提供了一种可以用传统的硅片所使用的方式来进行处理的衬底结构。本领域普通技术人员可以意识到多种变化、修改和替代。

59.在导电层314(例如,多晶硅层)的周围形成有第二粘附层316(例如,第二teos氧化层)。所述第二粘附层316的厚度大约为在一些实施例中,第二粘附层316完全包围导电层114,以形成完全封装的结构,并且可以利用lpcvd工艺来形成该第二粘附层316。

60.围绕阻挡层118(例如,氮化硅层)形成第二粘附层316。在一些实施例中,所述阻挡层118具有大约为至的厚度。在一些实施例中,阻挡层118完全包围第二粘附层112,以形成完全封装的结构,并且可以利用lpcvd工艺来形成该阻挡层118。

61.在一些实施例中,使用包括氮化硅的所述阻挡层118防止,例如在高温(例如,1000℃)外延生长工艺期间,存在于芯110中的元素扩散或放气进入到可能存在工程化衬底的半导体处理室的环境中。存在于芯中的元素包括,例如,氧化钇(即,钇氧化物)、氧、金属杂质、其他微量元素等。通过使用在本文描述的封装层,可以在半导体工艺流程和洁净的室环境中使用陶瓷材料,所述陶瓷材料包括多晶氮化铝,其设计为用于非洁净的室环境。

62.在一些实施例中,所述工程化衬底100可以遵从半导体器件和材料国际(semiconductor equipment and materials international,semi)标准规范。由于工程化衬底100可以遵从semi规范,因此工程化衬底100可以与现有的半导体制造工具一起使用。例如,用于工程化衬底的晶片直径可以为4英寸、6英寸或者8英寸。在一些实施例中,8英寸的工程化衬底晶片的厚度可以为725μm至750μm。相反地,由于硅衬底的厚度为1050μm至1500μm,因此当前用于制造氮化镓外延层的硅衬底并没有遵从semi规范。由于没有遵从规范,硅衬底不能用于遵从semi规范的设备中。

63.图4为示出了根据本发明的另一个实施例的工程化衬底结构400的简化的截面示意图。在图4所示出的实施例中,所述粘附层412形成在芯110的至少一部分上,但并没有封装芯110。在该实施方式中,为了提高随后形成的导电层414(在下文将对其进行更加完整的描述)的附着力,所述粘附层412形成在芯的下表面(芯的背面)上。虽然在图4中粘附层412仅仅示出在芯的下表面上,应当理解的是,将粘附层材料沉积在芯的其他部分上将不会对工程化衬底结构的性能产生不利的影响,并且这样的材料可以在各个实施例中出现。本领域普通技术人员可以意识到多种变化、修改和替代。

64.所述导电层414(并不是形成为图3所示的壳)并没有封装粘附层412和芯110,而是与粘附层412实质上对齐。虽然导电层414被示出为沿着粘附层412的底面或者背面延伸以及向上延伸粘附层412的侧面的一部分,但这并不是本发明所必需的。因此,实施例可以使用衬底结构的一侧的沉积、衬底结构的一侧的掩蔽(masking)等。所述导电层414可以形成在粘附层412的一侧(例如,底面/者背面)的一部分上。导电层414提供了工程化衬底结构400的一侧上的电导体,该工程化衬底结构400具有在射频(rf)和大功率应用中的优势。导电层414可以包括关于图1中的导电层114所讨论的掺杂的多晶硅。除了基于半导体的导电层,在其他的实施例中,导电层414为金属层,例如,的钛等等。

65.为了提高阻挡层418对下面的材料的粘附力,部分芯110、部分粘附层412以及导电层414由第二粘附层416覆盖。如上面关于图2a、图2b和图2c所讨论的,所述阻挡层418形成封装结构,以防止来自下面的层的扩散。

66.再次参见图4,根据该实施例,可以移除一个或多个层。例如,可以移除层412和层414,只留下单个的粘附壳416和阻挡层418。在其他实施例中,可以只移除层414,留下阻挡层416下面的单个的粘附层412。在该实施例中,所述粘附层412也可以平衡由沉积在阻挡层418的顶部上的键合层120引起的应力和晶片弯曲。在芯100的顶侧上具有绝缘层(例如,在芯110与键合层120之间仅具有绝缘层)的衬底结构的构造,可以为功率/rf器件提供益处,其中,期望有高度绝缘的衬底。

67.在另一个实施例中,所述阻挡层418可以直接地封装芯110,随后是导电层414和随后的粘附层416。在该实施例中,所述键合层120可以从顶侧直接地沉积在粘附层416上。在又一个实施例中,粘附层416可以沉积在芯110上,接着是阻挡层418,并且然后接着是导电层414以及另一粘附层412。

68.尽管已经从层的方面讨论了一些实施例,术语“层”应当被理解为,使得层可以包括被构建形成感兴趣的层的多个子层。因此,术语“层”并不旨在表示由单一材料组成的单层,而是涵盖以复合方式分层以形成所期望的结构的一种或多种材料。本领域普通技术人员可以意识到多种变化、修改和替代。

69.图5为示出了根据本发明的实施例的制造工程化衬底的方法的简化的流程图。所述方法可以用于制造衬底,该衬底的cte与生长在衬底上的一个或多个外延层的cte匹配。所述方法500包括:通过提供多晶陶瓷芯来形成支撑衬底(510);在形成壳(例如,teos氧化物壳)的第一粘附层中封装所述多晶陶瓷芯(512);并且在导电壳(例如,多晶硅壳)中封装所述第一粘附层(514)。所述第一粘附层可以形成为单层teos氧化物。所述导电壳可以形成为单层多晶硅。

70.所述方法还包括:在第二粘附层(例如,第二teos氧化物壳)中封装所述导电壳(516);以及在阻挡层壳中封装所述第二粘附层(518)。所述第二粘附层可以形成为单层teos氧化物。所述阻挡层可以形成为单层氮化硅。

71.一旦通过过程510至518形成所述支撑结构,所述方法进一步包括:将键合层(例如,氧化硅层)接合至所述支撑结构(520);以及将实质单晶层(例如,单晶硅层)接合至所述氧化硅层(522)。根据本发明的实施例,也可以使用其他的实质单晶层,该单晶层包括:碳化硅、蓝宝石、氮化镓、氮化铝、锗硅、锗、金刚石、三氧化二镓、氧化锌等。所述键合层的接合可包括键合材料的沉积,随后进行本文所描述的平坦化处理过程。如在下文描述的一个实施例中,使用层转移工艺将实质单晶层(例如,单晶硅层)接合至键合层,在层转移工艺中,所述层是从硅晶片转移的单晶硅层。

72.参见图1,所述键合层120可以通过沉积厚的(例如,4μm厚)氧化层、随后利用化学机械抛光(cmp)工艺将氧化物的厚度减薄到大约1.5μm来形成。厚的初始氧化物用于填充支撑结构上存在的空洞和表面特征,这些空洞和表面特征在多晶芯制造后可能存在,并且在形成图1所示的封装层时继续存在。所述cmp处理提供了没有空洞、颗粒和其他特征的实质上平坦的表面,可以在晶片转移过程期间使用该表面将单晶层122(例如,单晶硅层)键合至键合层120。应当理解的是,所述键合层并不一定具有原子级的平坦表面的特征,而是应当提供实质上平坦的表面,该表面将以所希望的可靠性支持单晶层(例如,单晶硅层)的键合。

73.层转移工艺被用于将单晶层122(例如,单晶硅层)接合至键合层120。在一些实施例中,注入包括实质单晶层122(例如,单晶硅层)的硅晶片来形成解理面。在该实施例中,在

晶片键合之后,硅衬底可以和解理面下面的单晶硅层的一部分一起被移除,得到剥离的单晶硅层。所述单晶层122的厚度可以改变,以满足各种应用的规范。此外,所述单晶层122的晶体取向可以改变,以满足应用的规范。另外,所述单晶层的掺杂水平和分布可以改变,以满足特殊应用的规范。在一些实施例中,所述注入深度可以被调整为大于所希望的单晶层122的最终厚度。额外的厚度允许移除转移的实质单晶层的被损坏的薄的部分,留下具有所希望的最终厚度的未损坏的部分。在一些实施例中,可以修改表面的粗糙度,以用于高质量的外延生长。本领域普通技术人员可以意识到多种变化、修改和替代。

74.在一些实施例中,所述单晶层122可以足够厚以便为后续的一个或多个外延层生长提供高质量的晶格模版,但是足够薄以具有高顺应性(compliant)。当单晶层122相对较薄使得其物理特性受到较少的约束,并且与包围该单晶层的材料相似,并具有较小的产生晶体缺陷的倾向时,该单晶层122可以被认为是“顺应的”。单晶层122的顺应性可以相对于单晶层122的厚度成反比。较高的顺性可以导致在模板上生长的外延层中的缺陷密度更低,并且能够实现较厚的外延层生长。在一些实施例中,可以通过在剥离硅层上的硅的外延生长,来增加单晶层122的厚度。

75.在一些实施例中,可以通过对剥离硅层的顶部进行热氧化,然后用氢氟酸(hf)酸进行氧化层剥离来实现对单晶层122的最终厚度的调节。例如,具有初始厚度0.5μm的剥离硅层可以被热氧化,以生成具有大约420nm厚度的二氧化硅层。在移除了生长的热氧化物之后,转移层中的剩余的硅的厚度可以为大约53nm。在热氧化期间,注入的氢会向表面迁移。因此,随后的氧化层的剥离可以去除一些损害。但是,热氧化通常在1000℃或者更高的温度下进行。升高的温度也可以修复晶格损伤。

76.在热氧化期间形成在单晶层的顶部的氧化硅层可以用hf酸蚀刻进行剥离。通过调整hf溶液的温度和浓度以及氧化硅的化学计量和密度,可以调整hf酸在氧化硅与硅(sio2:si)之间的蚀刻选择性。蚀刻选择性指的是一种材料相对于其他材料的蚀刻速率。对于(sio2:si),hf溶液的选择性可以在大约10:1到大约100:1的范围内。高的蚀刻选择性可以将表面粗糙度从初始表面粗糙度以相似的因子降低。然而,所得的单晶层122的表面粗糙度可能依然大于所需的表面粗糙度。例如,在进行额外处理之前,通过2μm

×

2μm原子力显微镜(afm)扫描确定的块体硅(111)表面的均方根(rms)表面粗糙度可小于0.1nm。在一些实施例中,用于硅(111)上的氮化镓材料的外延生长的所需的表面粗糙度可以为,例如,在30μm

×

30μm afm扫描区域中小于1nm、小于0.5nm、或者小于0.2nm。

77.在热氧化和氧化层剥离之后,如果单晶层122的表面粗糙度超过所需的表面粗糙度,则将会进行额外的表面平滑处理。这里具有几种平滑硅表面的方法。这些方法可以包括:氢退火、激光微调、等离子平滑以及触摸抛光(例如,cmp)。这些方法可以涉及高纵横比表面峰的择优侵蚀(preferential attack)。因此,表面上的高纵横比特征可以比低纵横比特征被更快地移除,从而得到更平滑的表面。

78.应当理解的是,图5中所示出的具体步骤提供了制造根据本发明的实施例的工程化衬底的特定方法。根据可替代的实施例,也可以执行其他的步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图5中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特定的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

79.图6为示出了根据本发明的另一个实施例的制造工程化衬底的方法的简化的流程图。所述方法包括:通过提供多晶陶瓷芯来形成支撑结构(610);形成耦合至多晶陶瓷芯的至少一部分的粘附层(612)。所述第一粘附层可以包括正硅酸四乙酯(teos)氧化层。所述第一粘附层可以形成为单层teos氧化物。该方法还包括:形成耦合至第一粘附层的导电层(614)。所述导电层可以为多晶硅层。所述导电层可以形成为单层多晶硅。

80.所述方法还包括:形成耦合至第一粘附层的至少一部分的第二粘附层(616),以及形成阻挡壳(618)。所述第二粘附层可以形成为单层teos氧化物。所述阻挡壳可以形成为单层氮化硅或者形成为形成该阻挡壳的一系列的子层。

81.一旦通过步骤610至618形成所述支撑结构,所述方法进一步包括:将键合层(例如,氧化硅层)接合至所述支撑结构(620);以及将单晶硅层或者实质单晶层接合至所述氧化硅层(622)。所述键合层的接合可包括键合材料的沉积,随后进行本文所描述的平坦化处理。在如下文描述的一个实施例中,使用层转移工艺将单晶层(例如,单晶硅层)接合至键合层,其中,所述单晶硅层从硅晶片转移。

82.应当理解的是,图6中所示出的具体步骤提供了制造根据本发明的另一个实施例的工程化衬底的特殊方法。根据可替代的实施例,也可以执行其他的步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图6中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特定的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

83.图7为示出了根据本发明的实施例的用于rf和功率应用的外延/工程化衬底结构700的简化的截面示意图。在一些led应用中,所述工程化衬底结构提供了生长衬底,该生长衬底可以实现高质量的氮化镓层的生长并且随后移除该工程化衬底结构。但是,对于rf和功率器件应用,所述工程化衬底结构形成了成品器件的一部分,并且结果是,该工程化衬底结构或者工程化衬底结构的组成部分的电、热和其他特性对于这些特定应用来说是重要的。

84.参见图1,所述单晶层122可以是利用注入和剥离技术从硅施主晶片剥离的剥离单晶硅层。典型的注入物是氢和硼。对于功率器件和rf器件应用,在工程化衬底结构中的层和材料的电特性是很重要的。例如,一些器件构架使用具有大于103ohm-cm的电阻的高绝缘硅层,来减少或者消除衬底和界面层的泄漏。其他应用所使用的设计包括具有预定厚度(例如,1μm)的导电硅层,以便将器件的源连接至其他元件。因此,在这些应用中,希望控制单晶硅层的尺寸和特性。在层转移期间使用注入和剥离技术的设计中,剩余的注入原子(例如,氢或硼)存在于硅层中,从而改变了电特性。此外,利用例如注入计量(其可以影响导电性)和注入深度(其可以影响层厚度)的调整,很难控制薄硅层的厚度、导电性和其他特性。

85.根据本发明的实施例,利用工程化衬底结构上的硅外延来获得适合于特定器件设计的所期望的单晶硅层的性能。

86.参见图7,外延/工程化衬底结构700包括工程化衬底结构710和形成在该工程化衬底结构上的外延单晶层720。在一些实施例中,所述外延单晶层720可以为单晶硅层。所述工程化衬底结构710可以与图1、图3和图4中示出的工程化衬底结构类似。典型地,在层转移之后所述单晶层122(例如,单晶硅层)大约为0.5μm。在一些过程中,可以使用表面处理工艺将

单晶层122的厚度减少至大约0.3μm。为了将单晶层122的厚度增加到大约1μm以用于形成可靠的欧姆接触,例如,使用外延工艺在由层转移工艺形成的单晶层122上生长外延单晶层720。可以使用多种外延生长工艺来生长所述外延单晶层720,包括:cvd、lpcvd、ald(原子层沉积)、mbe(分子束外延)等。所述外延单晶层720可以包括,例如,硅、碳化硅、蓝宝石、氮化镓、氮化铝、锗硅、锗、金刚石、三氧化二镓和/或氧化锌。外延单晶层720的厚度可以在大约0.1μm到大约20μm的范围内,例如,在0.1μm至10μm之间。

87.图8a为示出了根据本发明的实施例的在工程化衬底结构上的iii-v族外延层的简化的截面示意图。图8a中示出的结构可以被称为如下文所描述的双外延结构800。如图8a所示,一种工程化衬底结构810,包括外延单晶层720,该外延单晶层720具有形成在其上的iii-v族外延层820。在一个实施例中,所述iii-v族外延层包括氮化镓(gan)。为了在iii-v族外延层(其可以包括多个子层)的一部分之间提供导电性,在该示例中,从iii-v族外延层820的顶面形成有穿入到外延单晶层720中的一组过孔824。图8a示出了过孔824穿过外延层820延伸至外延单晶层720。作为一个示例,这些过孔可以用于通过由过孔824提供欧姆接触,将二极管或者晶体管的电极连接至下面的层,从而释放在器件中积聚的电荷。在一些实施例中,一个或多个过孔824可以在其侧壁上绝缘,使得其不与iii-v族外延层820电连接。所述电接触可便于移除寄生电荷,从而实现功率器件的快速切换。

88.在一些实施例中,过孔826可以延伸至单晶层122。为了解决制造过孔826来连接单晶层122的困难,可以在单晶层122和单晶层720上生成额外的导电外延层822,以增加用于过孔826的目标导电层的尺寸,也就是过孔在其中终止的层的厚度。由于工程化衬底结构810的独特的cte和扩散特性,所述外延单晶层720和iii-v族外延层820可以形成为比传统衬底更厚。因此,现有的衬底技术不能支持足够无缺陷的外延层的生长,以将导电外延层822包括在器件中。在一些实施例中,所述导电外延层822可以为氮化铝、氮化铝镓、氮化镓或者充分掺杂的半导体材料。在特别的实施例中,导电外延层822的厚度可以为0.1μm至10μm。在其他的实施例中,导电外延层822的厚度可以根据半导体器件的需要而改变。在一些实施例中,可以移除所述工程化衬底结构和单晶层122,以暴露外延单晶层720和/或导电外延层822。在衬底移除之后可以在暴露的外延层上形成接触。本领域普通技术人员可以意识到多种变化、修改和替代。

89.在一些实施例中,iii-v族外延层可以在单晶层122上生长。为了终止单晶层122中的过孔,利用了过孔的欧姆接触可以跨过整个晶片形成在0.3μm的单晶层中。通过使用本发明的实施例,可以提供厚度为若干微米的单晶层。由于大注入深度需要高注入能量,使用注入和剥离工艺很难获得多个微米的厚度。进而,厚的外延单晶层使得应用(例如所示出的过孔)可以实现多种器件设计。

90.除了通过在单晶层122上外延生长外延单晶层720来增加“层”的厚度,也可以对外延单晶层122的原始特性进行其他调整,所述原始特性包括导电性、结晶性的修改等。例如,如果在iii-v族层或其他材料的额外外延生长之前需要大约10μm的硅层,则可根据本发明的实施例生长这样的厚层。

91.注入工艺会影响单晶层122的特性,例如,残留的硼/氢原子会导致影响了硅晶体层的电特性的缺陷。在本发明的一些实施例中,在外延单晶层720的外延生长之前,可以移除单晶层122的一部分。例如,通过单晶硅层可以被减薄,以形成0.1μm或者小于0.1μm厚度

的层,移除大部分或者全部残余的硼/氢原子。使用单晶硅层的随后生长来提供具有电特性和/或实质上与使用层转移工艺形成的层的相应特性无关的其他特性的单晶材料。

92.除了增加耦合至工程化衬底结构的单晶硅材料的厚度,包括有外延单晶层720的导电性的电特性可以与单晶层122的电特性不同。在生长期间的外延单晶层720的掺杂可以通过掺杂硼产生p型硅和通过掺杂磷产生n型硅。可以生长未掺杂的硅,以提供在具有绝缘区域的器件中使用的高电阻率的硅。特别地,可以在rf器件中使用所述绝缘层。

93.所述外延单晶层720的晶格常数可以在生长期间进行调整,以改变单晶层122的晶格常数从而产生应变外延材料。除了硅之外,其他元素也可以外延生长以提供层(包括应变层),所述元素包括锗硅等。此外,晶面的晶体取向(例如在(100)硅上生长(111)硅)可用于引入应变。例如,可以在单晶层122上、外延单晶层720上、或者层之间生长缓冲层,以提高随后的外延生长。这些缓冲层可以包括iii-v族半导体材料层,例如氮化铝镓、氮化铟镓、和氮化铟铝镓、锗硅应力层等。为了所期望的材料特性,可以调整所述iii-v族半导体材料层的应力。此外,所述缓冲层和其他外延层可以按摩尔分数、掺杂剂、极性等进行分级。本领域普通技术人员可以意识到多种变化、修改和替代。

94.在一些实施例中,在单晶层122或者外延单晶层720中存在的应力在后续外延层(包括有iii-v族外延层)的生长期间可以被释放。

95.图8b为示出了根据本发明的实施例的四个双外延结构的简化的平面图。在图8b中示出的每一个双外延结构包括一组过孔824。第一双外延结构830示出了紧凑的过孔配置。第二双外延结构840示出了分散的过孔配置。所述分散的过孔配置在更有可能经历电荷积聚的器件的活跃区域中使用过孔824。第三双外延结构850示出了图案过孔配置。所述图案过孔配置可以将过孔824在整个双外延结构850上以等距间隔开。第四双外延结构860示出了横向过孔828。所述衡向过孔828可以被制作成实质上平行于双外延结构860的外延层而行进,并且例如在边缘862处与单晶层122接触。本领域普通技术人员可以意识到多种变化、修改和替代。

96.如上文所描述的工程化衬底可以提供在工程化衬底上的氮化镓器件层的外延层生长,该氮化镓器件层可以与工程化衬底实质上晶格匹配并且具有热膨胀系数(cte)与工程化衬底的热膨胀系数实质上匹配的特点。因此,所述工程化衬底可以提供非常好的热稳定性以及形状控制。该工程化衬底还可以实现晶片直径缩放,具有再使用能力。在无裂纹且具有低缺陷密度并且低的外延后弯曲和应力特点的工程化衬底上可以形成相对较厚(例如,大于20μm)的高质量外延氮化镓层。多种应用(例如,功率器件、射频(rf)器件、单片式微波集成电路(mmic)、显示器、发光二极管(led)等)可以实现在单个的平台上。这种工程化衬底也可以适用于各种器件架构,例如横向器件、垂直器件、芯片级封装(csp)器件等。

97.氮化镓(gan)和类似的宽带隙半导体材料提供优于硅的物理性能,这使得基于这些材料的功率半导体器件能够承受高电压和高温。这些特性还允许更高的频率响应、更大的电流密度和更快的切换。但是,在宽带隙器件能获得商业认可之前,它们的可靠性必须得到验证,并且对更高可靠性的需求也在不断增长。持续地推动以获得在器件和封装层级上的更大的功率密度,在整个封装上的较高温度和温度梯度方面产生了影响。如下文所述,利用工程化衬底用于形成cte匹配的外延器件层可以缓解许多对于宽带隙器件常见的热相关失效机制。

98.化合物半导体器件(例如基于氮化镓(gan)的高电子迁移率晶体管(hemt)),在被驱动进入深度饱和的同时,可能经受高电场和高电流(例如,大信号射频)。接触退化、逆压电效应、热电子效应和自发热是一些常见的问题。例如,肖特基(schottky)和欧姆接触可能会显示出接触电阻的增加,并且在温度超过约300℃时会出现钝化开裂。可能会发生栅极金属叠层中的互扩散以及镓外扩散(out-diffusion)到金属层中。当在大电场中加速的电子获得很高的动能时,产生热电子效应。所述热电子效应可能导致在氮化铝镓(algan)层、氮化铝镓/氮化镓界面、钝化层/氮化镓覆盖层界面处以及缓冲层中形成阱。

99.所述阱的形成进而会导致电流崩塌和栅极延迟(gate lag),从而导致跨导和饱和漏极电流的可逆退化。即使漏极电压或栅极电压突然改变,也会观察到慢电流瞬变。当漏极-源极电压被脉冲化时漏极电流的慢瞬变响应被称为漏极延迟(drain lag),或者在栅极-源极电压的情况下,被称为栅极延迟。当脉冲中的电压高于静态偏置点时,缓冲阱捕获自由电荷。与脉冲长度相比,这种现象是非常快的。当脉冲中的电压高于静态偏置点时,阱释放其电荷。该过程可以非常缓慢,甚至可以在几秒内。由于自由载流子被捕获和释放,它们不会导致瞬时输出电流。这种现象出现在电流瞬变的初始。

100.漏极延迟和栅极延迟的组合效应导致了电流崩塌(二维电子气[2-deg]密度降低)。当缓冲层中的深受主密度较高时,由于缓冲阱导致的栅极延迟变得更加显著。当栅极上的高反向偏压导致晶体缺陷的产生时,可能会产生逆压电效应。超出了一定的临界电压,会发生对器件的不可逆的损伤,该损伤可以通过缺陷提供泄漏路径。在高功率应力下可能发生自发热,并可能导致热应力应变。化合物半导体器件也会遭受电场驱动的退化,例如栅极金属化和在接触、表面和界面处的退化。栅极退化会导致电流泄漏和电介质击穿的增加。

[0101]

高温反向偏压(high temperature reverse bias,htrb)测试是用于功率器件的最常用的可靠测试中的一种测试。htrb测试在高漏极-源极偏压下评估长期稳定性。htrb测试旨在加速通过使用偏压操作条件而被热激活的失效机制。在htrb测试期间,器件样品在延长时段内(例如,1000小时),在接近最大额定结温的环境温度下,在等于或略小于最大额定反向击穿电压的电压下受到应力。根据阿伦纽斯(arrhenius)方程(其说明了反应速率的温度依赖性),该测试的高温加速了失效机制。在htrb测试期间,可能会发生分层、爆裂、器件爆破以及其他机械问题。

[0102]

在宽带隙半导体器件(如gan功率器件)的栅极电介质中,也观察到了类似于时间相关的电介质击穿(time-dependent dielectric breakdown,tddb)的失效机制(这是mosfet(金属氧化物半导体场效应晶体管)中常见的失效机制)。当栅极电介质由于长时间施加相对低的电场(与由强电场导致的立即击穿相反)而击穿时,发生了tddb。此外,温度循环(tmcl)期间的失效可以与封装应力、模制化合物、焊盘金属化、水分敏感度和其他封装级的问题相关。

[0103]

如上文所讨论的,所述工程化衬底可以具有与生长在其上的外延氮化镓器件层的cte相匹配的cte。所述外延氮化镓器件层也可以与工程化衬底晶格匹配。因此,所述外延氮化镓器件层可以具有更低缺陷密度和更高质量。通过外延生长可以形成相对厚的漂移区。此外,可以由工程化衬底制成大直径的晶片,从而降低了制造成本。所述工程化衬底可以提高器件的稳定性。例如,具有与外延氮化镓器件的cte匹配的cte可以有助于缓和热应力,该热应力是器件稳定性的关键因子。与热应力相关的器件失效可以包括热激活的漏极-源极

击穿、穿通效应、沿着沟道的击穿、穿过缓冲层的击穿。也可以减少自发热。此外,具有低缺陷密度的高质量的外延氮化镓层可以有助于提高器件的稳定性,因为一些缺陷可以被电压应力激活,并且可能导致横向泄漏和纵向泄漏。高质量的外延氮化镓层也可以解决可以影响场分布和位错密度的局部化的非化学计量区(non-stoichiometric regions)的问题。

[0104]

传统的硅基mosfet技术几乎达到了性能和切换速度的物理极限。横向基于氮化镓的高电子迁移率晶体管(high electron mobility transistor,hemt)提供了超越中低功率系统中的硅基mosfet领域的机会,所述中低功率系统如太阳能逆变器、紧凑型电源(compact power supply,pfc)、开关模式电源(switch-mode power supply,smps)、电机驱动器、rf功率放大器、固态照明(solid state lighting,ssl)、智能电网以及车辆电机驱动系统。横向氮化镓基的hemt可以提供许多其他优势中的高效率、高频率操作、低切换和传导损失。

[0105]

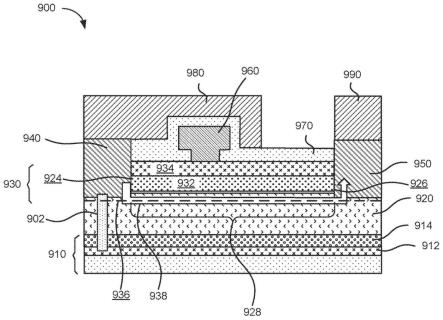

图9为示出了根据本发明的示例性实施例的形成在工程化衬底910上的功率器件900的简化的截面示意图。所述功率器件900可以用作耗尽模式(常开)hemt。功率器件900包括工程化衬底910。在一些实施例中,如参见图1、图3和图4所述的,所述工程化衬底910可以包括:多晶陶瓷芯、耦合至多晶陶瓷芯的第一粘附层、耦合至第一粘附层的阻挡层、耦合至阻挡层的键合层以及耦合至键合层的实质单晶层。根据一个实施例,所述工程化衬底910可以进一步包括耦合至键合层的实质单晶层912。例如,所述实质单晶层912可以包括实质单晶硅。在一些实施例中,所述工程化衬底910可以进一步包括耦合至实质单晶层912的成核层914,以便于包括实质单晶氮化镓基材料的外延器件层的形成。在一些实施例中,所述成核层914可以以等于、小于或高于包围层的水平进行掺杂。在其他的实施例中,所述成核层的成分可以利用预定的成分来设计并实现。

[0106]

在其他实施例中,衬底910的多晶陶瓷芯包括氮化铝。在一些实施例中,如上面参见图1所讨论的,所述衬底910可以进一步包括:耦合至第一粘附层的导电层,以及耦合至导电层的第二粘附层,其中,所述导电层和第二粘附层设置在第一粘附层与阻挡层之间。在一些实施例中,所述第一粘附层可以包括第一正硅酸乙酯(teos)氧化层,以及所述第二粘附层可以包括第二teos氧化层。所述阻挡层可以包括氮化硅层。所述导电层可以包括多晶硅层。

[0107]

根据一个实施例,所述功率器件900进一步包括耦合至所述成核层914和实质单晶层912的缓冲层920(例如,氮化镓(gan)缓冲层)。所述缓冲层920可以通过在成核层914或者实质单晶层912上进行外延生长来形成。根据一个实施例,缓冲层920可以具有大于约20微米的厚度。在一些实施例中,缓冲层920可以由氮化铝镓(即,al

x

ga

1-x

n)缓冲层来替代,或者可以为氮化镓层和氮化铝镓层的组合。应当注意的是在一些实施例中,作为氮化镓层来讨论的层可以由al

x

ga

1-x

n层替代。作为一个示例,缓冲层920可以由具有第一组摩尔分数的al

x

ga

1-x

n来替代,并且所述阻挡层932可以为具有第二组摩尔分数的al

x

ga

1-x

n。本领域普通技术人员可以意识到多种变化、修改和替代。

[0108]

较厚的缓冲层可以向功率器件900提供更低的漏电流和更高的击穿电压。在一些实施例中,所述缓冲层920可以包括多个层。例如,缓冲层920可以包括氮化铝、氮化铝镓和氮化镓层。在一些实施例中,缓冲层920可以包括具有150层的超晶格,每一层具有大约2nm至3nm的厚度。超晶格是通过周期性外延生长制成的人造晶格。周期性的超晶格是通过在彼

此顶部生长相互交叠的两个半导体层来实现的,每一个半导体每次生长相同的厚度和摩尔分数。根据本发明的一些实施例,使用超晶格而不是其他缓冲层设计的优点在于,所述超晶格可以通过在沟道区上生长(例如氮化铝镓/氮化镓)超晶格层来减小薄层电阻,并且可以降低异质界面处的潜在的势垒高度(potential barrier height)。在其他的实施例中,所述超晶格并不能降低在异质界面处的潜在的势垒高度。本领域普通技术人员可以意识到多种变化、修改和替代。

[0109]

根据一个实施例,所述功率器件900进一步包括耦合至缓冲层920的沟道区930。所述沟道区930具有第一端924、第二端926以及设置在第一端与第二端之间的中心部928。所述沟道区930的中心部可以包括沟道区阻挡层。在一些实施例中,所述沟道区阻挡层可以为耦合至缓冲层920的阻挡层932(例如,氮化铝镓(al

x

ga

1-x

n)阻挡层)以及耦合至阻挡层932的覆盖层934(例如,氮化镓覆盖层)。所述覆盖层有助于减少通过肖特基接触的反向泄漏以及减少峰值电场。还可以在处理期间保护阻挡层932并且防止氮除气。此外,所述覆盖层934对于器件性能也具有积极影响,例如增加增益、提高功率附加效率以及改善直流(dc)稳定性。

[0110]

所述功率器件900进一步包括:设置在沟道区930的第一端上的源极接触940、设置在沟道区930的第二端处的漏极接触950、以及耦合至覆盖层934并且设置在沟道区930的中心部中的栅极接触960。在一些实施例中,为了移除功率器件中的寄生电荷,过孔902可以将源极接触940连接至单晶层912。与硅上氮化镓相比(其可以利用通过导电硅衬底的背侧接触),应用了绝缘的工程化衬底的本发明的实施例可以利用过孔(例如,过孔902)提供到单晶层912的电连接。根据本发明的实施例,通过外延生长形成所述阻挡层932和覆盖层934。如图9所示,在操作中,在缓冲层920与阻挡层932之间的界面处,在缓冲层920中可以形成二维电子气(2deg)的薄层936。由于所述缓冲层920是未掺杂的,在二维电子气的薄层936中的电子可以快速移动,而不会与任何杂质相撞。这可以使沟道938具有非常低的电阻率,换句话说,具有非常高的电子迁移率。

[0111]

在一些实施例中,所述功率器件900可以进一步包括覆盖所述覆盖层934的钝化层970。所述钝化层970可以包括氮化硅或者其他绝缘材料。所述功率器件900还可以包括:电连接至所述源极接触940的第一场板金属(plate metal)(其形成源极电极)980以及设置在漏极接触950上的第二金属990(其形成漏极电极)。

[0112]

图10为示出了根据本发明的实施例的在工程化衬底上制造横向功率器件的方法1000的简化的流程图。根据一个实施例,所述方法1000包括:在1010,通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。

[0113]

所述方法1000进一步包括:在1012,在所述衬底上形成外延缓冲层(例如,氮化镓(gan)缓冲层);并且在1014,通过以下步骤在所述缓冲层上形成沟道区:在所述缓冲层上形成外延阻挡层(例如,氮化铝镓(al

x

ga

1-x

n)阻挡层);以及在所述阻挡层上形成外延覆盖层(例如,氮化镓覆盖层)。所述沟道区具有第一端、第二端以及在第一端与第二端之间的中心部。

[0114]

所述方法1000进一步包括:在1016,在所述沟道区的第一端处形成源极接触;在1018,在所述沟道区的第二端处形成漏极接触;以及在1020,在所述沟道区的中心部中在覆

盖层上形成栅极接触。

[0115]

应当理解的是,图10中所示出的具体步骤提供了制造根据本发明的另一实施例的工程化衬底的特定方法。根据可替代的实施例,也可以执行其他步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图10中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特定的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

[0116]

图11a为示出了根据本发明的其他的另一实施例的形成在工程化衬底结构上的横向功率器件1100的简化的截面示意图。所述功率器件1100可以使用沟道区1130中的凹槽1136作为增强模式(常关)hemt。功率器件1100包括工程化衬底1110。在一些实施例中,如参见图1、图3和图4所述的,所述工程化衬底1110可以包括:多晶陶瓷芯、耦合至多晶陶瓷芯的第一粘附层、耦合至第一粘附层的阻挡层、耦合至阻挡层的键合层以及耦合至键合层的实质单晶层。在一些实施例中,所述工程化衬底1110可以进一步包括耦合至键合层的实质单晶层1112。例如,所述实质单晶层1112可以包括实质单晶硅。在一些实施例中,所述工程化衬底1110可以进一步包括耦合至实质单晶层1112的成核层(未示出),以便于外延器件层的形成。

[0117]

在一个实施例中,所述衬底1110的多晶陶瓷芯包括氮化铝。在一些实施例中,如上面参见图1所讨论的,所述衬底1110可以进一步包括:耦合至第一粘附层的导电层,以及耦合至导电层的第二粘附层,其中,所述导电层和第二粘附层设置在第一粘附层与阻挡层之间。在一些实施例中,所述第一粘附层可以包括第一正硅酸乙酯(teos)氧化层,而所述第二粘附层可以包括第二teos氧化层。所述阻挡层可以包括氮化硅层。所述导电层可以包括多晶硅层。

[0118]

根据一个实施例,所述功率器件1100进一步包括耦合至实质单晶层1112的缓冲层1120(例如,氮化镓(gan)缓冲层)。所述缓冲层1120可以通过在实质单晶层1112上的外延生长来形成。根据一个实施例,缓冲层1120可以具有大于约20微米的厚度。较厚的缓冲层可以向功率器件1100提供更低的漏电流和更高的击穿电压。在一些实施例中,所述缓冲层1120可以包括多个层。例如,缓冲层1120可以为超晶格,该超晶格包括氮化铝层、氮化铝镓和氮化镓层。应当理解,在用于缓冲层1120生长的过程中可以使用一个或多个成核层。

[0119]

根据一个实施例,所述功率器件1100进一步包括耦合至缓冲层1120的沟道区1130。所述沟道区1130具有第一端1124、第二端1126以及设置在第一端1124与第二端1126之间的中心部1128。所述沟道区1130的中心部可以包括外延沟道区阻挡层。在一些实施例中,所述外延沟道区阻挡层可以为耦合至所述缓冲层1120的阻挡层1132(例如,氮化铝镓(al

x

ga

1-x

n)阻挡层)。根据本发明的实施例,通过外延生长形成所述阻挡层1132。所述阻挡层1132包括沟道区1130的中心部中的凹槽1136。可以通过利用蚀刻或者其他适用的技术移除一部分阻挡层1132来形成所述凹槽。所述功率器件110进一步包括设置在所述凹槽中并且耦合至所述阻挡层1132的绝缘层1134。

[0120]

所述功率器件1100进一步包括:设置在沟道区1130的第一端处的源极接触1140、设置在沟道区1130的第二端处的漏极接触1150、以及耦合至所述绝缘层1134并且设置在沟道区1130的中心部中的栅极接触1160。在一些实施例中,过孔1102可以用于将源极接触

1140连接至单晶层1112,以便移除功率器件1100中的寄生电荷。如图11所示,在缓冲层1120与阻挡层1132之间的界面处,在缓冲层1120中可以形成二维电子气(2deg)的薄层1138。由于所述缓冲层1120是未掺杂的,因此在2deg的薄层1138中的电子可以快速移动,而不会与任何杂质相撞。这就使沟道区1130具有非常低的电阻率,换句话说,具有非常高的电子迁移率。在耗尽模式(通常为关毕)中,当栅极电压为零时,所述凹槽1136和绝缘层1134阻挡一部分2deg。

[0121]

在一些实施例中,所述缓冲层1120可以实现为氮化铝镓(algan)缓冲层。所述氮化铝镓缓冲层可以包括多个层。使用了al

x

ga

1-x

n缓冲层的所述功率器件可以通过制造al

x

ga

1-x

n缓冲层来引入沟道区1130,所述al

x

ga

1-x

n缓冲层具有从工程化衬底延伸的第一预定摩尔分数(x)和在源极接触、栅极接触和漏极接触附近的第二预定摩尔分数(x)。所述第一预定摩尔分数(x)可以是低的,例如小于10%,以提供所期望的载流子约束。在其他的实施例中,铝摩尔分数(x)的范围是10%至30%。al

x

ga

1-x

n外延层可以用铁或碳掺杂,以进一步增加外延层的电阻率,其用作绝缘层或者阻挡层。在申请号为62/447,857的美国临时专利申请中提供了与外延缓冲层所用材料和外延缓冲层的制造有关的附加说明,其全部内容以引用方式并入本文中,以用于所有目的。

[0122]

图11b为示出了根据本发明的实施例的形成在工程化衬底结构上的具有外延栅极结构的横向功率器件1190的简化的截面示意图。所述功率器件1190可以通过利用外延栅极结构(例如,p型氮化镓基结构1162)来用作增强模式(常关)hemt,以在零偏压下耗尽沟道区中的电荷。功率器件1190包括工程化衬底1110。在一些实施例中,所述工程化衬底1110可以包括在上文参见图1、图3和图4所描述的元素。根据一个实施例,所述工程化衬底1110可以进一步包括耦合至键合层的实质单晶层1112。

[0123]

在一些实施例中,所述功率器件1190进一步包括耦合至实质单晶层1112的缓冲层1120。在一些实施例中,所述缓冲层可以为其他的单晶外延层,例如,其他的iii-v族材料(例如,氮化铝镓、氮化铟镓、氮化铟铝镓或者它们的组合等)。所述功率器件1190可以包括耦合至缓冲层1120的沟道区1130。所述沟道区的中心部可以包括耦合至缓冲层1120的阻挡层1132。根据本发明的实施例,通过外延生长形成所述阻挡层1132。

[0124]

所述功率器件1190进一步包括:设置在沟道区1130的第一端处的源极接触1140、设置在沟道区的第二端处的漏极接触1150、以及栅极接触1164。在一些实施例中,所述栅极接触1164可以为部分欧姆接触或者为半欧姆接触,例如,氮化钛。部分欧姆栅极接触1164可以耦合至p型氮化镓结构1162。所述部分欧姆栅极接触1164的作用是阻挡漏电流(如果存在完全的欧姆接触则漏电流会流出)。可以通过选择性地蚀刻p型氮化镓外延层来形成p型氮化镓结构1162。在一些实施例中,可以利用多个外延层来形成所述p型氮化镓结构1162。当利用多个外延层时,一个或多个层可以包括具有多种成分的材料,该成分与阻挡层1132的成分不同或者彼此成分不同,例如氮化铝镓等。

[0125]

可以调节与p型氮化镓结构1162相关联的特性(例如,应力或者压电特性),以减少或者限制漏电流。p型氮化镓结构中的每一层可以具有不同的掺杂剂浓度。在一些实施例中,当栅极电压为零时,所述p型氮化镓结构1162耗尽一部分沟道区1130。所述耗尽区使得功率器件1190用作增强模式(常关)hemt。

[0126]

图11c为示出了p型氮化镓结构1162的分解视图的简化的截面示意图。在一些实施

例中,第一层1170可以具有第一掺杂剂浓度和/或材料成分。第二层1172可以具有第二掺杂剂浓度和/或材料成分。第三层1174可以具有第三掺杂剂浓度和/或材料成分。与现有的衬底技术相比,工程化衬底1110的独特的cte匹配特性提供了能够支持更厚、更复杂的外延层生长的衬底。在一些实施例中,所述外延栅极结构可以包括至少一个p型氮化镓外延层。通过层特定的掺杂剂浓度和/或材料成分,功率器件1190的漏电流可以得到控制。虽然图11c示出了三个外延层,但是本领域普通技术人员可以意识到多种变化、修改和替代。

[0127]

图12为示出了根据本发明的实施例的制造工程化衬底上的横向功率器件的方法1200的简化的流程图。根据一个实施例,所述方法1200包括:在1210,通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。

[0128]

所述方法1200进一步包括:在1212,在所述衬底上形成外延缓冲层(例如,氮化镓(gan)缓冲层);以及在1214,通过在所述缓冲层上形成外延阻挡层(例如,氮化铝镓(al

x

ga

1-x

n)挡层),在所述缓冲层上形成沟道区。所述沟道区具有第一端、第二端以及在第一端与第二端之间的中心部。根据一个实施例,所述方法1200进一步包括:在1216,在沟道区的中心部中的阻挡层中形成凹槽;以及在1218,在所述凹槽中形成绝缘层。所述绝缘层耦合至阻挡层。所述方法1200进一步包括:在1220,在所述沟道区的第一端处形成源极接触;在1222,在所述沟道区的第二端处形成漏极接触;以及在1224,在所述沟道区的中心部中的绝缘层上形成栅极接触。

[0129]

应当理解的是,图12中所示出的具体步骤提供了制造根据本发明的另一个实施例的工程化衬底的特定方法。根据可替代的实施例,也可以执行其他的步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图12中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特定的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

[0130]

垂直器件(p-n型二极管和hemt)的大功率模块可以具有多种应用。例如,它们可以用于驱动混合动力车辆功率系统中的主电机和工业电机。由于对高电压和大电流的同时需求,因此对这些器件提出了特定的挑战。当前,这些系统典型地使用基于硅碳的器件。由于基于氮化镓基的器件的开关性能(其提供了更小的占用空间),目前对基于氮化镓的器件的使用越来越感兴趣。如上文所描述的工程化衬底可以提供在可兼容cmos的硅晶片厂中大规模地制造氮化镓基器件的潜力。

[0131]

图13为示出了根据本发明的实施例的形成在工程化衬底结构上的垂直半导体二极管1300的简化的截面示意图。所述半导体二极管1300包括工程化衬底1310。在一些实施例中,如上文参见图1、图3和图4所述的,所述工程化衬底1310可以包括:多晶陶瓷芯、耦合至多晶陶瓷芯的第一粘附层、耦合至第一粘附层的阻挡层、耦合至阻挡层的键合层以及耦合至键合层的实质单晶层。根据一个实施例,所述工程化衬底1310可以进一步包括耦合至键合层的实质单晶层1312。例如,所述实质单晶层1312可以包括实质单晶硅。在一些实施例中,所述工程化衬底1310可以进一步包括耦合至实质单晶层1312的成核层(未示出),以便于外延器件层的形成。

[0132]

在一个实施例中,所述衬底1310的多晶陶瓷芯包括氮化铝。在一些实施例中,如上

文参见图1所讨论的,所述衬底1310可以进一步包括:耦合至第一粘附层的导电层,以及耦合至导电层的第二粘附层,其中,所述导电层和第二粘附层设置在第一粘附层与阻挡层之间。在一些实施例中,所述第一粘附层可以包括第一正硅酸乙酯(teos)氧化层,以及所述第二粘附层可以包括第二teos氧化层。所述阻挡层可以包括氮化硅层。所述导电层可以包括多晶硅层。

[0133]

根据一个实施例,所述半导体二极管1300进一步包括耦合至实质单晶层1312的缓冲层1320。在一些实施例中,所述缓冲层1320可以为超晶格,该超晶格包括多个层。例如,所述缓冲层1320可以包括:耦合至单晶硅层的氮化铝层、耦合至所述氮化铝层的氮化铝镓层以及耦合至所述氮化铝镓层的氮化镓层。所述半导体二极管1300进一步包括耦合至缓冲层1320的半绝缘层1330。在一个实施例中,所述半绝缘层1330包括氮化镓。

[0134]

根据一些实施例,所述半导体二极管1300进一步包括:耦合至半绝缘层1330的第一n型氮化镓层1342、耦合至所述第一n型氮化镓层1342的第二n型氮化镓层1344,以及耦合至所述第二n型氮化镓层1344的p型氮化镓层1346。所述第一n型氮化镓层1342可以用作p-n二极管的n区,并且具有相对高的n型掺杂剂浓度。所述第二n型氮化镓层1344可以用作漂移区,并且具有与所述第一n型氮化镓层1342的掺杂剂浓度相比相对低的掺杂剂浓度。所述p型氮化镓层1346可以用作p-n二极管的p区,并且具有相对高的p型掺杂剂浓度。

[0135]

在一个实施例中,移除一部分第二n型氮化镓层1344以及一部分p型氮化镓层1346,以暴露第一n型氮化镓层1342的一部分,从而可以在第一n型氮化镓层1342上形成阴极接触1370。在一些实施例中,所述阴极接触1370可以包括钛铝(ti/al)合金或者其他合适的金属材料。可以通过蚀刻或者其他合适的技术来移除第二n型氮化镓层1344的一部分以及p型氮化镓层1346的一部分。在p型氮化镓层1346的剩余部分上形成阳极接触1360。在一些实施例中,所述阳极接触1360可以包括镍铂合金(ni/pt)、镍金(ni/au)合金等。所述半导体二极管1300可以进一步包括:耦合至阳极接触1360的第一场板1382以及耦合至阴极接触1370的第二场板1370。在一些实施例中,半导体二极管1300可以进一步包括钝化层1390,该钝化层1390覆盖所述p型氮化镓层1346、第一n型氮化镓层1342和第二n型氮化镓层1344的暴露表面。所述钝化层1390可以包括氮化硅或者其他绝缘材料。

[0136]

在一些实施例中,所述第二n型氮化镓层1344可以具有大于约20μm的厚度。所述工程化衬底1310的独特的cte匹配特性提供了沉积相对厚的漂移区的能力,其中低位错密度可以向半导体二极管1300提供低漏电流和更高的击穿电压以及一些其他优点。

[0137]

图14为示出了根据本发明的实施例的制造工程化衬底上的垂直半导体二极管的方法1400的简化的流程图。所述方法1400包括:在1410,通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。

[0138]

该方法1400进一步包括:在1412,在所述单晶硅层上形成缓冲层;以及在1414,在所述缓冲层上形成半绝缘层。方法1400进一步包括:在1416,在所述半绝缘层上形成第一外延n型氮化镓层;在1418,在所述第一外延n型氮化镓层上形成第二外延n型氮化镓层;以及在1420,在所述第二外延n型氮化镓层上形成外延p型氮化镓层。根据一些实施例,所述第一外延n型氮化镓层具有第一掺杂剂浓度。所述第二外延n型氮化镓层具有比所述第一掺杂剂浓度小的第二掺杂剂浓度。

[0139]

根据一些实施例,所述方法1400进一步包括:在1422,移除第二外延n型氮化镓层的一部分以及外延p型氮化镓层的一部分,以暴露第一外延n型氮化镓层的一部分。该方法1400进一步包括:在1424,在所述外延p型氮化镓层的剩余部分上形成阳极接触;以及在1426,在所述第一外延n型氮化镓层的暴露部分上形成阴极接触。

[0140]

应当理解的是,图14中所示出的具体步骤提供了制造根据本发明的另一个实施例的工程化衬底的特定方法。根据可替代的实施例,也可以执行其他的步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图14中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特殊的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

[0141]

图15为示出了根据本发明的另一个实施例的形成在工程化衬底结构上的垂直半导体二极管1500的简化的截面示意图。所述垂直半导体二极管可以包括:耦合至阴极接触1570的第一n型氮化镓层1542(其可以包括钛/铝材料)、耦合至第一n型氮化镓层1542的第二n型氮化镓层1544,以及耦合至所述第二n型氮化镓层1544的p型氮化镓层1546。所述第一n型氮化镓层可以用作p-n二极管的n区,并且具有相对高的n型掺杂剂浓度。所述第二n型氮化镓层1544可以作为漂移区,并且可以具有与所述第一n型氮化镓层1542的掺杂剂浓度相比相对低的掺杂剂浓度。所述p型氮化镓层1546可以用作p-n二极管的p区,并且可以具有相对高的p型掺杂剂浓度。在一些实施例中,可以利用外延层来生长所述第一n型氮化镓层1542、p型氮化镓层1546以及第二n型氮化镓层1544。如在上文参见图1、图3和图4所描述的,可以在工程化衬底上生长所述外延层。所述外延层可以具有至少10μm的厚度并且具有6英寸的直径。

[0142]

所述垂直半导体二极管1500类似于半导体二极管1300,只是在p-n二极管形成后移除衬底1310、缓冲层1320和半绝缘层1330,从而形成了在晶片的相对侧上具有阳极1560和阴极1584的“真正”的垂直器件结构。在可替代的实施例中,所述衬底1310、缓冲层1320和半绝缘层1330的部分形成接触窗。所述接触窗可以用于创建在晶片的相对侧上具有阳极1560和阴极1584的垂直器件结构。

[0143]

在一些实施例中,通过从图13所示的结构中移除工程化衬底1310、缓冲层1320和半绝缘层1330,可以降低垂直半导体二极管1500的热阻。在一些实施例中,所述垂直半导体二极管1500可以转移至铜,其可以作为阴极电接触。镀铜也可以用作垂直半导体二极管1500的热沉。所述铜可以具有30μm的厚度,所述第一n型氮化镓层1542、第二n型氮化镓层1544和p型氮化镓层1546的组合的厚度可以小于或等于150μm。在该实施例中,所述垂直半导体二极管的热阻可以小于或等于0.2k*mm2/w。在该实施例中,所述热阻可以为利用氮化镓衬底上的外延氮化镓形成的二极管的四分之一。

[0144]

在其他的实施例中,可以形成沉积的金刚石层来提供到第一n型氮化镓层的电连接,以改善热阻和/或提供阴极电接触1584。可以使用化学气相沉积来形成沉积的金刚石层。可以对所述沉积的金刚石层进行掺杂以形成n型金刚石层。所述沉积的金刚石层可以为用于功率器件的热沉。在一些实施例中,该沉积的金刚石层可以具有20μm至50μm的厚度。应当理解的是,材料的组合可以用于形成阴极电接触,包括铜和沉积的金刚石层。

[0145]

在一些配置中,与衬底毗邻的外延层与远离与衬底的界面生长的外延层相比,具

有更高的缺陷发生率。这些缺陷可以包括,例如,杂质、晶体失配和位错。这些初始层中的缺陷可以占器件电阻的高百分比。图13示出的工程化衬底1310的独特的cte匹配特性允许与工程化衬底1310毗邻的第一n型氮化镓层1542比生长在传统衬底上的外延层更厚。在一些实施例中,除了移除工程化衬底1310,也可以移除与该工程化衬底1310毗邻的第一n型氮化镓层1542。在一些实施例中,在移除了衬底以及初始的较高缺陷的外延层之后,所述阴极电接触1584可以直接地形成在高质量的氮化镓外延层上。

[0146]

虽然工程化衬底的移除增加了额外的过程步骤,但是因为功率处理接触形成在晶片的两个不同侧面上,因此可以缓解金属化,从而改善了电流扩散和热提取,并且减少了电阻。在一些实施例中,为了提供低电阻,所述n型氮化镓层1542可以具有3

×

10

18

cm-3

至5

×

10

18

cm-3

级别的掺杂剂浓度。在一些实施例中,所述电阻可以小于或等于0.1ohm*mm2。此外,对于图13所示出的垂直半导体二极管1300,所述阳极接触1360可以不太接近与阴极接触1370毗邻的侧壁,这是因为否则在阳极接触1360与阴极接触1370之间可能存在击穿。所述垂直半导体二极管1500排除了这种可能性。

[0147]

图16为示出了根据本发明的实施例的在工程化衬底上制造垂直半导体二极管的方法1600的简化的流程图。所述方法1600包括:在1610,通过以下步骤形成衬底:提供多晶陶瓷芯;利用第一粘附壳封装所述多晶陶瓷芯;利用阻挡层封装所述第一粘附壳;在所述阻挡层上形成键合层;以及将实质单晶层接合至所述键合层。

[0148]

该方法1600进一步包括:在1612,在所述单晶硅层上形成缓冲层;以及在1614,在所述缓冲层上形成半绝缘层。方法1600进一步包括:在1616,在所述半绝缘层上形成第一外延n型氮化镓层;在1618,在所述第一外延n型氮化镓层上形成第二外延n型氮化镓层;以及在1620,在所述第二外延n型氮化镓层上形成外延p型氮化镓层。根据一些实施例,所述第一外延n型氮化镓层具有第一掺杂剂浓度。所述第二外延n型氮化镓层具有比所述第一掺杂剂浓度小的第二掺杂剂浓度。

[0149]

根据一些实施例,所述方法1600进一步包括:在1622,移除衬底、缓冲层和半绝缘层,以暴露所述第一n型氮化镓层的底面。在一些实施例中,可以移除所述第一n型氮化镓层的初始层。可以使用一些技术来移除所述工程化衬底、缓冲层和半绝缘层。例如,可以将化学物质(例如,氢氟酸(hf))注入到保留有垂直半导体二极管的晶片的侧面,以蚀刻出一个或多个缓冲层和半绝缘层,而陶瓷芯和垂直半导体二极管外延叠层保持完整。蚀刻一个或多个缓冲层和半绝缘层将垂直半导体二极管外延叠层与工程化衬底的剩余部分分离,而保留陶瓷芯,用于再次使用。这种化学剥离工艺也通过取消抛光工艺减少了垂直半导体二极管外延叠层上的整体应力。如果使用氮化镓衬底,则不能选择性地移除该衬底。此外,所述氮化镓衬底包括例如为面翻转、残余应力、易碎性和错切平面等缺陷,这些缺陷影响生长在该氮化镓衬底上的外延层的质量。在利用氮化镓衬底的一些实施例中,75%的电阻可以归因于衬底中的缺陷。本发明的实施例(其将衬底移除以暴露用于接触形成的外延层)可以减少电阻和热阻。

[0150]

在一些实施例中,可以使用牺牲层以用于所述化学剥离工艺。所述牺牲层可以使用当暴露到hf时极易溶解的金属(例如,钛(ti))。在一些实施例中,所述牺牲层可以包括:钛(ti)、钒(v)、铬(cr)、钽(ta)、钨(w)、铼(re)、氧化硅、氮化硅、氮氧化硅中的一种或者它们的组合。除了牺牲层,也可以使用保护层。所述保护层可以防止在外延氮化镓生长期间,

金属(例如,钛)从牺牲层200扩散至氮化镓外延层中。在申请号为15/288,506的美国专利申请提供了关于移除衬底、缓冲层和半绝缘层的附加描述,其全部内容以引用方式并入本文中,以用于所有目的。在关于垂直半导体二极管所描述的衬底移除过程也可以用于本文所描述的任何一种器件。本领域普通技术人员可以意识到多种变化、修改和替代。

[0151]

所述方法进一步包括:在1624,在所述外延p型氮化镓层上形成阳极接触;以及在1626,在所述第一外延n型氮化镓层的底面上形成阴极接触。

[0152]

应当理解的是,图16中所示出的具体步骤提供了根据本发明的另一个实施例的制造工程化衬底的特定方法。根据可替代的实施例,也可以执行其他的步骤顺序。例如,本发明的可替代的实施例可以以不同的顺序执行上述步骤。此外,图16中所示出的单独的步骤可以包括多个子步骤,这些子步骤可以以适合于单独步骤的各种顺序来执行。另外,根据特定的应用,可以增加或移除额外的步骤。本领域普通技术人员可以意识到多种变化、修改和替代。

[0153]

所述功率器件可以在恶劣的热条件下进行操作。例如,其可以经历高达几百摄氏度的热循环。一些局部的热点可以高至250℃(摄氏度)。所述热循环和内在应力可能导致了可靠性失效,例如,分层、电介质的击穿等。因此,在工程化衬底上形成氮化镓器件层(其具有工程化衬底的cte与功率器件的cte实质上匹配的特点)可以消除或缓解这样的可靠性失效,这是因为氮化镓器件层可以与工程化衬底以相同的速率膨胀和收缩。

[0154]

图17为示出了根据本发明的实施例的形成在工程化衬底1710上的半导体器件1700的简化的截面示意图。所述半导体器件1700包括衬底1710。在一些实施例中,如参见图1、图3和图4所上述的,所述工程化衬底1710可以包括:多晶陶瓷芯、耦合至多晶陶瓷芯的第一粘附层、耦合至第一粘附层的阻挡层、耦合至阻挡层的键合层以及耦合至键合层的实质单晶层。根据一个实施例,所述工程化衬底1710可以进一步包括耦合至键合层的实质单晶层。例如,所述实质单晶层可以包括实质单晶硅。

[0155]

在一个实施例中,所述衬底1710的多晶陶瓷芯包括氮化铝。在一些实施例中,如上文参见图1所讨论的,所述衬底1710可以进一步包括:耦合至第一粘附层的导电层,以及耦合至导电层的第二粘附层,其中,所述导电层和第二粘附层设置在第一粘附层与阻挡层之间。在一些实施例中,所述第一粘附层可以包括第一正硅酸乙酯(teos)氧化层,以及所述第二粘附层可以包括第二teos氧化层。所述阻挡层可以包括氮化硅层。所述导电层可以包括多晶硅层。

[0156]

所述半导体器件1700包括形成在工程化衬底1710上的器件结构1720。根据一些实施例,所述器件结构1720可以包括生长在衬底1710的实质单晶层上的多个外延氮化镓基层,其中,多个外延氮化镓层的热膨胀系数实质上上等于衬底1710的热膨胀系数。

[0157]

同样应该理解,本文描述的示例和实施例仅用于说明目的,并且对于本领域技术人员而言,将启发其对本发明进行各种修改或改变,并且这些修改或改变被包括在本技术的精神和范围内和所附权利要求的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。