1.本技术案主张2021年9月8日申请的美国正式申请案第17/469,010号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开关于一种半导体元件及其制备方法,特别是关于一种具有不同图案密度的导电层的半导体元件及其制备方法。

背景技术:

3.半导体元件被用于各种电子应用,如个人电脑、移动电话、数码相机和其他电子装置。半导体元件的尺寸正在不断缩小,以满足日益增长的计算能力的需求。然而,在缩小尺寸的过程中出现了各种问题,而且这种问题在不断增加。因此,在实现提高品质、产量、性能和可靠性以及降低复杂性方面仍然存在挑战。

4.上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现要素:

5.本公开的一实施例提供一种半导体元件,包括一基底、多个密集导电层、以及多个松散导电层。该基底包括一密集图案区和与该密集图案区相邻设置的一松散图案区。该多个密集导电层设置在该基底的该密集图案区上。该多个松散导电层设置在该基底的该松散图案区上。该多个密集导电层的相邻对之间距离小于该多个松散导电层的相邻对之间距离。

6.在一些实施例中,该多个密集导电层的元件密度(element density)大于该多个松散导电层的元件密度。

7.本公开的另一实施例提供一种半导体元件的制备方法,包括:提供包括一密集图案区和一松散图案区的一基底,并在该密集图案区和该松散图案区上依次形成一导电堆叠和一第一硬遮罩层;对该第一硬遮罩层进行图案化,在该密集图案区上方形成多个密集图案层;形成覆盖该第一硬遮罩层和该多个密集图案层的一第二硬遮罩层;对该第二硬遮罩层进行图案化,在该松散图案区上方形成多个松散封盖层;使用该多个松散封盖层作为遮罩,在该松散图案区上方对该第一硬遮罩层进行图案化,以在该松散图案区上方形成多个松散图案层,并移除该第二硬遮罩层和该多个松散封盖层;以及使用该多个密集图案层和该多个松散图案层作为遮罩对该导电堆叠进行图案化,在该密集图案区上方形成多个密集导电层,在该松散图案区上方形成多个松散导电层。该多个密集导电层的相邻对之间距离小于该多个松散导电层的相邻对之间距离。

8.在一些实施例中,该密集图案区和该松散图案区彼此相邻。

9.在一些实施例中,该多个密集导电层的元件密度大于该多个松散导电层的元件密度。

10.在一些实施例中,该第一硬遮罩层包括氮化硅。

11.在一些实施例中,对该第一硬遮罩层进行图案化,在该密集图案区上方形成该多个密集图案层,包括:在该第一硬遮罩层上形成一第一遮罩层,其中该第一遮罩层完全覆盖该松散图案区,部分覆盖该密集图案区;以及使用该第一遮罩层作为遮罩进行一密集区蚀刻制程,在该密集图案区上方形成多个密集图案层。

12.在一些实施例中,对该第二硬遮罩层进行图案化,在该松散图案区上方形成该多个松散封盖层,包括:在该第二硬遮罩层上形成一第二遮罩层,其中该第二遮罩层完全覆盖该密集图案区,部分覆盖该松散图案区;以及使用该第二遮罩层作为遮罩进行一第一松散区蚀刻制程,在该松散图案区域上方形成多个松散封盖层。

13.在一些实施例中,该密集区蚀刻制程的蚀刻气体包括三氯化硼和氯。

14.在一些实施例中,该第一松散区蚀刻制程的蚀刻气体包括三氯化硼和氯。

15.在一些实施例中,该密集区蚀刻制程的三氯化硼与氯的比率大于该第一松散区蚀刻制程的三氯化硼与氯的比率。

16.在一些实施例中,该密集区蚀刻制程的功率比小于该第一松散区蚀刻制程的功率比。

17.在一些实施例中,该第二硬遮罩层包括与该第一硬遮罩层不同的材料。

18.在一些实施例中,该第二硬遮罩层包括碳膜、介电质材料或抗反射涂层。

19.在一些实施例中,该导电堆叠包括一底部导电层、一中间导电层和一顶部导电层。

20.在一些实施例中,该底部导电层包括钛。

21.在一些实施例中,该中间导电层包括铝铜合金。

22.在一些实施例中,该顶部导电层包括钛/氮化钛双层。

23.在一些实施例中,在该密集区蚀刻制程中,化学蚀刻量大于物理蚀刻量。

24.在一些实施例中,在该第一松散区蚀刻制程中,化学蚀刻量小于物理蚀刻量。

25.由于本公开的半导体元件的设计,借由采用第一硬遮罩层和第二硬遮罩层,具有不同元件密度的多个密集导电层和多个松散导电层可以容易地积集(integrated)在半导体元件中。因此,制备半导体元件的复杂性可以降低。相应地,半导体元件的产量可以提高。

26.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求书标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求书所定义的本公开的精神和范围。

附图说明

27.参阅实施方式与权利要求书合并考量图式时,可得以更全面了解本技术的揭示内容,图式中相同的元件符号是指相同的元件。

28.图1是流程图,例示本公开一实施例的半导体元件的制备方法。

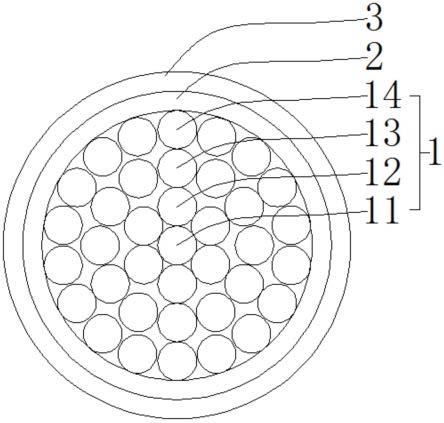

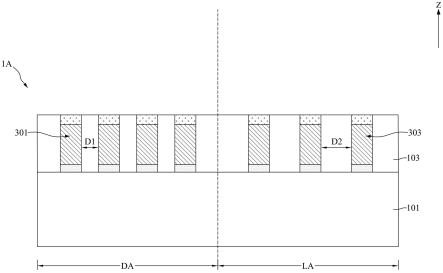

29.图2至图13例示本公开一实施例的半导体元件的制备流程的剖视示意图。

30.图14例示本公开一实施例的用于制备半导体元件的一些蚀刻制程中的蚀刻反应

器的示意图。

31.其中,附图标记说明如下:

32.1a:半导体元件

33.10:制备方法

34.101:基底

35.103:顶部介电质层

36.201:底部导电层

37.203:中间导电层

38.205:顶部导电层

39.301:密集导电层

40.303:松散导电层

41.401:第一硬遮罩层

42.401d:密集图案层

43.401l:松散图案层

44.403:第二硬遮罩层

45.403l:松散封盖层

46.501:第一遮罩层

47.503:第二遮罩层

48.600:蚀刻反应器

49.601:控制器

50.603:射频源

51.605:气体源

52.607:蚀刻室

53.609:室壁

54.611:通道

55.613:冷却器

56.615:排气泵

57.617:气体分配板

58.619:静电吸盘(esc)

59.621:静电吸盘温度控制器

60.623:静电吸盘源

61.627:冷却剂

62.d1:距离

63.d2:距离

64.da:密集图案区

65.la:松散图案区

66.s11:步骤

67.s13:步骤

68.s15:步骤

69.s17:步骤

70.s19:步骤

71.sk:导电堆叠

72.z:方向

具体实施方式

73.本公开的以下说明伴随并入且组成说明书的一部分的图式,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

[0074]“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等系指本公开所描述的实施例可以包括特定特征、结构或是特性,然而并非每一实施例必须包括该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

[0075]

以下公开内容提供作为实作本公开的不同特征的诸多不同的实施例或实例。以下阐述组件及排列形式的具体实施例或实例以简化本公开内容。当然,这些仅为实例且不旨在进行限制。举例而言,元件的尺寸并非仅限于所公开范围或值,而是可相依于制程条件及/或元件的所期望性质。此外,以下说明中将第一特征形成于第二特征“之上”或第二特征“上”可以包括其中第一特征及第二特征被形成为直接接触的实施例,且亦可以包括其中第一特征与第二特征的范围内可形成有附加特征、进而使得所述第一特征与所述第二特征可能不直接接触的实施例。为简洁及清晰起见,可按不同比例任意绘制各种特征。在附图中,为简化起见,可省略一些层/特征。

[0076]

此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下方(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所绘示的取向外亦囊括元件在使用或操作中的不同取向。所述元件可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行直译。

[0077]

应当理解,当一元件或层被称为“连接到”或“耦合到”另一元件或层时,它可以直接连接到或耦合到另一元件或层,或者可能存在中间的元件或层。

[0078]

在本公开内容中,半导体元件一般是指利用半导体特性而能发挥作用的元件,电光元件、发光显示元件、半导体电路和电子元件都包括在半导体元件的范畴内。

[0079]

在本公开描述中“上方(above)”、“上(up)”对应于方向z的箭头方向,“下方(below)”、“下(down)”对应于方向z的箭头的相反方向。

[0080]

图1是流程图,例示本公开一实施例的半导体元件1a的制备方法10。图2至图13例示本公开一实施例的半导体元件1a的制备流程的剖视示意图。

[0081]

参照图1和图2,在步骤s11,可以提供基底101,基底101可以包括密集图案区da和松散图案区la,可以在基底101上形成导电堆叠sk,可以在导电堆叠sk上形成第一硬遮罩层401。

[0082]

参照图2,在一些实施例中,密集图案区da和松散图案区la可以彼此相邻。在一些实施例中,密集图案区da和松散图案区la可以彼此分开。在一些实施例中,基底101可以包

括由至少一种半导体材料组成的块状(bulk)半导体基底。块状半导体基底的制作技术可以例如是本质(elementary)半导体(例如硅或锗)、化合物半导体(例如硅锗)、碳化硅(silicon carbide)、砷化镓(gallium arsenide)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indium arsenide)、锑化铟(indium antimonide),或其他iii-v族化合物半导体或ii-vi族化合物半导体,或其组合。

[0083]

在一些实施例中,基底101可以包括绝缘体上半导体(semiconductor-on-insulator,soi)结构,由下到上包括处理基底、绝缘体层和最上面半导体材料层。处理基底和最上面半导体材料层的制作技术可以是上述块状半导体基底相同的材料。绝缘层可以是结晶或非结晶的介电质材料,如氧化物和/或氮化物。例如,绝缘层可以是介电质氧化物,如氧化硅(silicon oxide)。再例如,绝缘层可以是介电质氮化物,如氮化硅(silicon nitride)或氮化硼(boron nitride)。再又例如,绝缘层可以包括介电质氧化物和介电质氮化物的堆叠,如按任何顺序的氧化硅和氮化硅或氮化硼的堆叠。绝缘层的厚度可以在10纳米(nm)到200纳米的范围内。

[0084]

应当理解,术语“大约”修改本公开的成分、组成或反应物的数量是指可能发生的数值数量的变化,例如,通过用于制造浓缩物或溶液的典型测量和液体处理程序。此外,测量程序中的疏忽错误、用于制造组合物或执行方法的成分的制造、来源或纯度的差异等都可能产生变化。在一实施例中,术语“大约”是指报告数值的10%的范围内。在另一实施例中,术语“大约”是指报告数值的5%的范围内。在更另一实施例中,术语“大约”是指报告数值的10、9、8、7、6、5、4、3、2或1%的范围内。

[0085]

在一些实施例中,基底101可以包括设置在块状半导体基底或最上面半导体材料层上的介电质、绝缘层或导电特征(为清晰起见未显示)。介电质或绝缘层的制作技术可以例如是氧化硅、硼硅酸盐玻璃(borosilicate glass)、未掺杂的硅酸盐玻璃(undoped silicate glass)、氟化硅酸盐玻璃(fluorinated silicate glass)、低介电常数(low-k)材料等,或其组合材料。每个介电质或绝缘层的厚度可以在大约0.5微米(mm)到3.0微米的范围内。低介电常数材料的介电常数可以小于3.0或甚至小于2.5。导电特征可以是导电线、导电通孔(via)、导电触点(contact)、导电垫(pad)或类似物。导电特征的制作技术可以是多晶硅(polycrystalline silicon)、多晶锗(polycrystalline germanium)、多晶硅锗(polycrystalline silicon germanium)、钨(w)、钴(co)、锆(zr)、钽(ta)、钛(ti)、铝(al)、钌(ru)、铜(cu)、金属碳化物(例如,碳化钽(tac)、碳化钛(tic)、碳化钽镁(tamgc))、金属氮化物(例如,氮化钛(tin))、过渡金属铝化物或其组合。

[0086]

在一些实施例中,元件单元(device element)(为清晰起见未示出)可以设置在基底101中。元件单元可以是,例如,双极接面晶体管(bjt)、金属氧化物半导体场效应晶体管(mosfet)、二极管(diode)、系统大型集成电路(system lsi)、快闪存储器(flash memory)、动态随机存取存储器(dram)、静态随机存取存储器(sram)、电可擦除可编程设计只读存储器(eeprom)、影像感测器(image sensor)、微机电系统(mems)、主动元件或被动元件。元件单元可以借由绝缘结构(如浅沟隔离(sti))与相邻的元件单元进行电绝缘。元件单元可以借由导电特征相互电耦合。

[0087]

应当理解,密集图案区da可以包括基底101的一部分和基底101的该部分上方的空间。将单元描述为设置在密集图案区da上是指单元设置在基底101的该部分的顶面。将单元

描述为设置在密集图案区da中是指单元设置在基底101的该部分中;但是,该单元的顶面可以与基底101的该部分的顶面齐平。将元件描述为设置在密集图案区da上方意味着该元件设置在基底101的该部分的顶面上方。相应地,松散图案区la可以包括基底101的另一部分和基底101的该另一部分上方的空间。

[0088]

参照图2,导电堆叠sk可以形成在基底101的密集图案区da和松散图案区la上。在一些实施例中,导电堆叠sk可以包括底部导电层201、中间导电层203和顶部导电层205。

[0089]

底部导电层201可以在基底101的密集图案区da和松散图案区la上共形地形成。在一些实施例中,底部导电层201的制作技术可以例如是钛。底部导电层201的制作技术可以借由例如物理气相沉积(pvd)制程、原子层沉积(ald)制程、化学气相沉积(cvd)制程、溅镀(sputtering)制程或其他适用的沉积制程。

[0090]

中间导电层203可以形成在底部导电层201上,并在基底101的密集图案区da和松散图案区la上方。在一些实施例中,中间导电层203的制作技术可以例如是铝铜合金。中间导电层203的制作技术可以借由例如物理气相沉积制程、化学气相沉积制程、溅镀制程或其他适用的沉积制程。

[0091]

顶部导电层205可以形成在中间导电层203上,并在基底101的密集图案区da和松散图案区la上方。在一些实施例中,顶部导电层205的制作技术可以例如是钽、氮化钽(tan)、钛、氮化钛、铼(re)、硼化镍(ni2b)、氮化钛/钛双层或氮化钽/钽双层。顶部导电层205的制作技术可以借由例如物理气相沉积制程、原子层沉积制程、化学气相沉积制程、溅镀制程或其他适用的沉积制程。

[0092]

参照图2,第一硬遮罩层401可以形成在顶部导电层205上,并在基底101的密集图案区da和松散图案区la上方。应当理解,第一硬遮罩层401可以在当前阶段完全覆盖导电堆叠sk。在一些实施例中,第一硬遮罩层401可以具有大约80纳米(nm)到大约500纳米范围内的厚度。在一些实施例中,第一硬遮罩层401的厚度可以在大约100纳米到大约200纳米的范围内。在一些实施例中,第一硬遮罩层401的厚度可以在大约30纳米到大约50纳米的范围内。在一些实施例中,第一硬遮罩层401的制作技术可以例如是氧化硅、氮化硅、氧氮化硅(silicon oxynitride)、正硅酸四乙酯(tetraethyl orthosilicate)或氮氧化硅(silicon nitride oxide)。在一些实施例中,第一硬遮罩层401的制作技术可以是氮化硅。第一硬遮罩层401的制作技术可以借由例如化学气相沉积制程、等离子体增强化学气相沉积(pecvd)制程、原子层沉积制程等,或其他适用的沉积制程。在一些实施例中,形成第一硬遮罩层401的制程温度可以低于400℃(摄氏度)。

[0093]

应当理解,在本公开中,氧氮化硅是指含有硅(si)、氮(n)和氧(o)的物质,其中氧的比例大于氮的比例。氮氧化硅是指含有硅、氧和氮的物质,其中氮的比例大于氧的比例。

[0094]

参照图1和图3至图5,在步骤s13,密集图案区da上方的第一硬遮罩层401可以被图案化,以形成多个密集图案层401d。

[0095]

参照图3,可以在第一硬遮罩层401上形成第一遮罩层501。第一遮罩层501可以完全覆盖松散图案区la上方的第一硬遮罩层401,并且可以部分覆盖密集图案区da上方的第一硬遮罩层401。在一些实施例中,第一遮罩层501可以具有多个密集图案层401d的图案。在一些实施例中,第一遮罩层501可以是光阻(photoresist)层。

[0096]

参照图4,可以使用第一遮罩层501作为遮罩(或图案导引)来执行密集区蚀刻制

程,以移除密集图案区da上方的第一硬遮罩层401的部分。在密集区蚀刻制程之后,密集图案区da上方剩余的第一硬遮罩层401可以被称为多个密集图案层401d。导电堆叠sk的顶面(即顶层导电层205的顶面)可以通过多个密集图案层401d的相邻对之间的空间而部分曝露。多个密集图案层401d的相邻对之间的距离可以被称为距离d1。

[0097]

在一些实施例中,密集区蚀刻制程可以在低温温度(cryogenic temperature)下进行。应当理解,在本公开内容中,术语“低温”指的是“冷(cold)”基底温度。用于蚀刻的术语“冷”是指-20℃或更低。在一些实施例中,低温温度可以在大约-20℃到大约-200℃的范围内。在一些实施例中,低温温度可以借由使用冷却剂来实现。在一些实施例中,冷却剂可以是,例如,液态氮或液体vertel sinera

tm

(由杜邦公司制造)。

[0098]

在一些实施例中,密集区蚀刻制程的蚀刻气体可以包括三氯化硼(bcl3)和氯(cl)。三氯化硼不是习用的蚀刻剂,因为副产品如三氧化二硼(b2o3)可能会阻碍蚀刻制程。相信在低温温度下,这种阻碍可能较少,并且三氯化硼可以在低温温度下作为蚀刻剂成分而发挥作用。在一些实施例中,密集区蚀刻制程的蚀刻气体可以包括氮气(n2)和氟甲烷(ch3f)。在一些实施例中,密集区蚀刻制程中的化学蚀刻量大于物理蚀刻量。

[0099]

应当理解,在本公开中,化学蚀刻是指化学品化学吸附(chemisorb)在表面上,自发地与表面形成新的物种,并在热表面温度下解吸(desorb)的过程。物理蚀刻是指等离子体轰击在表面上以移除表面的物种的过程。

[0100]

在一些实施例中,密集区蚀刻制程的激发射频(excitation rf)可以是,例如,400千赫兹(khz)、60百万赫兹(mhz)、以及可选的2mhz、或27mhz。激发射频的功率可以在大约200瓦特(watt)到大约8000瓦特的范围内。在一些实施例中,在密集区蚀刻制程中,可以提供幅度至少为400伏特的偏压。在一些实施例中,幅度至少为1000伏特的偏压将提供改进的蚀刻制程。在一些实施例中,幅度至少为2000伏特的偏压将提供更改进的蚀刻制程。在一些实施例中,密集区蚀刻制程的等离子体可以保持在大约180秒到3600秒的范围内。在一些实施例中,密集区蚀刻制程的压力可以在大约5毫托(mtorr)到大约60毫托的范围内。

[0101]

在一些实施例中,在密集区蚀刻制程中,第一硬遮罩层401与顶部导电层205的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。

[0102]

参照图5,在形成多个密集图案层401d之后,可以用灰化(ashing)制程或其他适用的半导体制程移除第一遮罩层501。

[0103]

参照图1和图6至图8,在步骤s15,可形成第二硬遮罩层403,以覆盖多个密集图案层401d和松散图案区la上方的第一硬遮罩层401,并且第二硬遮罩层403可以被图案化,以形成多个松散封盖层403l。

[0104]

参照图6,在一些实施例中,第二硬遮罩层403可以完全填充多个密集图案层401d之间的空间。在一些实施例中,第二硬遮罩层403可以部分地填充多个密集图案层401d之间的空间。在一些实施例中,可以进行平面化(planarization)制程,例如化学机械研磨(cmp)制程,以为后续制程步骤提供实质上平坦的表面。

[0105]

在一些实施例中,第二硬遮罩层403的制作技术可以是对第一硬遮罩层401具有蚀刻选择性的材料。在一些实施例中,第二硬遮罩层403的制作技术例如是氮化硅以外的介电质材料或抗反射涂层(arc)。在一些实施例中,第二硬遮罩层403的制作技术可以例如是碳

膜。术语“碳膜”在此用于描述质量主要是碳的材料,其结构主要由碳原子定义,或其物理和化学特性由其碳含量主导。术语“碳膜”是指不包括那些简单的包括碳的混合物或化合物的材料,例如介电质材料,如碳掺杂的氧氮化硅、碳掺杂的氧化硅或碳掺杂的多晶硅。

[0106]

在一些实施例中,碳膜可以借由制程沉积,包括将由一种或多种碳氢化合物组成的制程气体混合物引入制程室(chamber)。碳氢化合物具有公式cxhy,其中x的范围在2到4的范围内,y的范围在2到10的范围内。碳氢化合物可以是,例如,丙烯(c3h6)、丙炔(c3h4)、丙烷(c3h8)、丁烷(c4h10)、丁烯(c4h8)、丁二烯(c4h6)或乙炔(c2h2),或其组合化合物。

[0107]

在一些实施例中,碳膜可以借由保持基底温度在大约100℃到大约700℃的范围内、或大约350℃到大约550℃的范围内,从制程气体混合物中沉积。在一些实施例中,碳膜可以借由室压保持在大约1托到大约20托的范围内,从制程气体混合物中沉积。在一些实施例中,碳膜可以借由引入碳氢化合物气体和任何惰性(inert)气体或活性(reactive)气体,分别以大约50sccm(标准毫升/分钟)到大约2000sccm范围内的流量,从制程气体混合物中沉积。

[0108]

在一些实施例中,制程气体混合物更包括惰性气体,例如氩气(ar)。然而,也可以使用其他惰性气体,如氮气或其他钝气(noble gas),如氦气(he)。惰性气体可用于控制碳膜的密度和沉积速率。此外,可以添加各种气体到制程气体混合物中,以改变碳膜的特性。这些气体可以是活性气体,如氢气(h2)、氨气(nh3)、氢气和氮气的混合物,或其组合气体。氢气或氨气的加入可用于控制碳膜的氢气比例,以控制层的特性,如蚀刻选择性、耐化学机械研磨特性和反射率。在一些实施例中,可以添加活性气体和惰性气体的混合物到制程气体混合物中,以沉积碳膜。

[0109]

碳膜可以包括碳和氢原子,可以是可调的碳氢比,范围从大约10%的氢到大约60%的氢。控制碳膜的氢比(hydrogen ratio)可以调整各自的耐蚀性能和耐化学机械研磨性能。随着氢气含量的减少,碳膜的耐蚀性能,以及因此而产生的蚀刻选择性,都会增加。碳膜移除率的降低可以使碳膜在执行蚀刻制程将所需图案转移到底层时适合作为遮罩层。

[0110]

或者,在一些实施例中,第二硬遮罩层403可以由碳和氢组成。在一些实施例中,第二硬遮罩层403可以由碳、氢和氧组成。在一些实施例中,第二硬遮罩层403可以由碳、氢和氟(f)组成。

[0111]

在一些实施例中,第二硬遮罩层403的制作技术可以借由高密度等离子体化学气相沉积(hdp-cvd)制程。高密度等离子体可使用电感耦合射频功率(inductively coupled rf power)在大约500瓦特到大约4000瓦特的范围内产生。在一些实施例中,高密度等离子体可以使用电容耦合射频功率(capacitively coupled rf power)在大约500瓦特到大约4000瓦特的范围内产生。碳源可以是甲烷(ch4)、乙烷(c2h6)、乙炔、苯(c6h6),或其组合。碳源的流速可以在大约50sccm到大约150sccm的范围内。碳源可以提供碳的聚合以形成碳-碳链。惰性气体如氩气、氖气(ne)或氦气可作为载气(carrier gas)来携带碳源。载气的流速可以在大约10sccm到150sccm的范围内。高密度等离子体化学气相沉积制程的制程压力可以在大约5毫托到大约20毫托的范围内。高密度等离子体化学气相沉积制程的制程温度可以在大约240℃到大约340℃的范围内。

[0112]

在一些实施例中,第二硬遮罩层403的制作技术可以借由在高密度等离子体化学气相沉积制程中加入氟源而形成氟掺杂。氟源可以是,例如,八氟环丁烷(c4f8)、四氟甲烷

(cf4)、六氟乙烷(c2f6)、八氟丙烷(c3f8)、三氟甲烷(chf3)、六氟苯(c6f6),或其组合。氟源的流速可以在稍大于0到大约150sccm的范围内。氟源与碳源的流速比对第二硬遮罩层403的掺杂程度和热稳定性很重要。对于无误差(unbiased)制程情况,氟源与碳源的流速比可以在大约0.2到大约2的范围内。对于有误差(biased)制程情况,氟源与碳源的流速比可以在大约0.7到大约1.3的范围内。

[0113]

在一些实施例中,在高密度等离子体化学气相沉积制程之后可以执退火(annealing)制程,以提高第二硬遮罩层403的热稳定性。退火制程可以在真空中进行,或在由氩气或氮气等气体组成的惰性环境中进行,温度在大约300℃到大约450℃的范围内,持续大约30分钟。

[0114]

借由制作技术是高密度等离子体化学气相沉积制程的第二硬遮罩层403的厚度和均匀性可以得到良好的控制。例如,第二硬遮罩层403的厚度的标准差可以小于4%。此外,借由制作技术是高密度等离子体化学气相沉积制程的第二硬遮罩层403在高达大约400℃的高温下可以具有热稳定性。热稳定性是指第二硬遮罩层403在曝露于大约200℃到大约400℃的蚀刻环境中时,不会出现重量损失、变形或化学反应。第二硬遮罩层403在高温下的热稳定性,将允许其作为遮罩以用于在高于200℃的温度下执行蚀刻操作。此外,第二硬遮罩层403的耐蚀性能可以借由调整氟的掺杂程度来调整。第二硬遮罩层403的蚀刻电阻特性可以随着氟的掺杂程度的提高而降低。

[0115]

参照图7,可以在第二硬遮罩层403上形成第二遮罩层503。第二遮罩层503可以完全覆盖密集图案区da上方的第二硬遮罩层403,并且可以部分覆盖松散图案区la上方的第二硬遮罩层403。在一些实施例中,第二遮罩层503可以具有多个松散封盖层403l的图案。在一些实施例中,第二遮罩层503可以是光阻层。

[0116]

参照图8,可以使用第二遮罩层503作为遮罩(或图案导引)来执行第一松散区蚀刻制程,以移除松散图案区la上方的第二硬遮罩层403的部分。在第一松散区蚀刻制程之后,松散图案区域la上方剩余的第二硬遮罩层403可以被称为多个松散封盖层403l。松散图案区la上方的第一硬遮罩层401的顶面可通过多个松散封盖层403l的相邻对之间的空间部分地曝露。多个松散封盖层403l的相邻对之间的距离可称为距离d2。多个松散封盖层403l的相邻对之间的距离d2可以大于多个密集图案层401d的相邻对之间的距离d1。

[0117]

在一些实施例中,可以在低温温度下执行第一松散区蚀刻制程。在一些实施例中,低温温度可以在大约-20℃到大约-200℃的范围内。在一些实施例中,低温温度可以借由使用冷却剂来实现。在一些实施例中,冷却剂可以是,例如,液态氮或液体vertel sinera

tm

(由杜邦公司制造)。在一些实施例中,第一松散区蚀刻制程的蚀刻气体可以包括三氯化硼和氯。在一些实施例中,第一松散区蚀刻制程的蚀刻气体可包括氟甲烷、四氯化碳(ccl4)、三氟碘甲烷(cf3i)、二溴二氟甲烷(cbr2f2)或五氟乙烷(cf3chf2)。这些化学成分可以相互结合,或加入氢气、氧气、水和过氧化氢(h2o2)中的一种或多种。在一些实施例中,第一松散区蚀刻制程可包括其他钝化(passivation)成分,如氯化铬(crcl3)、四氯化硅(sicl4)、亚硫酰氯(socl2)、二氯钛(ticl2)、三氯钛(ticl3)和光气(cocl2)。在一些实施例中,在第一松散区蚀刻制程中,化学蚀刻量小于物理蚀刻量。

[0118]

在一些实施例中,第一松散区蚀刻制程的激发射频可以是,例如,400khz、60mhz、以及可选的2mhz、或27mhz。激发射频的功率可以在大约200瓦特到大约8000瓦特的范围内。

在一些实施例中,在第一松散区蚀刻制程中,可以提供幅度至少为400伏特的偏压。在一些实施例中,幅度至少为1000伏特的偏压将提供改进的蚀刻制程。在一些实施例中,幅度至少为2000伏特的偏压将提供更改进的蚀刻制程。在一些实施例中,第一松散区蚀刻制程的等离子体可以保持在大约180秒到大约3600秒的范围内。在一些实施例中,第一松散区蚀刻制程的压力可以在大约5毫托到大约60毫托的范围内。

[0119]

在一些实施例中,在第一松散区蚀刻制程中,第二硬遮罩层403与第一硬遮罩层401的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。

[0120]

在一些实施例中,密集区蚀刻制程的三氯化硼与氯的比率大于第一松散区蚀刻制程的三氯化硼与氯的比率。在一些实施例中,密集区蚀刻制程的功率比小于第一松散区蚀刻制程的功率比。功率比可由激发射频的功率除以密集区蚀刻制程和第一松散区蚀刻制程的偏压功率分别定义。

[0121]

参照图1、图9和图10,在步骤s17,松散图案区la上方的第一硬遮罩层401可以被图案化以形成多个松散图案层401l。

[0122]

参照图9,第二遮罩层503可以通过灰化制程或其他适用的半导体制程移除。在一些实施例中,第二遮罩层503可以在形成多个松散图案层401l之后被移除。

[0123]

参照图9,可使用多个松散封盖层403l作为遮罩(或图案导引)来执行第二松散区蚀刻制程,以移除松散图案区la上方的第一硬遮罩层401的部分。在第二松散区蚀刻制程之后,松散图案区域la上方剩余的第一硬遮罩层401可以被称为多个松散图案层401l。松散图案区la上方的导电堆叠sk的顶面可以通过多个松散图案层401l的相邻对之间空间部分曝露。由于松散图案层401l的图案是从多个松散封盖层403l的图案转移过来的,多个松散图案层401l的相邻对之间距离也可以称为距离d2。多个松散图案层401l的相邻对之间距离d2可以大于多个密集图案层401d的相邻对之间距离d1。

[0124]

在一些实施例中,第二松散区蚀刻制程可以在低温温度下进行。在一些实施例中,低温温度可以在大约-20℃到大约-200℃的范围内。在一些实施例中,低温温度可以通过使用冷却剂来实现。在一些实施例中,冷却剂可以是,例如,液态氮或液体vertel sinera

tm

(由杜邦公司制造)。在一些实施例中,第二松散区蚀刻制程的蚀刻气体可包括三氯化硼和氯。在一些实施例中,第二松散区蚀刻制程的蚀刻气体可包括氟甲烷、四氯化碳、三氟碘甲烷、二溴二氟甲烷或五氟乙烷。这些化学成分可以相互结合,或加入氢气、氧气、水和过氧化氢中的一种或多种。在一些实施例中,第二松散区蚀刻制程可包括其他钝化成分,如氯化铬、四氯化硅、亚硫酰氯、二氯钛、三氯钛和光气。在一些实施例中,在第二松散区蚀刻制程中,化学蚀刻量小于物理蚀刻量。

[0125]

在一些实施例中,第二松散区蚀刻制程的激发射频可以是,例如,400khz、60mhz、以及可选的2mhz,或27mhz。激发射频的功率可以在大约200瓦特到大约8000瓦特的范围内。在一些实施例中,在第二松散区蚀刻制程中,可以提供幅度至少为400伏特的偏压。在一些实施例中,幅度至少为1000伏特的偏压将提供改进的蚀刻制程。在一些实施例中,幅度至少为2000伏特的偏压将提供更改进的蚀刻制程。在一些实施例中,第二松散区蚀刻制程的等离子体可以保持在大约180秒到大约3600秒的范围内。在一些实施例中,第二松散区蚀刻制程的压力可以在大约5毫托到大约60毫托的范围内。

[0126]

在一些实施例中,在第二松散区蚀刻制程中,第一硬遮罩层401与第二硬遮罩层403的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。在一些实施例中,在第二松散区蚀刻制程中,第一硬遮罩层401与顶部导电层205的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。

[0127]

在一些实施例中,密集区蚀刻制程的三氯化硼与氯的比率大于第二松散区蚀刻制程的三氯化硼与氯的比率。在一些实施例中,密集区蚀刻制程的功率比小于第二松散区蚀刻制程的功率比。功率比可以由激发射频的功率除以密集区蚀刻制程和第二松散区蚀刻制程的偏压功率分别定义。

[0128]

参照图10,在形成多个松散图案层401l之后,第二硬遮罩层403可以被完全移除。例如,第二硬遮罩层403可以用类似于图8中描述的第一松散区蚀刻制程的程序移除。密集图案区da和松散图案区la上方的导电堆叠sk可以通过多个密集图案层401d的相邻对之间、多个松散图案层401l的相邻对之间,以及密集图案层401d和松散图案层401l之间的相邻对之间的空间而部分曝露。

[0129]

在一些实施例中,多个密集图案层401d可以具有大于多个松散图案层401l的元件密度(或图案密度)。元件密度可以是由形成在密集图案区da(或松散图案区la)上方的单元(例如密集图案层401d或松散图案层401l)除以密集图案区da(或从俯视角度看松散图案区la)的表面积所定义的值。从剖视的角度来看,更大的元件密度可能意味着相邻对单元之间距离更小。换言之,单元的密度可能与单元的关键尺寸成反比。如图10所示,更多的密集图案层401d被显示出来,以强调多个密集图案层401d比多个松散图案层401l的元件密度更大。应当理解,图10中所示的密集图案层401d或松散图案层401l的数量仅是说明性的。

[0130]

参照图1和图11至图13,在步骤s19,导电堆叠sk可以被图案化,以形成多个密集导电层301和多个松散导电层303。

[0131]

参照图11,可以使用多个密集图案层401d和多个松散图案层401l作为遮罩(或图案导引)来执行堆叠蚀刻制程,以移除导部分的电堆叠sk。在堆叠蚀刻制程之后,密集图案区da上剩余的导电堆叠sk可以被称为多个密集导电层301,而松散图案区la上剩余的导电堆叠sk可以被称为多个松散导电层303。每个或多个密集导电层301和多个松散导电层303中的每个可以由从下到上的(剩余的)底部导电层201、(剩余的)中间导电层203和(剩余的)顶部导电层205组成。

[0132]

由于多个密集导电层301和多个松散导电层303的图案分别从多个密集图案层401d和多个松散图案层401l中相应地继承。多个密集导电层301的相邻对之间的距离也可称为距离d1。多个松散导电层303的相邻对之间的距离也可称为距离d2。多个松散导电层303的相邻对之间的距离d2可以大于多个密集导电层301的相邻对之间的距离d1。因此,多个密集导电层301的元件密度可以大于多个松散导电层303的元件密度。

[0133]

在一些实施例中,堆叠蚀刻制程可以是多步骤蚀刻制程。在一些实施例中,在堆叠蚀刻制程中,导电堆叠sk与多个密集图案层401d的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。在一些实施例中,在堆叠蚀刻制程中,导电堆叠sk与基底101的蚀刻速率比可以在大约100∶1到大约1.05∶1的范围内、大约15∶1到大约2∶1的范围内、或大约10∶1到大约2∶1的范围内。

[0134]

参照图12,可以形成顶部介电质层103,以覆盖多个密集导电层301和多个松散导电层303,并完全填充其间的空间。顶部介电层103的制作技术可以例如是氧化硅、硼磷酸盐玻璃(borophosphosilicate glass)、未掺杂的硅酸盐玻璃、氟化硅酸盐玻璃、低介电常数材料等或其组合材料。低介电常数材料的介电常数可以小于3.0或甚至小于2.5。在一些实施例中,低介电常数材料的介电常数可以小于2.0。顶部介电层103的制作技术可以借由例如化学气相沉积制程、等离子体增强化学气相沉积制程等,或其他适用的沉积制程。可以执行平坦化制程,例如化学机械研磨,以为后续的制程步骤提供实质上平坦的表面。此外,在一些实施例中,可以直接执行图12所示的平面化制程,直到曝露多个密集导电层301和多个松散导电层303的顶面,以形成半导体元件1a。因此,半导体元件1a的制程复杂性可以降低。

[0135]

参照图13,可以执行平面化制程,例如化学机械研磨,直到曝露多个密集导电层301和多个松散导电层303的顶面,以移除多余的材料,为后续加工步骤提供实质上平整的表面,并同时形成半导体元件1a。分离的平坦化制程可能有利于控制制程参数和终点检测,因此可以提高半导体元件1a的产量和/或品质。此外,半导体元件1a的制备成本可能会降低。

[0136]

图14例示本公开一实施例的用于制备半导体元件的蚀刻反应器600的示意图。蚀刻反应器600可以用于密集区蚀刻制程、第一松散区蚀刻制程、第二松散区蚀刻制程和堆叠蚀刻制程。在一些实施例中,蚀刻反应器600包括提供气体入口的气体分配板617和静电吸盘(electrostatic chuck,esc)619,在蚀刻室607内,由室壁609封住。在蚀刻室607内,待处理的中间半导体元件可以置放在静电吸盘619上方。静电吸盘619可以提供来自静电吸盘源623的偏压。蚀刻气体源605可以通过气体分配板617连接到蚀刻室607。静电吸盘温度控制器621与冷却器613相连,该冷却器冷却冷却剂627。

[0137]

在一些实施例中,冷却器613向静电吸盘619内或附近的通道611提供冷却剂627。射频源603向下电极和/或上电极提供射频功率,下电极和上电极分别是静电吸盘619和气体分配板617。在一些实施例中,400khz、60mhz,以及可选的2mhz、27mhz的功率源构成射频源603和静电吸盘源623。在一些实施例中,上电极是接地的。在一些实施例中,为每个频率提供一个发生器(generator)。在一些实施例中,发生器可以在单独的射频源中,或者单独的射频发生器可以连接到不同的电极。例如,上电极可以具有连接到不同射频源的内部和外部电极。在其他实施例中可以使用射频源和电极的其他安排。控制器601可控制地连接到射频源603、静电吸盘源623、排气泵615和蚀刻气体源605。制程室可以是电容耦合等离子体(ccp)反应器或电感耦合等离子体(icp)反应器。

[0138]

本公开的一实施例提供一种半导体元件,包括一基底、多个密集导电层、以及多个松散导电层。该基底包括一密集图案区和与该密集图案区相邻设置的一松散图案区。该多个密集导电层设置在该基底的该密集图案区上。该多个松散导电层设置在该基底的该松散图案区上。该多个密集导电层的相邻对之间距离小于该多个松散导电层的相邻对之间距离。

[0139]

本公开的另一实施例提供一种半导体元件的制备方法,包括:提供包括一密集图案区和一松散图案区的一基底,并在该密集图案区和该松散图案区上依次形成一导电堆叠和一第一硬遮罩层;对该第一硬遮罩层进行图案化,在该密集图案区上方形成多个密集图案层;形成覆盖该第一硬遮罩层和该多个密集图案层的一第二硬遮罩层;对该第二硬遮罩

层进行图案化,在该松散图案区上方形成多个松散封盖层;使用该多个松散封盖层作为遮罩,在该松散图案区上方对该第一硬遮罩层进行图案化,以在该松散图案区上方形成多个松散图案层,并移除该第二硬遮罩层和该多个松散封盖层;以及使用该多个密集图案层和该多个松散图案层作为遮罩对该导电堆叠进行图案化,在该密集图案区上方形成多个密集导电层,在该松散图案区上方形成多个松散导电层。该多个密集导电层的相邻对之间距离小于该多个松散导电层的相邻对之间距离。

[0140]

由于本公开的半导体元件的设计,借由采用第一硬遮罩层401和第二硬遮罩层403,具有不同元件密度的多个密集导电层301和多个松散导电层303可以容易地积集(integrated)在半导体元件1a中。因此,制备半导体元件1a的复杂性可以降低。相应地,半导体元件1a的产量可以提高。

[0141]

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求书所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

[0142]

再者,本技术的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤系包括于本技术的权利要求书内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。