半导体装置

1.本技术要求于2021年8月10日提交到韩国知识产权局的第10-2021-0105357号韩国专利申请的优先权,所述韩国专利申请的公开通过引用全部包含于此。

技术领域

2.本公开涉及半导体装置,更具体地,涉及包括场效应晶体管的半导体装置和制造该半导体装置的方法。

背景技术:

3.半导体装置可包括集成电路,集成电路包括金属氧化物半导体(mos)场效应晶体管(mosfet)。随着半导体装置的尺寸和设计规格减小,mos场效应晶体管也已经按比例缩小。半导体装置的操作特性可能受到mos场效应晶体管的按比例缩小的负面影响。因此,已经研究了用于制造能够在克服由高集成密度引起的限制的同时提高性能的半导体装置的各种方法。

技术实现要素:

4.本公开的示例实施例可提供具有提高的电特性和可靠性的半导体装置。

5.根据示例实施例的一个方面,提供了一种半导体装置,所述半导体装置包括:有源图案,在基底上沿第一方向延伸;第一下部源极/漏极图案,设置在有源图案上;第二下部源极/漏极图案,设置在有源图案上,并且在第一方向上与第一下部源极/漏极图案间隔开;第一上部源极/漏极图案,设置在第一下部源极/漏极图案上;第二上部源极/漏极图案,设置在第二下部源极/漏极图案上;以及栅电极,与有源图案交叉,并且在与第一方向相交的第二方向上延伸,其中,栅电极包括在第三方向上与有源图案重叠的重叠部分,第三方向垂直于第一方向和第二方向,并且其中,所述重叠部分在第二方向上的长度小于第一下部源极/漏极图案在第二方向上的长度。

6.根据示例实施例的一个方面,提供了一种半导体装置,所述半导体装置包括:有源图案,在基底上沿第一方向延伸;第一下部源极/漏极图案,设置在有源图案上;第二下部源极/漏极图案,设置在有源图案上,并且在第一方向上与第一下部源极/漏极图案间隔开;第一上部源极/漏极图案,设置在第一下部源极/漏极图案上;第二上部源极/漏极图案,设置在第二下部源极/漏极图案上;栅电极,与有源图案交叉,并且在与第一方向相交的第二方向上延伸;第一沟道图案,在第一方向上延伸以与栅电极交叉,并且连接第一下部源极/漏极图案和第二下部源极/漏极图案;第二沟道图案,在第一方向上延伸以与栅电极交叉,并且连接第一上部源极/漏极图案和第二上部源极/漏极图案;公共接触件,共同连接到第一下部源极/漏极图案和第一上部源极/漏极图案;底部接触件,连接到第二下部源极/漏极图案;顶部接触件,连接到第二上部源极/漏极图案;以及栅极接触件,与栅电极接触,其中,第一沟道图案和第二沟道图案中的至少一个包括在第三方向上彼此堆叠并间隔开的多个半导体图案,第三方向垂直于基底的顶表面,其中,第一上部源极/漏极图案和第二上部源极/

漏极图案中的每个在第二方向上的长度小于第一下部源极/漏极图案和第二下部源极/漏极图案中的每个在第二方向上的长度,其中,栅电极包括沿着第三方向与有源图案重叠的重叠部分,并且其中,所述重叠部分在第二方向上的长度小于第一下部源极/漏极图案在第二方向上的长度。

7.根据示例实施例的一个方面,提供了一种半导体装置,所述半导体装置包括:基底,包括第一区域、第二区域以及第三区域,第三区域在第一区域与第二区域之间;有源图案,在基底上沿第一方向延伸;第一下部源极/漏极图案,设置在有源图案上;第二下部源极/漏极图案,设置在有源图案上,并且在第一方向上与第一下部源极/漏极图案间隔开;第一上部源极/漏极图案,设置在第一下部源极/漏极图案上;第二上部源极/漏极图案,设置在第二下部源极/漏极图案上;以及栅电极,与第三区域上的有源图案交叉,并且在与第一方向相交的第二方向上延伸,其中,有源图案在第一区域上在第二方向上具有第一长度,其中,有源图案在第二区域上在第二方向上具有第二长度,其中,有源图案在第三区域上在第二方向上具有第三长度,并且其中,第三长度小于第一长度和第二长度。

8.根据示例实施例的一个方面,提供了一种半导体装置,所述半导体装置包括:有源图案,在基底上沿第一方向延伸;第一下部源极/漏极图案,设置在有源图案上;第二下部源极/漏极图案,设置在有源图案上,并且在第一方向上与第一下部源极/漏极图案间隔开;第一上部源极/漏极图案,设置在第一下部源极/漏极图案上;第二上部源极/漏极图案,设置在第二下部源极/漏极图案上;栅电极,与有源图案交叉,并且在与第一方向相交的第二方向上延伸;第一沟道图案,在第一方向上延伸以与栅电极交叉,并且连接第一下部源极/漏极图案和第二下部源极/漏极图案;以及第二沟道图案,设置在第一沟道图案上,在第一方向上延伸以与栅电极交叉,并且连接第一上部源极/漏极图案和第二上部源极/漏极图案,其中,第一沟道图案包括在第三方向上彼此堆叠并间隔开的多个下部半导体图案,第三方向垂直于基底的顶表面,其中,第二沟道图案包括在第三方向上彼此堆叠并间隔开的多个上部半导体图案,其中,栅电极包括沿着第三方向与有源图案重叠的重叠部分,并且其中,所述重叠部分在第二方向上的长度小于第一下部源极/漏极图案在第二方向上的长度。

附图说明

9.从以下结合附图对示例实施例的描述,以上和其他方面将更加清楚,其中:

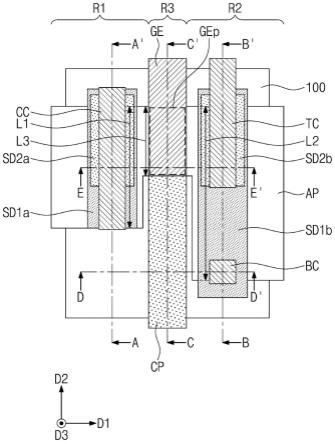

10.图1a是示出根据一些示例实施例的半导体装置的平面图;

11.图1b、图1c、图1d、图1e和图1f分别是沿着图1a的线a-a'、b-b'、c-c'、d-d'和e-e'截取以示出根据一些示例实施例的半导体装置的剖视图;

12.图2a是示出根据一些示例实施例的半导体装置的平面图;

13.图2b、图2c、图2d和图2e分别是沿着图2a的线a-a'、b-b'、c-c'和e-e'截取以示出根据一些示例实施例的半导体装置的剖视图;

14.图3、图4和图5是与图2d的部分“x”对应以示出根据一些示例实施例的半导体装置的部分的放大图;

15.图6a是示出根据一些示例实施例的半导体装置的平面图;

16.图6b和图6c分别是沿着图6a的线b-b'和f-f'截取以示出根据一些示例实施例的半导体装置的剖视图;

17.图7a是示出根据一些示例实施例的半导体装置的平面图;

18.图7b、图7c和图7d分别是沿着图7a的线a-a'、b-b'和c-c'截取以示出根据一些示例实施例的半导体装置的剖视图;

19.图8a是示出根据一些示例实施例的半导体装置的平面图;

20.图8b是沿着图8a的线b-b'截取以示出根据一些示例实施例的半导体装置的剖视图;

21.图9a、图12a、图13a、图14a、图15a、图16a和图17a是示出根据一些示例实施例的制造半导体装置的方法的平面图;

22.图9b、图10、图11、图12b、图13b、图14b、图15b和图16b分别是沿着图9a的线e-e'、图12a的线e-e'、图13a的线e-e'、图14a的线e-e'、图15a的线e-e'和图16a的线e-e'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图;

23.图12c、图13c和图14c分别是沿着图12a的线a-a'、图13a的线a-a'和图14a的线a-a'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图;

24.图13d和图14d分别是沿着图13a的线b-b'和图14a的线b-b'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图;以及

25.图16c和图17b分别是沿着图16a的线c-c'和图17a的线c-c'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图。

具体实施方式

26.现在将参照附图更全面地描述示例实施例。

27.图1a是示出根据一些示例实施例的半导体装置的平面图。图1b、图1c、图1d、图1e和图1f分别是沿着图1a的线a-a'、b-b'、c-c'、d-d'和e-e'截取以示出根据一些示例实施例的半导体装置的剖视图。

28.参照图1a、图1b、图1c、图1d、图1e和图1f,可提供包括有源图案ap的基底100。例如,基底100可以是包括硅(si)、锗(ge)和硅锗(sige)中的至少一者的半导体基底,或者混合物半导体基底。例如,基底100可以是硅基底。基底100的顶表面可平行于第一方向d1和第二方向d2,并且可垂直于第三方向d3。第一方向d1、第二方向d2和第三方向d3可彼此相交(例如,垂直或其他角度)。

29.基底100可包括第一区域r1、第二区域r2和第三区域r3,第三区域r3在第一区域r1与第二区域r2之间。第一区域r1和第二区域r2可在第一方向d1上彼此间隔开,第三区域r3置于在第一区域r1与第二区域r2之间。第一区域至第三区域r1、r2和r3中的每个可在第二方向d2上延伸。第一区域至第三区域r1、r2和r3可以是在其上设置有构成逻辑电路的标准单元的区域。例如,设置在第一区域至第三区域r1、r2和r3上的晶体管可以是逻辑晶体管。

30.器件隔离层st可被设置在基底100上,并且器件隔离层st可限定有源图案ap。器件隔离层st可覆盖有源图案ap的侧表面,并且可暴露有源图案ap的顶表面。例如,器件隔离层st可包括氧化硅、氮化硅和氮氧化硅中的至少一者。有源图案ap可对应于由器件隔离层st围绕的基底100的上部部分。

31.如图1a中所示,有源图案ap可在第一区域r1上在第二方向d2上具有第一长度l1,可在第二区域r2上在第二方向d2上具有第二长度l2,并且可在第三区域r3上在第二方向d2

pattern)。例如,第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可包括硅(si)、硅锗(sige)和碳化硅(sic)中的至少一者。第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可被形成,以向第一沟道图案ch1的下部半导体图案lsp提供拉伸应变或压缩应变。

41.覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个的至少一个侧表面的第一绝缘层110可被设置在基底100上。第一绝缘层110可被设置在器件隔离层st上。覆盖第一下部源极/漏极图案sd1a的侧表面的第二绝缘层120可被设置在基底100上。第二绝缘层120可与基底100接触。

42.更具体地,第一下部源极/漏极图案sd1a的第一侧表面sw11可具有平坦轮廓。例如,第一下部源极/漏极图案sd1a的第一侧表面sw11可平行于第三方向d3。第一下部源极/漏极图案sd1a的第一侧表面sw11可与有源图案ap的侧表面对齐。第一下部源极/漏极图案sd1a的第一侧表面sw11可与第二绝缘层120直接接触。

43.第一下部源极/漏极图案sd1a的第二侧表面sw12可具有在第二方向d2上凸起的轮廓。第一下部源极/漏极图案sd1a的第二侧表面sw12可不平行于第一侧表面sw11,并且可不与有源图案ap的另一侧表面对齐。第一下部源极/漏极图案sd1a的第二侧表面sw12可被覆盖有第一绝缘层110。第一下部源极/漏极图案sd1a的第一侧表面sw11和第二侧表面sw12可在第二方向d2上彼此背对。

44.第二下部源极/漏极图案sd1b的两个侧表面可不与第二绝缘层120接触,并且可被覆盖有第一绝缘层110。

45.第三绝缘层130可被设置在第一下部源极/漏极图案sd1a、第二下部源极/漏极图案sd1b以及第一绝缘层110上。第三绝缘层130可覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个的顶表面,并且可在第二方向d2上延伸。第三绝缘层130可沿着第一下部源极/漏极图案sd1a的第二侧表面sw12和第二下部源极/漏极图案sd1b的两个侧表面延伸。第三绝缘层130还可被布置在第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个与第一绝缘层110之间。第三绝缘层130的最顶表面可与第一绝缘层110和第二绝缘层120的顶表面基本共面。第三绝缘层130可与器件隔离层st的侧表面接触。

46.第一绝缘层至第三绝缘层110、120和130中的每个可包括氧化硅、氮化硅和氧氮化硅中的至少一者。例如,第一绝缘层110和第二绝缘层120可包括相同的绝缘材料。例如,第三绝缘层130可包括与第一绝缘层110和第二绝缘层120的绝缘材料不同的绝缘材料。例如,第一绝缘层110和第二绝缘层120可包括氧化硅,第三绝缘层130可包括氮化硅。

47.在第二方向d2上延伸的一对上部源极/漏极图案sd2a和sd2b可被设置在第三绝缘层130上。一对上部源极/漏极图案sd2a和sd2b可被设置在第二沟道图案ch2的两侧,并且可与第二沟道图案ch2的上部半导体图案usp接触。一对上部源极/漏极图案sd2a和sd2b可包括设置在第一区域r1上的第一上部源极/漏极图案sd2a和设置在第二区域r2上的第二上部源极/漏极图案sd2b。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可在第一方向d1上彼此间隔开,之后将被描述的栅电极ge置于第一上部源极/漏极图案sd2a与第二上部源极/漏极图案sd2b之间。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可在第三方向d3上与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b间

隔开,第三绝缘层130置于第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b之间。

48.第一上部源极/漏极图案sd2a在第一方向d1上的宽度可基本等于第二上部源极/漏极图案sd2b在第一方向d1上的宽度。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第一方向d1上的宽度可等于或小于第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个在第一方向d1上的宽度。

49.第一上部源极/漏极图案sd2a在第二方向d2上的长度可等于或小于第二上部源极/漏极图案sd2b在第二方向d2上的长度。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第二方向d2上的长度可小于第一长度l1。例如,第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第二方向d2上的长度可大于第三长度l3。在本公开中,第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第二方向d2上的长度可指示第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第二方向d2上的最大长度。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个可在其顶表面与底表面之间的水平高度处在第二方向d2上具有最大长度。在一些示例实施例中,第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个在第二方向d2上的长度可小于第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个在第二方向d2上的长度。

50.第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可包括使用上部半导体图案usp作为晶种形成的外延图案。例如,第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可包括硅(si)、硅锗(sige)和碳化硅(sic)中的至少一者。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可被形成,以向第二沟道图案ch2的上部半导体图案usp提供拉伸应变或压缩应变。

51.第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可具有与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b的导电类型不同的导电类型。例如,第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可具有第一导电类型(例如,p型或n型),第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可具有与第一导电类型不同的第二导电类型(例如,n型或p型)。例如,第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可包括与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b的掺杂剂不同的掺杂剂。

52.覆盖第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个的至少一个侧表面的第四绝缘层150可被设置在第二绝缘层120和第三绝缘层130上。第四绝缘层150的底表面可与第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b的底表面基本共面。第四绝缘层150的顶表面可位于比第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b的顶表面高的水平高度处。例如,第四绝缘层150可包括氧化硅、氮化硅和氧氮化硅中的至少一者。

53.更具体地,第一上部源极/漏极图案sd2a的第一侧表面sw21可具有平坦轮廓。例如,第一上部源极/漏极图案sd2a的第一侧表面sw21可平行于第三方向d3。第一上部源极/漏极图案sd2a的第一侧表面sw21可与之后将被描述的公共接触件cc的第一部分cca的侧表面接触并对齐。

54.第一上部源极/漏极图案sd2a的第二侧表面sw22可具有在第二方向d2上凸起的轮廓。第一上部源极/漏极图案sd2a的第二侧表面sw22可不平行于第一侧表面sw21,并且可不与之后将被描述的公共接触件cc的第二部分ccb的侧表面对齐。第一上部源极/漏极图案sd2a的第二侧表面sw22可被覆盖有第四绝缘层150。第一上部源极/漏极图案sd2a的第一侧表面sw21和第二侧表面sw22可在第二方向d2上彼此背对。

55.第二上部源极/漏极图案sd2b的两个侧表面可被覆盖有第四绝缘层150。

56.覆盖有源图案ap并在第二方向d2上延伸的栅电极ge可被设置在第三区域r3上。栅电极ge可在第三方向d3上与第一沟道图案ch1的下部半导体图案lsp和第二沟道图案ch2的上部半导体图案usp重叠,并且可围绕第一沟道图案ch1的下部半导体图案lsp和第二沟道图案ch2的上部半导体图案usp。

57.栅电极ge可包括在第三方向d3上与有源图案ap重叠的重叠部分gep。重叠部分gep在第二方向d2上的长度可基本等于第三区域r3上的有源图案ap在第二方向d2上的第三长度l3。重叠部分gep在第二方向d2上的长度可小于第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个在第二方向d2上的长度。

58.更具体地,栅电极ge可覆盖第一沟道图案ch1的下部半导体图案lsp和第二沟道图案ch2的上部半导体图案usp中的每个的顶表面和底表面。栅电极ge可覆盖下部半导体图案lsp中的每个的第一侧表面lsw1和上部半导体图案usp中的每个的第一侧表面usw1。下部半导体图案lsp中的每个的第二侧表面lsw2和上部半导体图案usp中的每个的第二侧表面usw2可不被栅电极ge覆盖,并且可与之后将被描述的覆盖图案cp的第二部分cpb接触。下部半导体图案lsp中的每个的第一侧表面lsw1和第二侧表面lsw2可在第二方向d2上彼此背对。上部半导体图案usp中的每个的第一侧表面usw1和第二侧表面usw2可在第二方向d2上彼此背对。

59.例如,栅电极ge可包括掺杂半导体材料、导电金属氮化物和/或金属。更具体地,栅电极ge可包括彼此不同的多个金属图案。例如,栅电极ge可包括围绕第一沟道图案ch1的下部半导体图案lsp的第一金属图案、围绕第二沟道图案ch2的上部半导体图案usp的第二金属图案、以及设置在上部半导体图案usp中的最顶部的上部半导体图案usp上的第三金属图案。第一金属图案至第三金属图案的电阻可彼此不同。可通过调整第一金属图案至第三金属图案中的每个的组成和厚度来获得下部晶体管和上部晶体管的期望的阈值电压。

60.第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可分别被设置在栅电极ge的两侧,并且第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b也可分别被设置在栅电极ge的两侧。如图1a中所示,第一下部源极/漏极图案sd1a、第二下部源极/漏极图案sd1b、第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个的至少一部分可在第一方向d1上与栅电极ge重叠。

61.栅极绝缘图案gi可被设置在栅电极ge与有源图案ap之间以及栅电极ge与第一沟道图案ch1的下部半导体图案lsp和第二沟道图案ch2的上部半导体图案usp中的每个之间。一对第一栅极间隔件gs1可被设置,以在第三方向d3上从第二沟道图案ch2的上部半导体图案usp中的最顶部的上部半导体图案usp的顶表面延伸并且覆盖栅电极ge的两个侧表面的部分。一对第二栅极间隔件gs2可被设置,以在第三方向d3上在第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个的顶表面与第一上部源极/漏极图案sd2a和

第二上部源极/漏极图案sd2b中的每个的底表面之间延伸并且覆盖栅电极ge的两个侧表面的其他部分。覆盖栅电极ge的最顶表面的覆盖图案cp可被设置。栅电极ge、栅极绝缘图案gi、第一栅极间隔件gs1、第二栅极间隔件gs2以及覆盖图案cp可被统称为栅极结构。

62.栅极绝缘图案gi可沿着栅电极ge的底表面延伸,并且可被布置在栅电极ge与器件隔离层st之间。例如,栅极绝缘图案gi可在第二方向d2上从有源图案ap的顶表面延伸到器件隔离层st的顶表面上。

63.栅极绝缘图案gi可被布置在栅电极ge与第一沟道图案ch1的下部半导体图案lsp和第二沟道图案ch2的上部半导体图案usp中的每个之间。栅极绝缘图案gi可围绕下部半导体图案lsp中的每个的顶表面、底表面和第一侧表面lsw1。栅极绝缘图案gi可围绕上部半导体图案usp中的每个的顶表面、底表面和第一侧表面usw1。下部半导体图案lsp和上部半导体图案usp中的每个可与栅电极ge间隔开,栅极绝缘图案gi置于下部半导体图案lsp与上部半导体图案usp之间。

64.覆盖下部半导体图案lsp和上部半导体图案usp中的每个的顶表面和底表面的栅极绝缘图案gi可在栅电极ge与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个之间以及栅电极ge与第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个之间延伸。第一下部源极/漏极图案sd1a、第二下部源极/漏极图案sd1b、第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个可在第一方向d1上与栅电极ge间隔开,栅极绝缘图案gi置于第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b与第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b之间。

65.栅极绝缘图案gi可被布置在栅电极ge与第二沟道图案ch2的上部半导体图案usp中的最顶部的上部半导体图案usp之间,并且可在栅电极ge与第一栅极间隔件gs1之间延伸。栅极绝缘图案gi的最顶表面可与栅电极ge的最顶表面基本共面。

66.例如,栅极绝缘图案gi可包括氧化硅、氮化硅、氮氧化硅和高k介电材料中的至少一者。高k介电材料可以是其介电常数大于氧化硅和氮化硅的介电常数的材料,例如,氧化铪(hfo)、氧化铝(alo)或氧化钽(tao)。

67.一对第一栅极间隔件gs1可在第三方向d3上从栅电极ge的两个侧表面延伸到覆盖图案cp的第一部分cpa的两个侧表面上。一对第一栅极间隔件gs1中的每个的顶表面可位于比栅电极ge的最顶表面高的水平高度处,并且可与覆盖图案cp的顶表面基本共面。一对第一栅极间隔件gs1可在第一方向d1上彼此间隔开,栅电极ge和/或覆盖图案cp置于一对第一栅极间隔件gs1之间。

68.一对第二栅极间隔件gs2可被设置在第三绝缘层130与栅电极ge之间以及第三绝缘层130与覆盖图案cp的第二部分cpb之间。一对第二栅极间隔件gs2中的每个的底表面可与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的一个接触,并且可与第三绝缘层130的底表面基本共面。一对第二栅极间隔件gs2中的每个的顶表面可与第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的一个接触,并且可与第三绝缘层130的顶表面基本共面。一对第二栅极间隔件gs2中的每个可在第三方向d3上不与一对第一栅极间隔件gs1重叠。可选地,在特定示例实施例中,一对第二栅极间隔件gs2可分别被设置在上部半导体图案usp中的最底部的上部半导体图案usp与下部半导体图案lsp中的最顶部的下部半导体图案lsp之间,并且可在第三方向d3上分别与第一栅极间隔件gs1重叠。

69.覆盖图案cp可包括覆盖栅电极ge的最顶表面并在第二方向d2上延伸的第一部分cpa、以及覆盖栅电极ge的侧表面和基底100的顶表面的第二部分cpb。覆盖图案cp的第一部分cpa和第二部分cpb可在第二方向d2上彼此连接。覆盖图案cp可被设置在第三区域r3上。

70.覆盖图案cp的第一部分cpa可与栅极绝缘图案gi的最顶表面接触。覆盖图案cp的第一部分cpa在第三方向d3上的厚度可比从上部半导体图案usp中的最顶部的上部半导体图案usp的顶表面到栅电极ge的最顶表面的距离小。

71.覆盖图案cp的第二部分cpb可与覆盖下部半导体图案lsp和上部半导体图案usp中的每个的顶表面和底表面的栅极绝缘图案gi接触。覆盖图案cp的第二部分cpb可与下部半导体图案lsp中的每个的第二侧表面lsw2和上部半导体图案usp中的每个的第二侧表面usw2直接接触。覆盖图案cp的第二部分cpb在第三方向d3上的厚度可大于第一部分cpa在第三方向d3上的厚度,并且大于栅电极ge在第三方向d3上的最大厚度。覆盖图案cp的第二部分cpb的底表面可位于比有源图案ap的顶表面低的水平高度处。例如,覆盖图案cp的第二部分cpb的底表面可位于比基底100的最顶表面低的水平高度处。覆盖图案cp的第二部分cpb的顶表面可位于与第一部分cpa的顶表面、一对第一栅极间隔件gs1中的每个的顶表面和第四绝缘层150的顶表面基本相同的水平高度处。在一些示例实施例中,覆盖图案cp的第二部分cpb在第一方向d1上可与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个的至少一部分重叠。

72.例如,第一栅极间隔件gs1和第二栅极间隔件gs2中的每个以及覆盖图案cp可包括氧化硅、氮化硅和氮氧化硅中的至少一者。在一些示例实施例中,覆盖图案cp可包括与第一绝缘层110、第二绝缘层120和第四绝缘层150的绝缘材料不同的绝缘材料。具体地,覆盖图案cp可包括针对第一绝缘层110、第二绝缘层120和第四绝缘层150具有蚀刻选择性的材料。例如,覆盖图案cp可包括氮化硅。

73.栅电极ge、第一沟道图案ch1、第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可构成下部晶体管,栅电极ge、第二沟道图案ch2、第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可构成上部晶体管。当下部晶体管是pmos场效应晶体管时,上部晶体管可以是nmos场效应晶体管,并且当下部晶体管是nmos场效应晶体管时,上部晶体管可以是pmos场效应晶体管。

74.在一些示例实施例中,下部晶体管和上部晶体管中的每个可以是在其中栅电极ge三维地围绕沟道的三维场效应晶体管(或全环绕栅极(gaa)型晶体管)。下部晶体管和上部晶体管可在第三方向d3上顺序地被堆叠在基底100上,并且根据示例实施例的半导体装置可被称为堆叠式晶体管。

75.再次参照图1a和图1b,公共接触件cc可被设置在第一区域r1上,并且公共接触件cc可穿透第三绝缘层130和第四绝缘层150,以便与第一下部源极/漏极图案sd1a和第一上部源极/漏极图案sd2a接触。

76.公共接触件cc可包括第一部分cca和第二部分ccb,第一部分cca穿透第三绝缘层130和第四绝缘层150以便与第一下部源极/漏极图案sd1a的顶表面接触,第二部分ccb穿透第四绝缘层150以便与第一上部源极/漏极图案sd2a的顶表面接触。公共接触件cc的第一部分cca的底表面可位于比第二部分ccb的底表面低的水平高度处。公共接触件cc的第一部分cca在第三方向d3上的高度可大于第二部分ccb在第三方向d3上的高度。公共接触件cc的第

一部分cca的侧表面可与第一上部源极/漏极图案sd2a的第一侧表面sw21接触。

77.再次参照图1a和图1c,底部接触件bc可穿透第二区域r2上的第三绝缘层130和第四绝缘层150以便与第二下部源极/漏极图案sd1b的顶表面接触,并且顶部接触件tc可穿透第二区域r2上的第四绝缘层150以便与第二上部源极/漏极图案sd2b的顶表面接触。

78.底部接触件bc可在第二方向d2上与顶部接触件tc间隔开,第四绝缘层150置于底部接触件bc与顶部接触件tc之间。底部接触件bc的底表面可位于比顶部接触件tc的最底表面低的水平高度处。底部接触件bc在第三方向d3上的高度可大于顶部接触件tc在第三方向d3上的最大高度。

79.顶部接触件tc的一部分可与第二上部源极/漏极图案sd2b的侧表面邻近,并且可在第三方向d3上延伸。然而,示例实施例不限于此。

80.如图1a中所示,底部接触件bc可在第一方向d1上不与公共接触件cc重叠,顶部接触件tc的一部分可在第一方向d1上与公共接触件cc重叠。底部接触件bc可在第一方向d1上与覆盖图案cp重叠,顶部接触件tc的一部分可在第一方向d1上与栅电极ge重叠。

81.再次参照图1a和图1d,可在第三区域r3上设置穿透覆盖图案cp的第一部分cpa以便与栅电极ge的顶表面接触的栅极接触件gc。

82.公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc中的每个可包括导电图案和围绕导电图案的阻挡图案(barrier pattern)。例如,导电图案可包括金属。阻挡图案可覆盖导电图案的侧表面和底表面。阻挡图案可包括金属层和/或金属氮化物层。

83.第五绝缘层170可被设置,以覆盖第四绝缘层150、覆盖图案cp、公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc的顶表面。可在第五绝缘层170中设置分别连接到公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc的第一垫(pad)至第四垫p1、p2、p3和p4、以及将公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc分别连接到第一垫至第四垫p1、p2、p3和p4的第一过孔(via)至第四过孔v1、v2、v3和v4。第一垫至第四垫p1、p2、p3和p4以及第一过孔至第四过孔v1、v2、v3和v4可包括导电材料(诸如,金属)。第一垫至第四垫p1、p2、p3和p4中的每个以及第一过孔至第四过孔v1、v2、v3和v4中的每个可通过双镶嵌工艺被形成在单个导电结构中。金属层可被附加地堆叠在第五绝缘层170上。

84.图2a是示出根据一些示例实施例的半导体装置的平面图。图2b、图2c、图2d和图2e分别是沿着图2a的线a-a'、b-b'、c-c'和e-e'截取以示出根据一些示例实施例的半导体装置的剖视图。在下文中,出于容易和方便解释的目的,对与上面的示例实施例相同的技术特征的描述将被省略,并且上面描述的示例实施例之间的差异将被主要描述。

85.参照图2a、图2b、图2c和图2d,有源图案ap可包括由器件隔离层st限定的多个有源鳍(active fin)。具体地,有源图案ap可包括由器件隔离层st限定的第一有源鳍至第四有源鳍af1、af2、af3和af4。

86.第一有源鳍至第四有源鳍af1、af2、af3和af4可以是基底100的部分,并且可以是在第三方向d3上突出的部分。第一有源鳍至第四有源鳍af1、af2、af3和af4中的每个可具有在第三方向d3上突出的鳍形状。使用第一有源鳍至第四有源鳍af1、af2、af3和af4的至少一部分作为沟道的下部晶体管可以是鳍式场效应晶体管(鳍式fet)。

87.第一有源鳍至第四有源鳍af1、af2、af3和af4可在第一方向d1上延伸,并且可在第

二方向d2上彼此间隔开。例如,第一有源鳍至第四有源鳍af1、af2、af3和af4中的每个可具有在第二方向d2上的宽度,该宽度随着在第三方向d3上的水平高度增大而减小。

88.第三有源鳍af3可包括第一部分af3a和第二部分af3b,第一部分af3a和第二部分af3b在第一方向d1上彼此间隔开,覆盖图案cp置于第一部分af3a与第二部分af3b之间。第三有源鳍af3可不被设置在第二区域r2上。第三有源鳍af3的第一部分af3a可被设置在第一区域r1上,第三有源鳍af3的第二部分af3b可被设置在第二区域r2上。

89.第四有源鳍af4可被局部地设置在第二区域r2上。例如,第四有源鳍af4可不被设置在第一区域r1和第三区域r3上。第四有源鳍af4可在第二方向d2上与第三有源鳍af3的第二部分af3b重叠。第四有源鳍af4可被设置为与覆盖图案cp相邻。

90.如图2a中所示,包括设置在第一区域r1上的第一有源鳍af1、第二有源鳍af2和第三有源鳍af3的第一部分af3a的有源图案ap在第二方向d2上的长度可被定义为第一长度l1。包括设置在第二区域r2上的第一有源鳍af1、第二有源鳍af2、第三有源鳍af3的第二部分af3b和第四有源鳍af4的有源图案ap在第二方向d2上的长度可被定义为第二长度l2。包括设置在第三区域r3上的第一有源鳍af1和第二有源鳍af2的有源图案ap在第二方向d2上的长度可被定义为第三长度l3。例如,第一区域至第三区域r1、r2和r3上的有源图案ap在第二方向d2上的长度可彼此不同。第一长度l1可小于第二长度l2,并且可大于第三长度l3。

91.参照图2b和图2c,第一长度l1可对应于在第一下部源极/漏极图案sd1a的底表面处在第二方向d2上的长度。第二长度l2可对应于在第二下部源极/漏极图案sd1b的底表面处在第二方向d2上的长度。

92.在第三区域r3上,第一有源鳍af1和第二有源鳍af2的上部部分可被覆盖有栅电极ge,并且在第二方向d2上与栅电极ge重叠的第一有源鳍af1和第二有源鳍af2的上部部分可被统称为第一沟道图案ch1。

93.在第三方向d3上延伸的第二沟道图案ch2可被设置在第一沟道图案ch1上。第二沟道图案ch2可在第三方向d3上与第一沟道图案ch1重叠。第二沟道图案ch2可在第三方向d3上与第一沟道图案ch1间隔开。第二沟道图案ch2可包括分别设置在第一有源鳍af1和第二有源鳍af2上的两个部分,并且这两个部分可在第二方向d2上彼此间隔开。第一沟道图案ch1和第二沟道图案ch2可在第一方向d1上延伸。

94.在第一区域r1上,第一下部源极/漏极图案sd1a可被设置在第一有源鳍af1、第二有源鳍af2以及第三有源鳍af3的第一部分af3a的顶表面上。在第二区域r2上,第二下部源极/漏极图案sd1b可被设置在第一有源鳍af1、第二有源鳍af2、第三有源鳍af3的第二部分af3b以及第四有源鳍af4的顶表面上。

95.第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可被设置在第一沟道图案ch1的两侧处,并且可与第一沟道图案ch1的侧表面接触。第一下部源极/漏极图案sd1a在第二方向d2上的长度可小于第二下部源极/漏极图案sd1b在第二方向d2上的长度。

96.第一绝缘层110可被设置,以覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b。第一绝缘层110可填充器件隔离层st与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b之间的空间。可在基底100的第一区域r1上设置在第二方向d2上与第一下部源极/漏极图案sd1a的侧表面间隔开并且在第一方向d1上与第二下部源极/漏极图案sd1b的侧表面间隔开的第二绝缘层120。可选地,在特定示例实施例中,第二绝缘层120

可与第一下部源极/漏极图案sd1a的侧表面接触。

97.第三绝缘层130可被设置在第一下部源极/漏极图案sd1a、第二下部源极/漏极图案sd1b以及第一绝缘层110上。第一绝缘层110可填充第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个与第三绝缘层130之间的空间。可选地,在特定示例实施例中,第三绝缘层130可共形地覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个的顶表面和侧表面,在这种情况下,第一绝缘层110可不被布置在第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个与第三绝缘层130之间。

98.在第二方向d2上延伸的第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可被设置在第三绝缘层130上。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个可在第三方向d3上与第一有源鳍af1和第二有源鳍af2重叠。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个可在第三方向d3上不与第三有源鳍af3重叠。

99.第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可被设置在第二沟道图案ch2的两侧处,并且可与第二沟道图案ch2的侧表面接触。第一上部源极/漏极图案sd2a在第二方向d2上的长度可基本等于第二上部源极/漏极图案sd2b在第二方向d2上的长度。

100.覆盖第一有源鳍af1和第二有源鳍af2并在第二方向d2上延伸的栅电极ge可被设置在第三区域r3上。栅电极ge可在第三方向d3上与第一沟道图案ch1和第二沟道图案ch2重叠。栅电极ge可围绕第二沟道图案ch2。更具体地,栅电极ge可覆盖被称为第一沟道图案ch1的第一有源鳍af1和第二有源鳍af2中的每个的两个侧表面和顶表面的一部分,并且可覆盖第二沟道图案ch2的顶表面、底表面和两个侧表面。栅极绝缘图案gi可被布置在栅电极ge与第一沟道图案ch1和第二沟道图案ch2中的每个之间。

101.栅电极ge可包括在第三方向d3上与第一有源鳍af1和第二有源鳍af2重叠的重叠部分gep。栅电极ge的重叠部分gep可包括在第三方向d3上与第一有源鳍af1的顶表面重叠的第一部分、在第三方向d3上与第二有源鳍af2的顶表面重叠的第二部分、以及在第一部分与第二部分之间的第三部分。

102.再次参照图2a和图2b,公共接触件cc的第一部分cca可被设置在第三有源鳍af3的第一部分af3a上,公共接触件cc的第二部分ccb可被设置在第一有源鳍af1和第二有源鳍af2上。

103.再次参照图2a和图2c,底部接触件bc可被设置在第四有源鳍af4上,顶部接触件tc可被设置在第一有源鳍af1和第二有源鳍af2上。

104.图3、图4和图5是与图2d的部分“x”对应以示出根据一些示例实施例的半导体装置的部分的放大视图。在下文中,出于容易和方便解释的目的,对与上面描述的示例实施例中相同的技术特征的描述将被省略,并且上面描述的示例实施例之间的差异将被主要描述。

105.参照图3,第一沟道图案ch1可包括在第三方向d3上顺序地堆叠在有源图案ap上的多个下部半导体图案lsp。在第三方向d3上延伸的第二沟道图案ch2可被设置在第一沟道图案ch1上。第二沟道图案ch2可包括设置在第一沟道图案ch1上的两个部分,并且这两个部分可在第二方向d2上彼此间隔开。

106.参照图4,包括在第三方向d3上顺序地堆叠的多个上部半导体图案usp的第二沟道

图案ch2可被设置在被称为第一沟道图案ch1的第一有源鳍af1和第二有源鳍af2的顶表面上。第二沟道图案ch2的上部半导体图案usp中的最底部的上部半导体图案usp可在第三方向d3上与第一有源鳍af1和第二有源鳍af2间隔开。

107.参照图5,在第三方向d3上顺序地堆叠的多个下部半导体图案lsp和多个上部半导体图案usp可被设置在第一有源鳍af1和第二有源鳍af2中的每个的顶表面上。例如,第一有源鳍af1和第二有源鳍af2的顶表面可与器件隔离层st的顶表面基本共面。下部半导体图案lsp和上部半导体图案usp中的每个可具有线形(wire shape),线形具有圆形横截面并且在第一方向d1上延伸。设置在第一有源鳍af1和第二有源鳍af2中的每个的顶表面上的下部半导体图案lsp和上部半导体图案usp可在第三方向d3上彼此间隔开。下部半导体图案lsp和上部半导体图案usp中的每个可被栅电极ge围绕。

108.图6a是示出根据一些示例实施例的半导体装置的平面图。图6b和图6c分别是沿着图6a的线b-b'和f-f'截取以示出根据一些示例实施例的半导体装置的剖视图。在下文中,出于容易和方便解释的目的,对与上面描述的实施例中相同的技术特征的描述将被省略,并且上面描述的示例实施例之间的差异将被主要描述。

109.参照图6a、图6b和图6c,有源图案ap可包括由器件隔离层st限定的多个有源鳍。更具体地,有源图案ap可包括由器件隔离层st限定的第一有源鳍至第三有源鳍af1、af2和af3。第三有源鳍af3可包括第一部分af3a和第二部分af3b,第一部分af3a和第二部分af3b在第一方向d1上彼此间隔开,覆盖图案cp置于第一部分af3a与第二部分af3b之间。

110.底部接触件bc可被设置在第三有源鳍af3的第二部分af3b上。如图6a中所示,底部接触件bc可在第一方向d1上与公共接触件cc重叠。底部接触件bc可在第一方向d1上与公共接触件cc间隔开,覆盖图案cp置于底部接触件bc与公共接触件cc之间。

111.可设置围绕底部接触件bc的侧表面的底部接触间隔件bcsp。底部接触件bc可在第二方向d2上与顶部接触件tc间隔开,底部接触间隔件bcsp置于底部接触件bc与顶部接触件tc之间。例如,底部接触间隔件bcsp可包括氧化硅、氮化硅和氮氧化硅中的至少一者。因为围绕底部接触件bc的侧表面的底部接触间隔件bcsp被设置,所以空间的使用可被提高,并且半导体装置的集成密度可被提高。

112.图7a是示出根据一些示例实施例的半导体装置的平面图。图7b、图7c和图7d分别是沿着图7a的线a-a'、b-b'和c-c'截取以示出根据一些示例实施例的半导体装置的剖视图。在下文中,出于容易和方便解释的目的,对与上面描述的示例实施例中相同的技术特征的描述将被省略,并且上面描述的示例实施例之间的差异将被主要描述。

113.参照图7a、图7b、图7c和图7d,根据一些示例实施例的半导体装置可包括例如第一反相器(inverter)inv1和第二反相器inv2。在下文中,将描述第一反相器inv1和第二反相器inv2。然而,示例实施例不限于此。根据特定示例实施例的半导体装置可包括各种逻辑电路(例如,与(and)电路、或(or)电路、与非(nand)电路、或非(nor)电路、触发器电路(flip-flop circuit)和/或锁存器电路)以及反相器。

114.第一反相器inv1和第二反相器inv2中的每个可具有与参照图2a至图2e描述的半导体装置基本相同的结构。第一反相器inv1的组件和第二反相器inv2的组件可在第二方向d2上彼此面对,并且可被对称地布置。第一反相器inv1和第二反相器inv2可共享单个第四有源鳍af4和单个底部接触件bc。第一反相器inv1的组件和第二反相器inv2的组件可相对

于单个底部接触件bc对称。单个底部接触件bc可被设置在单个第四有源鳍af4上。单个底部接触件bc可用作第一反相器inv1和第二反相器inv2中的每个中的底部接触件bc。因为第一反相器inv1和第二反相器inv2共享单个底部接触件bc,所以空间的使用可被提高,并且半导体装置的集成密度可被提高。

115.图8a是示出根据一些示例实施例的半导体装置的平面图。图8b是沿着图8a的线b-b'截取以示出根据一些示例实施例的半导体装置的剖视图。在下文中,出于容易和方便解释的目的,对与上面描述的示例实施例中相同的技术特征的描述将被省略,并且上面描述的示例实施例之间的差异将被主要描述。

116.参照图8a和图8b,第一反相器inv1和第二反相器inv2可共享两个第四有源鳍af4和单个底部接触件bc。单个底部接触件bc可在第三方向d3上与两个第四有源鳍af4重叠。单个底部接触件bc可用作第一反相器inv1和第二反相器inv2中的每个中的底部接触件bc。

117.图9a、图12a、图13a、图14a、图15a、图16a和图17a是示出根据一些示例实施例的制造半导体装置的方法的平面图。图9b、图10、图11、图12b、图13b、图14b、图15b和图16b分别是沿着图9a的线e-e'、图12a的线e-e'、图13a的线e-e'、图14a的线e-e'、图15a的线e-e'和图16a的线e-e'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图。图12c、图13c和图14c分别是沿着图12a的线a-a'、图13a的线a-a'和图14a的线a-a'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图。图13d和图14d分别是沿着图13a的线b-b'和图14a的线b-b'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图。图16c和图17b分别是沿着图16a的线c-c'和图17a的线c-c'截取以示出根据一些示例实施例的制造半导体装置的方法的剖视图。

118.在下文中,将参照图9a至图17b详细描述根据一些示例实施例的制造半导体装置的方法。

119.参照图9a和图9b,第一牺牲层(sacrificial layer)sl1和第一有源层al1可交替且重复地被堆叠在基底100上。第二牺牲层sl2和第二有源层al2可交替且重复地被堆叠在第一有源层al1中的最顶部的第一有源层al1上。

120.第一牺牲层sl1和第二牺牲层sl2可包括针对第一有源层al1和第二有源层al2具有蚀刻选择性的材料。例如,第一牺牲层sl1和第二牺牲层sl2可由硅锗(sige)形成,第一有源层al1和第二有源层al2可由硅(si)形成。可使用外延生长工艺(epitaxial growth process)形成第一牺牲层sl1、第二牺牲层sl2、第一有源层al1和第二有源层al2中的每个。

121.可图案化第一牺牲层sl1、第二牺牲层sl2、第一有源层al1、第二有源层al2、以及基底100的上部部分。可在基底100中形成限定有源图案ap的沟槽(trench)。可在沟槽中形成器件隔离层st(参见,图1b、图1c和图1d)。

122.可在有源图案ap上形成在第二方向d2上与有源图案ap相交的栅极牺牲图案pp。栅极牺牲图案pp可被形成,以具有在第二方向d2上延伸的线形或条形。栅极牺牲图案pp的形成可包括:在第二有源层al2中的最顶部的第二有源层al2的顶表面上沉积栅极牺牲层,在栅极牺牲层上形成硬掩模图案mp,以及使用硬掩模图案mp作为蚀刻掩模来图案化栅极牺牲层。栅极牺牲图案pp可由例如多晶硅形成。

123.第一栅极间隔层gsl1可被形成,以覆盖栅极牺牲图案pp的顶表面和两个侧表面。第一栅极间隔层gsl1可延伸到第二有源层al2中的最顶部的第二有源层al2的顶表面上。第

一栅极间隔层gsl1可由例如氮化硅形成。

124.参照图9b和图10,可通过第一蚀刻工艺去除第一栅极间隔层gsl1的一部分。通过这个第一蚀刻工艺,可从第二有源层al2中的最顶部的第二有源层al2的顶表面去除第一栅极间隔层gsl1。通过第一蚀刻工艺,第一栅极间隔层gsl1可保留在硬掩模图案mp的顶表面和侧表面以及栅极牺牲图案pp的侧表面上。第一蚀刻工艺可以是各向异性蚀刻工艺。

125.此后,可在第二牺牲层sl2和第二有源层al2上执行第一图案化工艺。第一图案化工艺可使用栅极牺牲图案pp和第一栅极间隔层gsl1作为蚀刻掩模。可通过第一图案化工艺形成包括上部半导体图案usp的第二沟道图案ch2。在一些示例实施例中,在第一图案化工艺之后,第二牺牲层sl2中的最底部的第二牺牲层sl2的下部部分可保留在第一有源层al1中的最顶部的第一有源层al1上。

126.第二栅极间隔层gsl2可被形成,以覆盖第一栅极间隔层gsl1的顶表面和侧表面、上部半导体图案usp的侧表面以及第二牺牲层sl2的侧表面。第二栅极间隔层gsl2可延伸到在第一有源层al1中的最顶部的第一有源层al1上保留的最底部的第二牺牲层sl2的顶表面上。第二栅极间隔层gsl2可包括例如氮化硅。

127.参照图10和图11,可通过第二蚀刻工艺去除第二栅极间隔层gsl2的一部分。通过第二蚀刻工艺,可从在第一有源层al1中的最顶部的第一有源层al1上保留的最底部的第二牺牲层sl2的顶表面去除第二栅极间隔层gsl2。通过第二蚀刻工艺,第二栅极间隔层gsl2可保留在第一栅极间隔层gsl1的顶表面和侧表面、上部半导体图案usp的侧表面、以及第二牺牲层sl2的侧表面上。第二蚀刻工艺可以是各向异性蚀刻工艺。

128.此后,可在第一牺牲层sl1和第一有源层al1上执行第二图案化工艺。第二图案化工艺可使用栅极牺牲图案pp、第一栅极间隔层gsl1和第二栅极间隔层gsl2作为蚀刻掩模。可通过第二图案化工艺形成包括下部半导体图案lsp的第一沟道图案ch1。在一些示例实施例中,还可通过第二图案化工艺去除基底100的一部分。

129.参照图12a、图12b和图12c,可在有源图案ap上形成在第二方向d2上延伸的第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b。第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可通过使用基底100和下部半导体图案lsp作为晶种的外延生长工艺形成。第一下部源极/漏极图案sd1a可被形成在第一区域r1上,第二下部源极/漏极图案sd1b可被形成在第二区域r2上。第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b可分别被形成在栅极牺牲图案pp的两侧。第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b中的每个可与第一沟道图案ch1的下部半导体图案lsp的侧表面、第一牺牲层sl1的侧表面、和第二栅极间隔层gsl2的最底表面接触。

130.覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b的侧表面以及器件隔离层st的顶表面的第一绝缘层110可被形成,覆盖第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b的顶表面的第三绝缘层130可被形成。牺牲绝缘层140可被形成在第三绝缘层130上。牺牲绝缘层140的顶表面可与第二栅极间隔层gsl2的顶表面基本共面。牺牲绝缘层140可由针对第三绝缘层130具有蚀刻选择性的材料形成。

131.参照图12b、图12c、图13a、图13b、图13c和图13d,可在第一区域r1上形成穿透第三绝缘层130、第一下部源极/漏极图案sd1a和第一绝缘层110的第一沟槽tr1。第一沟槽tr1可暴露第三绝缘层130的侧表面、第一下部源极/漏极图案sd1a的第一侧表面sw11、和有源图

案ap的侧表面。第一沟槽tr1的底表面可位于比器件隔离层st的底表面低的水平高度处。

132.牺牲绝缘层140可被去除。第二栅极间隔层gsl2的一部分可与牺牲绝缘层140一起被去除。此时,第二栅极间隔层gsl2的与第三绝缘层130的侧表面接触的其他部分可保留,因此一对第二栅极间隔件gs2可被形成。

133.参照图14a、图14b、图14c和图14d,可形成填充第一沟槽tr1的第二绝缘层120。第二绝缘层120的顶表面可与第三绝缘层130的顶表面基本共面。

134.在第二方向d2上延伸的第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可被形成在第三绝缘层130上。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可通过使用上部半导体图案usp作为晶种的外延生长工艺被形成。第一上部源极/漏极图案sd2a可被形成在第一下部源极/漏极图案sd1a上(即,可被形成在第一区域r1上),第二上部源极/漏极图案sd2b可被形成在第二下部源极/漏极图案sd1b上(即,可被形成在第二区域r2上)。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b可分别被形成在栅极牺牲图案pp的两侧。第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b中的每个可与第一栅极间隔层gsl1的侧表面、第二沟道图案ch2的上部半导体图案usp的侧表面、第二牺牲层sl2的侧表面、和第二栅极间隔件gs2的顶表面接触。

135.第四绝缘层150可被形成,以覆盖第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b的侧表面和顶表面、以及第二绝缘层120和第三绝缘层130的顶表面。第四绝缘层150的顶表面可与第一栅极间隔层gsl1的顶表面基本共面。

136.参照图14b、图15a和图15b,可通过平坦化工艺去除第一栅极间隔层gsl1的上部部分、硬掩模图案mp、以及第四绝缘层150的上部部分。例如,平坦化工艺可以是回蚀工艺(etch-back process)或化学机械抛光(chemical mechanical polishing,cmp)工艺。因为第一栅极间隔层gsl1的上部部分通过平坦化工艺被去除,所以第一栅极间隔件gs1可被形成。通过平坦化工艺,第四绝缘层150的顶表面可与第一栅极间隔件gs1的顶表面基本共面。

137.接下来,可通过第三蚀刻工艺选择性地去除暴露于外部的栅极牺牲图案pp、第一牺牲层sl1和第二牺牲层sl2。第三蚀刻工艺可以是湿法蚀刻工艺(wet etching process)。可通过选择性地去除栅极牺牲图案pp、第一牺牲层sl1和第二牺牲层sl2来形成空的空间es。第一沟道图案ch1的下部半导体图案lsp的顶表面和底表面、以及第二沟道图案ch2的上部半导体图案usp的顶表面和底表面可被空的空间es暴露。

138.参照图15a、图15b、图16a、图16b和图16c,栅极绝缘图案gi、栅电极ge和覆盖图案cp可被形成,以填充空的空间es。栅电极ge可在第三区域r3上沿第二方向d2延伸,并且栅电极ge在第二方向d2上的长度可大于有源图案ap在第二方向d2上的最大长度。

139.栅极绝缘图案gi可共形地被形成在栅电极ge与下部半导体图案lsp之间,栅电极ge与上部半导体图案usp之间,在栅电极ge与第一下部源极/漏极图案sd1a和第二下部源极/漏极图案sd1b之间,栅电极ge与第一上部源极/漏极图案sd2a和第二上部源极/漏极图案sd2b之间、以及栅电极ge与第一栅极间隔件gs1之间。

140.覆盖图案cp可被形成在栅电极ge的最顶表面上,并且可与第一栅极间隔件gs1的侧表面接触。覆盖图案cp的顶表面可与第一栅极间隔件gs1的顶表面和第四绝缘层150的顶表面基本共面。

141.参照图17a和图17b,可在第三区域r3上形成穿透覆盖图案cp、栅电极ge、第一沟道

图案ch1、第二沟道图案ch2以及有源图案ap的第二沟槽tr2。第二沟槽tr2可暴露第一沟道图案ch1的下部半导体图案lsp的第二侧表面lsw2、第二沟道图案ch2的上部半导体图案usp的第二侧表面usw2、和有源图案ap的侧表面。第二沟槽tr2的底表面可位于比器件隔离层st的底表面低的水平高度处。

142.参照图1a、图1b、图1c、图1d、图1e、图1f、图17a和图17b,可形成填充第二沟槽tr2的覆盖图案cp。更具体地,覆盖图案cp可包括预先形成在栅电极ge上的第一部分cpa和填充第二沟槽tr2的第二部分cpb。覆盖图案cp的第一部分cpa的顶表面可与第二部分cpb的顶表面基本共面。覆盖图案cp的第二部分cpb可与栅电极ge的侧表面接触,并且可在第三区域r3上在第二方向d2上延伸。

143.此后,可形成公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc。公共接触件cc可穿透第一区域r1上的第三绝缘层130和第四绝缘层150,以便与第一下部源极/漏极图案sd1a和第一上部源极/漏极图案sd2a接触。底部接触件bc可穿透第二区域r2上的第三绝缘层130和第四绝缘层150,以便与第二下部源极/漏极图案sd1b的顶表面接触。顶部接触件tc可穿透第四绝缘层150,以便与第二上部源极/漏极图案sd2b的顶表面接触。栅极接触件gc可穿透第三区域r3上的覆盖图案cp的第一部分cpa,以便与栅电极ge的顶表面接触。

144.此后,第五绝缘层170可被形成,以覆盖公共接触件cc、底部接触件bc、顶部接触件tc和栅极接触件gc,并且第一垫至第四垫p1、p2、p3和p4以及第一过孔至第四过孔v1、v2、v3和v4可在第五绝缘层170中被形成。

145.根据示例实施例的半导体装置可包括与下部源极/漏极图案和上部源极/漏极图案的顶表面接触的垂直接触件(即,公共接触件、底部接触件和顶部接触件),因此形成接触件的工艺可容易地被执行。

146.另外,在根据示例实施例的半导体装置中,下部源极/漏极图案和上部源极/漏极图案可在垂直于栅电极的延伸方向的方向上被外延生长,并且下部源极/漏极图案和上部源极/漏极图案中的每个的宽度(例如,第一方向上的宽度)可一致地被保持。因此,外延生长工艺可容易地被执行,并且重复地形成的栅电极的间距可被减小。因此,半导体装置的集成密度可被提高,并且由结构的非一致性引起的电特性的劣化可被最小化或防止。

147.虽然已经具体示出和描述了示例实施例的方面,但是本领域普通技术人员将理解,在不脱离所附权利要求的精神和范围的情况下,可在其中进行形式和细节上的变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。