1.本发明是有关于一种半导体结构及其制作方法,特别是有关于一种增强型(enhancement-mode)高电子迁移率晶体管(high electron mobility transistor,hemt)的结构及其制作方法。

背景技术:

2.gan材料因具有宽能带间隙及高速移动电子,广泛应用于高功率半导体结构当中,特别是射频与功率上的应用。传统上,高电子迁移率晶体管(high electron mobility transistor,hemt)利用三五族半导体堆叠,在其接口处形成异质结(heterojunction)。由于异质结处的能带弯曲,导带(conduction band)弯曲深处形成位能井(potential well),并在位能井中形成二维电子气(two-dimensional electron gas,2deg)。

3.然而高电子迁移率晶体管通常是一个常开型(即,耗尽型(depletion mode))器件。因此,需要施予额外负偏压才能关闭器件,除了使用上相对较不方便外,也局限了器件的使用范围。为了解决此一问题,目前已有增强型(enhancement-mode)高电子迁移率晶体管被提出,利用在形成金属栅极之前,以氟离子轰击破坏氮化铝镓层的晶格结构;或以刻蚀方式在氮化铝镓层中形成凹室(recess),再于凹室底部外延具有p型杂质的氮化镓层的栅极堆叠结构,以达到不需施予额外偏压即可关闭二维电子气的常关型(normally-off mode)器件。

4.然而,所述方法皆有其技术瓶颈。例如,当采用刻蚀工艺来形成凹室结构以提升高电子迁移率晶体管的击穿电压时,由于刻蚀精准度不易调控,不易将凹室底部的氮化铝镓层厚度调控在特定范围内,常使相同高电子迁移率晶体管器件之间的夹止电压(pinch-off voltage)产生很大的变异。此外,在凹室中底部外延生成具有p型杂质的氮化镓层需要特殊的外延技术,并且非常耗时。再者,由于氟的原子尺寸较小,以氟离子轰击的高电子迁移率晶体管,在长期高温高压操作下,氟离子容易从氮化铝镓层中扩散出来,易使增强型高电子迁移率电晶体器件反转成耗尽型器件,导致整体电路失效。

5.因此,有需要提供一种先进的增强型高电子迁移率晶体管及其制作方法,来解决习知技术所面临的问题。

技术实现要素:

6.本发明在此提出用以形成增强型高电子迁移率晶体管的半导体结构,通过调整第一顶部氮化物半导体层以及第二顶部氮化物半导体层的厚度以及p型掺杂的浓度,能够有效的控制形成载流子沟道的导通电压且同时增进动态导通电阻的特性。

7.此外,相对于先前技术中产生凹室所需的刻蚀精准度以及在凹室的底部外延具有p型杂质的氮化镓层所需的特殊外延技术,本发明提出的半导体结构的制造方法使用的是一般的外延工艺以及一般的刻蚀工艺,将有效的降低生产成本以及生产时间。相对于先前技术中利用氟离子轰击的高电子迁移率晶体管所产生的增强型器件反转为耗尽型器件的

问题,由于本发明的半导体结构及其制造方法并未使用氟离子,因此可轻易排除上述问题。

8.有鉴于此,本发明提出一种半导体结构,包括一基板、一第一氮化物半导体层、一第二氮化物半导体层、一第三氮化物半导体层、一第四氮化物半导体层以及一第五氮化物半导体层。所述第一氮化物半导体层设置于所述基板之上。所述第二氮化物半导体层设置于所述第一氮化物半导体层之上,其中所述第二氮化物半导体层的带隙高于所述第一氮化物半导体层的带隙。所述一第三氮化物半导体层设置于所述第二氮化物半导体层之上以及一源极电极以及一漏极电极之间,具有一第一p型掺杂。所述第四氮化物半导体层设置于所述第二氮化物半导体层之上且位于所述第三氮化物半导体层以及上述漏极电极之间,具有上述第一p型掺杂。所述第五氮化物半导体层设置于所述第三氮化物半导体层之上,具有一第二p型掺杂。

9.根据本发明的一实施例,半导体结构更包括一栅极电极以及一第二漏极电极。所述栅极电极设置于所述第五氮化物半导体层之上,且与所述第五氮化物半导体层直接接触。所述第二漏极电极设置于所述第四氮化物半导体层之上,且与所述第四氮化物半导体层直接接触,其中所述第二漏极电极与所述漏极电极相邻且相互电连接,其中所述源极电极以及所述漏极电极与所述第二氮化物半导体层直接接触。

10.根据本发明的一实施例,所述第二p型掺杂浓度不小于所述第一p型掺杂的浓度。

11.根据本发明一实施例,所述第三氮化物半导体层以及第四氮化物半导体层具有一第一厚度,其中所述第五氮化物半导体层具有一第二厚度,其中所述第二厚度不小于所述第一厚度。

12.根据本发明的一实施例,所述第一氮化物半导体层包括gan,其中所述第二氮化物半导体层包括alxga1-xn,且0《x《=1。

13.根据本发明的一实施例,所述第三氮化物半导体层以及所述第四氮化物半导体层包括具有所述第一p型掺杂的alyga1-yn,且0≤y≤1,其中所述第五氮化物半导体层包括具有所述第二p型掺杂的alzga1-zn,且0≤z≤1。

14.本发明更提出一种半导体结构的制造方法,包括提供一基板;在上所述基板之上形成一第一氮化物半导体层;在所述第一氮化物半导体层之上形成一第二氮化物半导体层,其中所述第二氮化物半导体层的带隙高于所述第一氮化物半导体层的带隙;在所述第二氮化物半导体层之上形成一第一顶部氮化物半导体层,其中所述第一顶部氮化物半导体层具有一第一p型掺杂;在所述第一顶部氮化物半导体层之上形成一第二顶部氮化物半导体层,其中所述第二顶部氮化物半导体层具有一第二p型掺杂;在所述第二顶部氮化物半导体层之上形成一栅极电极;利用所述栅极电极作为一刻蚀光掩膜,刻蚀所述第二顶部氮化物半导体层而形成一第五氮化物半导体层,其中所述栅极电极与所述第五氮化物半导体层直接接触;以及刻蚀所述第一顶部氮化物半导体层而形成一第三氮化物半导体层以及一第四氮化物半导体层,且露出所述第一顶部氮化物半导体层,其中所述第五氮化物半导体层堆叠于所述第三氮化物半导体层之上。

15.根据本发明的一实施例,制造方法还包括在所述第二氮化物半导体层之上形成一源极电极以及一漏极电极,其中所述源极电极以及所述漏极电极位于所述第三氮化物半导体层以及所述第四氮化物半导体层的相异两侧;以及在所述第四氮化物半导体层之上形成一第二漏极电极,其中所述第二漏极电极与所述第四氮化物半导体层直接接触,且所述漏

极电极以及所述第二漏极电极相邻且相互电连接。

16.根据本发明的一实施例,所述第二p型掺杂的浓度不小于所述第一p型掺杂的浓度,且其中所述第一氮化物半导体层包括gan,所述第二氮化物半导体层包括alxga1-xn,0《x《=1,所述第一顶部氮化物半导体层包括具有所述第一p型掺杂的alyga1-yn,且0≤y≤1,所述第二顶部氮化物半导体层包括具有所述第二p型掺杂的alzga1-zn,且0≤z≤1。

17.根据本发明的一实施例,所述第二顶部氮化物半导体层的厚度不小于所述第一顶部氮化物半导体层的厚度。

附图说明

18.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

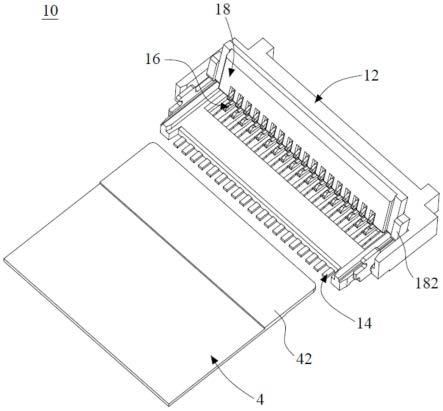

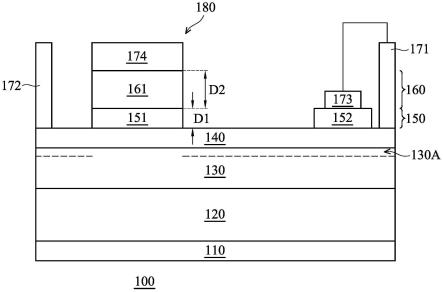

19.图1为根据本发明的一实施例所述的半导体结构的剖面图;

20.图2a至图2d为根据本发明的一实施例所述的半导体结构的制造方法的剖面示意图。

21.【附图标号】

22.100:半导体结构

23.110:基板

24.120:缓冲层

25.130:第一氮化物半导体层

26.130a:载流子沟道

27.140:第二氮化物半导体层

28.150:第一顶部氮化物半导体层

29.151:第三氮化物半导体层

30.152:第四氮化物半导体层

31.160:第二顶部氮化物半导体层

32.161:第五氮化物半导体层

33.171:漏极电极

34.172:源极电极

35.173:第二漏极电极

36.174:栅极电极

37.180:栅极堆叠结构

38.d1:第一厚度

39.d2:第二厚度

具体实施方式

40.以下针对本揭露一些实施例的器件衬底、半导体装置及半导体装置的制造方法作详细说明。应了解的是,以下的叙述提供许多不同的实施例或例子,用以实施本揭露一些实

施例的不同样态。以下所述特定的器件及排列方式仅为简单清楚描述本揭露一些实施例。当然,这些仅用以举例而非本揭露的限定。此外,在不同实施例中可能使用重复的标号或标示。这些重复仅为了简单清楚地叙述本揭露一些实施例,不代表所讨论的不同实施例及/或结构之间具有任何关联性。再者,当述及一第一材料层位于一第二材料层上或之上时,包括第一材料层与第二材料层直接接触的情形。或者,也可能间隔有一或更多其它材料层的情形,在此情形中,第一材料层与第二材料层之间可能不直接接触。

41.此外,实施例中可能使用相对性的用语,例如“较低”或“底部”及“较高”或“顶部”,以描述图式的一个器件对于另一器件的相对关系。能理解的是,如果将图式的装置翻转使其上下颠倒,则所叙述在“较低”侧的器件将会成为在“较高”侧的器件。

42.在此,“约”、“大约”、“大抵”的用语通常表示在一给定值或范围的20%之内,较佳是10%之内,且更佳是5%之内,或3%之内,或2%之内,或1%之内,或0.5%之内。在此给定的数量为大约的数量,也即在没有特定说明“约”、“大约”、“大抵”的情况下,仍可隐含“约”、“大约”、“大抵”的含义。

43.能理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种器件、组成成分、区域、层、及/或部分,这些器件、组成成分、区域、层、及/或部分不应被这些用语限定,且这些用语仅是用来区别不同的器件、组成成分、区域、层、及/或部分。因此,以下讨论的一第一器件、组成成分、区域、层、及/或部分可在不偏离本揭露一些实施例的教示的情况下被称为一第二器件、组成成分、区域、层、及/或部分。

44.除非另外定义,在此使用的全部用语(包括技术及科学用语)具有与此篇揭露所属的本领域技术人员所通常理解的相同涵义。能理解的是,这些用语,例如在通常使用的字典中定义的用语,应被解读成具有与相关技术及本揭露的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本揭露实施例有特别定义。

45.本揭露一些实施例可配合图式一并理解,本揭露实施例的图式也被视为本揭露实施例说明的一部分。需了解的是,本揭露实施例的图式并未以实际装置及器件的比例绘示。在图式中可能夸大实施例的形状与厚度以便清楚表现出本揭露实施例的特征。此外,图式中的结构及装置以示意的方式绘示,以便清楚表现出本揭露实施例的特征。

46.在本揭露一些实施例中,相对性的用语例如“下”、“上”、“水平”、“垂直”、“之下”、“之上”、“顶部”、“底部”等等应被理解为该段以及相关图式中所绘示的方位。此相对性的用语仅是为了方便说明的作用,其并不代表其所叙述的装置需以特定方位来制造或运作。而关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构直接接触,或者也可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语也可包括两个结构都可移动,或者两个结构都固定的情况。

47.本发明的实施例揭露半导体装置的实施例,且所述实施例可被包含于例如微处理器、存储器件及/或其他器件的集成电路(integrated circuit,ic)中。所述集成电路也可包含不同的被动和主动微电子器件,例如薄膜电阻器(thin-film resistor)、其他类型电容器例如,金属-绝缘体-金属电容(metal-insulator-metal capacitor,mimcap)、电感、二极管、金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistors,mosfets)、互补式mos晶体管、双极型结晶体管(bipolar junction transistors,bjts)、横向扩散型mos晶体管、高功率mos晶体管或其他类型的晶体管。在本

发明所属技术领域技术人员可以了解也可将半导体装置使用于包含其他类型的半导体器件于集成电路之中。

48.图1为根据本发明的一实施例所述的半导体结构的剖面图。如图1所示,半导体结构100包含基板110。在一些实施例中,基板110可为整块的(bulk)半导体基板或包含由不同材料形成的复合基板,并且可以将基板110掺杂(例如,使用p型或n型掺质)或不掺杂。在一些实施例中,基板110可包含半导体基板、玻璃基板或陶瓷基板,例如硅基板、硅锗基板、碳化硅、氮化铝基板、蓝宝石(sapphire)基板、前述的组合或类似的材料,但本发明实施例并非以此为限。在一些实施例中,基板110可包含绝缘体上覆半导体(semiconductor-on-insulator,soi)基板,其经由在绝缘层上设置半导体材料所形成。

49.如图1所示,半导体结构100还包含缓冲层120。在一些实施例,缓冲层120设置在基板110上方。缓冲层120的功用是为减少基板110与之后形成的氮化物半导体层所产生的应变。缓冲层120可例如为一aln晶核层及algan过渡层的组合。缓冲层120可减小基板110以及之后形成的氮化物半导体层之间晶格错差所造成缺陷。

50.如图1所示,半导体结构100还包含第一氮化物半导体层130以及形成于第一氮化物半导体层130上方的第二氮化物半导体层140。根据本发明的一实施例,第一氮化物半导体层130以及第二氮化物半导体层140为具有不同能带隙(band gap)的材料层,且第二氮化物半导体层140的带隙高于第一氮化物半导体层130的带隙。

51.根据本发明的一些实施例,第一氮化物半导体层130以及第二氮化物半导体层140是由周期表上第iii-v族的元素所形成的化合物所构成,然而,第一氮化物半导体层130以及第二氮化物半导体层140彼此在组成上是不同的。根据本发明的一些实施例,第一氮化物半导体层130包括gan层,第二氮化物半导体层140包括alxga1-xn层,其中0《x《=1。第一氮化物半导体层130与第二氮化物半导体层140彼此直接接触。由于第一氮化物半导体层130以及第二氮化物半导体层140具有不同能带隙(band gap),因此在第一氮化物半导体层130以及第二氮化物半导体层140之间的界面形成一异质结(heterojunction)。

52.第一氮化物半导体层130可使用含镓的前驱物以及含氮的前驱物,藉由金属有机化学气相沉积(metal-organic chemical vapor deposition,mocvd)外延长成。含镓的前驱物可包括三甲基镓(trimethylgallium,tmg)、三乙基镓(triethylgallium,teg)、或其他合适的化学品;含氮的前驱物包括氨(ammonia,nh3)、叔丁胺(tertiarybutylamine,tbam)、苯肼(phenyl hydrazine)或其他合适的化学品。然而,本发明实施例并非以此为限。第一氮化物半导体层130也可由其他沉积工艺所形成,例如氢化物气相外延法(hvpe)、分子束外延法(mbe)、其他适合的方法或前述的组合所形成。

53.如图1所示,第二氮化物半导体层140外延成长在第一氮化物半导体层130的上方。第二氮化物半导体层140可由沉积工艺所形成,例如金属有机化学气相沉积(mocvd)、氢化物气相外延法(hvpe)、分子束外延法(mbe)、其他适合的方法或前述的组合所形成。举例来说,第二氮化物半导体层140可使用含铝的前驱物、含镓的前驱物以及含氮的前驱物,藉由有机金属气相外延法(mocvd)外延长成。含铝的前驱物包含三甲基铝(trimethylaluminum,tma)、三乙基铝(triethylaluminum,tea)、或其他合适的化学品;含镓的前驱物包含三甲基镓(tmg)、三乙基镓(teg)或其他合适的化学品;含氮的前驱物包含氨(nh3)、叔丁胺(tbam)、苯肼(phenyl hydrazine)或其他合适的化学品。然而,本发明实施例并非以此为限。

54.第一氮化物半导体层130与第二氮化物半导体层140之间的能带差异(band gap discontinuity)与压电效应(piezo-electric effect)在第一氮化物半导体层130与第二氮化物半导体层140之间的界面附近产生具有高移动传导电子的载流子沟道130a,此载流子沟道130a称为二维电子气(two-dimensional electron gas,2-deg),其形成载流子沟道于第一氮化物半导体层130与第二氮化物半导体层140的界面上。根据本发明的一些实施例,由于半导体结构100为增强型晶体管,因此载流子沟道130a为不连续。

55.根据本发明的一些实施例,如图1所示,半导体结构100更包括利用第一顶部氮化物半导体层150所形成的第三氮化物半导体层151以及第四氮化物半导体层152。第三氮化物半导体层151以及第四氮化物半导体层152皆设置于第二氮化物半导体层140之上,其中第一顶部氮化物半导体层150具有第一p型掺杂且具有第一厚度d1。换句话说,第三氮化物半导体层151以及第四氮化物半导体层152皆具有第一p型掺杂以及第一厚度d1。根据发明的一些实施例,第一p型掺杂包括镁(mg)、铍(be)、钙(ca)、锌(zn)等可形成p型氮化物材料。根据本发明的许多实施例,第一顶部氮化物半导体层150包括p型alyga1-yn,且0≤y≤1。换句话说,第一顶部氮化物半导体层150可包括p型氮化镓层(当y=0),也可包括p型aln(当y=1),还可包括p型alyga1-yn(当0《y《1)。

56.根据本发明的一些实施例,如图1所示,半导体结构100更包括利用第二顶部氮化物半导体层160所形成的第五氮化物半导体层161,且第五氮化物半导体层161设置于第三氮化物半导体层151之上,其中第二顶部氮化物半导体层160具有第二p型掺杂以及第二厚度d2。根据发明的一些实施例,第二p型掺杂包括镁(mg)、铍(be)、钙(ca)、锌(zn)等可形成p型氮化物材料。根据本发明的一实施例,第二顶部氮化物半导体层160包括p型alzga1-zn层,其中0≤z≤1。换句话说,第二顶部氮化物半导体层160可包括p型氮化镓层(当z=0),也可包括p型aln(当z=1),还可包括p型alzga1-zn(当0《z《1)。

57.根据本发明的一实施例,第二厚度d2不小于第一厚度d1,第二p型掺杂的浓度不小于第一p型掺杂的浓度。换句话说,第二顶部氮化物半导体层160的p型掺杂浓度高于或等于第一顶部氮化物半导体层150的p型掺杂浓度,并且第二顶部氮化物半导体层160的第二厚度d2大于或等于第一顶部氮化物半导体层150的第一厚度d1。

58.根据本发明的一些实施例,如图1所示,半导体结构100更包括漏极电极171、源极电极172以及第二漏极电极173。漏极电极171以及源极电极172设置于第二氮化物半导体层140之上且分别位于第三氮化物半导体层151以及第四氮化物半导体层152的相异两侧,其中漏极电极171以及源极电极172直接接触第二氮化物半导体层140。第二漏极电极173形成于第四氮化物半导体层152之上且与第四氮化物半导体层152直接接触。漏极电极171与第二漏极电极173相邻,并且漏极电极171与第二漏极电极173相互电连接。

59.根据本发明的一些实施例,漏极电极171、源极电极172以及第二漏极电极173的材料可包括导电材料,例如金属、金属硅化物、其他合适的材料或前述材料的组合。金属可包括金(au)、镍(ni)、铂(pt)、钯(pd)、铱(ir)、钛(ti)、铬(cr)、钨(w)、铝(al)、铜(cu)、前述的组合、前述的合金或前述的多层。然而,本发明实施例并非以此为限。根据本发明的一些实施例,漏极电极171以及源极电极172与第二氮化物半导体层140形成欧姆接触(ohmic contact),第二漏极电极173与第四氮化物半导体层152形成欧姆接触。根据本发明的另一些实施例,第二漏极电极173还可与第四氮化物半导体层152形成萧特基接触。

60.根据本发明的一些实施例,如图1所示,半导体结构100更包括栅极电极174。栅极电极174设置于第五氮化物半导体层161之上且与第五氮化物半导体层161直接接触。在一些实施例中,栅极电极174的材料可与漏极电极171、源极电极172以及第二漏极电极173的材料相同或相似,在此不多加赘述。根据本发明的一些实施例,栅极电极174与第五氮化物半导体层161形成萧特基接触(schottky-contact)。根据本发明的另一些实施例,栅极电极174与第五氮化物半导体层161形成欧姆接触。

61.根据本发明的一些实施例,如图1所示,半导体结构100形成增强型高电子迁移率晶体管,第三氮化物半导体层151、第五氮化物半导体层161以及栅极电极174形成增强型高电子迁移率晶体管的栅极堆叠结构180,第四氮化物半导体层152、漏极电极171以及第二漏极电极173形成增强型高电子迁移率晶体管的漏极端,源极电极172形成增强型高电子迁移率晶体管的源极端,其中漏极电极171以及源极电极172分别位于栅极电极174以及第二漏极电极173的相异两侧,且漏极电极171以及第二漏极电极173相邻。根据本发明的一些实施例,位于漏极电极171以及栅极电极174之间的第四氮化物半导体层152以及第二漏极电极173用以提升增强型高电子迁移率晶体管的动态导通电阻(dynamic on-resistance)的特性。

62.根据本发明的一些实施例,第五氮化物半导体层161的第二厚度d2以及第二p型掺杂的浓度用以提高第三氮化物半导体层151下方(即,高电子迁移率晶体管的栅极堆叠结构180的下方)的载流子沟道130a的导通阈值电压,使得栅极堆叠结构180下方的载流子沟道130a在不施加电压的情况下能够达到完全空乏(fully depletion),进而完全截止载流子沟道130a。根据本发明的一些实施例,第四氮化物半导体层152的第一厚度d1以及第一p型掺杂的浓度用以调整第四氮化物半导体层152下方(即,高电子迁移率晶体管的第二漏极电极173的下方)的载流子沟道130a的导通阈值电压,使得第四氮化物半导体层152下方的载流子沟道130a只能够达到部分空乏(partial depletion),以增进半导体结构100所形成的增强型高电子迁移率晶体管的器件特性。

63.图2a至图2d为根据本发明的一实施例所述示的半导体结构的制造方法的剖面示意图。参照图2a,提供基板110。接着,可在基板110上方形成缓冲层120,以缓解基板110与缓冲层120之上的膜层之间的晶格差异,提升外延品质。在一些实施例中,缓冲层120的材料可包含iii-v族化合物半导体材料,例如iii族氮化物。举例来说,缓冲层120的材料可包含氮化镓(gan)、氮化铝(aln)、氮化铝镓(algan)、氮化铝铟(alinn)、类似的材料或前述的组合,但本发明实施例并非以此为限。在一些实施例中,缓冲层120可通过沉积工艺所形成,例如化学气相沉积(cvd)、原子层沉积(ald)、分子束外延(mbe)、液相外延(lpe)、类似的工艺或前述的组合,但本发明实施例并非以此为限。在一些实施例中,缓冲层120可包含掺杂的碳或铁。

64.如图2a所示,可在缓冲层120上方形成第一氮化物半导体层130。在一些实施例中,第一氮化物半导体层130的材料可包含一或多种iii-v族化合物半导体材料,例如iii族氮化物。在一些实施例中,第一氮化物半导体层130的材料可包括氮化镓(gan)。第一氮化物半导体层130可由沉积工艺所形成,例如金属有机化学气相沉积(mocvd)、氢化物气相外延法(hvpe)、分子束外延法(mbe)、其他适合的方法或前述的组合所形成。举例来说,第一氮化物半导体层130可使用含镓的前驱物以及含氮的前驱物,藉由金属有机化学气相沉积(mocvd)

外延长成。含镓的前驱物可包括三甲基镓(trimethylgallium,tmg)、三乙基镓(triethylgallium,teg)、或其他合适的化学品;含氮的前驱物包括氨(ammonia,nh3)、叔丁胺(tertiarybutylamine,tbam)、苯肼(phenyl hydrazine)或其他合适的化学品。然而,本发明实施例并非以此为限。

65.如图2a所示,可在第一氮化物半导体层130上方形成第二氮化物半导体层140。在一些实施例中,第二氮化物半导体层140的材料可包含一或多种iii-v族化合物半导体,例如,iii族氮化物。在一些实施例中,第二氮化物半导体层140的材料可包括氮化铝镓(algan)。在一些实施例中,第二氮化物半导体层140可具有掺杂物,例如n型掺质或p型掺质。第二氮化物半导体层140可由沉积工艺所形成,例如金属有机化学气相沉积(mocvd)、氢化物气相外延法(hvpe)、分子束外延法(mbe)、其他适合的方法或前述的组合所形成。举例来说,第二氮化物半导体层140可使用含铝的前驱物、含镓的前驱物以及含氮的前驱物,藉由有机金属气相外延法(mocvd)外延长成。含铝的前驱物包含三甲基铝(trimethylaluminum,tma)、三乙基铝(triethylaluminum,tea)、或其他合适的化学品;含镓的前驱物包含三甲基镓(tmg)、三乙基镓(teg)或其他合适的化学品;含氮的前驱物包含氨(nh 3)、叔丁胺(tbam)、苯肼(phenyl hydrazine)或其他合适的化学品。然而,本发明实施例并非以此为限。

66.根据本发明的一些实施例,第一氮化物半导体层130包括gan层,第二氮化物半导体层140包括alxga1-xn层,其中0《x《=1。此外,第二氮化物半导体层140的带隙高于第一氮化物半导体层130的带隙。

67.在一些实施例中,如图2a所示,可在第二氮化物半导体层140上方形成第一顶部氮化物半导体层150。在一些实施例中,第一顶部氮化物半导体层150的材料包括以p型掺杂的alyga1-yn,且0≤y≤1。换句话说,第一顶部氮化物半导体层150可包括p型氮化镓层(当y=0),也可包括p型aln(当y=1),更可包括p型alyga1-yn(当0《y《1)。

68.第一顶部氮化物半导体层150可例如通过外延成长工艺在第二氮化物半导体层140上沉积掺杂的化合物半导体材料所形成,但本发明实施例并非以此为限。根据发明的一些实施例,p型掺杂包括镁(mg)、铍(be)、钙(ca)、锌(zn)等可形成p型氮化物材料。根据本发明的一实施例,第一顶部氮化物半导体层150具有第一厚度d1以及第一p型掺杂。

69.在一些实施例中,如图2a所示,可在第一顶部氮化物半导体层150上方形成第二顶部氮化物半导体层160。在一些实施例中,第二顶部氮化物半导体层160的材料包括以p型掺杂的alzga1-zn,其中0≤z≤1。换句话说,第二顶部氮化物半导体层160可包括p型氮化镓层(当z=0),也可包括p型aln(当z=1),更可包括p型alzga1-zn(当0《z《1)。第二顶部氮化物半导体层160可例如通过外延成长工艺在第一顶部氮化物半导体层150上沉积化合物半导体材料所形成,但本发明实施例并非以此为限。

70.根据本发明的一实施例,第二顶部氮化物半导体层160具有第二厚度d2,其中第二厚度d2不小于第一厚度d1,且第二p型掺杂的浓度不小于第一p型掺杂的浓度。也即,第二顶部氮化物半导体层160的第二厚度d2大于或等于第一顶部氮化物半导体层150的第一厚度d1,第二顶部氮化物半导体层160的p型掺杂浓度高于或等于第一顶部氮化物半导体层150的p型掺杂浓度。

71.根据本发明的其他实施例,除了依序将缓冲层120、第一氮化物半导体层130、第二

氮化物半导体层140、第一顶部氮化物半导体层150以及第二顶部氮化物半导体层160形成于基板110上方之外,也可提供具有所述半导体层之外延片(epitaxial wafer),以利缩短工艺步骤。

72.接着,如图2b所示,在第二顶部氮化物半导体层160的上方形成栅极电极174,并且以栅极电极174作为刻蚀光掩膜,且以第一顶部氮化物半导体层150作为刻蚀停止层,藉以图形化第二顶部氮化物半导体层160而在栅极电极174的下方形成第五氮化物半导体层161。此外,第一顶部氮化物半导体层150因此而暴露在外。

73.根据本发明的一些实施例,栅极电极174的材料可包括导电材料,例如金属、金属硅化物、其他合适的材料或前述材料的组合。金属可包括金(au)、镍(ni)、铂(pt)、钯(pd)、铱(ir)、钛(ti)、铬(cr)、钨(w)、铝(al)、铜(cu)、前述的组合、前述的合金或前述的多层。然而,本发明实施例并非以此为限。根据本发明的一些实施例,栅极电极174与第二顶部氮化物半导体层160形成欧姆接触。根据本发明的一些实施例,栅极电极174与第二顶部氮化物半导体层160形成萧特基接触。

74.接着,如图2c所示,对第一顶部氮化物半导体层150进行图形化,并以第二氮化物半导体层140作为刻蚀停止层,而在栅极电极174以及第五氮化物半导体层161的下方形成第三氮化物半导体层151,并形成第四氮化物半导体层152。

75.随后,如图2d所示,在第三氮化物半导体层151以及第四氮化物半导体层152的相异两侧,形成漏极电极171以及源极电极172,其中漏极电极171以及源极电极172与第二氮化物半导体层140直接接触,漏极电极171与第二漏极电极173相邻且相互电连接。根据本发明的一实施例,漏极电极171以及源极电极172与第二氮化物半导体层140形成欧姆接触。

76.如图2d所示,通过第一氮化物半导体层130与第二氮化物半导体层140之间不同能带隙所引发的自发性极化及压电极化效应,于第一氮化物半导体层130与第二氮化物半导体层140之间的异质界面上形成载流子沟道130a。此外,在不施加任何电压的情况下,载流子沟道130a于第三氮化物半导体层151的下方截止。

77.根据本发明的一些实施例,半导体结构100形成增强型高电子迁移率晶体管,第三氮化物半导体层151、第五氮化物半导体层161以及栅极电极174形成增强型高电子迁移率晶体管的栅极堆叠结构180,第四氮化物半导体层152、漏极电极171以及第二漏极电极173形成增强型高电子迁移率晶体管的漏极端,源极电极172形成增强型高电子迁移率晶体管的源极端。根据本发明的一些实施例,第四氮化物半导体层152以及第二漏极电极173用以提升增强型高电子迁移率晶体管的动态导通电阻(dynamic on-resistance)的特性。

78.本发明在此提出用以形成增强型高电子迁移率晶体管的半导体结构,通过调整第一顶部氮化物半导体层以及第二顶部氮化物半导体层的厚度以及p型掺杂的浓度,能够有效的控制形成载流子沟道的导通阈值电压且同时增进动态导通电阻的特性。

79.此外,相对于先前技术中产生凹室所需的刻蚀精准度以及在凹室的底部外延具有p型杂质的氮化镓层所需的特殊外延技术,本发明提出的半导体结构的制造方法使用的是一般的外延工艺以及一般的刻蚀工艺,将有效的降低生产成本以及生产时间。相对于先前技术中利用氟离子轰击的高电子迁移率晶体管所产生的增强型器件反转为耗尽型器件的问题,由于本发明的半导体结构及其制造方法并未使用氟离子,因此可轻易排除上述问题。

80.虽然本揭露的实施例及其优点已揭露如上,但应该了解的是,任何所属技术领域

技术人员,在不脱离本揭露的精神和范围内,当可作更动、替代与润饰。此外,本揭露的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,任何所属技术领域技术人员可从本揭露一些实施例的揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本揭露一些实施例使用。因此,本揭露的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求构成个别的实施例,且本揭露的保护范围也包括各个权利要求及实施例的组合。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。