1.本实用新型涉及多fpga芯片控制系统技术领域,更具体地说,涉及一种新型数据处理电路板。

背景技术:

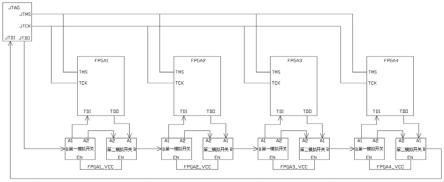

2.在现有的多个fpga芯片串连系统中,如图1所示,用jtag接口芯片实时监控读取fpga芯片温度等信息时,需要把串连的fpga芯片全部上电打开,由jtdo引脚将数据输出到fpga的tdi引脚,在由fpga的tdo输出到下一个fpga,最后串连的fpga在将数据传回jtag接口芯片的jtdi引脚,打开的fpga的待机功耗为2w,如果只使用单个或某几个fpga时,其它没有使用的fpga待机功耗将造成电能量的浪费。

技术实现要素:

3.本实用新型要解决的技术问题在于,针对现有技术的上述缺陷,提供一种新型数据处理电路板。

4.本实用新型解决其技术问题所采用的技术方案是:一种新型数据处理电路板,包括jtag接口芯片和多组控制电路;所述控制电路包括fpga芯片、第一模拟开关和第二模拟开关;多个所述fpga芯片与所述jtag接口芯片依次并联;所述第一模拟开关上设有与所述fpga芯片的tdi引脚电连接的第一档位、第二档位和接收数据信号的输入端;所述第二模拟开关上设有与所述fpga芯片的tdo引脚电连接的第三档位、与所述第二档位电连接的第四档位,和输出所述数据信号的输出端;所述控制电路还包括切换模块;所述切换模块根据所述fpga芯片的通断电状态切换所述第一模拟开关的输出档位;相邻两个所述控制电路通过所述输出端将所述数据信号传送给所述输入端而连接;所述jtag接口芯片的jtdo引脚与第一组所述控制电路的所述输入端电连接;所述jtag接口芯片的jtdi引脚与最后一组所述控制电路的所述输出端电连接;

5.本实用新型所述的新型数据处理电路板,其中,所述切换模块包括所述第一模拟开关上的第一en引脚、所述第二模拟开关上的第二en引脚;所述第一en引脚与所述第二en引脚均与所述fpga芯片的vcc引脚电连接;

6.本实用新型所述的新型数据处理电路板,其中,所述fpga芯片通电时,所述fpga芯片对应的所述切换模块中的所述第一en引脚与所述第二en引脚均为高电平,且所述切换模块将所述第一模拟开关的输出档位切换为所述第一档位,所述第一模拟开关上的第一档位与所述fpga芯片的tdi引脚连通,所述第二模拟开关上的第三档位与所述fpga芯片的tdo引脚连通;

7.本实用新型所述的新型数据处理电路板,其中,所述fpga芯片断电时,所述fpga芯片对应的所述切换模块中的所述第一en引脚与所述第二en引脚均为低电平,且所述切换模块将所述第一模拟开关的输出档位切换为所述第二档位;所述第一模拟开关上的所述第二档位与所述第二模拟开关上的所述第四档位连通;

8.本实用新型所述的新型数据处理电路板,其中,所述jtag接口芯片的jtms引脚通过导线与多个所述fpga芯片的tms引脚依次并联;所述jtag接口芯片的jtck引脚通过另一导线与多个所述fpga芯片的tck引脚依次并联。

9.本实用新型的有益效果在于:该新型数据处理电路板包括jtag接口芯片和多组控制电路,其中,控制电路包括fpga芯片、第一模拟开关和第二模拟开关;多个fpga芯片与jtag接口芯片依次并联,jtag接口芯片上的jtdo引脚与第一组控制电路的输入端电连接,fpga芯片的tdi引脚与第一模拟开关的第一档位电连接,fpga芯片的tdo引脚与第一模拟开关的第三档位电连接;第一模拟开关的第二档位与第四档位电连接;第二模拟开关的输出端与下一控制电路的输入端电连接,控制电路还包括切换模块;切换模块根据fpga芯片的通断电状态切换第一模拟开关的输出档位;相邻两个控制电路通过输出端将数据信号传送给输入端而连接;jtag接口芯片的jtdo引脚与第一组控制电路的输入端电连接;jtag接口芯片的jtdi引脚与最后一组控制电路的输出端电连接;当fpga芯片通电时,与其对应的切换模块将第一模拟开关上的输出档位切换为第一档位,从而使fpga芯片与jtag接口芯片成功连接,fpga芯片正常工作;当fpga芯片断电时,与其对应的切换模块将第一模拟开关上的输出档位切换为第二档位,从而使jtag接口芯片不与fpga芯片连通,电路仍可正常工作;该新型数据处理电路板把不需要使用的fpga芯片断电,而不影响电路正常工作,从而达到节能省电。

附图说明

10.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将结合附图及实施例对本实用新型作进一步说明,下面描述中的附图仅仅是本发明的部分实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图:

11.图1是现有技术中的数据处理电路板的电路原理图;

12.图2是本实用新型较佳实施例的新型数据处理电路板的电路原理图;

13.图3是本实用新型较佳实施例的fpga1芯片的电路图;

14.图4是本实用新型较佳实施例的fpga2芯片的电路图;

15.图5是本实用新型较佳实施例的fpga3芯片的电路图;

16.图6是本实用新型较佳实施例的fpga4芯片的电路图;

17.图7是本实用新型较佳实施例的jtag接口芯片的电路图;

18.图8是本实用新型较佳实施例中与fpga1芯片电连接的第一模拟开关及第二模拟开关的电路原理图;

19.图9是本实用新型较佳实施例中与fpga2芯片电连接的第一模拟开关及第二模拟开关的电路原理图;

20.图10是本实用新型较佳实施例中与fpga3芯片电连接的第一模拟开关及第二模拟开关的电路原理图;

21.图11是本实用新型较佳实施例中与fpga4芯片电连接的第一模拟开关及第二模拟开关的电路原理图。

具体实施方式

22.为了使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本实用新型的部分实施例,而不是全部实施例。基于本发明的实施例,本领域普通技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型的保护范围。

23.本实用新型较佳实施例的一种新型数据处理电路板,如图2-11所示,包括jtag接口芯片和多组控制电路;其中,控制电路包括fpga芯片、第一模拟开关和第二模拟开关;多个fpga芯片与jtag接口芯片依次并联;值得说明的是,jtag接口芯片的型号可以为act8990或sn54act8990,fpga芯片的型号为x6cvl365t,第一模拟开关与第二模拟开关的型号为bl1551,该jtag接口芯片、fpga芯片、第一模拟开关与第二模拟开关也可以采用现有技术中其他的芯片型号,在此不再赘述;第一模拟开关上设有与fpga芯片的tdi引脚电连接的第一档位、第二档位和接收数据信号的输入端;该第一模拟开关的第一档位、第二档位和输入端分别为第一模拟开关上的a1引脚、a2引脚和b引脚;第二模拟开关上设有与fpga芯片的tdo引脚电连接的第三档位、与第二档位电连接的第四档位,和输出数据信号的输出端;该第二模拟开关的第三档位、第四档位和输出端分别为第二模拟开关上的a1引脚、a2引脚和b引脚;控制电路还包括切换模块;切换模块根据fpga芯片的通断电状态切换第一模拟开关的输出档位;相邻两个控制电路通过输出端将数据信号传送给输入端而连接;jtag接口芯片的jtdo引脚与第一组控制电路的输入端电连接;jtag接口芯片的jtdi引脚与最后一组控制电路的输出端电连接。

24.该新型数据处理电路板包括jtag接口芯片和多组控制电路,其中,控制电路包括fpga芯片、第一模拟开关和第二模拟开关;多个fpga芯片与jtag接口芯片依次并联,jtag接口芯片上的jtdo引脚与第一组控制电路的输入端电连接,fpga芯片的tdi引脚与第一模拟开关的第一档位电连接,fpga芯片的tdo引脚与第一模拟开关的第三档位电连接;第一模拟开关的第二档位与第四档位电连接;第二模拟开关的输出端与下一控制电路的输入端电连接,控制电路还包括切换模块;切换模块根据fpga芯片的通断电状态切换第一模拟开关的输出档位;相邻两个控制电路通过输出端将数据信号传送给输入端而连接;jtag接口芯片的jtdo引脚与第一组控制电路的输入端电连接;jtag接口芯片的jtdi引脚与最后一组控制电路的输出端电连接;当fpga芯片通电时,与其对应的切换模块将第一模拟开关上的输出档位切换为第一档位a1引脚,从而使fpga芯片与jtag接口芯片成功连接,fpga芯片正常工作;当fpga芯片断电时,与其对应的切换模块将第一模拟开关上的输出档位切换为第二档位a2引脚,从而使jtag接口芯片不与fpga芯片连通,电路仍可正常工作;该新型数据处理电路板把不需要使用的fpga芯片断电,而不影响电路正常工作,从而达到节能省电。

25.如图2所示,4组fpga芯片分别为fpga1芯片、fpga2芯片、fpga3芯片和fpga4芯片;jtag接口芯片的jtms引脚通过导线分别与fpga1芯片、fpga2芯片、fpga3芯片和fpga4芯片的tms引脚依次并联;jtag接口芯片的jtck引脚通过另一导线分别与fpga1芯片、fpga2芯片、fpga3芯片和fpga4芯片的tck引脚依次并联;当不使用任一或多个fpga芯片时,其他正在使用的fpga芯片不会受到影响,仍可正常接收时钟信号;

26.优选的,切换模块包括第一模拟开关上的第一en引脚、第二模拟开关上的第二en引脚;第一en引脚与第二en引脚均与fpga芯片的vcc引脚电连接;

27.优选的,如图8所示,fpga芯片通电时,fpga芯片对应的切换模块中的第一en引脚与第二en引脚均为高电平,且切换模块将第一模拟开关的输出档位切换为第一档位,第一模拟开关上的第一档位与fpga芯片的tdi引脚连通,第二模拟开关上的第三档位与fpga芯片的tdo引脚连通;从而使fpga芯片与jtag接口芯片成功连接,fpga芯片正常工作;jtag接口芯片输出的数据信号接入fpga芯片的tdi引脚进入fpga芯片中,fpga芯片将数据信号处理后由fpga芯片的tdo引脚输出数据经过第二模拟开关的a1引脚传送至第二模拟开关,数据信号在通过第二模拟开关的b引脚输出到下一组控制电路的第一模拟开关的b引脚上,若下一组控制电路中的fpga芯片也为通电状态,则对下一组控制电路重复上述动作。

28.优选的,fpga芯片断电时,fpga芯片对应的切换模块中的第一en引脚与第二en引脚均为低电平,且切换模块将第一模拟开关的输出档位切换为第二档位即a1引脚;第一模拟开关上的第二档位a2引脚与第二模拟开关上的第四档位a2引脚连通;jtag接口芯片的jtdo引脚输出数据信号直接传到下一组控制电路中,不影响整个电路的正常工作,耗电低,若下一组控制电路中的fpga芯片也为断电状态,则对下一组控制电路重复上述动作,若下一组控制电路中的fpga芯片为通电状态,则重复fpga芯片为通电时的动作。

29.应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本实用新型所附权利要求的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。