一种基于fpga和emac/gmac控制器的多cpu通信系统与方法

技术领域

1.本发明涉及cpu间通信技术领域,特别是一种基于fpga和emac/gmac控制器的多cpu通信系统与方法。

背景技术:

2.自cpu芯片诞生以来,发展及其迅速,其应用已经涉及消费电子、航空航天、工业控制、电力系统等各个领域。虽然单个cpu的功能已日益强大,但仍有许多场合需要多个cpu协同工作来实现特定功能,尤其对于实时性要求较高的场合,多cpu之间稳定高效的通信就显得尤为重要。

3.目前比较广泛的多cpu间的通信方式,是串行方式中的串口通信和并行方式中的双口ram通信,这两种方法一般都会占用cpu较多的时间资源,传输速度较慢,实时性较差,影响cpu的效率。

4.emac/gmac控制器,一般集成在cpu的内部,作为cpu对外通信的百兆或千兆的网络接口,控制器数据的接收与发送多采用dma模式与cpu的内存进行交互,无需cpu干预。在现实应用中控制器多与百兆/千兆phy芯片连接,来实现对外网络通信,但是多cpu之间的串口通信、双口ram通信会占用cpu资源,导致传输速度慢以及实时性差的问题。

技术实现要素:

5.本发明的目的是提供一种基于fpga和emac/gmac控制器的多cpu通信系统与方法,旨在解决现有技术中多cpu之间的串口通信、双口ram通信会占用cpu资源,导致传输速度慢以及实时性差的问题,实现提高多cpu间通信效率。

6.为达到上述技术目的,本发明提供了一种基于fpga和emac/gmac控制器的多cpu通信系统,所述系统包括:

7.一个作为主设备的fpga以及多个作为从设备的集成emac/gmac接口的cpu芯片;

8.所述fpga中包括emac/gmac接口收发控制模块、数据缓存区读写模块以及缓存区数据交互模块;

9.所述emac/gmac接口收发控制模块用于控制数据收发的时序,构建与emac/gmac控制器通信的接口时序控制,接收emac/gmac控制器发送的数据存入fpga中接收缓冲区以及发送fpga中发送缓冲区的数据;

10.所述数据缓存区读写模块包含接两个接收缓冲区和两个发送缓冲区,不同类型的两个缓冲区可分别同时进行emac/gmac读写操作以及缓存区数据交互;

11.所述缓存区数据交互模块用于定时接收除本emac/gmac接口之外的其他emac/gmac接口的缓冲区数据,并存储在本接口的发送缓冲区内供emac/gmac接口收发控制模块进行数据发送。

12.优选地,所述fpga与cpu的emac/gmac接口有以下通信信号:

13.txd[3:0]为数据发送总线,方向为cpu-》fpga;

[0014]

tx_en为发送使能引脚;

[0015]

tx_clk为数据发送的时钟信号,方向为cpu-》fpga;

[0016]

rxd[3:0]为数据接收总线,方向为fpga-》cpu;

[0017]

rx_dv为数据接收有效信号,方向为fpga-》cpu;

[0018]

rx_clk为数据接收的时钟信号,方向为fpga-》cpu;

[0019]

gclk_ref为emac/gmac模块的参考时钟,方向为fpga-》cpu。

[0020]

优选地,所述emac/gmac控制器与cpu内存采用dma通信方式。

[0021]

优选地,所述cpu的扩展数量取决于所选fpga的io引脚数量、开辟数据缓存区所需ram资源以及实现模块功能所需的逻辑资源。

[0022]

本发明还提供了一种利用所述系统实现的基于fpga和emac/gmac控制器的多cpu通信方法,所述方法包括以下操作:

[0023]

fpga内的待发送数据的cpu所对应的emac/gmac接口收发控制模块实时接收对应cpu内emac/gmac控制器所发送的数据,并将数据存储在各自的接收缓存区内,并将缓存区的数据有效标志置起;

[0024]

当fpga内的缓存区数据交互模块监测到有效标志置起时,待接收数据的cpu对应的缓存区数据交互模块依次轮询其他cpu对应的接收缓存区的数据有效标志,将含有有效标志的接收缓存区进行汇总;

[0025]

将汇总后的数据放置在待接收cpu对应的发送缓冲区,并将发送缓冲区的有效标志置起;

[0026]

当emac/gmac接口收发控制模块监测到发送缓冲区有效标志置起后,将发送缓冲区数据发送至对应的待接收cpu中,完成本次通信。

[0027]

优选地,所述方法包括以下通信的实现:

[0028]

cpu2、cpu3到cpun的数据发送到cpu1;cpu1、cpu3到cpun的数据发送到cpu2;cpu1、cpu2、cpu4到cpun的数据发送到cpu3;...,cpu1、cpu2到cpun-1的数据发送到cpun。

[0029]

发明内容中提供的效果仅仅是实施例的效果,而不是发明所有的全部效果,上述技术方案中的一个技术方案具有如下优点或有益效果:

[0030]

与现有技术相比,本发明所述方案速度快、实时性高,由于速度主要受限于所选fpga的最高工作频率和集成在cpu内emac/gmac控制器的工作最高频率,使用gmac速度可达1000mb/s,使用emac可达100mb/s,若未来cpu内集成万兆mac控制器,且fpga最高工作频率也可达到相应要求,理论上此种方式的通信速率可达万兆;本发明基本不消耗cpu的资源,cpu集成的emac/gmac控制器与内存通信大都采用dma方式,基本无需cpu的干预,提高了cpu的运行效率;可同时实现任意两个或多个cpu之间的通信,可扩展性强,其扩展的数量主要取决于所选用fpga的io引脚数量、开辟数据缓存区所需的ram资源以及实现模块功能所需的其他资源;本发明为全双工通信,数据的接收和发送可同时进行,大大加快了cpu间的通信效率,且应用范围广,市场上大多数的cpu芯片集成emac/gmac控制器。

附图说明

[0031]

图1为本发明实施例中所提供的一种基于fpga和emac/gmac控制器的多cpu通信系统结构示意图;

[0032]

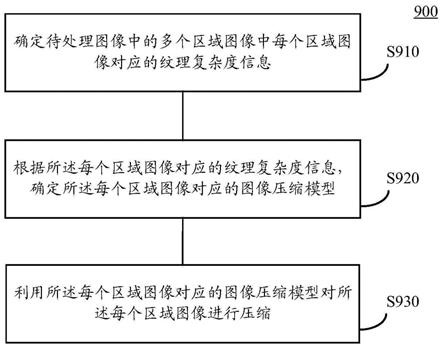

图2为本发明实施例中所提供的一种基于fpga和emac/gmac控制器的多cpu通信流程图。

具体实施方式

[0033]

为了能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

[0034]

下面结合附图对本发明实施例所提供的一种基于fpga和emac/gmac控制器的多cpu通信系统与方法进行详细说明。

[0035]

如图1所示,本发明实施例公开了一种基于fpga和emac/gmac控制器的多cpu通信系统,所述系统包括:

[0036]

一个作为主设备的fpga以及多个作为从设备的集成emac/gmac接口的至少两个cpu芯片;

[0037]

所述fpga中包括emac/gmac接口收发控制模块、数据缓存区读写模块以及缓存区数据交互模块;

[0038]

所述emac/gmac接口收发控制模块用于控制数据收发的时序,构建与emac/gmac控制器通信的接口时序控制,接收emac/gmac控制器发送的数据存入fpga中接收缓冲区以及发送fpga中发送缓冲区的数据;

[0039]

所述数据缓存区读写模块包含接两个接收缓冲区和两个发送缓冲区,不同类型的两个缓冲区可分别同时进行emac/gmac读写操作以及缓存区数据交互;

[0040]

所述缓存区数据交互模块用于定时接收除本emac/gmac接口之外的其他emac/gmac接口的缓冲区数据,并存储在本接口的发送缓冲区内供emac/gmac接口收发控制模块进行数据发送。

[0041]

本发明实施例通过使用fpga构建多个emac/gmac通信接口,来实现fpga与多个cpu之间的通信,使用fpga作为数据交换的中转功能,并依靠fpga并行、快速的处理特性,中转过程用时短,基本等同于任意两个cpu或多cpu之间的直接通信。

[0042]

将fpga作为主设备,将集成emac/gmac接口的至少2个cpu芯片,在fpga中分别设置每个cpu对应的emac/gmac接口收发控制模块、数据缓存区读写模块以及缓存区数据交互模块。

[0043]

所述emac/gmac接口收发控制模块实现cpu与fpga之间的通信,采用全双工模式,收发可同时进行。通过控制数据收发的时序部分,并构建与emac/gmac控制器通信的接口时序控制,接收和发送分别置于独立模块中,触发条件相互独立,互不干涉。在接收时,实时准备接收cpu的emac/gmac控制器发送来的数据,并将接收的数据放入接收缓存区内,接收完成后,置数据接收完成标志;在发送时,则在发送缓存区的有效标志有效前提下,将fpga发送数据缓存区内的数据发送出去。

[0044]

所述数据缓存区读写模块包含至少4个数据缓存区,其中两个是接收数据缓存区,

用于存储通过emac/gmac接口接收的对应的cpu内存数据,另外两个是发送数据缓存区,用于存储通过emac/gmac接口发送给cpu的有效数据。设置接收和发送缓存区的目的是为了提高通信效率,在一个缓存区处于emac/gmac读写控制使用时,另一个缓存区可同时用于缓存区数据交互,两个缓存区交替使用,从而达到高效率的全双工通信。在本发明实施例中,对于数据缓存区读写还可设置定时器,产生轮询emac/gmac接收缓存区是否有效的读写标志,定时器的时间设置可根据通信的每帧数据包的大小、通信的速率以及通信的cpu个数进行设置,合理设置最优的定时时间。

[0045]

所述缓存区数据交互模块可定时的将除本emac/gmac接口之外的其他emac/gmac接口接收数据缓冲区的数据进行汇总和处理,并按照规定好的帧格式存储在本接口的发送数据缓冲区中,完成后将该发送缓冲区数据有效标志置起,供emac/gmac接口收发控制进行发送操作。

[0046]

在emac/gmac接口中,txd[3:0]为数据发送总线,方向为cpu-》fpga,fpga会在发送时钟的双沿采样;tx_en为发送使能引脚,fpga在tx_clk的上升沿和下降沿,判断该信号电平,若电平为高则fpga将发送总线数据进行采样锁存;tx_clk为数据发送的时钟信号,方向为cpu-》fpga,一般最大为125mhz,与gclk_ref频率相同,可调整,作为发送数据的脉搏;rxd[3:0]为数据接收总线,方向为fpga-》cpu,cpu的emac/gmac控制器会在接收时钟的双沿采样;rx_dv为数据接收有效信号,方向为fpga-》cpu,一般cpu内部集成的emac/gmac控制器会在rx_clk上升沿和下降沿,判断此信号电平,若为高电平则emac/gmac控制器会将接收总线数据进行采样锁存;rx_clk为数据接收的时钟信号,方向为fpga-》cpu,一般最大设置为125mhz,可调整,作为接收数据的脉搏;gclk_ref为emac/gmac模块的参考时钟,方向为fpga-》cpu,此时钟频率决定了emac/gmac控制器的tx_clk和内部模块的工作频率。

[0047]

本发明所述方案速度快、实时性高,由于速度主要受限于所选fpga的最高工作频率和集成在cpu内emac/gmac控制器的工作最高频率,使用gmac速度可达1000mb/s,使用emac可达100mb/s,若未来cpu内集成万兆mac控制器,且fpga最高工作频率也可达到相应要求,理论上此种方式的通信速率可达万兆;本发明基本不消耗cpu的资源,cpu集成的emac/gmac控制器与内存通信大都采用dma方式,基本无需cpu的干预,提高了cpu的运行效率;可同时实现任意两个或多个cpu之间的通信,可扩展性强,其扩展的数量主要取决于所选用fpga的io引脚数量、开辟数据缓存区所需的ram资源以及实现模块功能所需的其他资源;本发明为全双工通信,数据的接收和发送可同时进行,大大加快了cpu间的通信效率,且应用范围广,市场上大多数的cpu芯片集成emac/gmac控制器。

[0048]

如图2所示,本发明实施例还公开了一种利用所述系统实现的基于fpga和emac/gmac控制器的多cpu通信方法,所述方法包括以下操作:

[0049]

fpga内的待发送数据的cpu所对应的emac/gmac接口收发控制模块实时接收对应cpu内emac/gmac控制器所发送的数据,并将数据存储在各自的接收缓存区内,并将缓存区的数据有效标志置起;

[0050]

当fpga内的缓存区数据交互模块监测到有效标志置起时,待接收数据的cpu对应的缓存区数据交互模块依次轮询其他cpu对应的接收缓存区的数据有效标志,将含有有效标志的接收缓存区进行汇总;

[0051]

将汇总后的数据放置在待接收cpu对应的发送缓冲区,并将发送缓冲区的有效标

志置起;

[0052]

当emac/gmac接口收发控制模块监测到发送缓冲区有效标志置起后,将发送缓冲区数据发送至对应的待接收cpu中,完成本次通信。

[0053]

以图1中将cpu2至cpun的数据发送至cpu1为例,在fpga中为需要通信的cpu1至cpun分别设置各自的emac/gmac接口收发控制模块、数据缓存区读写模块以及缓存区数据交互模块,其中数据缓存区读写模块包含至少两个数据发送缓冲区和两个数据接收缓存区。

[0054]

fpga内的cpu2至cpun对应的的emac/gmac接口收发控制模块分别实时接收各自对应的cpu内emac/gmac控制器所发送来的数据,并将接收的数据存储在各自的接收缓冲区内,接收数据完成后,将缓存区的数据有效标志置起。cpu之间可异步,并非所有cpu的emac/gmac控制器都同时发送数据。

[0055]

当缓存区数据交互模块监测到读写标志为1时,则cpu1对应的缓存区数据交互模块依次轮询cpu2至cpun对应的各接收缓冲区的数据有效标志,并将含有效标志的接收缓存区数据进行汇总和处理,若缓存区无有效标志被置起,则无需进行任何处理,等待下一个定时标志到来再进行轮询。

[0056]

将上述汇总和处理后的数据存储在cpu1对应的发送缓冲区内,存储完成后,将发送缓冲区的有效标志置起。

[0057]

当emac/gmac接口收发控制模块监测到发送缓冲区的有效标志后进行数据的发送操作,将fpga中的数据发送至cpu1中,本次通信完成。

[0058]

同理可完成以下操作:

[0059]

cpu1、cpu3到cpun的数据发送到cpu2;cpu1、cpu2、cpu4到cpun的数据发送到cpu3;...,cpu1、cpu2到cpun-1的数据发送到cpun。

[0060]

上述通信为收发双向并行,且相互独立,按照此方式完成任意两个和任意多个的cpu之间的通信。

[0061]

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。