tcam及其位单元、写操作方法

技术领域

1.本技术涉及半导体器件及集成电路领域,尤其涉及一种tcam及其位单元、写操作方法。

背景技术:

2.三态内容寻址存储器(tcam,ternary content addressable memory)是在传统的存储技术基础上实现的联想记忆存储器,拥有三种存储状态:“0”,“1”和“don’t care”,使其既能进行精确匹配查找,又能进行模糊匹配查找。

3.tcam的基本操作有三种:写操作、读操作和查找操作,其中写操作和读操作的方式与随机存取存储器(ram,random access memory)相同,查找操作是tcam的最主要用途,能够从巨大的数据库中进行快速查找,并且返回最佳的匹配地址,最快查找速度能够达到每秒一亿次以上。

4.tcam的位单元(bitcell)通常包含两个基本存储单元,因此需要两个写周期来完成对一个存储单元的信息输入,耗时较长。

技术实现要素:

5.本技术要解决的技术问题是提供一种tcam及其位单元、写操作方法,能够大幅度缩短写入时间。

6.为解决上述技术问题,本技术提供了一种tcam位单元,包括:信息存储单元,用于存储信息,包括第一存储单元和第二存储单元;多位写入单元,与所述第一存储单元和第二存储单元连接,所述多位写入单元被配置为同时对所述第一存储单元和第二存储单元进行写操作。

7.在本技术实施例中,所述第一存储单元连接第一字线,所述第二存储单元连接第二字线,所述多位写入单元连接第三字线。

8.在本技术实施例中,向所述第一存储单元和所述第二存储单元同时写入不同数据时,打开所述第一字线或所述第二字线,并打开所述第三字线;向所述第一存储单元和所述第二存储单元同时写入相同数据时,打开所述第一字线和所述第二字线,关闭所述第三字线。

9.在本技术实施例中,所述多位写入单元包括:第五mos管,所述第五mos管的源端连接所述第一存储单元,所述第五mos管的漏端连接所述第二存储单元;第六mos管,与所述第五mos管通过栅端连接,且所述第六mos管的源端连接所述第二存储单元,所述第六mos管的漏端连接所述第一存储单元。

10.在本技术实施例中,所述第五mos管和第六mos管的栅端连接至所述第三字线。

11.在本技术实施例中,所述第一存储单元和所述第二存储单元均分别连接第一位线和第二位线,其中所述第一存储单元包括依次连接的第一mos管、第一反相单元及第二mos管,所述第二存储单元包括依次连接的第三mos管、第二反相单元及第四mos管。

12.在本技术实施例中,所述第一mos管的漏端连接所述第一位线,所述第一mos管的源端连接所述第一反相单元,所述第一mos管的栅端连接所述第一字线;所述第二mos管的漏端连接所述第一反相单元,所述第二mos管的源端连接所述第二位线,所述第二mos管的栅端连接所述第一字线。

13.在本技术实施例中,所述第三mos管的漏端连接所述第一位线,所述第三mos管的源端连接所述第二反相单元,所述第三mos管的栅端连接所述第二字线;所述第四mos管的漏端连接所述第二反相单元,所述第四mos管的源端连接所述第二位线,所述第四mos管的栅端连接所述第二字线。

14.在本技术实施例中,所述第五mos管的源端连接所述第一反相单元的输出端,所述第五mos管的漏端连接所述第二反相单元的输入端;所述第六mos管的源端连接所述第二反相单元的输出端,所述第六mos管的漏端连接所述第一反相单元的输入端。

15.在本技术实施例中,所述第一反相单元包括首尾相连的第一反相器和第二反相器;所述第二反相单元包括首尾相连的第三反相器和第四反相器。

16.在本技术实施例中,所述第一存储单元为数据存储单元,所述第二存储单元为掩码存储单元。

17.在本技术实施例中,所述的tcam位单元还包括:匹配比较单元,与所述信息存储单元连接,用于比较输入信息与存储信息,并输出比较结果。

18.在本技术实施例中,所述匹配比较单元包括依次连接的第七mos管、第八mos管、第九mos管以及第十mos管,其中:所述第七mos管的栅端连接所述第一反相单元,所述第七mos管的源端连接比较结果输出线;所述第八mos管的源端连接所述第七mos管的漏端,所述第八mos管的栅端用于接收所述输入信息;所述第九mos管的漏端连接所述第八mos管的漏端,所述第九mos管的栅端用于接收所述输入信息;所述第十mos管的漏端连接所述第九mos管的源端,所述第十mos管的源端连接所述比较结果输出线,所述第十mos管的栅端连接所述第二反相单元。

19.本技术还提供一种写操作方法,采用上述的tcam位单元,所述写操作方法包括:利用多位写入单元同时将数据写入第一存储单元和第二存储单元内。

20.在本技术实施例中,写入状态为0时,在所述第一存储单元内写入0,在所述第二存储单元内写入1;写入状态为1时,在所述第一存储单元内写入1,在所述第二存储单元内写入0;写入状态为x时,在所述第一存储单元内写入0,在所述第二存储单元内写入0;写入状态为无效状态时,在所述第一存储单元内写入1,在所述第二存储单元内写入1。

21.本技术还提供一种tcam,包括:上述的tcam位单元。

22.本技术技术方案通过在tcam bitcell的逻辑电路结构中设计多位写入单元,所述多位写入单元与各存储单元连接,并通过外围电路的逻辑控制,能够同时对各存储单元进行写操作,进而实现tcam bitcell的一次性写入,大幅度提高了写入速率。

附图说明

23.以下附图详细描述了本技术中披露的示例性实施例。其中相同的附图标记在附图的若干视图中表示类似的结构。本领域的一般技术人员将理解这些实施例是非限制性的、示例性的实施例,附图仅用于说明和描述的目的,并不旨在限制本技术的范围,其他方式的

实施例也可能同样的完成本技术中的发明意图。应当理解,附图未按比例绘制。其中:

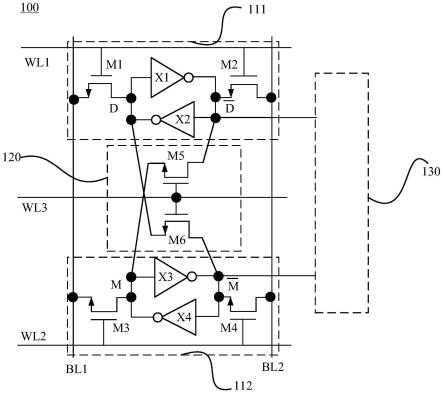

24.图1为一种tcam bitcell的逻辑电路示意图;

25.图2为本技术实施例的tcam bitcell的逻辑电路示意图;

26.图3为本技术实施例的tcam bitcell在写入状态0时的电流方向示意图;

27.图4为本技术实施例的tcam bitcell在写入状态1时的电流方向示意图;

28.图5为本技术实施例的tcam bitcell在写入状态x时的电流方向示意图;

29.图6为本技术实施例的tcam bitcell中匹配比较单元的结构示意图。

具体实施方式

30.以下描述提供了本技术的特定应用场景和要求,目的是使本领域技术人员能够制造和使用本技术中的内容。对于本领域技术人员来说,对所公开的实施例的各种局部修改是显而易见的,并且在不脱离本技术的精神和范围的情况下,可以将这里定义的一般原理应用于其他实施例和应用。因此,本技术不限于所示的实施例,而是与权利要求一致的最宽范围。

31.参考图1,一种tcam bitcell,包括第一存储单元10、第二存储单元11以及匹配比较单元13。进行写操作时,在所述第一存储单元10中写入数据d,在所述第二存储单元11中写入数据m。《d,m》组成一个数据,当《d,m》为《0,1》时,代表存储状态为“0”;当《d,m》为《1,0》时,代表存储状态为“1”;当《d,m》为《0,0》时,代表存储状态为“x”;当《d,m》为《1,1》时,代表存储状态为无意义。

32.写入数据《d,m》时,需要分别对所述第一存储单元10和所述第二存储单元11进行一次写操作,因此需要两个写周期来完成对一个tcambitcell的信息输入。

33.为了缩短写时间,本技术技术方案通过对tcam bitcell的电路结构进行改进,增加了多位写入单元,所述多位写入单元被配置为同时对信息存储单元中的各存储单元进行写操作,因此可以大幅度提高写入速率。

34.以下结合附图和具体的实施例对本技术技术方案的tcam bitcell进行详细说明。

35.参考图2,本技术实施例的tcam bitcell 100,包括:信息存储单元、多位写入单元120及匹配比较单元130。其中所述信息存储单元用于存储信息,包括第一存储单元111和第二存储单元112,所述第一存储单元111可以是数据存储单元,所述数据存储单元例如可以是静态随机存取存储器单元(sram cell),写操作时在所述第一存储单元111写入数据d。所述第二存储单元112可以是掩码存储单元,所述掩码存储单元例如可以是sram cell,写操作时在所述第二存储单元112写入数据m。所述第一存储单元111和所述第二存储单元112存储的数据构成一个两位的状态《d,m》,《0,1》为状态0,《1,0》为状态1,《0,0》为状态x,《1,1》为无效状态。

36.所述第一存储单元111连接第一字线wl1、第一位线bl1及第二位线bl2。具体地,所述第一存储单元111包括依次连接的第一mos管m1、第一反相单元及第二mos管m2,其中所述第一mos管m1的漏端连接所述第一位线bl,所述第一mos管m1的源端连接所述第一反相单元,所述第一mos管m1的栅端连接所述第一字线wl1;所述第二mos管m2的漏端连接所述第一反相单元,所述第二mos管m2的源端连接所述第二位线bl2,所述第二mos管m2的栅端连接所述第一字线wl1。

37.所述第一反相单元包括首尾相连的第一反相器x1和第二反相器x2。所述第一反相器x1和第二反相器x2可以是任何结构的反相器,只要能实现反相的效果即可。

38.所述第二存储单元112连接所述第一字线wl1、第一位线bl1及第二位线bl2。具体地,所述第二存储单元112包括依次连接的第三mos管m3、第二反相单元及第四mos管m4,其中所述第三mos管m3的漏端连接所述第一位线bl1,所述第三mos管m3的源端连接所述第二反相单元,所述第三mos管m3的栅端连接所述第二字线wl2;所述第四mos管m4的漏端连接所述第二反相单元,所述第四mos管m4的源端连接所述第二位线bl2,所述第四mos管m4的栅端连接所述第二字线wl2。

39.所述第二反相单元包括首尾相连的第三反相器x3和第四反相器x4。对所述第三反相器x3和第四反相器x4的结构不作特殊限定,只要能实现反相的效果即可。

40.所述多位写入单元120包括第五mos管m5、第六mos管m6,其中所述第五mos管m5的源端连接所述第一存储单元111,所述第五mos管m5的漏端连接所述第二存储单元112。在本技术实施例中,所述第五mos管m5的源端连接所述第一存储单元111的第一反相单元,具体地,所述第五mos管m5的源端可以连接所述第一反相器x1的输出端以及所述第二反相器x2的输入端。所述第五mos管m5的漏端连接所述第二存储单元112的第二反相单元,例如,所述第五mos管m5的漏端连接所述第三反相器x3的输入端以及所述第四反相器x4的输出端。所述第六mos管m6的源端连接所述第二存储单元112的第二反相单元,例如所述第六mos管m6的源端连接所述第三反相器x3的输出端以及所述第四反相器x4的输入端。所述第六mos管m6的漏端连接所述第一存储单元111的第一反相单元,例如所述第六mos管m6的漏端连接所述第一反相器x1的输入端和所述第二反相器x2的输出端。所述第五mos管和第六mos管的栅端相互连接,并连接至所述第三字线wl3。

41.通过控制所述第一字线wl1、第二字线wl2及第三字线wl3的开关状态,并从第一位线或第二位线输入正确的数据,实现在一个写周期内对所有存储单元进行写操作,进而实现不同状态的写入。具体地,向所述第一存储单元111和所述第二存储单元112同时写入不同数据时,打开所述第一字线wl1或所述第二字线wl2,并打开所述第三字线wl3;向所述第一存储单元111和所述第二存储单元112同时写入相同数据时,打开所述第一字线wl1和所述第二字线wl2,关闭所述第三字线wl3。

42.在本技术实施例中,在一个写周期内同时完成对第一存储单元111和所述第二存储单元112进行写操作,可以通过如下方法实现:写入状态0时,也即《d,m》为《0,1》,同时打开所述第一字线wl1和第三字线wl3,所述第二字线wl2关闭,所述第一位线bl1置低,所述第二位线bl2置高(电流方向如图3中的箭头方向)写入状态1时,也即《d,m》为《1,0》,所述第一字线wl1和第三字线wl3同时打开,所述第二字线wl2关闭,所述第一位线bl1置高,所述第二位线bl2置低(电流方向如图4中的箭头方向);写入状态x时,也即《d,m》为《0,0》,所述第一字线wl1和所述第二字线wl2同时打开,所述第三字线wl3关闭,所述第一位线bl1置低,所述第二位线bl2置高(电流方向如图5中的箭头方向);写入无效状态时,所述第一字线wl1和所述第二字线wl2同时打开,所述第三字线wl3关闭,所述第一位线bl1置高,所述第二位线bl2置低。

43.在其他实施例中,也可以通过如下方法来实现在一个写周期内同时完成对第一存储单元111和所述第二存储单元112进行写操作:写入状态0时,所述第二字线wl2和第三字

线wl3同时打开,所述第一字线wl1关闭,所述第一位线bl1置高,所述第二位线bl2置低;写入状态1时,所述第二字线wl2和第三字线wl3同时打开,所述第一字线wl1关闭,所述第一位线bl1置低,所述第二位线bl2置高;写入状态x时,所述第一字线wl1和第二字线wl2同时打开,所述第三字线wl3关闭,所述第一位线bl1置低,所述第二位线bl2置高;写入无效状态时,所述第一字线wl1和所述第二字线wl2同时打开,所述第三字线wl3关闭,所述第一位线bl1置高,所述第二位线bl2置低。

44.由此可见,本技术实施例在tcam bitcell中增加多位写入单元,并且配合外围电路的逻辑控制,能够实现tcam bitcell的一次性写入,减少一半的写入时间。

45.参考图6,所述匹配比较单元130用于比较输入信息与存储信息,并输出比较结果,可以包括依次连接的第七mos管m7、第八mos管m8、第九mos管m9以及第十mos管m10,其中:所述第七mos管m7的栅端连接所述第一反相单元,具体地,所述第七mos管m7的栅端连接所述第一反相器x1的输出端和所述第二反相器的输入端,所述第七mos管m7的源端连接比较结果输出线hl;所述第八mos管m8的源端连接所述第七mos管m7的漏端,所述第八mos管m8的栅端用于接收所述输入信息;所述第九mos管m9的漏端连接所述第八mos管m8的漏端,所述第九mos管m9的栅端用于接收所述输入信息,其中所述输入信息包括相反的第一输入信息key和第二输入信息keyb,且第一输入信息key和第二输入信息keyb分别被所述第八mos管m8的栅端和所述第九mos管m9的栅端接收;所述第十mos管m10的漏端连接所述第九mos管m9的源端,所述第十mos管m10的源端连接所述比较结果输出线hl,所述第十mos管m10的栅端连接所述第二反相单元,具体地,所述第十mos管m10的栅端连接所述第三反相器x3的输出端和所述第四反相器x4的输入端。

46.本技术实施例还提供一种写操作方法,采用上述的tcam位单元,所述写操作方法包括:利用多位写入单元同时将数据写入第一存储单元和第二存储单元内。在一些实施例中,写入状态为0时,在所述第一存储单元内写入0,在所述第二存储单元内写入1;写入状态为1时,在所述第一存储单元内写入1,在所述第二存储单元内写入0;写入状态为x时,在所述第一存储单元内写入0,在所述第二存储单元内写入0;写入状态为无效状态时,在所述第一存储单元内写入1,在所述第二存储单元内写入1。

47.本技术实施例还提供一种tcam,包括上述的tcam位单元。

48.综上所述,在阅读本技术内容之后,本领域技术人员可以明白,前述申请内容可以仅以示例的方式呈现,并且可以不是限制性的。尽管这里没有明确说明,本领域技术人员可以理解本技术意图囊括对实施例的各种合理改变,改进和修改。这些改变,改进和修改都在本技术的示例性实施例的精神和范围内。

49.应当理解,本实施例使用的术语

″

和/或

″

包括相关联的列出项目中的一个或多个的任意或全部组合。应当理解,当一个元件被称作

″

连接

″

或

″

耦接

″

至另一个元件时,其可以直接地连接或耦接至另一个元件,或者也可以存在中间元件。

50.类似地,应当理解,当诸如层、区域或衬底之类的元件被称作在另一个元件

″

上

″

时,其可以直接在另一个元件上,或者也可以存在中间元件。与之相反,术语

″

直接地

″

表示没有中间元件。还应当理解,术语

″

包含

″

、

″

包含着

″

、

″

包括

″

或者

″

包括着

″

,在本技术文件中使用时,指明存在所记载的特征、整体、步骤、操作、元件和/或组件,但并不排除存在或附加一个或多个其他特征、整体、步骤、操作、元件、组件和/或它们的组。

51.还应当理解,尽管术语第一、第二、第三等可以在此用于描述各种元件,但是这些元件不应当被这些术语所限制。这些术语仅用于将一个元件与另一个元件区分开。因此,在没有脱离本技术的教导的情况下,在一些实施例中的第一元件在其他实施例中可以被称为第二元件。相同的参考标号或相同的参考标记符在整个说明书中表示相同的元件。

52.此外,本技术说明书通过参考理想化的示例性截面图和/或平面图和/或立体图来描述示例性实施例。因此,由于例如制造技术和/或容差导致的与图示的形状的不同是可预见的。因此,不应当将示例性实施例解释为限于在此所示出的区域的形状,而是应当包括由例如制造所导致的形状中的偏差。例如,被示出为矩形的蚀刻区域通常会具有圆形的或弯曲的特征。因此,在图中示出的区域实质上是示意性的,其形状不是为了示出器件的区域的实际形状也不是为了限制示例性实施例的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。