1.本发明是关于一种封装结构及其制造方法,特别关于一种具有电磁干扰屏蔽功能的半导体封装结构及其制造方法。

背景技术:

2.电磁干扰(electromagnetic interference, emi)可能以电流的形式沿载流导体(例如电源线和电缆)传播,或以电磁波的形式通过空间传播。因此,根据电磁干扰的耦合通路的不同,电磁干扰可以分为传导电磁干扰和辐射电磁干扰两种。通过载流导体传播的电磁干扰称为传导型电磁干扰,通过空间传播的电磁干扰称为辐射型电磁干扰。

3.一般而言,对于辐射型电磁干扰通常是采取空间上屏蔽或隔离的方式作为改善对策,其大致分为利用金属盖或打线(wire bonding)包覆的方式来屏蔽电磁干扰,其将分述如下。

4.请参照图1所示,现有的一种封装结构10包括一电路板11、一芯片12、一封装层13。芯片12是电性连接于电路板11的一表面上,且封装层13是包覆芯片12。电路板11可以是为多层电路板,其具有多个层叠的电路层111,并包覆在一介电层112中。其中,层叠的电路层111是通过导电通孔或导电盲孔形成电性连接,并且,电路层111的其中一个是设计为一接地层(grounding layer)111a。

5.为了避免芯片12受到辐射型电磁干扰的影响,第一种电磁干扰屏蔽手段是采用一金属外盖14罩设于封装结构10的外侧,以隔绝外来的电磁干扰。其中金属外盖14具有一顶盖141及一侧壁142,顶盖141是覆盖于芯片12上,而侧壁142是电性连接于封装结构10侧缘的接地层111a,以使金属外盖14接地,并据此达到电磁干扰屏蔽的目的。

6.请参照图2所示,现有的一种电子装置20是包括一电路板21、多个芯片22以及多个被动组件23。芯片22以及被动组件23是焊接于电路板21的表面上。

7.为了避免芯片22受到辐射型电磁干扰的影响,第二种电磁干扰屏蔽手段是采用打线包覆芯片22,以隔绝外来的电磁干扰。打线包覆是利用铜线(cu wire)24包覆芯片22,其中铜线24的两端是电性连接于电路板21的接地焊垫(ground pad),而接地焊垫是与电路板21的接地层导通的外露电性连接垫,以形成局部或全区的电磁干扰屏蔽。

8.上述第一种电磁干扰屏蔽手段必须先形成单颗的封装结构10后,再对其逐一组装金属外盖14,因此制程手续相当繁琐;而上述第二种电磁干扰屏蔽手段必须针对需要电磁干扰屏蔽的芯片进行局部打线或是全区打线,可想而知其所需的制程步骤将更加繁复。

9.因应于现有技术存在的上述技术问题,提供一种封装结构及其电磁干扰屏蔽组件及具有电磁干扰屏蔽功能的封装结构制造方法,使封装结构具有电磁干扰屏蔽效果,同时能够简化制程手续,实属当前重要课题。

技术实现要素:

10.有鉴于上述,本发明的一目的是提供一种半导体电磁干扰屏蔽组件、半导体封装

结构及其制造方法,其具有制造工艺简便的优点。

11.为达上述目的,本发明提供一种半导体封装结构,其包括一封装载板、至少一电子组件、一封装层、一支撑组件以及一屏蔽层。封装载板具有相对的第一表面与第二表面,且包括一增层线路及一包覆该增层线路的一第一介电层。电子组件是设置于封装载板的第一表面,并与增层线路电性连接。封装层是设置于封装载板的第一表面,且包覆电子组件。支撑组件是嵌埋于封装层内并且至少框围住电子组件。其中支撑组件的一侧端面是暴露于封装层的一表面,而支撑组件的另一侧端面与封装载板的增层线路电性连接并且电性接地。屏蔽层是设置于封装层与支撑组件上,且包括一图案化金属层及一包覆图案化金属层的第二介电层。图案化金属层与支撑组件电性连接,且图案化金属层的遮蔽范围至少涵盖电子组件及支撑组件。支撑组件与该屏蔽层共同框围形成一包覆电子组件的屏蔽空间。

12.在一实施例中,其中图案化金属层设置有多个贯穿图案化金属层的穿孔。

13.在一实施例中,其中图案化金属层的上表面是暴露于第二介电层的上表面。

14.在一实施例中,支撑组件包括有呈栅栏式排列的多个导电柱、或呈围墙状的连续侧壁、或多个导电柱与连续侧壁的组合。

15.在一实施例中,半导体封装结构还包括多个导电黏合胶,借以将支撑组件结合于封装载板的第一表面,且与该增层线路电性连接为电性接地,其中这些导电黏合胶之间具有空隙。

16.另外,为达上述目的,本发明提供一种半导体电磁干扰屏蔽组件,其可结合在一封装载板上。半导体电磁干扰屏蔽组件包括一第二介电层、一图案化金属层以及一支撑组件。图案化金属层是嵌设于该第二介电层内。支撑组件是由导电金属所构成,且支撑组件的其中一侧端面是嵌入该第二介电层并且电性连接结合于该图案化金属层,而支撑组件的另一侧端面是暴露且凸出于该第二介电层。图案化金属层与支撑组件共同框围形成一屏蔽空间。

17.本发明的半导体电磁干扰屏蔽组件更进一步的改进在于,该图案化金属层设置有多个贯穿该图案化金属层的穿孔。该图案化金属层的一侧表面暴露出于该第二介电层的一表面。该支撑组件包括呈栅栏式排列的多个导电柱,或呈围墙状的连续侧壁,或多个导电柱与连续侧壁的组合。

18.又,为达上述目的,本发明提供一种半导体封装结构的制造方法,其包括下列步骤:步骤一是提供一封装载板,其具有相对的第一表面与第二表面,且包括一增层线路,以及一包覆增层线路的一第一介电层。步骤二是在封装载板的一第一表面上设置至少一电子组件,且电子组件与增层线路电性连接。步骤三是提供一如上所述的半导体电磁干扰屏蔽组件,且使其结合于封装载板的第一表面,并且至少罩盖住电子组件,其中半导体电磁干扰屏蔽组件与封装载板的增层线路电性连接且电性接地。步骤四是形成一封装层于封装载板的第一表面上与半导体电磁干扰屏蔽组件间的腔体,并包覆电子组件与半导体电磁干扰屏蔽组件的支撑组件。

19.在一实施例中,其中将半导体电磁干扰屏蔽组件结合于封装载板的第一表面的步骤前,还包括于封装载板的第一表面形成多个非连续的导电黏合胶,且这些导电黏合胶与该增层线路电性连接并电性接地,供半导体电磁干扰屏蔽组件以支撑组件的一侧端面来黏接结合于封装载板,且这些导电黏合胶间具有空隙,以作为填充封装材料的填充通道。

20.再者,为达上述目的,本发明提供另一种半导体封装结构的制造方法,其包括下列步骤:步骤一是提供一封装载板,其具有相对的一第一表面与一第二表面,且包括有一增层线路,以及一包覆增层线路的第一介电层。步骤二是于封装载板的第一表面上设置至少一电子组件,且电性连接增层线路。步骤三是形成一支撑组件及一封装层于封装载板的第一表面,其中支撑组件电性连接增层线路以接地并框围住电子组件,而封装层包覆电子组件及支撑组件。步骤四是于封装层上以曝光显影方法电镀形成一图案化金属层,且图案化金属层与支撑组件电性连接,其中图案化金属层的遮蔽范围至少涵盖电子组件及支撑组件。步骤五是形成一第二介电层于封装层及图案化金属层上,以包覆图案化金属层。

21.在一实施例中,形成支撑组件及封装层的方法还至少包括下列两个步骤。首先,是以一感光型介电材形成封装层于封装载板的第一表面上,以包覆电子组件。接着,于封装层以图案化曝光显影形成多个开口,且于开口内电镀形成支撑组件以框围住电子组件,其中支撑组件与增层线路电性连接并且接地。

22.于另一实施例中,在一实施例中,形成支撑组件及封装层的方法还至少包括下列两个步骤。首先,于封装载板的第一表面上以图案化曝光显影电镀形成支撑组件,以框围住电子组件,其中支撑组件与增层线路电性连接并且接地。接着,形成一封装层于封装载板的第一表面上,以包覆电子组件及支撑组件,并且露出支撑组件的一端面。

23.在一实施例中,其中形成图案化金属层的步骤前,还包括于封装层上对应于支撑组件露出的一侧端面上,以曝光显影方法电镀形成与支撑组件相连接的一导电金属;以及形成一第一子介电层于封装层上,以包覆导电金属,并且露出导电金属的一侧端面。

24.在一实施例中,其中形成图案化金属层的步骤前,还包括形成一第一子介电层于封装层上,并且于第一子介电层形成多个开孔以对应露出支撑组件的一侧端面;以及于多个开孔内电镀形成与支撑组件相连接的导电金属,且导电金属的一侧端面露出于第一子介电层的一表面。

25.在一实施例中,图案化金属层的上表面是露出于第二介电层的上表面。

26.承上所述,本发明公开的一种封装结构及其半导体电磁干扰屏蔽组件及封装结构的制造方法是利用半导体制程来制作电磁干扰屏蔽组件,其可以与封装结构的制程整合,于封装时同步形成电磁干扰屏蔽结构,而可以简化具有电磁干扰屏蔽功能的封装结构的制程。

附图说明

27.图1显示一种现有电磁干扰屏蔽方法的结构示意图;图2显示另一种现有电磁干扰屏蔽方法的结构示意图;图3显示依据本发明较佳实施例的一种封装结构的剖面示意图;图4a显示依据本发明较佳实施例的封装结构的半导体电磁干扰屏蔽组件的俯视示意图;图4b显示依据本发明较佳实施例的封装结构的半导体电磁干扰屏蔽组件的侧视示意图;图5a至5d显示依据本发明较佳实施例的封装结构,其中不同实施样态的半导体电磁干扰屏蔽组件的支撑组件的仰视示意图;

图6a至6c显示本发明较佳实施例的第一种封装结构的制造方法流程示意图;图7a至7f显示本发明较佳实施例的第二种封装结构的制造方法流程示意图。

28.附图标记说明11,21:电路板111:电路层111a:接地层112:介电层12,22:芯片13:封装层14:金属外盖141:顶盖142:侧壁20:电子装置23:被动组件24:铜线10,30:半导体封装结构31:封装载板311:第一表面312:第二表面313:增层线路3131,3133,3135:图案化导电层3132,3134:导电柱层314:第一介电层321,322,323:电子组件33:封装层331:第三表面332:第四表面34:支撑组件341:第一侧端面342:第二侧端面343a:导电柱343b:连续侧壁35:屏蔽层351:图案化金属层3511:第一子导电金属3512:第二子导电金属352:第二介电层3521:第五表面3522:第六表面

3523:第一子介电层3524:第二子介电层36:焊球am1:半导体电磁干扰屏蔽组件o1:第一开孔o2:第一子开孔o3:第二子开孔z01:围设区域z11:第一围设区域z12:第二围设区域。

具体实施方式

29.为了使所属技术领域中具有通常知识者能了解本发明的内容,并可据以实现本发明的内容,兹配合适当实施例及附图说明如下。

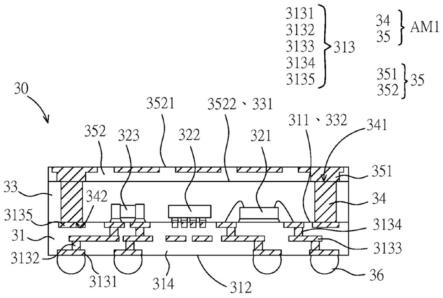

30.图3是依据本发明较佳实施例的一种封装结构的剖面示意图。半导体封装结构30包括一封装载板31、三个电子组件321~323、一封装层33、一支撑组件34、一屏蔽层35以及多个焊球36。

31.封装载板31具有相对的一第一表面311与一第二表面312,并具有一增层线路313与一第一介电层314。其中,增层线路313嵌埋于第一介电层314中,并且包括堆栈设置的图案化导电层3131、3133、3135以及导电柱层3132、3134,其材质例如为铜,借以形成导电路径。在本实施例中,部分的图案化导电层3131、3135是可作为电性连接垫(或称焊垫)。例如,部分的图案化导电层3131与焊球36电性连接。

32.电子组件321~323可通过焊球(conductive bump)或导电黏合胶等具有导电黏合的组件而分别设置于封装载板31的第一表面311上,并且与增层线路313电性连接。在本实施例中,电子组件321例如是打线封装式的芯片、电子组件322例如是覆晶封装式的芯片、而电子组件323例如是电容器。换言之,电子组件可以是主动组件(active component)或被动组件(passive component),其并未限定。

33.封装层33具有相对的一第三表面331与一第四表面332。封装层33是包覆封装载板31的第一表面311与电子组件321~323。在本实施例中,封装层33的第四表面332与封装载板31的第一表面311是为共平面。

34.支撑组件34是由导电金属所构成,并且具有相对的一第一侧端面341以及一第二侧端面342。支撑组件34嵌埋于封装层33内并且框围这些电子组件321~323。支撑组件34的第一侧端面341暴露于封装层33的第三表面331,而第二侧端面342与封装载板的增层线路313电性连接并且电性接地。

35.屏蔽层35设置于封装层33的第三表面331以及支撑组件34上,并且屏蔽层35包括一图案化金属层351以及一第二介电层352。第二介电层352包覆图案化金属层351,并具有相对的一第五表面3521及一第六表面3522,其中,第六表面3522与封装层33的第三表面331为共平面。部分的图案化金属层351分别暴露于第二介电层352的第五表面3521及第六表面3522,其中,暴露于第六表面3522的部分的图案化金属层351与支撑组件34的第一侧端面

341电性连接。

36.另外,值得一提的是,上述的支撑组件34与屏蔽层35可组成一半导体电磁干扰屏蔽组件am1,并且支撑组件34与屏蔽层35共同框围形成一包覆电子组件321~323的屏蔽空间。请同时参照图3及图4a所示,其中图4a是半导体电磁干扰屏蔽组件am1的俯视示意图。由图3及图4a可知,图案化金属层351的遮蔽范围至少涵盖电子组件321~323以及支撑组件34。再由图4a可知,部分的图案化金属层351的一侧表面暴露于第二介电层352的第五表面3521,由俯视图观察,半导体电磁干扰屏蔽组件am1可利用类似网状的结构来达到电磁干扰屏蔽效果。在其他实施例中,半导体电磁干扰屏蔽组件am1亦可利用完整的金属面或利用其他图案化金属层来达到电磁干扰屏蔽效果,于此并未加以限制。

37.请再同时参照图3及图4b所示,其中图4b是半导体电磁干扰屏蔽组件am1的侧视示意图。由图4b可知,在本实施例中,支撑组件34具有多个导电柱343a,其是呈栅栏式排列,并且各导电柱343a可以通过导电黏合胶或焊球而连接于封装载板31上(图中未示出)。

38.另外,半导体电磁干扰屏蔽组件am1的支撑组件34可以具有多种的变化样态以扩展其应用范围,以下是以图5a至5d图的仰视示意图简单说明半导体电磁干扰屏蔽组件am1的支撑组件34的变化样态。

39.如图5a所示,支撑组件34具有多个导电柱343a,其是间隔排列,并且构成一围设区域z01。前述的电子组件321~323位于围设区域z01中,而被导电柱343a框围。如图5b所示,通过支撑组件34的导电柱343a还可分别构成一第一围设区域z11及一第二围设区域z12,其可形成范围不一的围设区域,以针对局部的电子组件做电磁干扰屏蔽,例如前述的电子组件321、322位于一第一围设区域z11的范围内,而电子组件323位于第二围设区域z12的范围内。上述的围设区域的叙述仅为举例性,其围设区域的形状大小是可依据实际需求所设计。

40.另外,如图5c所示,支撑组件34除上述具有导电柱的样态之外,还可呈围墙状的连续侧壁343b的样态,或是如图5d所示,是由连续侧壁343b以及导电柱343a组合的样态。支撑组件34的实现亦可由图5a~图5d的样态依据实际需求而搭配使用,于此并未限定。

41.针对上述具有电磁干扰屏蔽功能的封装结构,以下将列举两个实施例,以说明具有电磁干扰屏蔽功能的封装结构的制造方法。

42.请参照图6a至6c所示,本发明的第一种半导体封装结构的制造方法,其包括步骤s01~s05。

43.如图6a所示,步骤s01是提供一封装载板31,其具有相对的一第一表面311与一第二表面312,并且包括一增层线路313,以及一包覆增层线路313的第一介电层314。

44.步骤s02是于封装载板31的第一表面311上设置三个电子组件321~323。其中,电子组件321~323可通过打线制程、覆晶制程、回焊制程或导电黏合胶黏合等制程而设置于封装载板31上,并与增层线路313电性连接。

45.如图6b所示,步骤s03是将一半导体电磁干扰屏蔽组件am1结合于封装载板31的第一表面311,并罩盖电子组件321~323。其中,半导体电磁干扰屏蔽组件am1与封装载板31的增层线路313电性连接且电性接地。在本实施例中,半导体电磁干扰屏蔽组件am1具有一支撑组件34以及一屏蔽层35。支撑组件34可包括多个呈栅栏式排列的导电柱343a,其可通过导电黏合胶而设置或固定于封装载板31的第一表面311,并与增层线路313电性连接。屏蔽层35包括一图案化金属层351以及一第二介电层352,并且部分的图案化金属层351与导电

柱343a电性连接。

46.如图6c所示,步骤s04是形成一封装层33于封装载板31的第一表面311与半导体电磁干扰屏蔽组件am1间的腔体,并包覆电子组件321~323与支撑组件34。在本实施例中,由于半导体电磁干扰屏蔽组件am1的支撑组件34包括多个呈栅栏式排列的导电柱343a,因此封装层33能在流体的状态下覆盖封装载板31,并且填充于半导体电磁干扰屏蔽组件am1、封装载板31以及电子组件321~323间,再予以固化。

47.步骤s05是形成焊球36于封装载板31的第二表面312。另外,在本实施例中,上述步骤所形成的封装结构可由大版面制程来完成,而在进行切单制程后,即可形成单一个具有电磁干扰屏蔽功能的封装结构。

48.于此要特别说明的是,当半导体电磁干扰屏蔽组件am1的支撑组件34是连续侧壁形式时,可通过间隔设置导电黏合胶于侧壁的底端部与封装载板31的第一表面间,则封装层33亦能在流体的状态下通过间隔的导电黏合胶而填充至半导体电磁干扰屏蔽组件am1、封装载板31以及电子组件321~323间。

49.请再参照图7a至图7f所示,本发明的第二种半导体封装结构的制造方法,其包括步骤s11~s22。

50.与前述实施例的图6a相同,步骤s11是提供封装载板31。步骤s12是于封装载板31的一表面上设置三个电子组件321~323。

51.如图7a所示,步骤s13是以一感光型介电材形成封装层33于封装载板31的第一表面311上,并且包覆电子组件321、322、323。步骤s14是以图案化曝光显影方式于封装层33形成多个第一开孔o1,以暴露出部分的封装载板31的第一表面311及/或增层线路313。在本实施例中,这些第一开口o1是呈栅栏式排列以框围电子组件321、322、323,并且暴露部分的增层线路313。

52.如图7b所示,步骤s15是分别于各第一开孔o1中电镀形成一导电柱343a,以使这些导电柱343a构成前述的支撑组件34。

53.于此,值得一提的是,在其他实施例中上述的步骤s13、步骤s14及步骤s15是可以替换如下。首先,是于封装载板31的第一表面311上以图案化曝光显影电镀形成导电柱343a(支撑组件34),以框围住电子组件321、322、323。接着,形成一封装层33于封装载板31的第一表面311上,以包覆电子组件321、322、323及支撑组件34,并且露出支撑组件34的一端面。其中,支撑组件34与增层线路313电性连接并且接地。须注意,在这个例示中,封装层33的材质则无选用感光型介电材的必要性,而有更多的封装材料可供选择。

54.回到本实施例,如图7c所示,步骤s16是形成一第一子介电层3523于封装层33及导电柱343a上,以覆盖封装层33。步骤s17是于第一子介电层3523形成多个第一子开孔o2以暴露出各导电柱343a的上端面。

55.如图7d所示,步骤s18是形成一第一子导电金属3511于这些第一子开孔o2中,并且电性连接这些导电柱343a。

56.如图7e所示,步骤s19是形成一第二子介电层3524于第一子介电层3523及第一子导电金属3511上,以包覆第一子介电层3523。其中,第一子介电层3523与第二子介电层3524是共同组成第二介电层352。步骤s20是形成多个第二子开孔o3以暴露出部分的第一子导电金属3511及部分的第一子介电层3523。

57.如图7f所示,步骤s21是形成一第二子导电金属3512于这些第二子开孔o3,以使第一子导电金属3511及第二子导电金属3512构成图案化金属层351。最后,步骤s22是形成焊球36于封装载板31的第二表面312。

58.与前述实施例的第一种制造方法相似的是,上述步骤s11~s22所形成的半导体封装结构可由大版面制程来完成,而在进行切单制程后,即可形成单一个具有电磁干扰屏蔽功能的半导体封装结构。

59.综上所述,本发明公开的一种半导体电磁干扰屏蔽组件、半导体封装结构及其制造方法是利用半导体制程来制作电磁干扰屏蔽组件,其可以与封装结构的制程整合同步,而可以简化具有电磁干扰屏蔽功能的封装结构的制程。相较于现有技术,本发明至少具有下列优点:01.本发明可以在封装载板尚未进行切单制程前即可与半导体电磁干扰屏蔽组件组合,并在组合后再进行切单制程。

60.02.本发明对于仅需局部电磁干扰屏蔽的封装结构具有可作业性高且生产周期短的优点。

61.03.本发明的电磁干扰屏蔽组件以半导体制程完成,而能够与同为半导体制程的封装结构利用相似的制程技术同步完成,而可简化制程。

62.惟,以上所述仅为本发明的较佳实施例,自不能以此限制本发明的专利范围。举凡本本领域技术人员依本发明精神所作的等效修饰或变化,皆应包括于权利要求的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。