sio2/sin/al2o

3 with tan metal gate for multi-giga bit flash memories)”,2003年ieee国际电子器件会议(iedm),2003年,第26.5.1-26.5.4页,doi:10.1109/iedm.2003.1269356。

11.[2]h.t.lue、s.y.wang、e.k.lai、y.h.shih、s.c.lai、l.w.yang、k.c.chen、j.ku、k.y.hsieh、r.liu和c.y.lu,“be-sonos:具有优异性能和可靠性的带隙设计sonos(be-sonos:a bandgap engineered sonos with excellent performance and reliability)”,2005年ieee国际电子器件会议(iedm),2005年,第547-550页,doi:10.1109/iedm.2005.1609404。

[0012]

[3]m.ishiduki、y.fukuzumi、r.katsumata、m.kito、m.kido、h.tanaka、y.komori、y.nagata、t.fujiwara、t.maeda、y.mikajiri、s.oota、m.honda、y.iwata、r.kirisawa、h.aochi和a.nitayama,“用于具有优异性能和可靠性的超高密度存储器件的管状bics闪存的优化器件结构(optimal device structure for pipe-shaped bics flash memory for ultra high density storage device with excellent performance and reliability)”,2009年ieee国际电子器件会议(iedm),2009年,第27.3.1-27.3.4页,doi:10.1109/iedm.2009.5424261。

[0013]

[4]s.tsuda、y.kawashima、k.sonoda、a.yoshitomi、t.mihara、s.narumi、m.inoue、s.muranaka、t.maruyama、t.yamashita、y.yamaguchi和d.hisamoto,“用于16/14纳米节点及更高节点的高速和高可靠性嵌入式闪存的finfet分栅monos的首次演示(first demonstration of finfet split-gate monos for high-speed and highly-reliable embedded flash in16/14nm-node and beyond)”,2016年ieee国际电子器件会议(iedm),2016年,第11.1.1-11.1.4页,doi:10.1109/iedm.2016.7838393。

[0014]

[5]p.wang、x.lin、l.liu、q.sun、p.zhou、x.liu、w.liu、y.gong、d.w.zhang,“用于低电压超快存储器和传感操作的半浮动栅晶体管(a semi-floating gate transistor for low-voltage ultrafast memory and sensing operation)”,《science》(科学),第334卷,第6146期,第640-643页,2013年8月,doi:10.1126/science.1240961。

[0015]

[6]z.zheng、l.zhang、w.song、s.feng、h.xu、j.sun、s.yang、t.chen、j.wei和k.j.chen,“基于氮化镓的互补逻辑集成电路(gallium nitride-based complementary logic integrated circuits)”,nat.electron.,2021年7月,doi:10.1038/s41928-021-00611-y。

[0016]

[7]z.zheng、w.song、l.zhang、s.yang、j.wei、k.j.chen,“在p-gan栅极功率hemt平台上的高ion和ion/ioff比增强型掩埋p-沟道gan mosfet(high ion and ion/ioff ratio enhancement-mode buried p-channel gan mosfets on p-gan gate power hemt platform)”,ieee electron device lett.(ieee电子器件快报),第41卷,第1期,2020年1月,第26-29页,doi:10.1109/led.2019.2954035。

技术实现要素:

[0017]

本公开提出了一种仅有一个单个绝缘层的宽带隙(wbg)半导体双极电荷俘获(bct)非易失性存储器。尤其是,所提出的wbg半导体bct非易失性存储器结构利用了包括但不限于氮化镓(gan)的具有宽带隙的半导体材料,以增强数据保持能力和双极电荷俘获过

程,从而在增强耐久性的同时提高了数据p/e的速度。优选地,所提出的wbg半导体bct非易失性存储器结构是基于gan基异质结或平面gan异质结基高电子迁移率晶体管(hemt)而制造的。所提出的wbg半导体bct非易失性存储器结构在半导体内在无to情况下的空穴和电子注入以及俘获提供了足够的势垒高度。在所提出的结构的p/e阶段仅需要外部偏置电压来减小在宽带隙半导体结中的势垒以用于电子注入和空穴扩散,并且,在所提出的结构中,由于外部偏压补偿了内建电势,因此随着电场的减小发生明显的载流子输运,而这又保证了高耐久性。利用所提出的结构,能够实现高达亚纳秒级的p/e速度、超过108个周期的p/e操作以及超过10年的有效保持时间。所提出的结构可以在市售的硅上氮化镓(gan-on-si)平台上制造,在该平台上,外围写/读电路很容易获得,并且能够与其它现有的或新兴的gan基电子器件或光电子器件集成[6-7]。

[0018]

因此,本发明的第一方面提供了一种电荷俘获半导体器件,所述电荷俘获半导体器件包括具有下宽带隙半导体沟道层和一个或更多个对应的欧姆接触区、上宽带隙半导体沟道层和一个或更多个对应的欧姆接触区、布置在上宽带隙半导体沟道层和下宽带隙半导体沟道层之一或这两者上的一个或更多个绝缘层、布置在上宽带隙半导体沟道层/下宽带隙半导体沟道层与它们各自的绝缘层之间的一个或更多个电荷俘获层、以及与对应的绝缘层接触的一个或更多个控制栅极的结构。

[0019]

在某些实施例中,所述上宽带隙半导体沟道层是n型掺杂的,且所述下宽带隙半导体沟道是p型掺杂的。

[0020]

在某些实施例中,所述上宽带隙半导体沟道层是p型掺杂的,且所述下宽带隙半导体沟道是n型掺杂的。

[0021]

在某些实施例中,所述上宽带隙半导体沟道层和所述下宽带隙半导体层之一或这两者是未掺杂的。

[0022]

在某些实施例中,所述电荷俘获层中的至少一个布置在所述上宽带隙半导体沟道层上;所述绝缘层之一布置在所述电荷俘获层上;并且所述控制栅极之一布置在所述绝缘层上,形成顶部栅极结构。

[0023]

在某些实施例中,所述电荷俘获层中的至少一个布置在所述下宽带隙半导体沟道层下;所述绝缘层之一布置在所述电荷俘获层下;并且所述控制栅极之一布置在所述绝缘层下,形成底部栅极或掩埋栅结构。

[0024]

在其它实施例中,在所述上宽带隙半导体沟道层上布置有上电荷俘获层;在所述上电荷俘获层上布置有上绝缘层;并且所述顶部控制栅极布置在所述上绝缘层上,形成顶部栅极结构;而在所述下宽带隙半导体沟道层下布置有下电荷俘获层,在所述下电荷俘获层下布置有下绝缘层,并且所述底部控制栅极布置在下所述绝缘层下,形成底部栅极或掩埋栅结构。

[0025]

在某些实施例中,阻挡层(或称势垒层)布置在所述下宽带隙半导体沟道与所述上宽带隙半导体沟道之间,其包括但不限于具有比下宽带隙半导体沟道层或上宽带隙半导体沟道层的带隙更宽的带隙的半导体材料、或者与下宽带隙半导体沟道层或上宽带隙半导体沟道层形成异质结结构的其它半导体材料。

[0026]

在某些实施例中,所述p型掺杂的宽带隙半导体沟道层由p型掺杂的宽带隙半导体制成,所述p型掺杂的宽带隙半导体包括但不限于p型氮化镓(gan)、p型碳化硅(sic)、p型氮

化铝(aln)、p型氧化镓(ga2o3)、p型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0027]

在某些实施例中,所述n型掺杂的宽带隙半导体沟道由n型掺杂的宽带隙半导体制成,所述n型掺杂的宽带隙半导体包括但不限于n型氮化镓(gan)、n型碳化硅(sic)、n型氮化铝(aln)、n型氧化镓(ga2o3)、n型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0028]

在某些实施例中,所述未掺杂的宽带隙半导体沟道由未掺杂的宽带隙半导体制成,所述未掺杂的宽带隙半导体包括但不限于未掺杂的氮化镓(gan)、未掺杂的碳化硅(sic)、未掺杂的氮化铝(aln)、未掺杂的氧化镓(ga2o3)、未掺杂的金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0029]

在某些实施例中,所述控制栅极由金属、金属合金、金属氧化物、金属氮化物和重掺杂半导体中的一种或多种制成。

[0030]

优选地,所述控制栅极由以下材料中的一种或多种制成:镍、钛、铝、银、金、钨、铬、氮化钛、钨化钛、氧化铟锡和多晶硅。

[0031]

在某些实施例中,所述绝缘层由氧化物、氮化物介电材料、或具有比下宽带隙半导体沟道层或上宽带隙半导体沟道层的带隙更宽的带隙的半导体材料制成。

[0032]

优选地,所述绝缘层由阻挡氧化物(bo)制成,所述阻挡氧化物包括氧化硅(sio)、氧化铝(alo)、氧化镓(gao)、氧化锆(zro)、氧化铪(hfo)或氧化铪锆(hfzro);或者由氮化物介电材料制成,所述氮化物介电材料包括氮化硅(sin)、氮氧化硅(sion)、氮氧化铝(alon)或氮氧化镓(gaon)。

[0033]

在某些实施例中,所述下宽带隙半导体沟道层和所述上宽带隙半导体沟道层由iii族氮化物制成,所述iii族氮化物包括氮化铝(aln)、氮化镓(gan)或氮化铟(inn)、硅化合物或碳化硅(sic)。

[0034]

在某些实施例中,所述上宽带隙半导体沟道层或所述下宽带隙半导体沟道层具有至少两个欧姆接触区,所述至少两个欧姆接触区布置在设置有控制栅极的两个相对侧。

[0035]

在某些实施例中,所述电荷俘获层是与所述绝缘层直接接触的n型、p型或未掺杂的宽带隙半导体沟道层的改性半导体表面。

[0036]

在其它实施例中,所述电荷俘获层是另外的半导体层,其带隙小于所述n型、p型或未掺杂的宽带隙半导体沟道层的带隙。

[0037]

在一些其它实施例中,所述电荷俘获层是金属层。

[0038]

在另一些其它实施例中,所述电荷俘获层是重掺杂的半导体层。

[0039]

在某些实施例中,所述下宽带隙半导体沟道层和所述上宽带隙半导体沟道层由相同的材料制成,形成宽带隙半导体p-n结。

[0040]

在其它实施例中,所述宽带隙半导体沟道层之一由异质半导体材料或多层结构制成,以与另一个宽带隙半导体沟道层形成异质结。

[0041]

在某些实施例中,所述下宽带隙半导体沟道层或所述上宽带隙半导体沟道层也是本器件的衬底。

[0042]

在其它实施例中,所述下宽带隙半导体沟道层或所述上宽带隙半导体沟道层具有

布置在其下的其它衬底材料。

[0043]

优选地,所述下宽带隙半导体沟道层或所述上宽带隙半导体沟道层的至少一个欧姆接触区具有独立的电极。

[0044]

在某些实施例中,所述宽带隙半导体层之一的至少一个欧姆接触区通过互连金属而与另一个宽带隙半导体沟道层的至少两个欧姆接触区之一短接。

[0045]

在某些实施例中,至少一个欧姆接触区是一对n型欧姆接触区,这对n型欧姆接触区布置在设置于下宽带隙半导体层上的阻挡层上,其中在该处布置在阻挡层上的上宽带隙半导体沟道层被有选择性地去除以部分地暴露所述阻挡层,并且布置在其余的上宽带隙半导体沟道层的其中设有控制栅极的两个相对侧上。

[0046]

在某些实施例中,所述电荷俘获半导体器件是掩埋p型沟道氮化镓(gan)场效应晶体管(p-fet)电荷俘获存储器件,所述存储器件可以主要分为两个部分,即,p沟道部分和n沟道部分。

[0047]

在某些实施例中,所述p-fet电荷俘获存储器件包括衬底、布置在衬底上的缓冲层、布置在缓冲层上的n型宽带隙半导体沟道层、布置在n型宽带隙半导体沟道层上的阻挡层、形成布置在阻挡层上的p型宽带隙半导体沟道层的p型掺杂gan(p-gan)、以及布置在p-gan沟道层的凹槽上的栅极结构。

[0048]

在某些实施例中,在p-gan沟道层上,通过从阻挡层有选择性地去除p-gan沟道层的一部分来形成n型异质结沟道区。

[0049]

在某些实施例中,至少一个n型欧姆接触区形成在所述n型异质结沟道区上。

[0050]

在某些实施例中,所述p-fet电荷俘获存储器件的分别作为源极接触区和漏极接触区的一对p型欧姆接触区形成在其中将在p-gan沟道的凹槽上布置栅极结构的位置的两个相对侧上。

[0051]

在某些实施例中,所述栅极结构包括电荷俘获层(tl)、布置在tl上的用作阻挡氧化物(bo)层的介电层、以及布置在bo层上的栅电极。

[0052]

在某些实施例中,所述衬底选自硅、蓝宝石、金刚石、碳化硅(sic)、氮化铝(aln)或氮化镓(gan)。

[0053]

在某些实施例中,所述缓冲层选自氮化铝(aln)、氮化镓(gan)、氮化铟(inn)、或者它们的任何合金。

[0054]

根据在本文中说明的某些实施例,本发明的第二方面提供了一种制造电荷俘获半导体器件的方法,所述方法包括:

[0055]

提供包括至少衬底、缓冲层、下宽带隙半导体层、阻挡层和上宽带隙半导体层的结构;

[0056]

部分地去除上宽带隙半导体沟道层,以部分地暴露阻挡层,以在阻挡层上留下所述上宽带隙半导体沟道层的有源区,用于随后与栅极结构接合;

[0057]

在阻挡层的其中去除了上宽带隙半导体沟道层的区域的两个相对侧上提供一对相同的欧姆接触区;

[0058]

在上宽带隙半导体沟道层的其中将与栅极结构接合的有源区的两个相对侧上提供一对欧姆接触区;

[0059]

在上宽带隙半导体沟道层的有源区处提供凹槽,用于与栅极结构接合;

[0060]

在上宽带隙半导体层的凹槽的表面之上提供电荷俘获层;

[0061]

在上宽带隙半导体沟道层和阻挡层上的欧姆接触区、电荷俘获层、以及除了设有欧姆接触的区域之外的其它区域上提供绝缘层;

[0062]

在上宽带隙半导体沟道层的凹槽上提供栅电极,以覆盖至少栅极底脚区域,在所述栅极底脚区域处在所述凹槽中的电荷俘获层上设有绝缘层;

[0063]

从覆盖所述欧姆接触区的水平表面和部分地覆盖其垂直表面的绝缘层中有选择性地去除绝缘层,使得上宽带隙半导体沟道层保持被绝缘层绝缘,同时对应的欧姆接触区的接触窗口被打开;以及

[0064]

在栅电极和欧姆接触区上沉积焊盘金属以在其上形成焊盘。

[0065]

在某些实施例中,选择硅晶片作为衬底。也可以选择其它可能的候选材料,例如蓝宝石、金刚石、碳化硅(sic)、氮化铝(aln)和氮化镓(gan)。

[0066]

在某些实施例中,所述缓冲层选自氮化铝(aln)、氮化镓(gan)或氮化铟(inn)、或者它们的合金。

[0067]

在某些实施例中,选择gan沟道层作为下宽带隙半导体沟道层。

[0068]

在某些实施例中,所述作为下宽带隙半导体沟道层的gan沟道层被非有意地掺杂有镁。

[0069]

在某些实施例中,选择氮化铝镓(algan)阻挡层作为所述阻挡层。其它可能的阻挡层材料可以选自氮化铝(aln)、氮化镓(gan)、氮化铟(inn)、或者它们的任何合金。

[0070]

在某些实施例中,所述阻挡层可以是单层或多层结构。

[0071]

在某些实施例中,所述上宽带隙半导体沟道层由与下宽带隙半导体沟道层相同的材料制成。

[0072]

在某些实施例中,所述下宽带隙半导体沟道层是n型掺杂的,而且所述上宽带隙半导体沟道层是p型掺杂的。

[0073]

在某些实施例中,所述下宽带隙半导体沟道层是p型掺杂的,而且所述上宽带隙半导体沟道层是n型掺杂的。

[0074]

在某些实施例中,所述下宽带隙半导体沟道层和所述上宽带隙半导体沟道层之一或这两者是未掺杂的。

[0075]

在某些实施例中,所述n型掺杂的宽带隙半导体沟道层由n型宽带隙半导体制成,所述n型宽带隙半导体包括但不限于n型氮化镓(gan)、n型碳化硅(sic)、n型氮化铝(aln)、n型氧化镓(ga2o3)、n型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0076]

在某些实施例中,所述p型掺杂的宽带隙半导体沟道层由p型宽带隙半导体制成,所述p型宽带隙半导体包括但不限于p型氮化镓(gan)、p型碳化硅(sic)、p型氮化铝(aln)、p型氧化镓(ga2o3)、p型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0077]

在某些实施例中,部分地移除所述上宽带隙半导体沟道层以部分地暴露阻挡层并留下用于与栅极结构接合的有源区是通过干法蚀刻进行的,例如等离子体干法蚀刻或数字蚀刻、或者它们的组合。

[0078]

在某些实施例中,在阻挡层的其中去除了上宽带隙半导体沟道层的区域的两个相

对侧上的所述一对相同的欧姆接触区是从金属、金属合金、金属氧化物、金属氮化物、重掺杂的半导体通过利用化学气相沉积、分子束外延、溅射、原子层沉积或蒸发或类似工艺所进行的外延生长制成的。

[0079]

在某些实施例中,在上宽带隙半导体沟道层的其中待接收栅极结构的有源区的两个相对侧上的所述一对不同的欧姆接触区是从金属、金属合金、金属氧化物、金属氮化物、重掺杂的半导体通过利用化学气相沉积、分子束外延、溅射、原子层沉积或蒸发或类似工艺所进行的外延生长制成的。

[0080]

在某些实施例中,所述上宽带隙半导体沟道层的凹槽是通过干法蚀刻、数字蚀刻或者它们的组合提供的。

[0081]

在某些实施例中,所述电荷俘获层是通过对上宽带隙半导体沟道层进行等离子体处理(包括氧等离子体处理)或者通过利用化学气相沉积、分子束外延、溅射、原子层沉积或蒸发或类似工艺所进行的外延生长而提供的。

[0082]

在某些实施例中,所述绝缘层是通过利用化学气相沉积、分子束外延、溅射、原子层沉积或蒸发或类似工艺所进行的外延生长形成介电层而提供的。

[0083]

在某些实施例中,所述栅电极是由金属、金属合金、金属氧化物、金属氮化物或重掺杂的半导体制成的,并且是通过利用化学气相沉积、分子束外延、溅射、原子层沉积或蒸发或类似工艺所进行的外延生长提供的。

[0084]

在某些实施例中,从上宽带隙半导体沟道层有选择性地去除绝缘层以形成对应的欧姆接触区的接触窗口是通过干法蚀刻进行的,例如等离子干法蚀刻、数字蚀刻、或者它们的组合。

[0085]

在某些实施例中,通过用焊盘金属探查对应的欧姆接触区的接触窗口以形成焊盘窗口,并且所述欧姆接触区包括源极接触区和漏极接触区两者。

[0086]

在某些实施例中,所述焊盘金属包括镍、钛、铝、银、金、钨、铬及其任何合金中的一种或更多种。

[0087]

本发明的第三方面提供了一种用于宽带隙半导体基互补逻辑(cl)门的形成在单个衬底上的单片集成的增强型(e-mode)n沟道和p沟道场效应晶体管(n-fet和p-fet)、以及一种在单次工艺执行中制造所述晶体管的方法,所述方法包括:

[0088]

提供衬底,所述衬底上设有缓冲层,

[0089]

布置在缓冲层上的下宽带隙半导体沟道层,

[0090]

布置在下宽带隙半导体沟道层上的阻挡层,以及

[0091]

布置在阻挡层上的上宽带隙半导体沟道层;

[0092]

在上宽带隙半导体沟道层上提供硬掩模,用于在随后的图案化期间进行掩蔽;

[0093]

从n-fet的栅极区域和在p-fet外部的区域有选择性地去除未掩蔽的上宽带隙半导体层;

[0094]

从其中上宽带隙半导体沟道被有选择性地去除的位置去除硬掩模,随后在p-fet和n-fet区域上沉积表面钝化层;

[0095]

通过在表面钝化层上的对应区域中打开接触窗口而分别在n-fet和p-fet上提供对应的欧姆接触区;

[0096]

去除在p-fet的栅极区域上的表面钝化层,随后在上宽带隙半导体沟道层上开凹

槽,以形成凹陷的p-fet栅极区域;

[0097]

对凹陷的p-fet栅极区域进行表面处理,随后在n-fet和p-fet两者上沉积介电层;

[0098]

通过多能级离子注入来隔离所述n-fet和p-fet;

[0099]

从n-fet的对应的欧姆接触区和栅极区域有选择性地去除质电层;

[0100]

分别在n-fet和p-eft的对应的栅极区域上提供栅电极;以及

[0101]

在栅电极和欧姆接触区上沉积焊盘金属以在其上形成焊盘。

[0102]

在某些实施例中,选择硅晶片作为衬底。也可以选择其它可能的候选材料,例如蓝宝石、金刚石、碳化硅(sic)、氮化铝(aln)和氮化镓(gan)。

[0103]

在某些实施例中,所述缓冲层选自氮化铝(aln)、氮化镓(gan)或氮化铟(inn)、或者它们的合金。

[0104]

在某些实施例中,选择氮化铝镓(algan)阻挡层作为所述阻挡层。其它可能的阻挡层材料可以选自氮化铝(aln)、氮化镓(gan)、氮化铟(inn)、或者它们的任何合金。

[0105]

在某些实施例中,选择gan沟道层作为下宽带隙半导体沟道层。

[0106]

在某些实施例中,所述下宽带隙半导体沟道层是n型掺杂的,而且所述上宽带隙半导体沟道层是p型掺杂的。

[0107]

在某些实施例中,所述下宽带隙半导体沟道层是p型掺杂的,而且所述上宽带隙半导体沟道层是n型掺杂的。

[0108]

在某些实施例中,所述下宽带隙半导体沟道层和/或所述上宽带隙半导体沟道层是未掺杂的。

[0109]

在某些实施例中,所述n型宽带隙半导体沟道层由n型宽带隙半导体制成,所述n型宽带隙半导体包括但不限于n型氮化镓(gan)、n型碳化硅(sic)、n型氮化铝(aln)、n型氧化镓(ga2o3)、n型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0110]

在某些实施例中,所述p型宽带隙半导体沟道层由p型宽带隙半导体制成,所述p型宽带隙半导体包括但不限于p型氮化镓(gan)、p型碳化硅(sic)、p型氮化铝(aln)、p型氧化镓(ga2o3)、p型金刚石;或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0111]

在某些实施例中,所述介电层由氧化物、氮化物介电材料或具有比宽带隙半导体沟道层的带隙更宽的带隙的半导体材料制成。

[0112]

在某些实施例中,所述介电层由氧化硅(sio)、氧化铝(alo)、氧化镓(gao)、氧化锆(zro)、氧化铪(hfo)或氧化铪锆(hfzro)制成,或者由氮化物介电材料制成,所述氮化物介电材料包括氮化硅(sin)、氮氧化硅(sion)、氮氧化铝(alon)或氮氧化镓(gaon)。

[0113]

在某些实施例中,所述硬掩模和所述表面钝化层都由氧化硅制成。

[0114]

在某些实施例中,所述表面钝化层由氧化硅(sio)、氧化铝(alo)、氧化镓(gao)、氧化锆(zro)、氧化铪(hfo)或氧化铪锆(hfzro)制成;或者由氮化物介电材料制成,所述氮化物介电材料包括氮化硅(sin)、氮化铝(aln)、氮氧化硅(sion)、氮氧化铝(alon)或氮氧化镓(gaon);或者由双层或多层介电材料制成,所述双层或多层介电材料包括但不限于aln/sin、aln/sio、aln/alo、alon/aln/sin、alon/aln/sio或alon/aln/alo。

[0115]

在某些实施例中,所述对凹陷的p-gan栅极区域的表面处理是通过等离子体处理

实施的,所述等离子体包括但不限于氧等离子体、氢等离子体和氮等离子体;或者是通过溶剂处理实施的,所述溶剂包括但不限于稀释或未稀释的盐酸、氢硫酸、氢氟酸、食人鱼溶液、四甲基氢氧化铵溶液、氨溶液。

[0116]

在某些实施例中,所述多能级离子注入选自氟离子注入。

[0117]

在某些实施例中,所述n-fet与p-fet的对应栅极具有1:10的栅极纵横比。

[0118]

在某些实施例中,所述n-fet和p-fet中的每一个的欧姆接触区是源极接触区和漏极接触区。

[0119]

在某些实施例中,所述焊盘金属包括镍、钛、铝、银、金、钨、铬及其任何合金中的一种或更多种。

[0120]

本发明的其它方面包括一种通过使用第三方面所述的方法制备的集成gan互补逻辑(cl)门、以及一种结合有一个或更多个集成gan cl门的单级或多级逻辑电路,其中所述单级逻辑电路包括但不限于反相器、或非(nor)门、与非(nand)门和传输门;所述多级逻辑电路包括但不限于具有多达15级互补逻辑门的锁存单元和环形振荡器。

[0121]

本节“发明内容”部分提供了将在下面的“具体实施方式”部分中进一步描述的一些概念的简要介绍。本节“发明内容”部分并非旨在确定所要保护的主题的关键特征或基本特征,也并非旨在帮助确定所要保护的主题的范围。在下文的实施例中公开了本发明的其它方面。

附图说明

[0122]

附图中的相同附图标记表示相同元件或在功能上相似的元件,附图包括某些实施例的图形,以进一步示出和阐明本发明的上述和其它方面、优点和特征。应当理解,这些附图仅示出了本发明的一些实施例,而并非意图限制本发明的范围。下面将使用附图以更多特征和细节来说明和解释本发明,在附图中:

[0123]

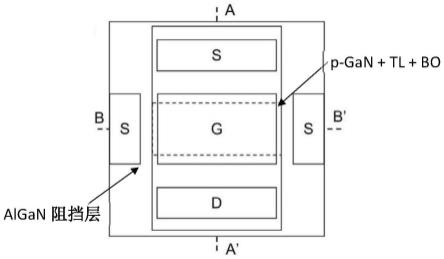

图1a示出了根据本发明的某些实施例的在gan异质结上的电荷俘获半导体器件的俯视图;

[0124]

图1b示出了图1a所示的器件的用于p沟道部分的横截面图(a-a’);

[0125]

图1c示出了图1a所示的器件的用于n沟道部分的另一个横截面图(b-b’);

[0126]

图2示出了描绘根据本发明的某些实施例的在gan异质结上制造电荷俘获半导体器件的方法的流程图;

[0127]

图3示出了描绘根据本发明的某些实施例的制造方法的一系列横截面图,这些横截面图分别示出了p沟道部分和n沟道部分的横截面;

[0128]

图4a示出了根据本发明的某些实施例的电荷俘获半导体器件的准静态转移曲线;

[0129]

图4b示出了根据本发明的某些实施例的电荷俘获半导体器件的脉冲模式转移曲线,其中示出了两种存储状态和2.2伏的存储窗口;

[0130]

图5a示出了在用不同的擦除脉冲宽度(te)和-10伏的固定擦除电压(ve)进行擦除操作后测得的根据本发明的某些实施例的电荷俘获半导体器件的转移曲线;虚线包围的曲线代表被有效擦除的曲线;

[0131]

图5b示出了在用不同的编程脉冲宽度(t

p

)和20伏的固定编程电压(v

p

)进行编程操作后测得的根据本发明的某些实施例的电荷俘获半导体器件的转移曲线;虚线包围的曲线

代表被有效编程的曲线;

[0132]

图6a示出了在针对保持特性测量使用变化的延迟时间进行p/e操作后测得的根据本发明的某些实施例的电荷俘获半导体器件的转移曲线;两个不同的虚线圆分别代表在固定擦除电压和固定编程电压下的保持性能测量值;

[0133]

图6b示出了从图6a中的对应的虚线包围的保持特性测量值提取的v

th

;

[0134]

图7a示出了在针对耐久特性测量的p/e循环后测得的根据本发明的某些实施例的电荷俘获半导体器件的转移曲线;两个不同的虚线圆分别代表在固定擦除电压(ve)和固定编程电压(v

p

)处的耐久性特性测量值;

[0135]

图7b示出了从如图7a所示的虚线包围的耐久特性测量值提取的v

th

,其中v

p

=20伏并且ve=-10伏;

[0136]

图8a示出了在针对耐久特性测量的不同p/e循环后测得的根据本发明的某些实施例的电荷俘获半导体器件的转移曲线;两个不同的虚线圆分别代表在固定擦除电压(ve)和固定编程电压(v

p

)处的耐久性特性测量值;

[0137]

图8b示出了从如图8a所示的虚线包围的耐久特性测量值提取的v

th

,其中v

p

=10伏并且ve=-10伏;

[0138]

图9示意性地描绘了根据本发明的某些实施例的集成gan互补逻辑(cl)反相器的制造方法;

[0139]

图10a示意性地描绘了按照图9所示的制造方法制备的集成gan cl反相器的透视图;

[0140]

图10b示意性地描绘了集成gan cl反相器在两个静态逻辑状态下的对应电路图,其中在每个静态状态下只有一个fet导通;

[0141]

图10c示意性地描绘了集成gan cl反相器的n-fet和p-fet在不同逻辑输入下的能带图,并示出了它们如何产生被极大抑制的静态功耗;“br”和“ox”分别指阻挡层和氧化物介电层;“e

fn”和“e

fp”分别表示在非平衡系统中的电子和空穴的准费米能级;

[0142]

图10d以灰度图示出了集成gan cl反相器的sem图像;n-fet和p-fet两者的无源区都是通过氟离子注入(一种平面隔离技术)限定的,以使本器件看起来是一种没有明显的台面-沟槽的平面结构;

[0143]

图11a示出了根据本发明的某些实施例的集成gan cl反相器的n-fet和p-fet的栅极电容;vs、vg和vd分别表示施加至反相器的源极、栅极和漏极的电压;

[0144]

图11b以对数标度示出了如图11a所示的n-fet和p-fet的转移特性;

[0145]

图11c示出了根据本发明的某些实施例的集成gan cl反相器的n-fet和p-fet的输出特性(i-v);

[0146]

图12a示出了根据本发明的某些实施例的gan cl反相器在不同电源电压(v

dd

)下的输入-输出电压(v

in-v

out

)转移特性;

[0147]

图12b示出了根据本发明的某些实施例的gan cl反相器通过在不同v

in

和v

dd

下从电源获取电流所产生的准静态功耗;

[0148]

图12c示出了根据本发明的某些实施例的gan cl反相器在不同v

in

和v

dd

下的电压增益;

[0149]

图12d示出了根据本发明的某些实施例的gan cl反相器在5伏v

dd

下的噪声容限

(1201);1201代表转换窗口区域;1203代表在单位增益点限定的转换窗口的边界;插图示出了使用三维共焦激光显微镜进行测试所获得的反相器的图像;

[0150]

图12e示出了根据本发明的某些实施例的gan cl反相器在从室温到200℃范围内的不同温度下的电压转移曲线;

[0151]

图12f按照逻辑“低”和“高”输出电压(分别表示为v

ol

和v

oh

)、更低和更高输入转换电压(分别表示为v

il

和v

ih

)以及转换阈值(v

th

)汇总了根据本发明的某些实施例的gan cl反相器在5伏v

dd

下在不同温度下的噪声容限;

[0152]

图12g示出了根据本发明的某些实施例的gan cl反相器在5伏v

dd

和从100khz到2mhz的变化驱动频率的连续开关操作下的v

in

和v

out

的波形;

[0153]

图12h示出了根据本发明的某些实施例的gan cl反相器在其平均v

ih

、v

th

和v

il

(n=50)方面的转移特性;ave:平均;dev.:偏差;

[0154]

图13a示出了按照本发明的某些实施例制备的nand门的共焦激光显微镜灰度图像;

[0155]

图13b示出了图13a中的nand门的电路图;

[0156]

图13c示出了图13a中的nand门的输入-输出波形;

[0157]

图13d示出了按照本发明的某些实施例制备的nor门的共焦激光显微镜灰度图像;

[0158]

图13e示出了图13d中的nor门的电路图;

[0159]

图13f示出了图13d中的nor门的输入-输出波形;

[0160]

图13g示出了按照本发明的某些实施例制备的传输门的共焦激光显微镜灰度图像;

[0161]

图13h示出了图13g中的传输门的电路图;

[0162]

图13i示出了如图13g所示的传输门的输入-输出波形,其中所述传输门被阻断,输出模式是高阻抗(高z);

[0163]

图14a示出了根据本发明的某些实施例的由两个交叉耦合的反相器构成的锁存单元的电路图;

[0164]

图14b示出了按照图14a的电路图制备的锁存单元的共焦激光显微镜灰度图像;

[0165]

图14c示出了在不同输入电压下测得的图14b中的锁存单元的输入-输出波形,其中开关“s”间歇地闭合以加载输入信号(灰色阴影区域);

[0166]

图14d示出了在加载逻辑状态并打开开关“s”之后在长时间偏压下测量的图14b中的锁存单元的输入-输出波形;

[0167]

图15a示出了按照本发明的某些实施例制备的振荡器(osc)的电路图;

[0168]

图15b示出了按照图15a的电路图制备的15级环形振荡器的共焦激光显微镜灰度图像;

[0169]

图15c示出了在输出缓冲反相器(具有5伏v

dd

)的输出处监测的如图15b中的环形振荡器的单个振荡周期(t

osc

)(灰色阴影区域)的输出波形(上图)、以及具有502khz的基频和例如1.004mhz的后续谐波峰值的对应功率谱(p

out

)(下图);

[0170]

图15d示出了如图15b中的环形振荡器的基本振荡频率(f

osc

)的电源电压依赖性(上图)及其每一级的功率时延乘积(下图);

[0171]

图15e示出了图15d中所示的环形振荡器的f

osc

的温度依赖性(上图)及其每一级的

功率时延乘积(下图);

[0172]

图15f示出了具有不同数量的反相器级(n)的如图15b中的环形振荡器的相应f

osc

(上图)和振荡周期(t

osc

),其中t

osc

对n的线性拟合产生了每级61纳秒的平均传播延迟(τ

pd

)。

[0173]

本领域技术人员可以理解,附图中的元件是出于简洁和清晰的目的示出的,并且不一定是按比例绘制的。

具体实施方式

[0174]

对于本领域技术人员来说显而易见的是,能够做出各种修改,包括添加和/或替换,而并未脱离本发明的范围和精神。可以省略具体细节,以避免模糊本发明;但是,撰写本公开的目的是为了使本领域技术人员不需要进行过分的实验就能实践本文的教导。

[0175]

请转到图1a,其中以俯视图描绘了本器件的一种优选结构,所述结构至少包括:

[0176]

布置在上宽带隙半导体、p型掺杂gan(p-gan)、沟道层的凹陷沟槽(在由垂直于图1a的俯视图中的两条虚线的两条平行虚线所限定的矩形区域中示出)上的控制栅极(g);

[0177]

布置在控制栅极的两个相对侧上并与p-gan沟道层接触(如图1b的横截面所示)的两个源极(s)接触区和漏极(d)接触区;

[0178]

布置在控制栅极的另外两个相对侧上并与algan阻挡层接触(如图1c的横截面所示)的另外两个相同的源极(s)接触区;

[0179]

除了源极接触区和漏极接触区之外,绝缘层(例如阻挡氧化物(bo)层)布置在包括在控制栅极下的凹陷沟槽区的p-gan沟道层上;

[0180]

在绝缘层与p-gan沟道层之间布置在其上设有控制栅极的p-gan沟道的凹陷沟槽的水平表面处的电荷俘获层(tl);以及

[0181]

布置在algan阻挡层下的下宽带隙半导体n型沟道层(例如gan沟道)。

[0182]

控制栅级(g)包括由金属、金属合金、金属氧化物、金属氮化物和重掺杂半导体中的一种或多种形成的栅电极,所述金属、金属合金、金属氧化物、金属氮化物和重掺杂半导体包括但不限于镍(ni)、钛(ti)、铝(al)、银(ag)、金(au)、钨(w)、铬(cr)、氮化钛(tin)、钨化钛(tiw)、氧化铟锡(ito)和多晶硅。

[0183]

形成绝缘层的阻挡氧化物(bo)包括但不限于氧化硅(sio)、氧化铝(alo)、氧化镓(gao)、氧化锆(zro)、氧化铪(hfo)和氧化铪锆(hfzro)。用于制造绝缘层的其它潜在材料包括氮化物介电材料或具有比宽带隙半导体沟道层的带隙更宽的带隙的半导体材料,例如氮氧化硅(sion)、氮氧化铝(alon)和氮氧化镓(gaon)。

[0184]

除了氮化镓(gan)之外,上宽带隙半导体沟道层和下宽带隙半导体沟道层也可以由碳化硅(sic)、氧化镓(ga2o3)、氮化铝(aln)、金刚石制成,或者由宽带隙半导体异质结结构制成,所述宽带隙半导体异质结结构包括但不限于algan/gan和aln/gan结构。

[0185]

如图1b所示(该图是沿着图1a中的结构的俯视图的a-a’平面截取的横截面图),上宽带隙半导体沟道层(p-gan)可以具有至少两个欧姆接触区,这两个欧姆接触区分别由d和s表示,布置在控制栅极的两侧。

[0186]

电荷俘获层(tl)可以是与绝缘层直接接触的宽带隙半导体沟道层的改性半导体表面,或者是具有比宽带隙半导体沟道层的带隙更小的带隙的另外的半导体层,或者是金属层。

[0187]

下宽带隙半导体沟道层可以由与上宽带隙半导体沟道层相同的材料制成,但是其掺杂类型不同,以与宽带隙半导体沟道形成p-n结;或者由异质半导体材料或多层材料制成,以与宽带隙半导体沟道形成异质结。

[0188]

在下宽带隙半导体沟道层由与上宽带隙半导体沟道层相同的材料制成的情况下,一个优选实施例是氮化镓(gan)。其它可能的材料可以是碳化硅(sic)、iii族氮化物、氧化镓(ga2o3)或金刚石。

[0189]

上宽带隙半导体沟道层和下宽带隙半导体沟道层的掺杂类型可以相同或不同。

[0190]

在某些实施例中,下宽带隙半导体沟道层也是本器件的衬底。

[0191]

在其它实施例中,下宽带隙半导体沟道层具有布置在其下的其它衬底材料。

[0192]

在下宽带隙半导体沟道层具有至少一个欧姆接触区时,它可以是独立的电极,或者如图1c所示(该图是沿着图1a的结构的俯视图的b-b’平面截取的截面图),或者通过一个或更多个互连金属层与其它两个欧姆接触区之一短接。

[0193]

在下宽带隙半导体沟道层不是所述器件的衬底的情况下,可以在其下布置一种或多种其它衬底材料,例如缓冲层、成核层和/或硅晶片。

[0194]

请转到图2,其中示出了一种根据某些实施例的在gan基异质结上制造wbg半导体bct非易失性存储器结构的方法的流程图。图3提供了对应的示意图,该示意图根据图2中所示的每个步骤以相应的横截面图(分别与图1b和1c中的a-a’和b-b’平面对应)描绘了本器件的p沟道和n沟道部分中的几何变化,其中所述方法包括初始地提供布置在衬底上的缓冲层、布置在缓冲层上的gan沟道层、布置在gan沟道层上的algan阻挡层、以及最后的布置在algan阻挡层上的p-gan层(s201,301a,301b)。如果下宽带隙半导体沟道层不是本器件的衬底,那么执行这个初始步骤。然后通过从其中有选择性地蚀刻p-gan层来形成n型异质结沟道区(s202,302a,302b)。然后在n型异质结沟道上形成n型欧姆接触区(s203,303b)。然后在将被限定的p-gan栅极区域的两个相对侧上的p-gan层上形成p型欧姆源极/漏极接触区(s204,304a)。然后有选择性地使p-gan层凹陷,以限定p-gan栅极区域(s205,305a,305b)。之后,在p-gan栅极区域上按顺序地沉积电荷俘获层(tl)和阻挡氧化物(bo)层(s206,306a,306b)。在形成bo层之后,在p-gan栅极区的bo层上进一步形成栅极接触区(例如栅电极)(s207,307a,307b)。通过从源极和漏极接触区上去除对应的bo层来打开源极和漏极接触区(s208,308a,308b),随后通过在源极、漏极和栅极接触区上探查焊盘金属以在其上形成焊盘(s209,309a,309b)。用于执行本方法的每个步骤的其它细节将在以下说明的其它实施例或实例中提供。

[0195]

请转到图4a和4b,大的迟滞窗口表明了所提出的wbg半导体bct非易失性存储器件对于存储器应用的极佳适合性。

[0196]

请转到图5a和5b,具有100纳秒擦除脉冲宽度的-10伏擦除电压和具有短至20纳秒的编程时间的20v编程电压足以进行有效的编程和擦除,由此表明所提出的器件能实现超快的p/e速度。

[0197]

请转到图6a和6b,其中示出了所提出的器件能够在104秒的保持时间后保持编程/擦除状态。10年寿命是根据测量结果推算出来的,且在10年的保持时间后,仍能保持1.5伏的良好存储窗口。

[0198]

请转到图7a和7b,其中示出了所提出的器件能够承受超过106次p/e循环而没有显

著的劣化。

[0199]

请转到图8a和8b,所提出的器件显现出增强的耐久性能,其能够承受超过108次p/e循环。

[0200]

下面的实例将说明如何将所提出的包括上宽带隙半导体沟道和下宽带隙半导体沟道的结构应用在包括各种互补逻辑(cl)门的不同集成电路中、以及它们的相应制造方法。

[0201]

实例

[0202]

(a)用于互补逻辑(cl)门的在单个衬底上的增强型(e-mode)n沟道和p沟道gan场效应晶体管(n-fet和p-fet)的单片集成

[0203]

在大的硅衬底上制造的作为功率开关器件的基于氮化镓(gan)的平面异质结型高电子迁移率晶体管(hemt)需要用作驱动、控制、感测和保护模块的外围电路,因此需要单片集成以产生片上功能,增强鲁棒性,并促进功率转换系统的小型化。gan hemt的平面构型(即,源极、栅极和漏极位于顶表面上)有益于高密度集成,但目前大多数常规gan集成电路主要基于以电子作为多数载流子的n沟道器件。此外,gan功率器件的典型外围电路由很大数量的逻辑块组成。互补金属氧化物半导体(cmos)拓扑在硅基逻辑电路中占主导地位,因为它能够为超大规模集成电路(vlsi)和混合信号ic提供最高效节能的方案。但是,在常规gan-cmos电路中,没有适当的集成策略来将增强型n-fet和p-eft两者都结合在单个衬底上。

[0204]

通过使用在本文中说明的制造方法,制造了具有轨到轨操作和超低静态功耗的集成cmos基本逻辑门,例如反相器、或非(nor)门、与非(nand)门和传输门、以及多级逻辑电路,例如两级锁存器和环形振荡器。为以p-gan/algan/gan外延叠层为特征的功率电子器件所设计的市售硅上氮化镓(gan-on-si)晶片可以用作ic制造的“衬底”。氧等离子体处理(opt)用于形成具有用于互补逻辑(cl)电路的特性的掩埋p沟道结构增强型fet。例如,通过本方法制造的反相器表现出恰到好处的转变阈值和尖锐的转变区域,为多级逻辑门集成提供了良好的噪声容限和鲁棒性;可以制造具有多达15级的两级锁存器和环形振荡器。

[0205]

gan hemt通常是基于纤锌矿gan及其合金的异质结(例如algan/gan异质结)而制造的。非中心对称的纤锌矿结构以及在氮与iii族元素(例如镓、铝、铟)之间的明显的电负性差异在iii族氮化物化合物中诱发显著的极化效应,其中由在不同堆叠的合金层之间的晶格失配引起的应变诱发了额外的压电极化。在algan/gan异质界面处的高密度极化电荷(大约10

13

cm-2

)产生了一个尖锐的势阱,其中形成了具有非常高的电子迁移率(大约2000cm2/v.s)的二维电子气(2deg)。

[0206]

由于gan hemt是自然的耗尽型(d-mode)晶体管,为了实现增强型操作,在algan层之上的栅极区中设有一层p-gan(通常是重掺杂的),以耗尽下面的2deg。

[0207]

gan hemt的互补器件(例如p沟道gan fet)不太常见,因为在gan材料中的空穴迁移率与电子迁移率相比相当低(在室温下《50cm2/v

·

s,典型地是大约15cm2/v

·

s),电子迁移率固有地源于价带结构和本征的强声子散射。虽然对p-fet平台的设计进行了一些明显的改进以提高空穴迁移率或电流密度,但是本征迁移率失配并不支持gan作为面向低功率高速逻辑电路的先进cmos技术的合适候选。另一方面,将外围电路与在中频下工作的gan功率开关单片集成的期望为gan互补cl电路提供了迷人而又轻松的机会。典型的工作频率在

100khz~10mhz范围内,这对于gan cl电路是技术上能够达到且成本可接受的。因此,本器件从主流gan功率平台(p-gan/algan/gan-on-si)开始,而不是从被设计成使gan p-fet的电流密度最大化的其它特定外延结构开始。

[0208]

用于n-fet(在algan/gan异质结处)和p-fet(在p-gan层中)的位置自然地共存,并且是固有地去耦的,因为p-gan层和薄algan阻挡层被设计成耗尽下面的2deg n沟道。cl电路中所需的增强型n-fet可以使用与用于常关p-gan栅极功率hemt的工艺相同的工艺来实现,具有更短的栅极-漏极距离。密集的外延生长和工艺优化已经在这样的商业平台上产生了高质量的p-gan层。霍尔测量结果表明,室温下的空穴薄层密度为大约1.23

×

10

13

cm-2

,空穴迁移率为大约10.2cm2/v

·

s,这与从其它平台提取的数据在同一范围内。p-fet的实质增强型操作可以通过用于保持合理的空穴电流密度的掩埋沟道结构来实现。

[0209]

(b)集成gan cl反相器的外延结构和制造

[0210]

在本文中说明的所有集成gan逻辑电路优选地在单次工艺运行中在硅上氮化镓(gan-on-si)晶片上制造。在这个实例中,n-fet的特征在于其构型具有2微米的栅极-源极间距(l

gs

)、3.5微米的栅极长度(lg)、2微米的栅极-漏极间距(l

gd

)和10微米的栅极宽度(wg);p-fet的l

gs

/lg/l

gd

/wg分别是3/1.5/3/100微米。iii族氮化物外延层通过金属有机化学气相沉积(mocvd)生长在p型低阻硅晶片上,由4微米过渡/缓冲层、非有意掺杂的gan沟道层、12纳米algan阻挡层、以及具有标称镁掺杂浓度大约为3

×

10

19

cm-3

的85纳米p-gan层组成。在器件制造之前,对样品进行基于湿溶液的清洗步骤,包括在丙酮中进行超声波处理和在缓冲氧化物蚀刻剂(boe)中浸泡,以去除表面污染物和天然氧化物。随后,将样品装载到等离子体增强化学气相沉积(pecvd)室中,以沉积大约70纳米厚的二氧化硅层,作为p-gan的干法蚀刻的硬掩模。

[0211]

所有的图案限定都是通过光刻法进行的。第一次图案化是去除在为p-fet保留的区域和n-fet的p-gan栅极之外的p-gan。通过使用chf3/o2混合气体的反应离子蚀刻(rie)打开硬掩模,随后利用感应耦合等离子体反应离子蚀刻(icp-rie)系统使用bcl3等离子体进行p-gan蚀刻。蚀刻深度由预先校准的蚀刻时间控制,并通过原子力显微镜(afm)检测。在干法蚀刻后,通过浸入boe中来去除硬掩模。然后沉积另一层70纳米的二氧化硅层,作为表面钝化层。然后,通过在钝化层上打开接触窗口、电子束蒸发ti/al/ni/au金属叠层(20/150/50/80纳米)、剥离和在氮气气氛中在850℃处快速热退火(rta)30秒,来形成n-fet的欧姆接触区。通过类似的方式形成p-fet的欧姆接触区,但其中将金属叠层改变为ni/au(两者都是20纳米厚),并且在氧气气氛中在550℃处进行退火10分钟。通过使用传输长度法(tlm)将p-fet的接触电阻提取为61ω

·

mm。

[0212]

p-fet的沟道区由凹陷沟槽限定,所述凹陷沟槽是通过利用rie进行的钝化层开口和利用icp-rie进行的p-gan蚀刻所形成的。保留大约30纳米(总厚度为85纳米)的p-gan层作为沟道区。为了实现增强型操作,使用低功率氧等离子体在icp室中对蚀刻的p沟道表面原位进行氧等离子体处理(opt)。icp等离子体的线圈功率(coil power)和压板功率(platen power)分别为50瓦和30瓦。室压设定为10毫托,氧气气流设定为10sccm。处理时间为1分钟。用x射线光电子能谱(xps)对经过opt和未经过opt的p-gan表面进行了表征。

[0213]

在opt之后,将样品装载到原子层沉积(ald)系统中,以沉积p-fet的栅极电介质层。使用大约20纳米的三氧化二铝作为栅极电介质。随后,通过多能级(最高110kev)氟离子

注入进行器件隔离。这种平面隔离技术能够消除在基于台阶-沟槽的方案中的泄漏侧壁,并能够有效地抑制泄漏电流。在n-fet中,栅极金属与p-gan直接肖特基接触。通过ni/au的电子束沉积和剥离同时形成n-fet和p-fet两者的栅电极和探查焊盘。图9示出了描绘这个实例的制造工艺的示意图,且图10a和10d分别示出了按照该制造工艺制备的集成gan cl反相器的示意性透视图和sem图像。

[0214]

请转到图10b和10c,p-gan层用作在n-fet沟道中的栅极叠层的一部分,这提高了能带,以在热平衡下耗尽下面的2deg沟道。结果,在反相器的输入是逻辑

‘0’

时,从电源(v

dd

)至地(gnd)的电流路径被n-fet阻断(图10b-(i))。在正栅极偏压的情况下,所述能带向下弯曲,并且电子被诱导到2deg沟道中以传导电流(图10c-(ii)),而在p-fet沟道中,在栅极下的p-gan用作p沟道并且被减薄,从而它能够被栅极有效地控制。在适度的凹槽蚀刻之后进行氧等离子体处理(opt),以将剩余的p-gan的顶部部分转化为无孔区域,因为氧会补偿镁掺杂或者通过形成镁氧络合物而钝化镁。这样的opt过程促进了在热平衡下的p沟道的耗尽(图10c-(iv))。因此,p-fet沟道被配置为增强型(e-mode),并利用逻辑

‘1’

输入阻断从v

dd

到gnd的电流路径(图10b-(ii))。由于具有相对于源极(其被连接至v

dd

)的负栅极偏压,因此所述能带被向上拉,并且掩埋p沟道开始形成(图10c-(iii))。在这种导通状态下,空穴位于掩埋沟道中,即,在远离电介质与半导体层的界面的p-gan区域中,在该区域中发生显著的无序/界面散射。掩埋p沟道与界面区域相比具有更高的晶体质量,并且受到的来自所述界面的不利影响更少,在该界面处,凹槽蚀刻引起的损害比较集中。因此,通过增强型操作实现了合理的空穴电流密度,使反相器的输出能够在两种逻辑状态下分别达到v

dd

和gnd的供电轨。

[0215]

(c)分立的n-fet和p-fet沟道的准静态器件表征

[0216]

请转到图11a,其中示出了栅极电容-栅极电压(c

g-vg)特性的差异,揭示了n-fet和p-fet沟道的不同器件工作原理。对于n-fet沟道,漏极电流(id)是通过调整在2deg沟道中的电子密度来调节的。由于所有载流子都被限制在2d薄层中,因此它们通过平行板电容与在栅极金属中的电荷耦合,且由此在器件被接通时,n-fet沟道的c-v曲线大致呈现一个平台。对于掩埋p-fet沟道,在工作栅极电压范围内(例如0~-5伏),其id是通过控制非耗尽的p-gan层(即,沟道)的厚度来调节的。因此,可变的耗尽边界导致了依赖于vg的cg。

[0217]

请转到图11b,对数标度的转移曲线表明n-fet和p-fet沟道都是真正的增强型的,具有几乎对称的阈值电压,极大地抑制了栅极电流和关断状态的漏极泄漏。由于在p-fet中的mos栅极叠层和在n-fet中的肖特基型p-gan/algan/gan栅极叠层,这两个沟道都表现出高的通/断比、非常小的泄漏电流和受到抑制的栅极电流,从而产生gan互补逻辑模块的高的准静态/静态输入阻抗,这确保了在多级逻辑电路中的轨到轨操作,而超低关断状态泄露电流确保了在两种逻辑状态下的低静态功耗。

[0218]

请转到图11c,n/p-fet沟道的输出电流-电压(i-v)特性表明,由于它们在gan材料中的电子和空穴迁移率之间的固有失配,在它们的电流密度之间存在显著的失配,因此需要小心配置n-fet和p-fet的栅极宽度比以解决这种失配。优选地,在本发明中,n-fet与p-fet的栅极宽度比为1:10。

[0219]

与其中p-fet和n-fet都具有

‘

金属氧化物半导体(mos)’栅极叠层的常规硅基cmos电路不同的是,根据本发明的某些实施例,只有p-fet具有

‘

mos’结构,而n-fet基本上是异

质结场效应晶体管(hfet)。因此,对在本反相器中的电路的更适当的解释应是具有

‘

类似cmos的’行为的

‘

互补逻辑(cl)电路’,而不是

‘

cmos’。但是,应说明的是,在本发明的增强型n-fet的栅极叠层中,在algan/gan异质结构上有附加的p-gan层。因此,栅极i-v特性明显不同于常规的hfet,从而形成更像mosfet的n-fet。本发明中的n-fet的特征在于具有p-gan栅极叠层,其可以被模型化为p-i-n结(即,p-gan/algan/gan结)和栅极金属/p-gan肖特基结的串联连接。肖特基结在正的正向栅极偏压下是反向偏压的,从而抑制栅极泄漏,使栅极正向击穿电压大于10伏,并增大栅极电压摆幅,所有这些对于采用标准5伏电源电压的gan互补ic的操作都是至关重要的。

[0220]

(d)gan cl反相器的表征

[0221]

请转到图12a,在不同的电源电压(v

dd

)下,逻辑

‘1’

输出电压电平总是等于v

dd

,而逻辑

‘0’

输出总是0伏,即,反相器的输出从v

dd

的轨道摆动到gnd的轨道(轨到轨),这表明实现了轨到轨操作。通常在v

in

=v

out

下限定的转换阈值(v

th

)位于v

dd

的一半,因为n-fet和p-fet的阈值电压是对称的。在v

dd

仅为2伏时,gan cl反相器表现出三态行为,因为在v

in

大约为1伏时,n-fet和p-fet两者均处于关断状态。

[0222]

请转到图12b,其中示出了gan cl反相器的功耗发生在转换状态期间,但是在n-fet和p-fet两者都表现出严格的增强型操作和高的开/关电流比(大约107)时,与转换状态相比,在两种静态状态(v

in

=0伏或v

dd

)下的功耗被大大抑制了高达3个数量级(取决于v

dd

)。本发明的gan cl反相器的这种静态功耗特性与cmos电路的最重要的特性(即,低静态状态功耗)等同,就能效而言,这种静态功耗特性优于其它传统的逻辑电路方案,例如电阻-晶体管逻辑(rtl)或直接耦合fet逻辑(dcfl)结构。随着v

dd

的增大,转换窗口变窄,而电压增益提高,其中在5伏的v

dd

时记录到80伏/伏的最大峰值增益(图12c)。

[0223]

在gan功率电子器件中,通常为逻辑控制子电路使用5伏电源。本反相器也适合于在这种5伏的v

dd

下工作。图12d示出了按照交叉耦合反相器电压转移关系所分析的本反相器的噪声容限,其中逻辑

‘

低’电平(v

il

–vol

)的噪声容限是2.1伏,而逻辑

‘

高’电平(v

oh

–vih

)的噪声容限是2.6伏,这表明两个噪声容限都足够大,从而本反相器被示为具有对各种噪声(例如由高频电源开关产生的电磁干扰)的高抗扰性。

[0224]

请转到图12e,其中示出了在从室温到高达200℃的升高温度下测量的本gan cl反相器的电压转移,从中提取了特征转换电压并汇总在图12f中。虽然在高温下转换窗口和v

th

的偏差略有扩大,但是gan cl反相器的优异特性(例如轨到轨操作、宽噪声容限、以及快速的逻辑状态转换)仍得以很好地保留。在高达350℃的高温下(在图12e中未示出),虽然输出摆幅略有压缩,但仍能获得不错的噪声容限(大约1.83伏)和电压增益(大约18.1伏/伏)。相比之下,由于硅的带隙相对较窄(大约1.1ev),常规的体硅cmos电路的工作温度通常被限制于125℃,或者在某些特殊应用中被限制于175℃,因为硅mosfet无法有效关断,并且热诱发的结泄漏电流很容易导致闩锁和故障。已经开发了用于在较高的温度下工作的基于绝缘体上硅(soi)和碳化硅(sic)的cmos电路。soi cmos电路不存在闩锁问题,并且能抑制体泄漏电流,因而能够在高达300℃的高温下工作。由于在sic中的3.26ev的较宽带隙,sic cmos的工作温度进一步提高到400℃和以上。另一方面,gan具有大约3.4ev的较宽带隙,并为开发在高温下应用的器件和电路提供了有利的平台。此外,本发明中采用的基于异质结的外延结构自然地没有闩锁过程,因为它没有寄生晶闸管结构。在本文中描述的gan cl反相器已

经显现出显著的高温耐用性,这表明它们很有潜力在恶劣环境中部署。

[0225]

请转到图12g,对本发明的反相器在采用高达2mhz的变化驱动频率的连续开关操作下的波形进行了测量,其中其上升时间受到p-fet的限制。但是,本实例中的p-fet尚未达到迁移率的固有极限。随着对沟道凹槽蚀刻和氧化工艺的进一步优化,预计在相同器件尺寸下的p-eft的电流密度会增大,且因此工作频率会提高几兆赫兹。此外,由于所用的光刻技术的限制,本实例中的p-fet的栅极长度为1.5微米。通过能够同时降低沟道电阻和栅极电容的合理的器件缩放,p-fet的速度能够大大提高到数兆赫兹。通过使用8英寸生产线来生产gan功率hemt器件,亚微米光刻技术能够将栅极长度(lg)缩减到180~250纳米。考虑到掩埋p沟道结构、电源电压级别和短沟道效应,可以采用250纳米的lg来在当前gan cl电路中实现以数兆赫兹频率工作。

[0226]

请转到图12h,对各自具有2

×

2平方厘米表面积的50个反相器在它们的平均边界输入电压(v

il

、v

ih

)和转换阈值(v

th

)方面的转移特性进行了表征。与n-fet的导通过程相关的v

il

的紧密分布表明所制造的n-fet有良好的一致性。由于本发明中的p-fet是通过干法蚀刻制造的,因此蚀刻深度的波动可能导致v

th

和v

ih

的分布稍稍粗劣。不过,本文中描述的所有反相器都表现出能够以足够的噪声容限工作,并且,在工业规模的大规模生产期间,其一致性有望得到显著改善。

[0227]

(e)在单级gan单片集成cl门中的应用

[0228]

除了用在集成gan cl反相器中之外,本器件结构还适合于形成作为逻辑电路的基本构件的其它基本cl门。

[0229]

请转到图13a-13i,其中提供了由共焦激光显微镜拍摄的nand门(图13a)、nor门(图13d)和传输门(图13g)的灰度图像、以及它们各自的电路图(分别是图13b、13e和13h)和操作波形(分别是图13c、13f和13i),在图中标明了对应的逻辑状态。在这个实例中,nand和nor门均按照其真值表展现了正确的逻辑运算,并以亚mhz工作频率提供轨到轨输出。馈入nand门的两个输入信号都是0.5mhz,具有90

°

相移,这驱动输出信号等效地以1mhz的频率切换。但是,由于nor门的两个p-fet是串联的,因此nor门表现出较慢的开关速度。因此,它的特征是具有0.25mhz的输入信号。可以在不同的逻辑门中进一步调整器件比率,以产生最佳性能。具有并联的互补n-fet和p-fet的传输门允许信号在导通状态下通过而不被截断,并且在关断状态下有效地阻挡信号,因为n-fet和p-fet两者都能够在v

gs

为0伏时完全关断。

[0230]

(f)多级逻辑电路——锁存器和环形振荡器

[0231]

请转到图14a和14b,为了证明在多级逻辑电路中应用本器件的可行性,提供了由在本文中说明的两个交叉耦合的gan cl反相器构成的锁存单元,其中在如这个实例所示的锁存单元中可以存储一位信息。通过间歇地闭合开关

‘

s’,将不同的输入电压加载到锁存单元的节点q。在5伏v

dd

的情况下,由于反相器中的高的噪声容限,即使加载了从静态偏离2伏的输入电压,锁存单元也保持逻辑状态(图14c)。如图14d所示,逻辑状态可以由外部脉冲快速切换,但是保持很长时间。存储数据的能力使得能够实现存储单元(例如静态随机存取存储器(sram))和时序逻辑电路。这个实例的结果表明,本发明适合于使用iii族氮化物(例如gan)来构建有限状态机或微处理器。

[0232]

请转到图15a和15b,其中提供了多级逻辑电路的第二个实例,即,环形振荡器,所述环形振荡器具有级联成环的15级反相器以及布置在环外的用作内部振荡节点的输出缓

冲器的附加反相器。图15c示出了环形振荡器的振荡波形(上图)和对应的功率谱(下图),其中分别示出了1.99微秒的振荡周期和502khz的基频。图15d示出了环形振荡器的每级的基频和功率时延乘积对电源电压(v

dd

)的依赖性。通过增大这种类型的cl门的v

dd

,电路的传输速度提高,但同时牺牲了动态功耗,这不同于常规的dcfl电路,在常规的dcfl电路中,增大v

dd

不一定导致更高的速度。图15e进一步示出了环形振荡器在高达200℃的温度下的温度依赖性,其中环形振荡器在很宽的温度范围内表现出稳定的振荡频率和功率时延乘积,因为本发明的反相器具有令人满意的热稳定性。还制造和表征了由不同数量的反相器组成的更多环形振荡器,如图15f所示。在图15f中,可以用线性拟合来提取每级61纳秒的平均延迟。通过采用本发明的制造方法和界面优化,仍有很大的空间来提高速度,将传播延迟降低到亚纳秒级,以满足功率电子器件在mhz频率下切换的要求。本发明的gan cl反相器在构建cmos环形振荡器中的成功实施表明了本发明在制造基于gan的互补逻辑ic中的实际应用。

[0233]

从本文描述的实例来看,基于本发明提出的结构的单级逻辑反相器和多级逻辑电路表现出了轨到轨操作、显著抑制的静态功耗、恰到好处的转换阈值、具有高电压增益和良好的噪声容限的窄转换窗口、以及良好的热稳定性,这表明本发明适合于在恶劣环境中应用。基于所提出的能够驱动、控制和保护gan器件的gan cl反相器结构的单片集成节能外围电路适合于高频/高功率密度应用或在恶劣环境中应用。

[0234]

虽然本发明是以某些实施例说明的,但是对于本领域普通技术人员来说显而易见的其它实施例也在本发明的范围之内。因此,本发明的范围应仅由所附权利要求限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。