1.本发明涉及压电器件。

背景技术:

2.作为公开压电器件的结构的文献,有国际公开第2019/102951号(专利文献1)。专利文献1中记载的压电器件具备压电单晶体、上部电极、下部电极和支承基板。压电单晶体的极化状态相同。上部电极配置在压电单晶体的上表面上。下部电极配置在压电单晶体的下表面上。支承基板配置在压电单晶体的下方。设置有从支承基板的下表面向压电单晶体的下表面上凹进的凹部。现有技术文献专利文献

3.专利文献1:国际公开第2019/102951号

技术实现要素:

发明要解决的课题

4.专利文献1中记载的压电器件仅具备一层单晶压电体层,在想要增大压电器件的激励时的振幅的情况下,由于从与单晶压电体层正交的方向观察时的单晶压电体层的面积变大,因此压电器件的占有面积变大。

5.此外,在通过蚀刻形成用于与下部电极层电连接的孔部时由于过蚀刻而在下部电极层形成贯通孔的情况下,与下部电极层的电连接变得不充分而使压电器件的激励特性降低。

6.本发明是鉴于上述问题点而完成的,其目的在于,提供一种能够抑制压电器件的占有面积变大以及与下部电极层的电连接变得不充分而使激励特性降低、同时能够增大压电器件的激励时的振幅的压电器件。用于解决课题的技术方案

7.基于本发明的压电器件具备基部和层叠部。基部包括一个主面和位于与一个主面相反的一侧的另一个主面,且具有在一个主面形成的开口部。层叠部层叠在基部的一个主面侧,从上方覆盖开口部。层叠部至少在开口部的上方包括第一单晶压电体层、配置在第一单晶压电体层的上方的第二单晶压电体层、配置在第一单晶压电体层与第二单晶压电体层之间的中间电极层、配置在第一单晶压电体层的下侧并隔着第一单晶压电体层而与中间电极层相对的下部电极层、以及配置在第二单晶压电体层的上侧并隔着第二单晶压电体层而与中间电极层相对的上部电极层,且具有作为覆盖开口部的部分的膜片部。从与上述一个主面正交的方向观察,在层叠部中,在开口部的外侧的位置,形成有贯通第一单晶压电体层、中间电极层及第二单晶压电体层而到达下部电极层的孔部。在上述孔部的内侧设置有引出电极,该引出电极与中间电极层绝缘的同时与下部电极层连接,并且引出到第二单晶压电体层的上表面上。第一单晶压电体层由在极化电荷的正侧和负侧产生蚀刻速率差的材

料构成。第一单晶压电体层的极化电荷在中间电极层侧为正,在下部电极层侧为负。发明的效果

8.根据本发明,能够抑制压电器件的占有面积变大以及由于与下部电极层的连接不良而导致压电器件的激励特性降低,同时能够增大压电器件的激励时的振幅。

附图说明

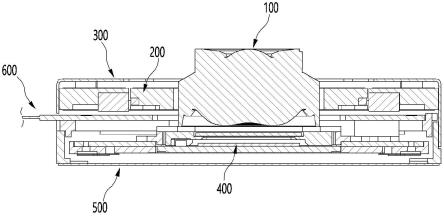

9.图1是本发明的实施方式1涉及的压电器件的纵剖视图。图2是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第一单晶压电体层的下表面设置了下部电极层的状态的剖视图。图3是示出在本发明的实施方式1涉及的压电器件的制造方法中、在下部电极层和第一单晶压电体层各自的下表面设置了中间层的状态的剖视图。图4是示出在本发明的实施方式1涉及的压电器件的制造方法中、拟使基部接合到图3所示的多个层的状态的剖视图。图5是示出在本发明的实施方式1涉及的压电器件的制造方法中、使基部接合于中间层的下表面之后的状态的剖视图。图6是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去第一单晶压电体层的上表面之后的状态的剖视图。图7是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第一单晶压电体层的上表面设置了中间电极层的状态的剖视图。图8是示出在本发明的实施方式1涉及的压电器件的制造方法中、使第二单晶压电体层接合到图7所示的多个层的状态的剖视图。图9是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去第二单晶压电体层的上表面之后的状态的剖视图。图10是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第二单晶压电体层的上表面设置了上部电极层的状态的剖视图。图11是示出在本发明的实施方式1涉及的压电器件的制造方法中、在层叠部形成了孔部的状态的剖视图。图12是示出在本发明的实施方式1涉及的压电器件的制造方法中、在形成于层叠部的孔部的内侧形成了绝缘膜的状态的剖视图。图13是示出在本发明的实施方式1涉及的压电器件的制造方法中、除去了绝缘膜的底部的中央部的状态的剖视图。图14是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了引出电极的状态的剖视图。图15是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了第一引出布线和第二引出布线中的每一个引出布线的状态的剖视图。图16是本发明的实施方式2涉及的压电器件的纵剖视图。

具体实施方式

10.(实施方式1)

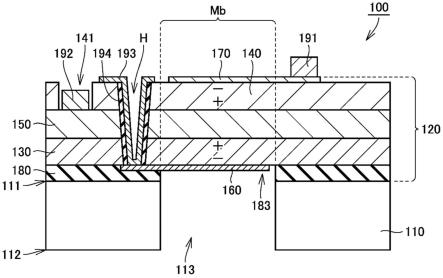

图1是本发明的实施方式1涉及的压电器件的纵剖视图。如图1所示,本发明的实施方式1涉及的压电器件100具备基部110和层叠部120。

11.基部110包括一个主面111和位于与一个主面111相反的一侧的另一个主面112。基部110具有形成在一个主面111的开口部113。在本实施方式中,开口部113从一个主面111贯通至另一个主面112。但是,开口部113也可以从一个主面111侧形成而不到达另一个主面112。或者,开口部113也可以从另一个主面112侧形成到靠近一个主面111的位置,而不到达一个主面111。开口部113被层叠在基部110的一个主面111侧的层叠部120从上方覆盖。

12.在本实施方式中,基部110由si构成。但是,构成基部110的材料并不限定于si。

13.层叠部120至少在开口部113的上方包括第一单晶压电体层130、第二单晶压电体层140、中间电极层150、下部电极层160和上部电极层170。

14.层叠部120具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部120中的位于开口部113的开口端部的内侧的部分。

15.从与一个主面111正交的方向观察,在层叠部120中,在开口部113的外侧的位置,形成有贯通第一单晶压电体层130、中间电极层150及第二单晶压电体层140而到达下部电极层160的孔部h。在孔部h的内周面上形成有绝缘膜194。在孔部h的内侧设置有引出电极193,该引出电极193与中间电极层150绝缘的同时与下部电极层160连接,并且引出到第二单晶压电体层140的上表面上。

16.第一单晶压电体层130位于基部110的上方。第一单晶压电体层130的一部分位于开口部113的上方。第一单晶压电体层130的上表面和下表面各自是平坦的。

17.第二单晶压电体层140位于第一单晶压电体层130的上方。第二单晶压电体层140的一部分位于开口部113的上方。第二单晶压电体层140的上表面和下表面各自是平坦的。

18.第二单晶压电体层140具有孔部141。孔部141上下贯通第二单晶压电体层140。在本实施方式中,孔部141位于基部110的一个主面111的上方,而不位于开口部113的上方。

19.第一单晶压电体层130由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成。第二单晶压电体层140由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成。第二单晶压电体层140可以由与第一单晶压电体层130相同的材料构成,也可以由与第一单晶压电体层130不同的材料构成。

20.在本实施方式中,第一单晶压电体层130和第二单晶压电体层140各自由铌酸锂(linbo3)或者钽酸锂(litao3)构成。另外,第一单晶压电体层130和第二单晶压电体层140各自也可以由k和na以外的其他碱金属的铌酸化合物或钽酸化合物构成。

21.第一单晶压电体层130的极化电荷在中间电极层150侧为正,在下部电极层160侧为负。第二单晶压电体层140的极化电荷在中间电极层150侧为正,在上部电极层170侧为负。另外,第二单晶压电体层140的极化电荷也可以在中间电极层150侧为负,在上部电极层170侧为正。

22.中间电极层150位于第一单晶压电体层130与第二单晶压电体层140之间。中间电极层150被夹在第一单晶压电体层130的上表面与第二单晶压电体层140的下表面之间。中间电极层150的一部分位于开口部113的上方。中间电极层150的上表面和下表面各自是平坦的。中间电极层150也可以通过层叠两层电极层而构成。在本实施方式中,中间电极层150的厚度比下部电极层160和上部电极层170各自的厚度厚。但是,中间电极层150的厚度也可

以在下部电极层160和上部电极层170各自的厚度以下。

23.中间电极层150例如由al或者pt等金属构成。中间电极层150也可以由掺杂有as等的电阻率低的si构成。在该情况下,中间电极层150例如优选由电阻率为20mωcm以下的si构成。或者,中间电极层150也可以由lanio3、srruo3或ruo2等导电性氧化物构成。

24.另外,也可以在中间电极层150与第一单晶压电体层130之间配置有由ti等构成的密接层。也可以在中间电极层150与第二单晶压电体层140之间配置有由ti等构成的密接层。

25.下部电极层160配置在第一单晶压电体层130的下侧,隔着第一单晶压电体层130而与中间电极层150相对。下部电极层160的一部分位于开口部113的上方。下部电极层160的另一部分位于形成在第一单晶压电体层130的孔部h的下方。下部电极层160的另一部分从下方覆盖孔部h。

26.下部电极层160例如由al或者pt等金属构成。下部电极层160也可以由lanio3、srruo3或ruo2等导电性氧化物构成。下部电极层160也可以是通过使导电物外延生长而形成的外延生长膜。

27.上部电极层170配置在第二单晶压电体层140的上侧,隔着第二单晶压电体层140而与中间电极层150相对。上部电极层170的一部分位于开口部113的上方。

28.上部电极层170例如由al或者pt等金属构成。上部电极层170也可以是通过使导电物外延生长而形成的外延生长膜。另外,也可以在上部电极层170与第二单晶压电体层140之间配置有由ti等构成的密接层。

29.引出电极193遍及形成在第二单晶压电体层140的上表面上、绝缘膜194的内周面上、以及通过孔部h露出的下部电极层160的一部分的上表面上。引出电极193例如由al或者pt等金属构成。绝缘膜194例如由sio2等绝缘物构成。

30.层叠部120还具备中间层180。中间层180在与第一单晶压电体层130之间夹着下部电极层160。在中间层180的下表面形成有与基部110的开口部113连通的开口部183。开口部183位于开口部113的上方。通过开口部183,下部电极层160的下表面的一部分露出。通过开口部183露出的下部电极层160的下表面的一部分构成膜片部mb的下表面。

31.中间层180由sio2构成。中间层180的材料并不限定于sio2,只要是绝缘物即可。例如,中间层180也可以由具有电绝缘性和绝热性的有机材料构成。

32.压电器件100还具备第一引出布线191和第二引出布线192。第一引出布线191配置在上部电极层170的上侧。第二引出布线192在孔部141内配置在中间电极层150的上侧。

33.这样,层叠部120至少在开口部113的上方包括第一单晶压电体层130、第二单晶压电体层140、中间电极层150、下部电极层160和上部电极层170。

34.在本实施方式中,从与一个主面111正交的方向观察,开口部113的外形为矩形。但是,从与一个主面111正交的方向观察,开口部113的外形不限于矩形,也可以是矩形以外的多边形或者圆形。

35.根据上述结构,通过在下部电极层160与中间电极层150之间施加电压,第一单晶压电体层130伸缩,并且通过在上部电极层170与中间电极层150之间施加电压,第二单晶压电体层140伸缩,另一方面,上部电极层170、中间电极层150及下部电极层160各自不伸缩,因此膜片部mb上下弯曲振动。

36.以下,对本发明的实施方式1涉及的压电器件的制造方法进行说明。图2是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第一单晶压电体层的下表面设置了下部电极层的状态的剖视图。形成时的第一单晶压电体层130的厚度比本实施方式涉及的压电器件100中最终包括的第一单晶压电体层130的厚度厚。

37.第一单晶压电体层130的极化电荷在上表面侧为正,在下表面侧为负。第一单晶压电体层130由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成。

38.如图2所示,通过剥离(lift-off)法、镀敷法或者蚀刻法等,在第一单晶压电体层130的下表面设置下部电极层160。在下部电极层160由导电性氧化物构成的情况下,通过反应溅射法,将靶中含有的金属氧化后的导电性氧化物在第一单晶压电体层130的下表面上成膜,从而设置下部电极层160。在下部电极层160为外延生长膜的情况下,通过在第一单晶压电体层130的下表面通过异质外延生长形成导电膜,并使导电膜图案化来设置下部电极层160。

39.图3是示出在本发明的实施方式1涉及的压电器件的制造方法中、在下部电极层和第一单晶压电体层各自的下表面设置了中间层的状态的剖视图。如图3所示,通过化学气相沉积(cvd,即chemical vapor deposition)法或者物理气相沉积(pvd,即physical vapor deposition)法等,在下部电极层160和第一单晶压电体层130各自的下表面设置中间层180,之后,通过化学机械研磨(cmp:chemical mechanical polishing)等使中间层180的下表面平坦。

40.图4是示出在本发明的实施方式1涉及的压电器件的制造方法中、拟使基部接合到图3所示的多个层的状态的剖视图。图5是示出在本发明的实施方式1涉及的压电器件的制造方法中、使基部接合于中间层的下表面的状态的剖视图。

41.如图4和图5所示,通过表面活性化接合或者原子扩散接合等,使未形成开口部113的、作为基部110的基板接合于中间层180的下表面。另外,也可以在基部110预先形成有开口部113。

42.图6是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去第一单晶压电体层的上表面之后的状态的剖视图。如图6所示,通过cmp等削去第一单晶压电体层130的上表面,使第一单晶压电体层130变为所希望的厚度。另外,也可以在第一单晶压电体层130的上表面侧预先通过进行离子注入从而形成剥离层。在该情况下,在通过切削或者cmp等削去第一单晶压电体层130的上表面之前,使剥离层剥离,由此第一单晶压电体层130的厚度调整变得容易。第一单晶压电体层130的厚度被调整为可获得电压的施加所引起的第一单晶压电体层130的所希望的激励。

43.图7是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第一单晶压电体层的上表面设置了中间电极层的状态的剖视图。如图7所示,通过剥离法、镀敷法或者蚀刻法等,在第一单晶压电体层130的上表面设置中间电极层150。

44.在中间电极层150由电阻率低的si构成的情况下,通过表面活性化接合或者原子扩散接合等,将掺杂有as等的si基板接合到第一单晶压电体层130的上表面,之后,通过cmp等削去si基板的上表面,使其变为所希望的厚度。另外,也可以在si基板的上表面侧预先通过进行离子注入从而形成剥离层。在该情况下,在通过切削或者cmp等削去si基板的上表面之前,使剥离层剥离,由此si基板的厚度调整变得容易。在中间电极层150由导电性氧化物

构成的情况下,通过反应溅射法,将靶中含有的金属氧化后的导电性氧化物在第一单晶压电体层130的上表面上成膜,从而设置中间电极层150。

45.图8是示出在本发明的实施方式1涉及的压电器件的制造方法中、使第二单晶压电体层接合到图7所示的多个层的状态的剖视图。如图8所示,通过表面活性化接合或者原子扩散接合等,使第二单晶压电体层140接合于中间电极层150的上表面。形成时的第二单晶压电体层140的厚度比本实施方式涉及的压电器件100中最终包括的第二单晶压电体层140的厚度厚。

46.在本实施方式中,第二单晶压电体层140的极化电荷在上表面侧为负,在下表面侧为正。第二单晶压电体层140由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成。

47.图9是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去第二单晶压电体层的上表面之后的状态的剖视图。如图9所示,通过cmp等削去第二单晶压电体层140的上表面,使第二单晶压电体层140变为所希望的厚度。另外,也可以在第二单晶压电体层140的上表面侧预先通过进行离子注入从而形成剥离层。在该情况下,在通过切削或者cmp等削去第二单晶压电体层140的上表面之前,使剥离层剥离,由此第二单晶压电体层140的厚度调整变得容易。第二单晶压电体层140的厚度被调整为可获得电压的施加所引起的第二单晶压电体层140的所希望的激励。

48.图10是示出在本发明的实施方式1涉及的压电器件的制造方法中、在第二单晶压电体层的上表面设置了上部电极层的状态的剖视图。如图10所示,通过剥离法、镀敷法或者蚀刻法等,在第二单晶压电体层140的上表面设置上部电极层170。在上部电极层170为外延生长膜的情况下,通过在第二单晶压电体层140的上表面通过异质外延生长形成导电膜,并使导电膜图案化来设置上部电极层170。

49.图11是示出在本发明的实施方式1涉及的压电器件的制造方法中、在层叠部形成了孔部的状态的剖视图。如图11所示,通过蚀刻法,形成贯通第一单晶压电体层130、中间电极层150及第二单晶压电体层140而到达下部电极层160的孔部h。此外,通过蚀刻法,形成贯通第二单晶压电体层140而到达中间电极层150的孔部141。

50.孔部h和孔部141各自通过从第二单晶压电体层140的上表面侧蚀刻而形成。第二单晶压电体层140由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成,从极化电荷的负侧进行蚀刻的情况下的蚀刻速率,比从极化电荷的正侧进行蚀刻的情况下的蚀刻速率高。由于第二单晶压电体层140的极化电荷在上表面侧为负,在下表面侧为正,因此,通过从第二单晶压电体层140的上表面侧进行蚀刻,能够以高蚀刻速率对第二单晶压电体层140进行蚀刻。

51.在本实施方式中,由于中间电极层150的厚度比下部电极层160和上部电极层170各自的厚度厚,因此,能够抑制由于过蚀刻而使孔部141贯通中间电极层150。

52.在孔部h贯通中间电极层150之后,第一单晶压电体层130从上表面侧被蚀刻。第一单晶压电体层130由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成,从极化电荷的正侧进行蚀刻的情况下的蚀刻速率,比从极化电荷的负侧进行蚀刻的情况下的蚀刻速率低。由于第一单晶压电体层130的极化电荷在上表面侧为正,在下表面侧为负,因此,通过从第一单晶压电体层130的上表面侧进行蚀刻,能够以低蚀刻速率对第一单晶压电体层130进行蚀刻。由此,能够抑制由于过蚀刻而使孔部h贯通下部电极层160。

53.图12是示出在本发明的实施方式1涉及的压电器件的制造方法中、在形成于层叠部的孔部的内侧形成了绝缘膜的状态的剖视图。如图12所示,通过溅射法或者cvd法等,在孔部h的内侧形成绝缘膜194。

54.图13是示出在本发明的实施方式1涉及的压电器件的制造方法中、除去了绝缘膜的底部的中央部的状态的剖视图。如图13所示,通过蚀刻法,留下绝缘膜194中位于孔部h的内周面上的部分,同时除去绝缘膜194的底部的中央部,由此使下部电极层160的一部分露出。

55.图14是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了引出电极的状态的剖视图。如图14所示,通过溅射法、蒸镀法或者镀敷法等,遍及形成在第二单晶压电体层140的上表面上、绝缘膜194的内周面上、以及通过孔部h露出的下部电极层160的一部分的上表面上。

56.图15是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了第一引出布线和第二引出布线中的每一个引出布线的状态的剖视图。如图15所示,通过剥离法、镀敷法或者蒸镀法等,在上部电极层170的上表面上形成第一引出布线191,在通过孔部141露出的中间电极层150的一部分的上表面上形成第二引出布线192。

57.最后,通过蚀刻法,在基部110形成开口部113,并且在中间层180形成开口部183。另外,未必一定要形成开口部183。通过上述工序,制造如图1所示的本发明的实施方式1涉及的压电器件100。

58.在本发明的实施方式1涉及的压电器件100中,具备膜片部mb,该膜片部mb具有夹在中间电极层150与下部电极层160之间的第一单晶压电体层130、以及夹在中间电极层150与上部电极层170之间的第二单晶压电体层140这两层单晶压电体层,由此,与压电器件仅具备一层单晶压电体层的情况相比,能够在不增大单晶压电体层的面积的情况下增大压电器件的激励时的振幅。其结果是,能够在抑制压电器件100的占有面积变大的同时增大压电器件100的激励时的振幅。

59.在本发明的实施方式1涉及的压电器件100中,第一单晶压电体层130由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成,第一单晶压电体层130的极化电荷在中间电极层150侧为正、在下部电极层160侧为负,由此,在通过蚀刻形成用于与下部电极层160电连接的孔部h时,能够以低蚀刻速率对第一单晶压电体层130进行蚀刻,因此能够抑制由于过蚀刻而在下部电极层160形成贯通孔。其结果是,能够抑制与下部电极层160的电连接变得不充分而使压电器件100的激励特性降低。

60.在本发明的实施方式1涉及的压电器件100中,中间电极层150的厚度比下部电极层160和上部电极层170各自的厚度厚。由此,能够抑制在通过蚀刻形成孔部141时由于过蚀刻而在中间电极层150形成贯通孔。其结果是,能够抑制中间电极层150与第二引出布线192的电连接变得不充分而使压电器件100的激励特性降低。

61.在本发明的实施方式1涉及的压电器件100中,中间电极层150也可以由si构成。在该情况下,由于si结晶稳定,因此不与第一单晶压电体层130和第二单晶压电体层140的每一个压电体层反应,因而能够抑制由于与第一单晶压电体层130和第二单晶压电体层140的每一个压电体层的相互反应而使第一单晶压电体层130和第二单晶压电体层140各自的特性劣化。

62.在本发明的实施方式1涉及的压电器件100中,由于第二单晶压电体层140由在极化电荷的正侧和负侧产生蚀刻速率差的材料构成,第二单晶压电体层140的极化电荷在中间电极层150侧为正、在上部电极层170侧为负,因此通过从第二单晶压电体层140的上表面侧进行蚀刻,能够以高蚀刻速率对第二单晶压电体层140进行蚀刻。其结果是,能够缩短第二单晶压电体层140的蚀刻所需要的时间。

63.在本发明的实施方式1涉及的压电器件100中,第一单晶压电体层130和第二单晶压电体层140各自由k和na以外的碱金属的铌酸化合物或钽酸化合物构成,不含铅,因此能够减轻对环境造成的负担。第一单晶压电体层130和第二单晶压电体层140各自由铌酸锂(linbo3)或者钽酸锂(litao3)构成,由此能够提高压电器件100的压电特性。

64.在本发明的实施方式1涉及的压电器件100中,下部电极层160和中间电极层150中的至少一者也可以由导电性氧化物构成。在下部电极层160由导电性氧化物构成的情况下,在对第一单晶压电体层130进行干式蚀刻而形成孔部h时,增大第一单晶压电体层130与下部电极层160的蚀刻选择比,能够抑制由于过蚀刻而在下部电极层160形成贯通孔。在中间电极层150由导电性氧化物构成的情况下,在对第二单晶压电体层140进行干式蚀刻而形成孔部141时,增大第二单晶压电体层140与中间电极层150的蚀刻选择比,能够抑制由于过蚀刻而在中间电极层150形成贯通孔。

65.在本发明的实施方式1涉及的压电器件100中,下部电极层160及上部电极层170中的至少一者可以是外延生长膜。外延生长膜的结晶性良好,因此能够抑制迁移的发生,能够提高下部电极层160和上部电极层170各自的耐功率特性。

66.(实施方式2)以下,参照附图对本发明的实施方式2涉及的压电器件进行说明。本发明的实施方式2涉及的压电器件与本发明的实施方式1涉及的压电器件100的不同点仅在于,设置有增强用下部电极层,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

67.图16是本发明的实施方式2涉及的压电器件的纵剖视图。如图16所示,在本发明的实施方式2涉及的压电器件200中,在下部电极层160中的位于孔部h的下方的部分的下侧设置有增强用下部电极层260。

68.增强用下部电极层260例如由al或者pt等金属构成。增强用下部电极层260也可以由lanio3、srruo3或ruo2等导电性氧化物构成。增强用下部电极层260也可以是通过使导电物外延生长而形成的外延生长膜。

69.具体地,通过剥离法、镀敷法或者蚀刻法等,在下部电极层160的下表面设置增强用下部电极层260。在增强用下部电极层260由导电性氧化物构成的情况下,通过反应溅射法,将靶中含有的金属氧化后的导电性氧化物在下部电极层160的下表面上成膜,从而设置增强用下部电极层260。在增强用下部电极层260为外延生长膜的情况下,通过在下部电极层160的下表面通过同质外延生长形成导电膜,并使导电膜图案化来设置增强用下部电极层260。

70.在本发明的实施方式2涉及的压电器件200中,通过在下部电极层160中的位于孔部h的下方的部分的下侧设置增强用下部电极层260,能够抑制在通过蚀刻形成孔部h时由于过蚀刻而在下部电极层160和增强用下部电极层260形成贯通孔。

71.此外,在通过使下部电极层160整体变厚来防止由过蚀刻引起的贯通孔的形成的情况下,由于在下部电极层160产生的应力而在膜片部mb发生翘曲,压电器件的激励特性降低,但通过仅在下部电极层160中的位于孔部h的下方的部分的下侧设置增强用下部电极层260,能够抑制由于膜片部mb的翘曲而导致压电器件200的激励特性降低。

72.在上述实施方式的说明中,也可以将能够组合的结构相互组合。

73.应认为本次公开的实施方式在所有方面均为例示而不是限制性的。本发明的范围不是由上述的说明示出,而是由权利要求书示出,其意图包含与权利要求书等同的含义以及范围内的所有变更。附图标记说明

74.100、200:压电器件,110:基部,111、112:主面,113、183:开口部,120:层叠部,130:第一单晶压电体层,140:第二单晶压电体层,141、h:孔部,150:中间电极层,160:下部电极层,170:上部电极层,180:中间层,191:第一引出布线,192:第二引出布线,193:引出电极,194:绝缘膜,260:增强用下部电极层,mb:膜片部。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。