电力轨入界线中部(mol)布线

1.相关申请的交叉引用

2.本技术是国际申请日为2016年10月11日、国际申请号pct/us2016/056472、于2018年5月7日进入中国国家阶段、中国国家申请号201680064949.5、发明名称为“电力轨入界线中部(mol)布线”的发明专利申请的分案申请。

技术领域

3.本公开的各方面一般地涉及在管芯上布线,并且更特别地涉及在管芯上的线中部(mol)布线。

背景技术:

4.半导体管芯可以包括许多半导体器件(例如,晶体管)。半导体器件可以通过一个或多个金属层被互连以形成集成电路。随着器件尺寸缩小,管芯上的布线拥塞增加,而使得互连管芯上的器件更加困难。

技术实现要素:

5.以下提出一个或多个实施例的简化概述以便提供对这样的实施例的基本理解。本概述不是所有被设想到的实施例的广泛概览,并且既不意图标识所有实施例的关键或重要元素,也不意图界定任何或全部实施例的范围。其唯一目的是以简化形式提出一个或多个实施例的一些概念,作为稍后提出的更详细描述的序言。

6.根据一方面,提供了一种半导体管芯。该半导体管芯包括电力轨、第一栅极和第二栅极。该半导体管芯还包括:电耦合到第一栅极的第一栅极接触部,其中第一栅极接触部由第一线中部(mol)金属层形成;以及电耦合到第二栅极的第二栅极接触部,其中第二栅极接触部由第一mol金属层形成。该半导体管芯进一步包括由第二mol金属层形成的互连部,其中互连部电耦合到第一和第二栅极接触部,并且互连部的至少一部分在电力轨下方。

7.第二方面涉及一种半导体管芯。该半导体管芯包括电力轨、栅极和源极。该半导体管芯还包括电耦合到栅极的栅极接触部,其中栅极接触部由第一线中部(mol)金属层形成。该半导体管芯还包括由第二mol金属层形成的互连部,其中互连部电耦合到栅极接触部和源极,并且互连部的至少一部分在电力轨下方。

8.第三方面涉及一种半导体管芯。该半导体管芯包括电力轨、第一单元和第二单元,第一单元包括第一多个栅极和第一多个源极/漏极,第二单元包括第二多个栅极和第二多个源极/漏极。该半导体单元还包括:电耦合到第一多个栅极中的一个栅极的第一栅极接触部,其中第一栅极接触部由第一线中部(mol)金属层形成;以及电耦合到第二多个栅极中的一个栅极的第二栅极接触部,其中第二栅极接触部由第一mol金属层形成。该半导体管芯还包括由第二mol金属层形成的互连部,其中互连部电耦合到第一和第二栅极接触部,并且在电力轨下方被布线。

附图说明

9.图1示出了根据本公开的某些方面的示例性半导体管芯的侧视图。

10.图2示出了根据本公开的某些方面的用于将栅极耦合到金属层的示例性结构的侧视图。

11.图3示出了根据本公开的某些方面的用于将源极/漏极耦合到金属层的示例性结构的侧视图。

12.图4示出了根据本公开的某些方面的示例性半导体管芯的顶视图。

13.图5示出了根据本公开的某些方面的由金属层m1形成的示例性局部互连部。

14.图6a和图6b示出了根据本公开的某些方面的图5中的示例性局部互连部的侧视图。

15.图7示出了根据本公开的某些方面的由金属层m1形成并且用于在单元之间布线的示例性互连部的顶视图。

16.图8a和图8b示出了根据本公开的某些方面的在金属m1电力轨之下提供布线的示例性互连部的顶视图。

17.图9示出了根据本公开的某些方面的图8a和图8b中的互连部的侧视图。

18.图10a和图10b示出了根据本公开的某些方面的在金属m1电力轨之下提供布线的另一示例性互连部的顶视图。

19.图11示出了根据本公开的某些方面的图10a和图10b中的互连部的侧视图。

20.图12示出了根据本公开的某些方面的多个晶体管的电路图,其中晶体管的源极和栅极被结扎以提供电屏障。

21.图13a和图13b示出了根据本公开的某些方面的用于实施图12中的电路的在金属m1电力轨之下的互连部的顶视图。

22.图14示出了根据本公开的某些方面的图13a和图13b中的互连部的侧视图。

具体实施方式

23.下面关于附图阐述的详细描述意图作为对各种配置的描述,并且不意图表示本文描述的概念可以被实践在其中的仅有配置。该详细描述包括具体细节用于提供对各种概念的透彻理解的目的。然而,对本领域的技术人员将明显的是,这些概念可以没有这些具体细节而被实践。在一些情况下,公知的结构和组件以框图形式示出,以便避免使这样的概念模糊不清。

24.图1示出了半导体管芯(芯片)110的简化示例。半导体管芯110包括多个互连金属层,其中相邻的互连金属层由一个或多个绝缘层分开。不同的互连金属层可以使用过孔和/或其他结构被互连,它们为了说明的简便性未在图1中示出。最底部的互连金属层被标记为m1。紧接在互连金属层m1上方的互连金属层被标记为m2,紧接在金属层m2上方的互连金属层被标记为m3,等等。在这个示例中,半导体管芯110包括被标记为m1-m9的九个互连金属层。

25.互连金属层m1-m9用于将管芯的各种组件耦合到彼此,耦合到一个或多个管芯外的器件,和/或耦合到一个或多个电力供应。通常,如下面进一步论述的,金属层m1形成在管芯上的半导体器件(例如,晶体管)之上,并且使用接触结构耦合到半导体器件。金属层m1可

以用来为管芯上的半导体器件提供电力轨,将管芯上的半导体器件耦合到彼此,和/或将管芯上的半导体器件耦合到较高金属层。在这点上,图1示出了在金属层m1之下的晶体管120(例如,场效应晶体管)的示例。在金属m1-m9被沉积在晶体管120之上之前,晶体管120被形成在管芯的衬底150上。晶体管120包括栅极130、第一源极/漏极140a、以及第二源极/漏极140b。栅极130可以包括多晶硅和/或其他材料。如本文使用的,术语“源极/漏极”指示对应的结构可以充当源极或漏极。尽管为了说明的简便性而在图1中示出了一个晶体管120,但是将明白,半导体管芯110包括许多晶体管。还将明白,图1没有按比例绘制,并且金属层m1-m9的厚度和相邻金属层之间的空间可以在管芯上变化。

26.晶体管120可以使用平面工艺或finfet工艺被形成在管芯上。图1示出了晶体管120使用平面工艺被形成的示例。在这个示例中,晶体管120包括在晶体管的栅极与沟道之间的栅极电介质145(例如,栅极氧化物)。对于使用finfet工艺形成的晶体管(未示出),晶体管可以包括在第一源极/漏极与第二源极/漏极之间的用以形成晶体管的沟道的一个或多个鳍、以及形成在鳍之上的栅极。在任一种情况下,晶体管包括栅极、第一源极/漏极、以及第二源极/漏极。因此,将明白,本公开的各方面适用于使用平面工艺和finfet工艺形成的晶体管。

27.图2示出了用于将晶体管(例如,晶体管120)的栅极230耦合到金属层m1的示例性接触结构250。在这个示例中,接触结构250设置在栅极230与金属层m1之间,并且将栅极230电耦合到金属层m1。接触结构250包括由第一线中部(mol)金属层(在图2中标记为“cb”)形成的栅极接触部252。如本文使用的,术语“mol”是指在金属层m1之下的层。第一mol金属层(cb)可以包括钨、铜和/或其他导电材料。如图2中示出的,栅极接触部252可以与栅极230的顶部接触。接触结构250还包括栅极接触部252与金属层m1之间设置的过孔255。过孔255将栅极接触部252电耦合到金属层m1。

28.图3示出了用于将晶体管(例如,晶体管120)的源极/漏极340耦合到金属层m1的示例性接触结构350。在这个示例中,接触结构350设置在源极/漏极340与金属层m1之间,并且将源极/漏极电耦合到金属层m1。接触结构350包括在源极/漏极340的顶部上形成的第一源极/漏极接触部352。第一源极/漏极接触部352可以由沟槽硅化物(ts)层形成。在这个示例中,第一源极/漏极接触部352可以通过在电介质材料中蚀刻沟槽并且利用硅化物材料填充沟槽而被形成。接触结构350还包括由第二mol金属层(在图3中标记为“ca”)形成的第二源极/漏极接触部355。第二mol金属层(ca)可以包括钨、铜和/或其他导电材料。在图2中的示例中,第二源极/漏极接触部355堆叠在第一源极/漏极接触部352的顶部上。接触结构350进一步包括第二源极/漏极接触部355与金属层m1之间设置的过孔357。过孔357将第二源极/漏极接触部355电耦合到金属层m1。图2和图3中的过孔255和过孔357可以由相同的导电层形成。

29.因此,第一和第二mol金属层(cb和ca)常规地用于将栅极和源极/漏极分别耦合到金属层m1和/或其他更上方的金属层。第一和第二mol金属层(cb和ca)常规地不用于形成全局特征。如本文使用的,“全局特征”可以指代由多个单元共享的结构。如下面进一步论述的,全局特征的示例是由金属层m1形成的电力轨。

30.图4示出了金属层m2-m9为了说明的简便性而被移除的管芯110的示例性顶视图。在这个示例中,管芯110包括由金属层m1形成的第一电力轨410、由金属层m1形成的第二电

力轨412、以及由金属层m1形成的第三电力轨414。电力轨412可以使用本领域已知的任何金属蚀刻工艺由金属层m1形成。第一和第三电力轨410和414可以具有供应电压vdd,并且第二电力轨412可以具有供应电压vss,其中vdd可以是正电压并且vdd可以近似为零伏(例如,接地)或低于vdd的另一电压。替换地,第一和第三电力轨410和414可以具有供应电压vss,并且第二电力轨412可以具有供应电压vdd。将明白,电力轨410、412和414中的每个可以比图4中示出的更长。在图4中,电力轨410、412和414之下的结构以虚线示出。

31.管芯包括第一单元450和第二单元455。在图4中的示例中,第一单元450与第二单元455之间的边界位于第二电力轨412之下,但是将明白,情况不需要如此。将明白,管芯可以包括比图4中示出的更多的单元。

32.第一单元450包括多个栅极420a-420f(例如,多晶硅栅极)和多个源极/漏极430a-430j,它们形成第一单元450内的多个晶体管。在这点上,图4示出了由栅极420b、源极/漏极430a和源极/漏极430b形成的晶体管460的示例。在图4中的示例中,栅极420a-420f被延长并且与相邻栅极之间的一个或多个源极/漏极平行布置。对于栅极420a-420f包括多晶硅的示例,栅极可以被称为多晶导体(pc)。

33.第一单元450内的晶体管可以通过局部互连部(图4中未示出)互连,以形成执行一个或多个功能的集成电路。例如,晶体管可以被互连以形成执行逻辑功能的电路(“与”门、“或”门、“异或”门等)、执行存储功能的电路(触发器、锁存器等)、执行复用功能的电路(例如,复用器)等。如上面论述的,第一单元450内的晶体管可以由提供电压vdd和vss的第一和第二电力轨410和412来供电。在这点上,第一单元450内的晶体管中的一个或多个晶体管可以通过一个或多个接触结构(例如,图2和图3中示出的接触结构250和350)耦合到电力轨。

34.第二单元455包括多个栅极420b-420d、420g、420h和420i(例如,多晶硅栅极)和多个源极/漏极430k-430t,它们形成第二单元455内的多个晶体管。在图4中示出的示例中,第一单元450中的栅极420b-420d在第二电力轨412下方延伸到第二单元455中。在图4中的示例中,栅极420b-420d、420g、420h和420i被延长并且与相邻栅极之间的一个或多个源极/漏极平行布置。

35.第二单元455内的晶体管可以通过局部互连部(图4中未示出)互连,以形成执行一个或多个功能(例如,上面论述的功能中的任何功能)的集成电路。如上面论述的,第二单元455内的晶体管可以由提供电压vdd和vss的第二和第三电力轨412和414来供电。在这点上,第二单元455内的晶体管中的一个或多个晶体管可以通过一个或多个接触结构(例如,图2和图3中示出的接触结构250和350)耦合到电力轨。

36.如上面论述的,单元中的晶体管可以被互连以形成电路。在这点上,图5示出了第一单元450中的第一局部互连部510和第二局部互连部550的示例,其中每个局部互连部由金属层m1形成。为了说明的简便性,从图5中省略了图4中示出的用于源极/漏极430a-430t的参考标号。

37.在这个示例中,第一局部互连部510耦合栅极420d和420e,其中第一局部互连部510通过第一接触结构520耦合到栅极420d,并且通过第二接触结构525耦合到栅极420e。在这点上,图6a示出了第一局部互连部510的侧视图,其中第一接触结构520包括第一栅极接触部652a和第一过孔655a,并且第二接触结构520包括第二栅极接触部652b和第二过孔655b。

38.返回到图5,第二局部互连部550耦合栅极420b和源极/漏极430b,其中第二局部互连部550通过第三接触结构555耦合到栅极420d,并且通过第四接触结构560耦合到源极/漏极430b。在这点上,图6b示出了第二局部互连部550的侧视图,其中第三接触结构555包括栅极接触部662和第一过孔665,并且第四接触结构560包括第一源极/漏极接触部672(例如,ts)、第二源极/漏极接触部675、以及第二过孔678。

39.一般而言,金属层m1可以用于形成局部互连部,它们互连栅极、将一个或多个栅极互连到一个或多个源极/漏极、互连源极/漏极,等等。因此,金属层m1可以被图案化以形成局部互连部,它们互连单元中的晶体管以形成电路。如下面进一步论述的,金属层m1也可以用于形成两个或更多单元之间的全局互连部。

40.图7示出了一种示例,其中金属层m1用来形成互连部710,互连部710耦合第一和第二单元450和455中的晶体管。在这个示例中,互连部710通过第一接触结构720耦合到第一单元450中的栅极420b,并且通过第二接触结构725耦合到第二单元455中的栅极420d。第一和第二接触结构720和725中的每个可以包括图2中示出的接触结构250。如图7中示出的,互连部710提供第一单元450与第二单元455之间的布线。因此,金属层m1可以用于局部布线和全局布线两者。

41.然而,使用金属层m1用于互连部710的缺点是,如图7中示出的,它要求第二电力轨412中的中断以穿过第二电力轨412。这是因为互连部710和第二电力轨412由相同的金属层(即,金属层m1)形成。在图7中的示例中,第二电力轨412被中断为第一部分412a和第二部分412b以容纳互连部710。电力轨中的中断引起电力完整性劣化,这可能使得时间敏感电路出故障。电力完整性劣化可以包括电力网络中的增大的ir压降、和/或电磁发射。另一缺点是,互连部710占据显著的面积,引起金属布线拥塞。

42.一般而言,金属层m1布线在它与由金属层m1形成的结构(诸如,电力轨,例如第二电力轨412)冲突时被限制。在这种情况下,金属层m1布线必须绕过该结构被布线(这在许多情况下也许是不可能的),或者该结构必须被中断以允许金属层m1布线穿过(这可能引起上面论述的问题中的一个或多个问题)。

43.如下面进一步论述的,本公开的各方面提供了使用第一和第二mol金属层(ca和cb)的布线,其避免了上述缺点中的一个或多个缺点。

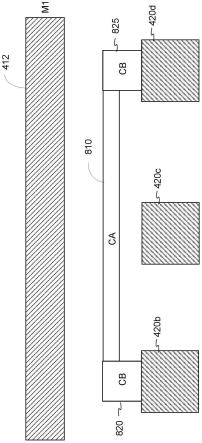

44.图8a和图8b示出了根据本公开的某些方面的示例性互连部810的顶视图。图8a示出了与第二电力轨412一起的互连部810,并且图8b示出了第二电力轨412被移除以提供互连部810的无障碍视图的互连部810。图9示出了互连部810的侧视图。

45.互连部810提供在第二电力轨412下方在栅极420b与栅极420d之间的布线。互连部810由第二mol金属层(ca)形成,如上文论述的,其是用于形成源极/漏极接触部(例如,源极/漏极接触部355)的相同金属层。如图9中示出的,互连部810在分别在栅极420b和420d上的栅极接触部820和825之间延伸并且与之接触。在这方面,互连部810充当栅极接触部820和825之间的电桥。在图9中的示例中,互连部810与栅极接触部820和825的侧壁接触。

46.因此,互连部810(其由第二mol金属层(ca)形成)以及栅极接触部820和825(它们由第一mol金属层(cb)形成)电耦合栅极420b和420d。由于第一mol金属层(ca)和第二mol金属层(cb)形成在比金属层m1低的水平面,所以互连部810以及栅极接触部820和825能够在第二电力轨412之下提供栅极420b和420d之间的布线。因此,不需要中断第二电力轨412。如

图8a和图9中示出的,第二电力轨412是连续的而没有中断。进一步地,由于互连部810以及栅极接触部820和825在金属层m1下方,所以它们不干扰金属层m1,并且因此减少了布线拥塞。作为结果,面积效率被提高。

47.因此,本公开的各方面使用第一和第二mol金属层(cb和ca)来提供mol布线(例如,在晶体管之间)。由于第一和第二mol金属层(cb和ca)形成在比金属层m1低的水平面,所以mol布线不受制于与金属层m1布线相同的限制。例如,mol布线可以在由金属层m1形成的结构(例如,电力轨)下方穿过,而不要求结构中的中断。相比之下,当金属层m1布线与金属层m1结构(例如,电力轨)冲突时,金属层m1布线必须绕过该结构被布线(这在许多情况下也许是不可能的),或者该结构必须被中断以允许金属层m1布线穿过。因此,根据本公开的各方面的mol布线可以有利地在使用金属层m1的布线将高度受限的情况下被使用。

48.尽管未在图8a和图8b中明确示出,但是将明白,管芯还可以包括局部互连部(例如,如图5中示出的局部互连部510和550)用于互连第一单元450和第二单元455中的晶体管以形成集成电路。

49.图10a和图10b示出了根据本公开的某些方面的另一示例性互连部1010的顶视图。图10a示出了与第二电力轨412一起的互连部1010,并且图10b示出了第二电力轨412被移除以提供互连部1010的无障碍视图的互连部1010。图11示出了互连部1010的侧视图。

50.在这个示例中,图8中的栅极420b被中断为第一单元450中的栅极420b-1和第二单元455中的栅极420b-2,图8中的栅极420c被中断为第一单元450中的栅极420c-1和第二单元455中的栅极420c-2,并且图8中的栅极420d被中断为第一单元450中的栅极420d-1和第二单元455中的栅极420d-2。

51.在这个示例中,互连部1010在第二电力轨412下方提供栅极420b-1与栅极420d-2之间的布线。互连部1010由第二mol金属层(ca)形成,如上面论述的,其是用于形成源极/漏极接触部(例如,源极/漏极接触部355)的相同金属层。如图11中示出的,互连部1010在分别在栅极420b-1和420d-2上的栅极接触部1020和1025之间延伸并且与之接触。在这方面,互连部1010充当栅极接触部1020和1025之间的电桥。

52.因此,互连部1010(其由第二mol金属层(ca)形成)以及栅极接触部1020和1025(它们由第一mol金属层(cb)形成)提供第一单元450中的栅极420b-1与第二单元中的420d-2之间的布线。在图11中的示例中,互连部1010与栅极接触部1020和1025的侧壁接触。由于第一mol金属层(ca)和第二mol金属层(cb)形成在比金属层m1低的水平面,所以互连部1010以及栅极接触部1020和1025能够在第二电力轨412之下提供布线。

53.将明白,本公开的各方面不限于所论述的特定示例。一般地,本公开的各方面使用由第二mol金属层(ca)形成的互连部在金属m1电力轨(例如,电力轨412)之下提供单元之间的布线。例如,互连部可以通过以下而将一个单元中的第一栅极耦合到另一单元中的第二栅极:在第一和第二栅极上的栅极接触部之间延伸并且与之接触,其中栅极接触部可以由第一mol金属层(cb)形成。在这方面,互连部充当栅极接触部之间的电桥。由于第二mol金属层(ca)形成在比金属层m1低的水平面,所以互连部能够在金属m1电力轨下方通过,并且因此不要求金属m1电力轨中的中断。

54.在某些方面,一个或多个晶体管可以被结扎(tie off)以在半导体器件(晶体管)之间提供电隔离。在这些方面,晶体管通过以下被结扎:将晶体管的源极和栅极耦合在一

起。这永久地关断晶体管,而允许晶体管充当在晶体管的相对侧的半导体器件之间的电屏障。

55.在这点上,图12是电路图,其图示了晶体管m1-m4被结扎以在节点1205、1210、1215和1220之间提供电隔离的示例。在这个示例中,晶体管m1-m4的栅极g1-g4和源极s1-s4都连结到节点1230,节点1230耦合到供应电压vdd。这有效地关断晶体管m1-m4,而在节点1205、1210、1215和1220(它们可以对应于晶体管m1-m4的漏极d1-d4)之间提供电屏障。作为结果,耦合到节点1205、1210、1215和1220之一的器件(例如,晶体管)与其他节点1205、1210、1215和1220电隔离。在图12中的示例中,晶体管m1-m4是p型场效应晶体管(pfet)。然而,将明白,晶体管m1-m4可以利用n型场效应晶体管(nfet)来替代,并且nfet的栅极和源极被连结到接地。

56.图13a和图13b示出了示例性互连部1310的顶视图,示例性互连部1310在第二电力轨412下方提供布线用于实施图12中示出的示例性电路。图13a示出了与第二电力轨412一起的互连部1310,并且图13b示出了第二电力轨412被移除以提供互连部1310的无障碍视图的互连部1310。图14示出了互连部1310的侧视图。如下面进一步论述的,互连部1310可以由第二mol金属层(ca)形成。

57.在这个示例中,栅极420c和源极/漏极430h可以提供晶体管m1的栅极g1和源极s1,栅极420c和源极/漏极430m可以提供晶体管m2的栅极g2和源极s2,栅极420d和源极/漏极430h可以提供晶体管m3的栅极g3和源极s3,并且栅极420d和源极/漏极430m可以提供晶体管m4的栅极g4和源极s4。因此,栅极420c可以为晶体管m1和m2两者提供栅极g1和g2,并且栅极420可以为晶体管m3和m4两者提供栅极g3和g4。类似地,源极/漏极430h可以为晶体管m1和m3两者提供源极s1和s3,并且源极/漏极430m可以为晶体管m2和m4两者提供源极s2和s4。源极/漏极430g、430l、430i和430n可以分别提供晶体管m1-m4的漏极d1-d4。

58.在这个示例中,互连部1310在分别在栅极420c和420d上的栅极接触部1320和1325之间延伸并且与之接触。作为结果,互连部1310以及栅极接触部1320和1325将晶体管m1-m4的栅极g1-g4耦合在一起。在图14中示出的示例中,互连部1310与栅极接触部1320和1325的侧壁接触。

59.互连部1310还耦合到源极/漏极430h和源极/漏极430m。在这个示例中,互连部1310通过互连部1310与源极/漏极430h之间设置的源极/漏极接触部1340(例如,ts源极/漏极接触部)耦合到源极/漏极430,并且通过互连部1310与源极/漏极430m之间设置的源极/漏极接触部1342(例如,ts源极/漏极接触部)耦合到源极/漏极430m。在图14中示出的示例中,互连部1310与源极/漏极接触部1340和1342(例如,ts源极/漏极接触部)的顶部接触。

60.因此,互连部1310将晶体管m1-m4的栅极g1-g4耦合在一起,并且将晶体管m1-m4的源极s1-s4耦合在一起。作为结果,晶体管m1-m4的栅极g1-g4和源极s1-s4全部耦合在一起。

61.互连部1310还通过互连部1310与第二电力轨412之间设置的过孔1350耦合到第二电力轨412。在一个示例中,第二电力轨412提供供应电压vdd,并且晶体管m1-m4是pfet。作为结果,在这个示例中,晶体管m1-m4的栅极g1-g4和源极s1-s4连结到vdd。这有效地关断晶体管m1-m4,而在第一单元450与第二单元455之间,并且更特别地是在源极/漏极430g、430l、430i和430n之间提供电屏障。

62.因此,互连部1310(其由第二mol金属层(ca)形成)在第二电力供应412之下提供布

线,用于结扎晶体管m1-m4以形成电屏障。将明白,本公开的各方面不限于图12-图14中示出的示例。一般地,本公开的各方面可以通过使用由第二mol金属层(ca)形成的互连部来结扎一个或多个晶体管,其中互连部耦合到每个晶体管的栅极和源极。互连部还可以通过互连部与电力轨之间的过孔耦合到金属m1电力轨。对于一个或多个晶体管是pfet的示例,电力轨可以提供供应电压vdd。对于一个或多个晶体管是nfet的示例,电力轨可以提供供应电压vss。

63.本公开的先前描述被提供以使得本领域的任何技术人员能够制作或使用本公开。对本公开的各种修改对本领域的技术人员将容易是明显的,并且本文定义的一般原理可以应用于其他变型而不偏离本公开的精神或范围。因此,本公开不意图限于本文描述的示例,而是将符合与本文公开的原理和新颖特征相一致的最宽范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。