一种基于lvds的spi信号板间传输电路

技术领域

1.本发明属于数据传输技术领域,尤其涉及一种基于lvds的spi信号板间传输电路。

背景技术:

2.spi是串行外设接口(serial peripheral interface)的缩写,是一种高速全双工的同步通信总线。最初由摩托罗拉公司在其mc68hcxx系列处理器上定义,后被各种电子设备广泛使用。spi的通信模型一般由主模块和从模块构成,两者之间通过4根信号线相连,分别是clk(时钟信号线),cs(片选信号线),miso(主模块收,从模块发信号线)和mosi(主模块发,从模块收)。主模块要负责产生时钟信号及片选信号,从模块会根据主模块产生的时钟信号线的跳边沿采样或改变miso和mosi信号线上的电平状态,达到接收数据或发送数据的目的,因此spi通信时是同步的。由于有miso和mosi两条信号线,所以对于主模块或从模块的任意一方,都可以同时进行数据的收发工作,因此spi通信是全双工的。spi的时钟频率可以达到40mhz以上,如果每个时钟周期都传输1bit数据,则spi的数据传输速率可以达到40mbps以上。spi多在pcb(printed circuit board,印制电路板)板内用于信号的高速传输,用于板间传输时易受干扰,传输速率和正确性都有所下降。

3.lvds是低电压差分信号(low-voltage differential signaling)的缩写,美国ieee(institute of electrical and electronics engineers,电气与电子工程师协会)在ieeep1996.3和ans/eia/eia-644这两个标准中对lvds做了定义,标准推荐的最大传输速率可以达到655mbps。它使用幅度差非常低的信号(约350mv)通过一对差分pcb走线或平衡电缆传输数据。由于lvds信号采用恒流源模式进行驱动,因此产生的噪声和小号的功率都很小,同时,采用差分方式进行数据传输,一方面可以有效防止共模噪声对传输信号的干扰,另一方面,由于差分信号的极性相反,对外辐射的电磁场可以相互抵消,有效减小了传输线对外的电磁干扰。

4.通过lvds转换芯片(可以收发lvds信号的芯片)可以将spi的4根信号线(均为单端信号线)转为符合lvds标准的差分信号,利用lvds信号传输速率快,抗干扰能力强的特点,在pcb板间以lvds信号的形式进行spi信号的传输,目前已有的实现方案中,申请公布号为cn 104796150 a的发明专利公开的方式中,在主模块端使用2片lvds发芯片,2片lvds收发芯片,在从模块端使用2片lvds收芯片,2片lvds收发芯片,通过这8片芯片之间的互连,实现lvds信号之间的通信。在美国德州仪器(ti)公司公布的编号为tida-060017的设计方案中,在主模块端和从模块端都使用1片4路lvds发芯片和1片4路lvds收芯片,发芯片只使用其中3路,收芯片只使用其中1路,互连实现lvds信号的通信。

5.上述两种方案的缺点在于,一方面,进行spi通信时,spi设备间主模块与从模块的角色关系已确定,即根据lvds转换芯片的收发属性,spi通信中主模块和从模块的相对关系无法更改。而对于某些电子设备或器件而言,作为spi主模块和spi从模块下可以支持的最高数据传输速率是不同的,因此不能够在主模块和从模块之间实现双向都使用设备可支持的最高数据传输速率进行通信。另一方面,现有方案的lvds信号线在板板之间的连接器多

使用排线等大端子,占用pcb面积,对于pcb板面积的减小和电子设备的小型化不利。

技术实现要素:

6.本发明解决使用lvds信号在板间传输spi信号时,spi设备主模块与从模块角色已被确定的问题,使得spi设备作为主模块和从模块的角色可以相互转换。同时,采用新的板板间lvds信号连接器,减小该连接器在pcb板上所占面积。

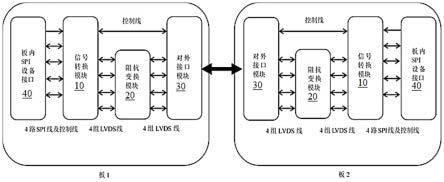

7.具体技术方案为一种基于lvds的spi信号板间传输电路,包括spi信号产生设备,还包括信号转换模块、阻抗变换模块和对外接口模块,其中,

8.所述信号转换模块与spi信号产生设备和阻抗变换模块连接,接收spi信号产生设备的spi单端信号,将其转化为lvds差分信号输出;或者接收阻抗变换模块的lvds差分信号,将其转化为spi单端信号输出;

9.所述阻抗变换模块处于信号转换模块与对外接口模块之间,用于变换从信号转换模块中引出的lvds信号路径的阻抗,变换后lvds信号路径的阻抗和对外接口模块的阻抗相同;

10.所述对外接口模块向pcb板外输出或从pcb板外输入lvds信号和信号转换模块中需要用到的控制信号。

11.优选地,所述信号转换模块包括4组lvds信号收发模组。

12.优选地,所述lvds信号收发模组包括安森美半导体公司的fin1019芯片及其外围电阻电容,fin1019芯片的din引脚和rout引脚分别用于接收和发送spi单端信号,dout 和dout-引脚用于发送lvds差分信号,rin 和rin-引脚用于接收lvds差分信号;de引脚用于控制fin1019芯片的lvds信号发送是否使能,在高电平时有效,即对de引脚输入高电平时,lvds信号发送使能,输入低电平时,lvds信号发送不使能;re/引脚用于控制fin1019芯片的lvds信号接收是否使能,在低电平时有效,即对re/引脚输入低电平时,lvds信号接收使能,输入高电平时,lvds信号引脚接收不使能。

13.优选地,所述阻抗变换模块通过在pcb板上lvds传输线宽度的变化实现。

14.优选地,所述对外接口模块包括24pin的usb typec接口及其外壳的接地电阻。

15.优选地,所述spi信号产生设备包括esp32-wroom模组。

16.与现有技术相比较,本发明至少包括以下有益效果:

17.1.在使用lvds信号于板间传输spi信号时,可以改变不同板上spi设备所处的工作状态角色,任意选择设备作为spi主模块或spi从模块,这可以使得在板间通信的任意方向上,均可以使用spi设备支持的最大速率进行spi通信,对于某些设备而言,在某一方向上的通信速率可以提高5-6倍;

18.2.可以减小用于板板间连接接口的尺寸,从而减小该接口在pcb板上所占用的面积,有利于pcb板尺寸的缩小,使用该电路板的设备的集成度更高。

附图说明

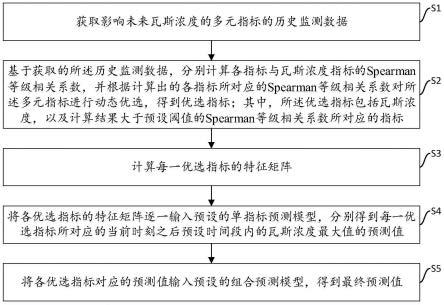

19.图1为本发明基于lvds的spi信号板间传输电路的结构框图;

20.图2为本发明基于lvds的spi信号板间传输电路的信号转换模块电路原理图;

21.图3为本发明基于lvds的spi信号板间传输电路的阻抗变换模块在pcb上的走线示

意图;

22.图4为本发明基于lvds的spi信号板间传输电路的对外接口模块电路原理图;

23.图5为本发明基于lvds的spi信号板间传输电路的spi信号产生设备电路原理图。

具体实施方式

24.以下将结合附图对本发明提供的技术方案作进一步说明。

25.为了解决现有技术存在的技术问题,参见图1,所示为本发明基于lvds的spi信号板间传输电路的框图,所示为每个电路板中模块之间的连接方式,以及在每个模块中传输的信号,每个电路板上设置信号转换模块10、阻抗变换模块20、对外接口模块30和板内spi设备接口40,板间通过对外接口模块30连接,板内的信号转换模块10与spi信号产生设备通过板内spi设备接口40连接。由3个功能模块构成,同时需要辅以一个能够产生spi信号及高低电平控制信号的设备,该4种元素应当同时集中在1个pcb板上,方可发挥本发明所述功能。

26.上述3个功能模块分别为信号转换模块10、阻抗变换模块20和对外接口模块30。对于spi信号来说,3个模块加上spi信号产生设备,这4个部分通过串联的方式连接在一起,spi信号依序流过这4个部分。而对于高低电平的控制信号,信号从设备产生后,流经信号转换模块10后,不经过阻抗变换模块20,直接流入到对外接口模块30中。

27.信号转换模块10的功能是接收输入该模块的spi单端信号,将其转化为lvds差分信号输出;或者接收输入该模块的lvds差分信号,将其转化为spi单端信号输出。如前述,spi包含4条信号线,因此本信号转换模块10应当包含至少4组能够进行lvds信号收发的设备。每一组信号的收发设备的单端信号接收和发送引脚与一条spi信号线相连,lvds信号引脚通过传输线引出至阻抗变换模块20中去;信号收发设备的收发使能控制引脚与接入本模块的控制信号连接。本模块还应当能够接收模块外传来的控制信号,该控制信号的来源有2处,一处是通过上文提到的可以产生高低电平控制信号的设备,另一处是由对外接口模块30中传来。控制信号用于控制本模块中lvds信号收发设备的收发使能状态,可在使能接收spi信号,发送lvds信号和使能接收lvds信号,发送spi信号两种状态中选择。因此,lvds信号收发的设备应当允许通过外部输入的控制信号实现上述控制效果。

28.在使用本发明时,应当事先在进行spi通信的电路板中确定一个主控板,注意,此处的主控板不代表其上的spi设备工作于主模块状态,是否是主控板与板上的spi设备在spi通信时是主模块还是从模块没有关系。主控板负责产生控制lvds收发器收发是否使能的控制信号,该控制信号一方面传输到主控板上的信号转换模块10,另一方面通过主控板上的对外接口模块30,将控制信号传输到非主控板上去,非主控板上的设备不应当产生或影响到主控板上传来的控制信号。

29.阻抗变换模块20处于信号转换模块10与对外接口模块30之间,用于变换从信号转换模块10中引出的lvds信号路径的阻抗,达到在变换后,lvds信号路径的阻抗和对外接口模块30的阻抗相同的状态。在信号于传输线上传输时,会在信号线与信号的参考平面之间产生电场,由于电场的建立会产生一个瞬间电流,而信号本身会有一个电压,此电压和瞬间电流的比值则为信号遇到的阻抗。如果传输线的阻抗不连续,则会在阻抗不连续处发生信号反射,从而对信号的电压造成影响,并最终影响到信号终端对信号的判决结果。因此当对

外接口模块30中使用的接口器件的特性阻抗与lvds信号要求的特性阻抗不同时,则应当进行阻抗变换,如果相同,可以不使用该模块。

30.对外接口模块30,用于向pcb板外输出或从pcb板外输入lvds信号和信号转换模块10中需要用到的控制信号,该接口应当尽量小巧,在pcb板上不占用过多面积,同时能够传输差分信号。对外接口模块30是板间通信时,板板之间连接线的接口。本发明中,从阻抗变换模块20中引出的4组lvds差分信号线和从信号转换模块10中引出的控制信号线应当全部接入对外接口模块30中。

31.具体实施例中,信号转换模块10包括4片安森美半导体公司的fin1019芯片及其外围电阻电容,一个由三极管ss8050及其外围电阻电容构成的电平反相电路。阻抗变换模块20不使用器件,通过在pcb板上lvds传输线宽度的变化实现。对外接口模块30包括一个全功能24pin的usb typec接口及其外壳的接地电阻。

32.用于产生spi信号和高低电平控制信号的设备使用esp32-wroom模组,该模组可配置2组对外使用的spi信号接口,本实施例中只使用其中1组,另外可使用该模组除spi信号接口外的任意一个信号接口,将其映射为gpio口,可产生高低电平信号用作控制信号。

33.本实施例只使用了2块含有本发明电路的电路板进行连接。

34.信号转换模块10的电路原理图参见图2。图2中位于上方的4片芯片为lvds信号收发芯片fin1019(u1-u4),该芯片的din引脚和rout引脚分别用于接收和发送spi单端信号,dout 和dout-引脚用于发送lvds差分信号,rin 和rin-引脚用于接收lvds差分信号。de引脚用于控制fin1019芯片的lvds信号发送是否使能,在高电平时有效,即对de引脚输入高电平时,lvds信号发送使能,输入低电平时,lvds信号发送不使能。re/引脚用于控制fin1019芯片的lvds信号接收是否使能,在低电平时有效,即对re/引脚输入低电平时,lvds信号接收使能,输入高电平时,lvds信号引脚接收不使能。图中标号为r2,r11,r14,r17的四个电阻用于在lvds信号接收端进行阻抗匹配,防止信号反射。

35.图2中下半部分是由标号为q1,型号是ss8050的三极管为核心组成的一个电平反相电路,其中信号网络名为en_p的一端为信号输入端,信号网络名为en_n的一端为信号输出端。该电平反相电路可以将输入的信号电平反相,即如果输入的信号电平为高电平,则输出信号电平为低电平,如果输入信号电平为低电平,输出信号电平为高电平。其中电阻r4用于在三极管导通时,钳位三级管be极之间的电压在0.7v的导通电压左右,其余电压由r4承受。电阻r5用于提高高电平导通三极管的门限阈值,增强抗干扰能力,否则输入信号线上较大的电压脉冲可能导致三极管的误导通,在输出端产生错误信号。电阻r1用于在三级管导通后限制ce极之间的电流,防止三极管因为通过了太大的电流而损坏。

36.由图2中可以看到,4片fin1019芯片的din和rout引脚分别与图1中所示的4路spi信号线相连,用于从esp32-wroom模组处接收spi信号或发送spi信号给esp32-wroom模组。图5中esp32_wroom模组io5引脚接出的信号网络en_p连接到了除了u3这片芯片以外的其余3片fin1019芯片的de和re/引脚,同时还连接到了电平反相电路的输入端,电平反相电路的输出端信号网络名为en_n,en_n连接到了u3片芯片的de引脚和re/引脚。图5的信号网络名称都在图中有所标识。

37.图2中所示的vcc网络是电源网络,电源网络负责给4片fin1019芯片供电,同时也给电平反相电路提供能量。在本实施例中,vcc电压取3.3v,如果使用其他lvds信号收发芯

片或有其他的信号电平标准,则可以通过在本发明所在的电路板上增添电源芯片的方式改变vcc网络的电压,此处不属于本发明的范围,不在此叙述。

38.参见图3,阻抗变换模块20通过在pcb上走线宽度的变化达到功能。由于本实施例的对外接口模块30中的接口选用的是usb typec接口,usb协议规定usb差分线的特性阻抗为90ohm,而lvds协议规定lvds差分线的特性阻抗为100ohm。因此,利用usb typec接口传输lvds信号时,应当将lvds信号传输线的阻抗变换到90ohm上。如图3所示,图左侧较细的差分线表示阻抗为100ohm的差分走线,右侧较粗的差分线表示阻抗为90ohm的差分走线,两者之间通过宽度渐变的走线予以过渡。本实施例中,走线宽度渐变的部分长度为5mm。图2中所示的cs /cs-,clk /clk-,mosi /mosi-和miso /miso-这4组差分线在pcb板上的走线均要如图3所示那样处理后,再接入到对外接口模块30中。

39.通过电磁仿真,本实施例中的阻抗变换模块20,在400mhz频率以下的s11反射系数均小于-20db,即表明通过该阻抗变换模块20后,信号功率的损失小于1/100。

40.参见图4,对外接口模块30包括usb typec接口和其外壳的接地电阻。图4中j1为usb typec接口的母座,j2为usb typec接口的公头,使用本发明进行板间通信时,用于板间互连的对外接口模块30中的usb typec接口,应当一为母座,一为公头,两者之间通过usb typec公头转母座的连接线连接。对于本实施例中任何一个具体的电路实现,对外接口模块30中只需要选择j1或j2中的一个作为对外接口模块30即可,连接后,公头和母座中同一序号的信号线连接在一起。

41.usb typec接口引脚的信号定义如表1所示。

42.表1对外接口模块30中的usb type-c接口引脚信号定义

43.44.[0045][0046]

esp32-wroom模组的电路原理图参见图5。由图5可以看到,使用该模组的io12,io13,io14和io15引脚作为spi信号的接口,其中,io12作为miso信号接口,引出信号的网络名称为spi_miso,io13作为mosi信号接口,引出信号的网络名称为spi_mosi,io14作为clk信号接口,引出信号的网络名称为spi_clk,io15作为cs信号的接口,引出信号的网络名称为spi_cs。另外使用io5接口产生高低电平控制信号,引出信号的网络名称为en_p。上述信号的网络名称在图5中的网络名称均已标识,图5及前面的图中出现的所有相同信号网络名称表示他们是连接在一起的。

[0047]

根据上述的各模块的结构和连接方式,接下来阐述信号的流向。

[0048]

对于spi信号,当spi设备当做spi主模块工作时,spi设备产生cs,clk和mosi信号,通过图2中所示的信号转换模块10中的u1,u2和u4 3片芯片将单端的spi信号转换为lvds差分信号,之后lvds差分信号通过阻抗变换模块20和对外接口模块30输出到板外。同时,本发明电路从对外接口模块30中接收到另一个板上传来的已转换为lvds信号的spi的miso信号,然后通过阻抗变换模块20,进入图2所示的信号转换模块10中的u3芯片,将lvds信号转换为spi单端信号,再传输给spi设备。当spi设备当做spi从模块工作时,spi设备只产生miso信号,之后的信号流向与spi设备作为主模块时,cs,clk和mosi信号的流向相同。同时,本发明电路从对外接口模块30中接收板外传来的已转换为lvds差分信号的cs,clk,mosi信号,信号流向与spi设备作为主模块时,miso信号的流向相同。

[0049]

本实施例中高低电平控制信号的控制逻辑如下所述。

[0050]

首先应当确定相连的2块电路板中的其中一块作为主控板,如前文所述,主控板中的spi设备具有产生高低电平控制信号并将其传输出去的责任,同时非主控板中的spi设备不能对高低电平控制信号造成影响。

[0051]

当主控板中的spi设备作为主模块,非主控板中的spi设备作为从模块时,主控板中的spi设备应当拉高高低电平控制信号的电平。即图2和图5中所示的en_p信号网络应当被拉为高电平。此时,en_p经过图2中所示的电平反相电路后,输出的en_n信号网络为低电平。根据图2中极上文叙述中所表明连接关系,此时u1,u2,u4这3片fin1019芯片均处于lvds发送使能而接收不使能的状态,可用于传输作为主模块的spi设备传出的cs,mosi和clk信号,而u3这片fin1019芯片则处于lvds信号接收使能而发送不使能的状态,可以用于接收由从模块传来的miso信号。通过图4所示的对外接口模块30原理图,可以看到,usb typec接口的公头和母座之间的高低电平控制信号之间的连接方式为母座的en_p连接公头的en_n,母座的en_n连接公头的en_p,图4中所示的en_p和en_n信号,正是从图2中所示的电平反相电路那里引来的。那么,当主控板中的en_p为高电平,en_n为低电平时,非主控板上的en_p信号为低电平,en_n信号为高电平。非主控板上,信号转换模块10的电路连接方式和图2所示一样,因此非主控板上的u1,u2和u4这3片芯片处于lvds信号接收使能,发送不使能的状态,可以接收从主模块上发来的cs,mosi,clk信号;而u3这片芯片处于lvds信号发送使能,接收

不使能的状态,可以向主模块发送miso信号。

[0052]

当主控板中的spi设备作为从模块,非主控板中的spi设备作为主模块时,主控板中的spi设备将高低电平控制信号的电平拉低即可。之后lvds信号收发芯片所处状态的分析流程和上段中所述相同,此处不再赘述。

[0053]

经过测试,将本实施例用于两块带有esp32-wroom模组的电路板间,板间的连接距离为500mm。在电路板间进行spi通信时,在两个方向上,数据传输的速率均可达到50mbps以上,同时可以任意切换两块电路板上的esp32-wroom模组是作为spi主模块工作还是作为spi从模块工作。

[0054]

以上实施例的说明只是用于帮助理解本发明的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本发明进行若干改进和修饰,这些改进和修饰也落入本发明权利要求的保护范围内。

[0055]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。