1.本发明涉及集成电路设计与制造技术领域,尤其涉及一种有源带通滤波器中心频率校准电路。

背景技术:

2.有源rc带通滤波器具有带外抑制好,带内平坦度优的特点,且随着电路集成工艺的高速发展和设计技术的快速进步,将带通滤波器和信号链路芯片化集成需求一直是射频链路系统高集成、低功耗发展趋势方向之一。带通滤波器中心频率的一致性往往受到工艺偏差的影响,尤其是利用硅基cmos工艺实现的有源rc带通滤波器芯片,片上电阻和电容c的参数波动会影响滤波器中心频率的漂移。

技术实现要素:

3.为解决现有的技术问题,本发明提供了一种有源带通滤波器中心频率校准电路。

4.本发明的具体内容如下:一种有源带通滤波器中心频率校准电路,通过对校准电路施加已知频率的参考信号,将滤波器滤波后的输出信号进行相位检测,将获取的相位信号和参考信号的相位进行比较,根据相位比较的结果来调整数字电路控制信号的输出,该控制信号用来控制带通滤波器内部的电容网络,电容网络调整后,带通滤波器的中心频率跟着调整,滤波器的输出信号相位继续和固定参考信号的相位进行比较,直至相位和参考信号对齐。

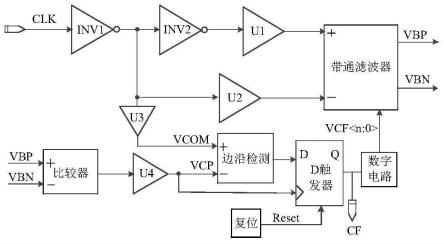

5.进一步的,包括反相器、缓冲器、比较器、边沿检测电路、d触发器电路、数字电路和带通滤波器电路,参考信号经过反相器后进入缓冲器,再经过比较器,边沿检测电路检测到比较器结果后输出脉冲信号至d触发器电路,d触发器电路的输出信号作为数字电路的控制输入端,数字电路控制带通滤波器电路。

6.进一步的,反相器inv1的输入端连接参考时钟clk,输出端和反相器inv2的输入端相连,同时和缓冲器u2的输入端相连,还和缓冲器u3的输入端相连;反相器inv2的输出端和缓冲器u1的输入端相连;缓冲器u1的输出端和带通滤波器的正向输入端相连;缓冲器u2的输出端和带通滤波器的反向输入端相连;缓冲器u3的输出端和边沿检测的正向输入端相连;带通滤波器的差分输出端vbp和vbn分别和比较器的正向和反向输入端相连;比较器的输出端和缓冲器u4的输入端相连;缓冲器u4的输出端vcp和边沿检测电路的反向输入端相连,同时和d触发器的时钟控制端相连;边沿检测的输出端和d触发器的输入端d相连;复位电路的reset端和d触发器的复位端相连;d触发器的输出端cf和数字电路的输入端相连;数字电路的输出控制信号vcf《n:0》和带通滤波器的控制端相连。

7.进一步的,clk为外部输入的参考时钟信号,频率为希望校准的目标频率。

8.本发明的一种易于集成的有源带通滤波器中心频率校准方法,能有效的对滤波器的中心频率进行调谐,实现预期的滤波器中心频率,提升芯片的可靠性。

附图说明

9.下面结合附图对本发明的具体实施方式做进一步阐明。

10.图1为有源带通滤波器中心频率校准电路示意图;

11.图2为关键点波形图,其中图2(a)为校准完成前的关键点波形图,图2(b)为校准完成后的关键点波形图;

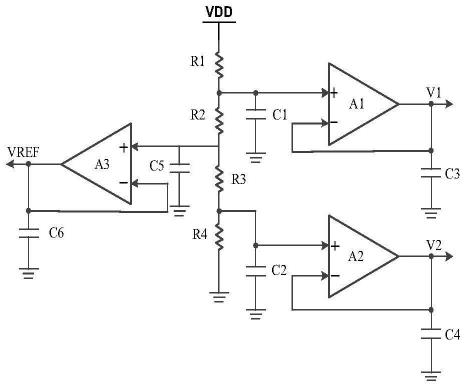

12.图3为有源rc网络的电容调谐方式示意图。

具体实施方式

13.结合图1-图3,本发明的有源带通滤波器中心频率校准电路由反相器、缓冲器、比较器、边沿检测电路、d触发器电路、数字电路和带通滤波器电路组成。

14.其结构如下:反相器inv1的输入端连接参考时钟clk,输出端和反相器inv2的输入端相连,同时和缓冲器u2的输入端相连,还和缓冲器u3的输入端相连;反相器inv2的输出端和缓冲器u1的输入端相连;缓冲器u1的输出端和带通滤波器的正向输入端相连;缓冲器u2的输出端和带通滤波器的反向输入端相连;缓冲器u3的输出端和边沿检测的正向输入端相连;带通滤波器的差分输出端vbp和vbn分别和比较器的正向和反向输入端相连;比较器的输出端和缓冲器u4的输入端相连;缓冲器u4的输出端vcp和边沿检测电路的反向输入端相连,同时和d触发器的时钟控制端相连;边沿检测的输出端和d触发器的输入端d相连;复位电路的reset端和d触发器的复位端相连;d触发器的输出端cf和数字电路的输入端相连;数字电路的输出控制信号vcf《n:0》和带通滤波器的控制端相连。

15.图1中clk为外部输入的参考时钟信号,频率为希望校准的目标频率。clk信号经过反相器inv1、inv2通路以及反相器inv1通路分别给到缓冲器u1和缓冲器u2的输入端,该两路信号为差分信号。缓冲器u1和缓冲器u2将差分的满摆幅信号转换成有驱动能力的差分输入信号。此时,差分输入信号的频率依然是目标频率。当输入的差分信号频率和校准带通滤波器的中心频率偏离时,则vbp和vbn信号经过比较器比较缓冲后,得到的vcp信号相位超前于vcom信号。此时边沿检测电路检测到vcom信号的上升沿滞后于vcp信号的上升沿到来,则边沿检测电路输出一个脉冲信号,该脉冲信号宽度反应了vcom信号相对于vcp信号的滞后量,则d触发器输出cf为低电平,此时数字电路对控制位vcf《n:0》进行进位处理。关键信号点的波形图如图2(a)所示。

16.当输入的差分信号频率和校准带通滤波器的中心频率接近时,vbp和vbn信号的相位和输入差分信号的相位分别相差180

°

,而输入差分信号是由参考信号经过反向和缓冲之后得到的,因此,此时vbp信号和vcom信号应该相差180

°

相位。方波输入信号经过带通滤波器后,输出正弦信号,相位相差180

°

,则vbp和vbn信号经过比较器比较缓冲后,得到和vcom相位近似相等的vcp信号。由于信号链路延时,此时vcp的相位要稍稍滞后于vcom信号,边沿检测电路检测到vcom信号的上升沿先于vcp信号的上升沿到来,则边沿检测电路输出和vcom同相位信号。vcp信号同时作为d触发器信号的时钟控制信号,因此,当vcp信号上升沿来临,d触发器检测输入信号,该信号为vcom的同相位信号,则d触发器输出高电平cf信号。cf信号作为数字电路的控制输入端,当cf为高电平时,数字电路停止对控制位vcf《n:0》进位。关键信号点的波形图如图2(b)所示。

17.在图3中,vcf《n:0》经过译码后,控制对应的nmos开关的导通或者关闭,来选取对

应的电容是否接入有源rc网络中。例如,当开关mj的栅极为高电平时,开关导通,电容cj接入有源rc网络中,则决定滤波器中心频率的电容值变大;反之,开关mj栅极电压为低时,总电容值变小。一般而言,总电容值变小时,中心频率变大,总电容变大时,中心频率变小。经过上述过程实现了有源rc带通滤波器的中心频率调谐。

18.本技术通过对校准电路施加已知频率的参考信号,将滤波器滤波后的输出信号进行相位检测,将获取的相位信号和参考信号的相位进行比较,根据相位比较的结果来调整数字电路控制信号的输出,该控制信号用来控制带通滤波器内部的电容网络,电容网络调整后,带通滤波器的中心频率跟着调整,滤波器的输出信号相位继续和固定参考信号的相位进行比较,直至相位和参考信号对齐,实现中心频率的校准。本发明采用反相器、缓冲器、比较器、边沿检测电路、d触发器电路、数字电路和带通滤波器电路组成一种有源带通滤波器中心频率校准电路,实现中频有源rc带通滤波器电路的中心频率调谐,跟传统的方法相比,电路实现方式简单,集成度高,能够跟现有的硅基有源电路集成。

19.在以上的描述中阐述了很多具体细节以便于充分理解本发明。但是以上描述仅是本发明的较佳实施例而已,本发明能够以很多不同于在此描述的其它方式来实施,因此本发明不受上面公开的具体实施的限制。同时任何熟悉本领域技术人员在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。