技术特征:

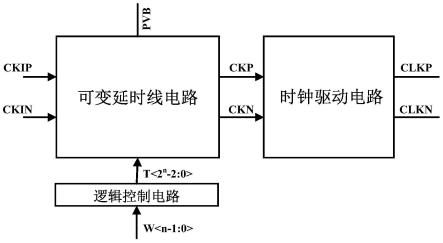

1.一种用于高速低抖动dll的可编程延时线电路,其特征在于,包括:可变延时线电路、逻辑控制电路和时钟驱动电路;所述逻辑控制电路将外部输入的n位延时线长度编程码w<n-1:0>译码为2

n-1位的延时线长度控制信号t<2

n-2:0>,并输出到可变延时线电路,实现对延时线长度的配置;可变延时线电路输入端接外部输入的差分时钟信号ckip、ckin,在逻辑控制电路输出的延时线长度控制信号t<2

n-2:0>控制下改变延时线长度,进而实现对输入时钟延时进行粗调整;另外,通过改变外部输入偏置电压pvb,实现对输入时钟延时的精调整;调整延时后输出差分时钟信号ckp、ckn,并传输给时钟驱动电路;时钟驱动电路接收来自可变延时线电路输出的差分时钟信号ckp、ckn,将ckp、ckn时钟放大恢复为满幅度的方波时钟信号,并校正占空比和交叉点;输出调整后的差分时钟信号clkp、clkn。2.根据权利要求1所述一种用于高速低抖动dll的可编程延时线电路,其特征在于:所述可变延时线电路包含2

n

1级结构相同的基本延时单元;2

n

1级基本延时单元首尾相连;通过在逻辑控制电路输出的延时线长度控制信号t<2

n-2:0>控制下,改变基本延时单元的接入数量,粗调整输入时钟延时。3.根据权利要求2所述一种用于高速低抖动dll的可编程延时线电路,其特征在于,所述基本延时单元包括:前向通路、反向通路;第k级基本延时单元前向通路输入接收来自第k-1级基本延时单元前向通路输出的前向差分时钟信号fp<k>、fn<k>,经过前向通路延时传输后产生输出前向差分信号fp<k 1>、fn<k 1>;2

n

1级基本延时单元由0开始依次编号,k∈[0,2

n

];同时,第k级基本延时单元反向通路输入接收来自第k 1级基本延时单元反向通路输出的反向差分时钟信号bp<k 1>、bn<k 1>,经过反向通路延时传输后产生输出反向差分信号bp<k>、bn<k>;0≤k≤2

n

;其中,第0级基本延时单元的前向通路输入fp<0>、fn<0>作为可变延时线的差分输入ckip、ckin,第0级基本延时单元的反向通路输出bp<0>、bn<0>为可变延时线的差分输出ckp、ckn;而第2

n

级基本延时单元的反向通路输入bp<2

n

1>、bn<2

n

1>分别连接电源电平与地电平。4.根据权利要求3所述一种用于高速低抖动dll的可编程延时线电路,其特征在于:第0级基本延时单元的控制信号s0<2:0>分别连接t<0>、0、0;第1级基本延时单元控制信号s1<2:0>分别连接t<1>、t<0>、0;第k级基本延时单元控制信号s

k

<2:0>分别连接t<k:k-2>,2≤k≤2

n-2;第2

n-1级基本延时单元控制信号s

2n-1

<2:0>分别连接1、t<2

n-2>、t<2

n-3>;第2

n

级基本延时单元控制信号s

2n

<2:0>分别连接1、1、t<2

n-2>。5.根据权利要求4所述一种用于高速低抖动dll的可编程延时线电路,其特征在于:第k级基本延时单元还包括:控制电路;2

n

1级基本延时单元由0开始依次编号,k∈[0,2

n

];控制电路包括:反相器i5和两输入或非门n0、两输入或非门n1和两输入或非门n2;两输入或非门n0的两个输入端分别连接控制信号s<2>和s<1>,输出接反相器i5输入端和两输入或非门n1的一个输入端;两输入或非门n1的另外一个输入端与两输入或非门n2的一个输入端相连,共同连接控制信号s<0>,两输入或非门n1的输出端产生控制信号kn;两输入或非门n2的另外一个输入端相连反相器i5的输出端,两输入或非门n2的输出端产生控制

信号k;前向通路包括:反相器i1、反相器i2、反相器i3和反相器i4;反相器i1输入端接fp<k>,输出端接fn<k 1>;反相器i2输入端接fn<k>,输出端接fp<k 1>;反相器i3输入端接fn<k 1>,输出端接fp<k 1>;反相器i4输入端接fp<k 1>,输出端接fn<k 1>;反向通路包括nmos晶体管m0、nmos晶体管m1、nmos晶体管m2、nmos晶体管m3、nmos晶体管m4、nmos晶体管m5、nmos晶体管m6、nmos晶体管m7以及pmos晶体管m8、pmos晶体管m9、pmos晶体管m10和pmos晶体管m11;nmos晶体管m0源极接地电位,栅极接反向输入的差分时钟bp<k 1>,漏极接nmos晶体管m4源极;nmos晶体管m4栅极接控制信号k,漏极接nmos晶体管m6漏极、pmos晶体管m8漏极、pmos晶体管m10漏极、pmos晶体管m11栅极,并产生输出时钟bn<k>;nmos晶体管m1源极接地电位,栅极接反向输入时钟bn<k 1>,漏极接nmos晶体管m5源极;nmos晶体管m5栅极接控制信号k,漏极接nmos晶体管m7漏极、pmos晶体管m9漏极、pmos晶体管m11漏极、pmos晶体管m10栅极,并产生输出时钟bp<k>;nmos晶体管m2源极接地电位,栅极接前向输出时钟fp<k 1>,漏极接nmos晶体管m6源极;nmos晶体管m6栅极接控制信号kn;nmos晶体管m3源极接地电位,栅极接前向输出时钟fn<k 1>,漏极接nmos晶体管m7源极;nmos晶体管m7栅极接控制信号kn;pmos晶体管m8源极接电源电位,栅极接外部输入偏置电压pvb;pmos晶体管m9源极接电源电位,栅极接外部输入偏置电压pvb;pmos晶体管m10源极接电源电位;pmos晶体管m11源极接电源电位。6.根据权利要求5所述一种用于高速低抖动dll的可编程延时线电路,其特征在于,当控制信号s<2:0>=111,控制信号k和kn均为地电平,nmos晶体管m4~m7全部关断,fp<k>、fn<k>延时输出到fn<k 1>、fp<k 1>,前向通路贯通;bp<k>、bn<k>保持电平输出,反向通路关断。7.根据权利要求5所述一种用于高速低抖动dll的可编程延时线电路,其特征在于,当控制信号s<2:0>=110或100,控制信号k为地电平,kn为电源电平,nmos晶体管m4、nmos晶体管m5关断,nmos晶体管m6、nmos晶体管m7导通,fp<k>、fn<k>延时输出到fn<k 1>、fp<k 1>,前向通路贯通;fp<k 1>、fn<k 1>延时输出到bn<k>、bp<k>;前向通路和反向通路短路连接。8.根据权利要求5所述一种用于高速低抖动dll的可编程延时线电路,其特征在于,当控制信号s<2:0>=000,控制信号k为电源电平,kn为地电平,nmos晶体管m4、nmos晶体管m5导通,nmos晶体管m6、nmos晶体管m7关断,fp<k>、fn<k>延时输出到fn<k 1>、fp<k 1>,前向通路贯通;bp<k 1>、bn<k 1>延时输出到bn<k>、bp<k>,反向通路贯通;此时,前向通路和反向通路分别独立延时传输时钟信号。9.根据权利要求1~8任意之一所述一种用于高速低抖动dll的可编程延时线电路,其特征在于:当n位二进制的编程码w<n-1:0>对应十进制数值为i时,0≤i≤2

n-1;当i=0时,延时线长度控制信号t<2

n-2:0>全部为逻辑“1”电平;当i=2

n-1时,延时线长度控制信号t<2

n-2:0>全部为逻辑“0”电平;当1≤i≤2

n-2时,延时线长度控制信号t<2

n-2:i>为逻辑“1”电平,延时线长度控制信号t<i-1:0>为逻辑“0”电平。

10.根据权利要求9所述的一种用于高速低抖动dll的可编程延时线电路,其特征在于:n为大于或等于2的正整数。

技术总结

本发明涉及一种用于高速低抖动DLL的可编程延时线电路,包括可变延时线电路、逻辑控制电路和时钟驱动电路。可变延时线电路可通过调节延时线长度,灵活改变输入时钟的传输延时;同时,可变延时线电路可通过改变单级延时偏置电压,进而精细改变输入时钟的传输延时;逻辑控制电路将外部输入编程码译码为延时线长度控制信号;时钟驱动电路能够将时钟恢复为满幅度的方波时钟信号,并校正时钟信号的占空比和交叉点以供后级电路使用。本发明能够精确且灵活实现高速低抖动差分时钟延时调整,通过增加延时链长度,进而单级延时单元的延时精度不断提高,能够满足高速低抖动DLL对可变延时线宽延时调节范围和高延时调节精度的要求。延时调节范围和高延时调节精度的要求。延时调节范围和高延时调节精度的要求。

技术研发人员:霍淼 张雷 初飞 王宗民 张铁良 王金豪 侯贺刚 任艳

受保护的技术使用者:北京微电子技术研究所

技术研发日:2022.09.30

技术公布日:2023/1/31

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。