1.本技术涉及光纤陀螺芯片技术领域,更具体地,涉及一种微系统级的光纤陀螺信号处理集成芯片及其制造方法。

背景技术:

2.光纤陀螺信号处理电路作为光纤陀螺的核心部分,国内外陀螺生产厂家均将其作为核心商业秘密进行保护,其中详细的电路设计都未公开作介绍。

3.国内未见对光纤陀螺信号处理电路的sip(system in a package的缩写,即系统级封装)、soc(system on chip,即系统级芯片)的报道,普遍采用的是分离器件进行搭建。北京772所已经研发出了将adc、fpga、dac进行集成的soc芯片baf1000,该芯片专用于陀螺电路;深圳国威目前正在计划将陀螺的fpga、dac、adc进行集成设计,制造出类似于772所的baf1000功能相似的芯片;2017年,中国电子科技集团公司第二十四研究所的李博等人公开了一种小尺寸数字闭环光纤陀螺信号处理电路,该方案将光纤陀螺中的模拟部分进行了sip化设计。

4.上述几个公司制造出的光纤陀螺用集成芯片是将光纤陀螺电路中的某一部分(数字电路部分或模拟电路部分)进行sip或soc,在实际使用的过程中,单芯片无法完成光纤陀螺主板电路的所有功能,需要配置外围电路,并与其他功能电路组合使用。另外,该集成芯片虽然降低了陀螺主板的体积,但其集成度并不高,单个芯片的体积也较大,无法满足更小型化主板的要求。

技术实现要素:

5.针对现有技术的至少一个缺陷或改进需求,本发明提供了一种微系统级的光纤陀螺信号处理集成芯片及其制造方法,用以弥补国内微系统级光纤陀螺用集成芯片的空缺,使得其在具有光纤陀螺调制、解调和通讯等功能的同时进一步缩小尺寸和提高集成度,实现光纤陀螺的100%国产化。

6.为实现上述目的,本发明提供了一种微系统级的光纤陀螺信号处理集成芯片,包括:裸芯片、无源器件和管壳;

7.所述裸芯片包括dac芯片、adc芯片和fpga芯片中的一种或多种;

8.所述无源器件包括flash、电阻、电容和电感中的一种或多种;

9.所述管壳包括板状的管壳衬底,采用双面腔体一体化陶瓷针栅阵列设计;

10.所述dac芯片、adc芯片和无源器件设置于所述管壳衬底某一个板状面的第一围腔腔体内,而所述fpga芯片设置于所述管壳衬底相对的另一个板状面的第二围腔腔体内。

11.进一步地,所述第一围腔腔体为kovar金属围腔,采用金丝引线键合工艺进行互联。

12.进一步地,所述第二围腔腔体为陶瓷挖腔,腔内设置填充料。

13.进一步地,所述第一围腔腔体和所述第二围腔腔体均采用平行缝焊工艺进行气密

性封装。

14.进一步地,所述fpga芯片为华微hwd2v1000-4fg256。

15.为实现上述目的,本发明还提供了一种微系统级的光纤陀螺信号处理集成芯片的制造方法,包括:

16.采用双面腔体一体化陶瓷针栅阵列设计方法以制作管壳,管壳包括板状的管壳衬底;

17.将dac芯片、adc芯片和无源器件设置于所述管壳衬底某一个板状面的第一围腔腔体内;所述无源器件包括flash、电阻、电容和电感中的一种或多种;

18.将fpga芯片设置于所述管壳衬底相对的另一个板状面的第二围腔腔体内。

19.进一步地,所述第一围腔腔体为kovar金属围腔,采用导电胶粘接,金丝引线键合工艺进行互联、平行缝焊工艺进行气密性封装。

20.进一步地,所述第二围腔腔体为陶瓷挖腔,腔内设置填充料,采用平行缝焊工艺进行气密性封装。

21.进一步地,所述管壳采用多层氧化铝陶瓷钨金属化高温共烧工艺制作,采用al2o3生瓷加工工艺,经冲孔、填孔、印刷、层压和热切后形成生瓷件,再经高温共烧制成熟瓷件,将熟瓷件镀镍后采用agcu28银铜焊料将封口环和针栅钎焊到瓷体上,再经镀镍镀金制成。

22.进一步地,还包括系统仿真分析流程、单项测试流程和系统测试流程中的一种或多种;

23.所述系统仿真分析流程包括信号完整性仿真子流程、电源完整性仿真子流程、热仿真子流程和结构仿真子流程中的一种或多种;

24.所述单项测试流程包括晶圆级测试子流程、3d ic封装测试子流程、堆叠芯片间互连测试子流程和辅助定位微系统测试子流程中的一种或多种;

25.所述系统测试流程为对已满足设计指标的集成芯片进行系统级别的测试,将其接入光纤陀螺系统中,测试光纤陀螺的各项功能指标。

26.总体而言,通过本发明所构思的以上技术方案与现有技术相比,能够取得下列有益效果:

27.本发明公开了一种微系统级的光纤陀螺信号处理集成芯片,包括裸芯片、无源器件和管壳;裸芯片包括dac芯片、adc芯片和fpga芯片中的一种或多种;无源器件包括flash、电阻、电容和电感中的一种或多种;管壳包括板状的管壳衬底,采用双面腔体一体化陶瓷针栅阵列设计;dac芯片、adc芯片和无源器件设置于管壳衬底某一个板状面的第一围腔腔体内,fpga芯片设置于管壳衬底相对的另一个板状面的第二围腔腔体内。本发明所公开的集成芯片能够作为光纤陀螺电路的主板使用,具有光纤陀螺调制、解调和通讯等功能;同时其尺寸和体积更小、集成度更高,大大地降低了光纤陀螺电路主板的尺寸和成本,有利于光纤陀螺的小型化和低成本化,也做到了光纤陀螺100%国产化的要求。

附图说明

28.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例中所需使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

29.图1为本技术实施例提供的集成芯片的fpga芯片与adc等芯片的三维集成物理架构示意图;

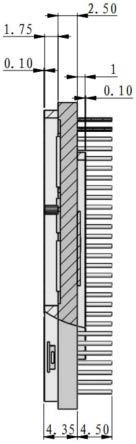

30.图2为本技术实施例提供的微系统级的光纤陀螺用集成芯片的底视图;

31.图3为本技术实施例提供的微系统级的光纤陀螺用集成芯片的侧视图;

32.图4为本技术实施例提供的通过微系统工艺进行集成芯片的制片的总体工艺路径流程框图。

具体实施方式

33.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细地说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

34.本技术的说明书、权利要求书或说明书附图中的术语“第一”、“第二”或“第三”等是用于区别不同对象,而不是用于描述特定顺序的。此外,术语“包括”或“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还可以包括没有列出的步骤或单元,或可选地还可以包括对于这些过程、方法、产品或设备固有的其他步骤或单元。

35.如图1所示,在一个实施例中,一种微系统级的光纤陀螺用集成芯片由裸芯片、无源器件和管壳组成,采用3d-sip进行系统集成封装,管壳采用的是中电十三所定制的陶瓷针栅阵列一体化封装外壳,管壳尺寸为25mm

×

25mm

×

5mm。其中裸芯片中的fpga芯片与adc/dac芯片间采用三维垂直互联进行三维soc集成;其它无源器件如arm、flash、电源管理电路、电阻、电容、电感、接口电路、调制电路和解调电路等采用smt工艺进行高密度sip封装,其产品外形的底试图和侧视图如图2、3所示;管壳采用双面金属围腔设计,分为上下两个腔体,adc/dac芯片、flash等器件放置于上腔体部分,该腔体优选采用kovar金属围腔,采用平行缝焊工艺进行气密性封装;下腔体优选用陶瓷挖腔,下填充料以缓解应力和提高焊接可靠性,也采用平行缝焊工艺进行气密性封装;fpga芯片与盖板间采用高导热率的导热材料进行粘接以提高fpga芯片的散热性能;为了减小整个系统的重量,采用了一体化封装外壳(管壳衬底内部进行布线,管壳衬底相当于基板),管壳的重量约10g,电路的重量小于15g,整个系统的重量小于25g。芯片内部通过集成不同路数的电路可用于不同轴数的光纤陀螺中。

36.元器件的选型决定了主板电路微系统化的成败,优选地,本发明中fpga芯片选择华微hwd2v1000-4fg256;adc芯片选择772所的b9245;dac芯片选择24所的sda1668mc;运算放大器选择24所的sx8138x;电源芯片选择24所的sw1963mf;串口通讯芯片选择华微的hwd3490;flash选择华微的hwd04smtssop20;运算放大器也可选择24所的sx8042xrh等芯片。

37.本实施例提出的一种微系统级的光纤陀螺用集成芯片能够实现光纤陀螺行业内主板电路的基本功能,包括光纤陀螺信号解调和调制、串口通信等功能。光纤陀螺信号处理微系统芯片采用陶封技术实现数字信号处理微系统芯片设计,是一种微系统级的光纤陀螺主板。其包括前放解调电路、fpga及其外围配置电路、后放调制电路、串口通讯电路和供电

电路等。

38.在另一个实施例中,光纤陀螺信号处理微系统芯片制造的具体步骤如下:

39.步骤一、光纤陀螺主板电路设计。光纤陀螺主板是光纤陀螺中最重要的一部分,其作用是将光纤环敏感到的角速度量通过前放解调电路转化为数字信号,并传递给fpga芯片进行处理,一方面通过串口通信电路对外输出当前光纤陀螺角速度值,另一方面经过闭环控制传递给后放调制电路,将数字信号转化为模拟电压信号,对光学器件进行相位调制,从而形成闭环回路。本实施例中选择的光纤陀螺主板电路是本公司自主研发的电路。

40.步骤二、对主板电路进行主要元器件选型。元器件的选型决定了主板电路微系统化的成败,优选地,本发明中的fpga芯片选择华微的hwd2v1000-4fg256;adc芯片选择772所的b9245;dac芯片选择24所的sda1668mc;运算放大器选择24所的sx8138x;电源芯片选择24所的sw1963mf;串口通讯芯片选择华微的hwd3490;flash选择华微的hwd04smtssop20;运算放大器也可选择24所的sx8042xrh等芯片。

41.步骤三、系统级芯片设计。将fpga、adc、dac及其外围配置电路进行系统级芯片设计,如图1所示。该部分采用三维垂直互联工艺技术进行三维集成,制作soc芯片。

42.步骤四、系统级封装设计。将soc芯片及其他器件如flash、电源管理电路、电阻、电容、电感、接口电路等采用smt工艺进行高密度组装,其产品外形底试图和侧视图如图2、3所示。产品管壳的大小约为25mmx25 mmx5.5 mm,采用双面金属围腔设计,分为上下两个腔体,adc、flash等器件放置于上腔体部分,该腔体采用kovar金属围腔,采用平行缝焊工艺进行气密性封装;下腔体设置有fpga芯片,采用平行缝焊工艺进行气密性封装。

43.步骤五、系统仿真分析。通过电/电磁、热、结构等多维物理场仿真保证设计的可靠性。电/电磁仿真,包括信号的完整性仿真与电源完整性仿真,保证高速信号的串扰和干扰达到最小,芯片阻抗、电源地平谐振、电流密度和电热等性能达到最优;热仿真,根据热仿真结果合理布局芯片,设计良好的热导结构,以达到最佳的散热效果,同时给出外部风冷或水冷散热的路径;结构仿真,评估优化微系统结构在加工前的震动、冲击和挤压等情况下的结构可靠性。

44.步骤六、微系统工艺制片。通过微系统工艺进行集成芯片的制片,其具体流程图如图4所示。主要分为芯片检验、管壳检验、芯片清洗、管壳清洗、芯片检验、管壳检验、fpga绑定、x射线检测、下填充料、涂覆导热胶、粘贴盖板、固化导热胶、平行缝焊、涂覆导电胶、贴装器件、固化导电胶、贴片检验、引线键合、键合检验、平行缝焊、检漏、贴盖板、检验和标识等步骤。管壳的上腔体优选用kovar金属围腔,采用导电胶粘接,金丝引线键合工艺进行互联、平行缝焊工艺进行气密性封装;下腔体优选用陶瓷挖腔,下填充料以缓解应力和提高焊接可靠性,平行缝焊工艺进行气密性封装;fpga芯片与盖板间采用高导热率的导热材料进行粘接以提高fpga芯片的散热性能;管壳进行上下双面腔体一体化陶瓷针栅阵列的设计,采用多层氧化铝陶瓷钨金属化高温共烧工艺制作,采用al2o3生瓷加工工艺,经冲孔、填孔、印刷、层压和热切后形成生瓷件,经高温共烧制成熟瓷件,将熟瓷件镀镍后采用agcu28银铜焊料将封口环和针栅钎焊到瓷体上,再经镀镍镀金制成成品。

45.步骤七、单项测试。单项测试技术的内容主要包含:一是晶圆级测试;二是3d ic封装测试,设计扫描测试图形从底层芯片传到顶层芯片的通路;三是堆叠芯片间互连测试;四是辅助定位微系统的专有测试。从测试算法研究入手,突破测试系统的设计技术,搭建模

拟、数字设计仿真平台,研制必要的仪器板卡,最终搭建全参数自动测试系统。

46.步骤八、系统测试。对已满足设计指标的集成芯片进行系统级别的测试,将其接入光纤陀螺系统中,测试光纤陀螺的各项功能指标。

47.本发明所公开的集成芯片能够作为光纤陀螺电路的主板使用,具有光纤陀螺调制、解调和通讯等功能;同时其尺寸和体积更小、集成度更高,大大地降低了光纤陀螺电路主板的尺寸和成本,有利于光纤陀螺的小型化和低成本化,也做到了光纤陀螺100%国产化的要求。

48.以上所述仅为本公开的示例性实施例,不能以此限定本公开的范围。即但凡依本公开教导所作的等效变化与修饰,皆仍属本公开涵盖的范围内。本领域技术人员在考虑说明书及实践这里的公开后,将容易想到本公开的其他实施方案。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未记载的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的范围和精神由权利要求限定。

49.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行详细描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

50.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。