1.本发明涉及一种改进型数字滤波处理电路。

背景技术:

2.信号在传输过程中,由于受到空间噪声的干扰,ad采集的数据会存在较大的测量误差,且方差较大,而单纯应用求和取平均值这种简单的数据处理方式不足以消除此类测量误差,进而无法保证整个系统的测量精度要求。随着高精度ad转换电路的普遍应用,这类问题变得越来越重要,亟需有效的数据处理方式。

技术实现要素:

3.本发明的技术解决问题是:针对现有ad测量手段的不足,提供一种改进型数字滤波处理电路,实现了对ad采集数据进行数据处理的功能,采用分组重叠处理机制进行预处理,对处理后的数据进行冒泡排序,最后取中位数输出的方案。有效提升ad采集数据的测量精度,改善了整个ad测量系统的性能。

4.本发明的技术解决方案是:

5.一种改进型数字滤波处理电路,用于对ad采集的数据进行处理,包括:ad数据采集模块、ad数据处理核心模块、ad数据存储模块;

6.所述ad数据采集模块采用有限状态机技术,按照ad器件的时序关系,输出各控制信号,对ad器件进行控制,将采集到的ad数据,利用有限状态机写入ad数据存储模块;

7.所述ad数据处理核心模块根据所述ad数据采集模块采集到并存入ad数据存储模块的ad采集数据,对之进行数据处理,并将处理结果输出;

8.所述ad数据存储模块根据ad数据采集模块和ad数据处理核心模块的控制信号,对ad采集数据进行临时存储。

9.进一步的,所述数字滤波处理电路基于fpga实现。

10.进一步的,ad数据处理核心模块采用分组重叠处理机制对存储的数据进行预处理。

11.进一步的,采用分组重叠处理机制对存储的数据进行预处理是指:ad数据处理核心模块对ad数据存储模块存储的数据进行分组,以固定数量重叠读取不同地址上的数据,用于后续冒泡算法进一步处理。

12.进一步的,ad数据处理核心模块从ad数据存储模块分别依次递增读取相应地址数据,分组读取地址a0—a

m-1

、an—a

m n-1

、a

2n

—a

m 2n-1

、a

3n

—a

m 3n-1、...,依此类推,将读取的固定m个数据进行存储;其中参数m表示分组重叠处理机制输出的数据固定个数,n表示除第一次以外,后续每次读取的数据个数。

13.进一步的,m、n的数量关系为n《m《2n。

14.进一步的,ad数据处理核心模块采用冒泡排序方法对分组重叠后的数据进行处理。

15.进一步的,ad数据处理核心模块从ad数据存储模块读取地址为b0和b1的数据,读取的数据分别为d0和d1:

16.如果d0》d1,则将d0与d1分别写回b0和b1;

17.如果d0≤d1,则将d0与d1分别写回b1和b0,即交换这两个地址的存储数据;之后,读取b1和b2的数据d1和d2;

18.如果d1》d2,则将d1与d2分别写回b1和b2;

19.如果d1≤d2,则将d1与d2分别写回b2和b1;

20.以此类推,实现整个采集数据序列的排序。

21.进一步的,假设一共有n个采集数据,那么经过n*(n-1)/2次比较之后,即可实现整个采集数据序列的排序。

22.进一步的,排序完成之后,读取a

n/2

或者a

(n 1)/2

得到数据d

n/2

或者d

(n 1)/2

,即排序之后序列的中位数,将此数据输出,作为数据处理的最终结果。

23.本发明与现有技术相比具有如下优点:

24.(1)本发明根据信号特点和ad采样率,选择合适的m值,采用本发明描述的技术,可以有效地滤除信号传输过程中的噪声毛刺,与现有技术对比,由于采用了采样数据分组重叠处理机制,使得处理后的相邻数据差值变小,还原后的波形更加平滑,波形还原度高。

25.(2)本发明在ad采集量测量值方差很大的情况下,应用排序取中位数的处理方法,可得到最接近实际值的ad采集数字量。逻辑电路采用流水线结构,处理延时小,不会影响整个测量系统的数据处理能力。

26.(3)本发明电路基于fpga内置的存储器,在处理ad采集数据时,可从存储器中读取出测量数据,经过比较处理后,再分别写回存储器,该方案只要保证存储器容量足够,可在对逻辑电路设计不做变动的同时,通过配置缓存容量参数,提升最后的处理精度。

27.(4)为了提升逻辑电路的可靠性、硬件描述语言的可读性以及整个模块的可扩展性,本发明采用了有限状态机的实现方式作为电路的主干结构。采用这种实现方式后,硬件描述代码清晰易读,可扩展性大大增强。

28.(5)本发明从fpga资源占用和处理速度两方面进行权衡,选用冒泡排序作为数据排序的主要算法。排序模块主时钟频率为50mhz,经计算,处理时间不会对数据采集模块造成影响。

附图说明

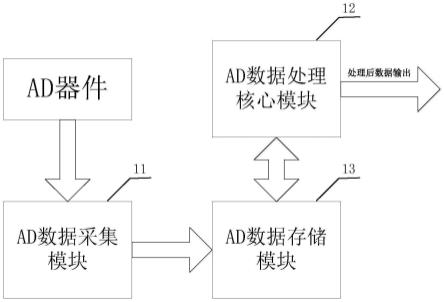

29.图1为本发明逻辑电路模块示意图;

30.图2为现有技术与本发明分组取值范围对比;

31.图3为ad数据分组重叠处理示意图;

32.图4为ad数据冒泡处理示意图。

具体实施方式

33.下面就结合附图对本发明做进一步介绍。

34.如图1所示,本发明提出一种改进型数字滤波处理电路,该数字滤波处理电路基于fpga实现,该电路包括:ad数据采集模块11、ad数据处理核心模块12、ad数据存储模块13。

35.本逻辑电路主要用于对采集到的ad数字量进行数据处理,利用所述ad数据采集模块11对转换后的ad数字量进行采集,并利用有限状态机将采集到的ad数字量写入fpga内部ram存储器。由所述ad数据处理核心模块12进行处理,最后将数据处理得到的数值输出。

36.所述ad数据采集模块11采用有限状态机技术,按照ad器件的时序关系,输出各控制信号,对ad器件进行控制,将采集到的ad数据,利用有限状态机写入ad数据存储模块13;

37.所述ad数据处理核心模块12根据所述ad数据采集模块11采集到并存入ad数据存储模块13的ad采集数据,ad数据处理核心模块采用分组重叠处理机制对存储的数据进行预处理,并将处理结果输出;

38.所述ad数据存储模块13根据ad数据采集模块11和ad数据处理核心模块12的控制信号,对ad采集数据进行临时存储。

39.图2所示为现有技术与本发明分组取值范围对比情况,左侧示意了现有技术对采样数据的分组取值范围情况,各分组取值相对独立,右侧为本发明的数据分组取值情况,各分组取值有部分重叠,即分组重叠数据处理。

40.故采用分组重叠处理机制对存储的数据进行预处理是指:ad数据处理核心模块对ad数据存储模块存储的数据进行分组,以固定数量重叠读取不同地址上的数据,用于后续冒泡算法进一步处理。

41.进一步如图3所示,该发明逻辑电路基于fpga,从面积与性能两方面权衡,ad数据处理核心模块采用分组重叠处理机制对ad采集存储的数据进行处理,ad数据处理模块从ad数据存储模块分别读取a0—a

m-1

、an—a

m n-1

、a

2n

—a

m 2n-1

、a

3n

—a

m 3n-1.......等依次类推地址上的数据,将读取的固定m个数据进行存储,并输出做冒泡处理。

42.其中参数m表示分组重叠处理机制输出的数据固定个数,n表示除第一次以外,后续每次读取的数据个数。m、n的数量关系n《m《2n。

43.假设m=15,n=10,如图3所示,第一次分组读取地址a0—a

14

,将读出的15个数据输出至后续冒泡处理,第二次分组读取地址a

15

—a

24

,将读出的10个数据,加上第一组读取的后5个数据,组成新的15个数据输出至后续冒泡处理,第三次分组读取地址a

25

—a

34

,将读出的10个数据,加上第二组读取的后5个数据,组成新的15个数据输出至后续冒泡处理,依次类推,以上三次读出的数据对应的地址范围分别为a0—a

14

、a

10

—a

24

、a

20

—a

34

,与上述分组重叠处理机制所列公式一致。因此,此方法具有一定的通用性。

44.如图4所示,ad数据处理核心模块冒泡排序方法对分组重叠处理后的数据进行处理。ad数据处理模块从ad数据存储模块读取地址为b0和b1的数据,读取的数据分别为d0和d1:如果d0》d1,则将d0与d1分别写回b0和b1;如果d0≤d1,则将d0与d1分别写回b1和b0,即交换这两个地址的存储数据。之后,读取b1和b2的数据d1和d2,如果d1》d2,则将d1与d2分别写回b1和b2;如果d1≤d2,则将d1与d2分别写回b2和b1。

45.以此类推,假设一共有n个采集数据,那么经过n*(n-1)/2次比较之后,即可实现整个采集数据序列的排序。

46.排序完成之后,读取a

n/2

或者a

(n 1)/2

得到数据d

n/2

或者d

(n 1)/2

,即排序之后序列的中位数。将此数据输出,作为数据处理的最终结果。

47.实施例

48.本发明的ad数据存储模块13中的存储器ram采用1k

×

16位的fpga内部block ram,

存储模块13对ad数据采集模块11采集到的数据进行临时存储,该1k容量大小可通过修改参数进行更改。理论上采集的数据越多,处理后的精度越高,但同时处理所需时间也会变长,降低整个数据处理模块的性能。

49.主频率时钟采用50mhz,周期为20ns。一次数据读取加上比较时间大概为10个时钟周期200ns,设采样n个数据进行处理,则整个比较过程耗时大概为100*n*(n-1)ns。

50.本发明未详细说明部分属本领域技术人员公知常识。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。