cht技术处理器电源管理设计架构

技术领域

1.本发明涉及集成电路领域,特别是cht技术(单发射多线程动态循环并行技术,以下简称cht技术)处理器soc设计和实现方法。

背景技术:

2.集成电路行业受到重点扶持。处理器的体系结构是构建处理器的基础,常见的体系结构大多是国外的体系结构,如x86体系结构、arm体系结构等。应用这些体系结构存在较多的限制,所以需要新型体系结构。新型体系结构技术是自主可控、安全可靠国产处理器的核心,也是难点所在。当前,体系结构技术创新成果较少,需求迫切,有重大的战略地位和广阔的市场空间;与之配套的soc技术体系,同样具有重要意义。

3.现有的处理器电源管理方案一般是通过应用层面实现对电源的管理,无法满足mbist测试(memory build-in-selftest,存储器内建自测试)需求和低功耗需求。

技术实现要素:

4.本发明的目的是:发明一种适用于cht技术处理器的电源管理方法,满足超低功耗需求和mbist测试需求(如cht dft flow需求),本发明旨在实现深层次电源管理策略,而非应用层面的(如dvfs方案)电源管理策略,特别对轻量化低功耗(如物联网)处理器具有重要应用价值。本发明技术对cht技术处理器设计具有重要指导意义,同样适应于普通架构处理器,因此对通用处理器设计具有重要指导意义。

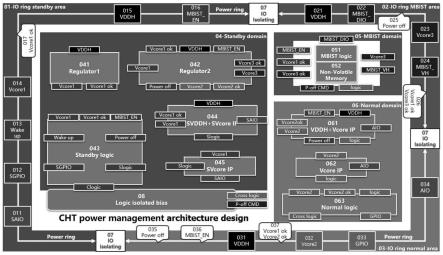

5.本发明提供cht技术处理器电源管理设计架构,所述电源管理设计架构包括:待机区io环、测试区io环、标准区io环、待机域、测试域和标准域;

6.所述待机区io环连接到模拟io端、通用数字io端、唤醒信号端、第一核心电压端,外部io域高压供电端、测试使能端和第一核心电压上电完标识;

7.所述测试区io环连接到外部io域高压供电端、测试数字io端、第三核心电压端、测试高压供电端、掉电信号端、第一核心电压上电完标识和第三核心电压上电完标识;

8.所述标准区io环连接到外部io域高压供电端、第二核心电压端、通用数字io端、模拟io端、掉电信号端、测试使能端、第一核心电压上电完标识和第三核心电压上电完标识;

9.所述待机域包括第一电压调节器、第二电压调节器、待机域逻辑、双压供电ip单元、核心电压ip单元;

10.所述的标准域包括标准域双压供电ip单元、待机域双压供电ip单元和标准域逻辑;

11.所述测试域包含测试域逻辑和非易失存储器,所述测试域逻辑连接到所述第一核心电压上电完标识、第三核心电压端、第三核心电压上电完标识,所述测试域逻辑连接到测试io口和测试使能端;所述测试使能端生效时,第二核心电压端关闭、第二核心电压上电完标识生效以及所述测试域逻辑进入测试状态。

12.进一步地,所述设计架构的内部接口信息包括:

13.所述的第一电压调节器连接到外部io域高压供电端、第一核心电压端和第一核心电压上电完标识;

14.所述的第二电压调节器连接到外部io域高压供电端、第一核心电压端、第一核心电压上电完标识、掉电信号端、测试使能端、第二核心电压端、第三核心电压上电完标识、第三核心电压端和第三核心电压上电完标识。

15.进一步地,还包括io隔离区,所述的待机区io环、测试区io环、标准区io环之间通过io隔离区进行隔离。

16.进一步地,所述的待机区io环连接到模拟io口、通用io口、唤醒信号端、第一核心电压端、外部io域高压供电端、测试使能端,并采用所述的第一核心电压上电完标识来进行上电偏置和掉电偏置;待机区io环的最小系统包括:唤醒信号端、外部io域高压供电端、测试使能端和第一核心电压上电完标识。

17.进一步地,所述的测试区io环连接到所述的外部io域高压供电端、测试数字io端、第三核心电压端、测试高压供电端,并采用掉电信号端、第一核心电压上电完标识和第三核心电压上电完标识来进行上电偏置和掉电偏置,所述的测试区io环的最小系统包括:测试数字io端、测试高压供电端、掉电信号端和第三核心电压上电完标识。

18.进一步地,所述的标准区io环包括所述的外部io域高压供电端、第二核心电压端、通用io端、模拟io端,并采用掉电信号端、测试使能端、第一核心电压上电完标识和第二核心电压上电完标识进行上电偏置和掉电偏置;所述的测试区io环的最小系统包括:通用io端、掉电信号端、测试使能端和第二核心电压上电完标识。

19.进一步地,处理器芯片内部电路切割成为:所述的待机域、测试域和标准域,跨域逻辑交互信号经过隔离偏置逻辑部来隔离偏置。

20.进一步地,所述的待机域还包括待机逻辑部、待机域双压供电ip单元、待机域核心供电ip单元,对外采用所述的待机区io环进行沟通,对内采用所述的隔离偏置逻辑部沟通;所述的第二电压调节器分成部分,如vcore2输出一路,vcore3输出另一路;所述的待机域的最小系统包括:第一电压调节器、第二电压调节器和待机逻辑部。

21.进一步地,所述的测试域包括所述的测试域逻辑、非易失存储器,对外采用所述的测试区io环沟通,对内采用所述的隔离偏置逻辑部沟通。

22.进一步地,所述的标准域包括所述的标准域双压供电ip单元、标准域核心供电ip单元、标准域逻辑,对外采用所述的标准区io环沟通,对内采用所述的隔离偏置逻辑部沟通;所述的标准域的最小系统包括:标准域逻辑。

23.进一步地,所述的测试域与标准域通过测试逻辑块和标准域逻辑的逻辑网络进行直接逻辑沟通。

24.进一步地,所述的隔离偏置逻辑部是跨域逻辑沟通的核心所在,所述的io隔离是io电路分割核心所在,以上两部分专为隔离偏置设计。

25.进一步地,所述的测试使能端用于与卡针连接。

26.综上所述,本发明实施的有益效果是:

27.1、创造了一种适用于cht技术处理器的电源管理方法;

28.2、发明了一种全新的电源管理技术,满足超低功耗需求和mbist测试需求(如cht dft flow需求),;

29.3、实现深层次电源管理策略,而非应用层面的(如dvfs方案)电源管理策略;

30.4、特别对轻量化低功耗(如物联网)处理器具有重要应用价值;

31.5、对cht技术处理器设计具有重要指导意义,基于cht技术特点,相得益彰、相辅相成;

32.6、同样适应于普通架构处理器,因此对通用处理器设计具有重要指导意义。

附图说明

33.图1绘示为cht技术处理器电源管理设计架构构成框图。

34.图2绘示为本发明技术中不测试内部电压的mbist时序分析。

35.图3绘示为本发明技术中测试内部电压的方法一mbist时序分析。

36.图4绘示为本发明技术中测试内部电压的方法二mbist时序分析。

37.图5绘示为本发明技术中低功耗模式的时序分析。

38.图6绘示为本发明技术中powertree分析。

39.图7绘示为本发明技术中resettree分析。

40.图8绘示为本发明技术中上电和关电偏置细节分析。

41.图9绘示为本发明技术中低功耗关电偏置细节分析。

42.图10绘示为本发明技术中隔离偏置方法。

43.图11绘示为本发明技术中mbist关电偏置细节分析。

44.图12绘示为本发明技术中mbist供电方法一流程。

45.图13绘示为本发明技术中mbist供电方法二流程。

46.图14绘示为本发明技术中低功耗关电现场保存还原框架。

47.图15绘示为本发明技术中低功耗关电现场保存还原流程。

具体实施方式

48.下面结合附图对本发明作进一步详细的说明。

49.本发明创造了一种适用于cht技术处理器的电源管理方法,发明了一种全新的电源管理技术。本发明技术满足超低功耗需求和mbist测试需求(如cht dft flow需求),本发明旨在实现深层次电源管理策略,而非应用层面的(如dvfs方案)电源管理策略,特别对轻量化低功耗(如物联网)处理器具有重要应用价值。本发明技术对cht技术处理器设计具有重要指导意义,同样适应于普通架构处理器,因此对通用处理器设计具有重要指导意义。

50.如图1所示,整个技术体系架构包括:

51.[0052][0053]

内部接口信息具体为:

[0054]

[0055]

[0056]

[0057][0058]

上述名称相同的信号(或网络),彼此连接,形成固有的连接关系。

[0059]

如图2所示,为本发明技术中不测试内部电压的mbist时序分析,依据流程,具体实现如下:

[0060]

s1:外部开始供电(vddh开始供电),内部处于高阻态(z);

[0061]

s2:vcore1开始set up并完成,vcore2和vcore3此时会被压制(0),无输出;vcore1 ok(第一核心电压上电完标识)输出生效(0),准备复位vcore1负载,vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)此时可为不定态(x),也可压制输出生效(0),若输出生效(0)则026-vcore1ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识),037-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识)可变成026-vcore3 ok(第三核心电压上电完标识),037-vcore3 ok(第三核心电压上电完标识);

[0062]

s3:vcore1输出正常,开始复位其负载,负载会出现短暂的不定态(x),直到复位完成;vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0);power_off和mbist_en(测试使能端)处于无效状态(invalid);vcore1 ok(第一核心电压上电完标识)输出无效(1);

[0063]

s4:vcore2、vcore3开始set up并完成;

[0064]

s5:vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0),复位vcore2、vcore3负载;

[0065]

s6:复位完成,进入正常工作状态;

[0066]

s7:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最大值,一般为1.1*vcore3;

[0067]

s8:开启mbist测试(cp测试),由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)生效,分别为:

[0068]

(1)来自于外部管脚,016-mbist_en(测试使能端);

[0069]

(2)来自于外部通信,022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)(p-offcmd)、08-isolated bias circuit、043-standby logic(待机逻辑部);

[0070]

这种情况可直接由p-offcmd致power off(掉电信号端)生效,因此,mbist_en(测试使能端)也可省略;

[0071]

vcore2关闭和vcore3 ok(第三核心电压上电完标识)生效;关闭内部vcore3,完全由外部控制;

[0072]

s9:测试完成,外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最小值,一般为0.9*vcore3;

[0073]

s10:由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)无效;

[0074]

这种情况可直接由p-offcmd致power off(掉电信号端)无效,因此,mbist_en(测试使能端)也可省略;

[0075]

vcore2开启上电,并由vcore3 ok(第三核心电压上电完标识)复位所有负载;

[0076]

s11:回到正常工作状态。

[0077]

如图3所示,为本发明技术中测试内部电压的方法一mbist时序分析,依据流程,具体实现如下,

[0078]

s1:外部开始供电(vddh开始供电),内部处于高阻态(z);

[0079]

s2:vcore1开始set up并完成,vcore2和vcore3此时会被压制(0),无输出;vcore1 ok(第一核心电压上电完标识)输出生效(0),准备复位vcore1负载,vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)此时可为不定态(x),也可压制输出生效(0),若输出生效(0)则026-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识),037-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识)可变成026-vcore3 ok(第三核心电压上电完标识),037-vcore3 ok(第三核心电压上电完标识);

[0080]

s3:vcore1输出正常,开始复位其负载,负载会出现短暂的不定态(x),直到复位完成;vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0);power_off和mbist_en(测试使能端)处于无效状态(invalid);vcore1 ok(第一核心电压上电完标识)输出无效(1);

[0081]

s4:vcore2、vcore3开始set up并完成;

[0082]

s5:vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0),复位vcore2、vcore3负载;

[0083]

s6:复位完成,进入正常工作状态;vcore1、vcore3可在此期间测量,测量电流比较大,会影响测量精度,可考虑增加卡针位,但会增加成本;

[0084]

s7:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最大

值,一般为1.1*vcore3;

[0085]

s8:开启mbist测试(cp测试),由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)生效,分别为:

[0086]

(1)来自于外部管脚,016-mbist_en(测试使能端);

[0087]

(2)来自于外部通信,022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)(p-offcmd)、08-isolated bias circuit、043-standby logic(待机逻辑部);

[0088]

这种情况可直接由p-offcmd致power off(掉电信号端)生效,因此,mbist_en(测试使能端)也可省略;

[0089]

vcore2关闭和vcore3 ok(第三核心电压上电完标识)生效;关闭内部vcore3,完全由外部控制;

[0090]

s9:测试完成,外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最小值,一般为0.9*vcore3;

[0091]

s10:由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)无效;

[0092]

这种情况可直接由p-offcmd致power off(掉电信号端)生效,因此,mbist_en(测试使能端)也可省略;

[0093]

vcore2开启上电,并由vcore3 ok(第三核心电压上电完标识)复位所有负载;

[0094]

s11:回到正常工作状态。

[0095]

如图4所示,为本发明技术中测试内部电压的方法二mbist时序分析,依据流程,具体实现如下:

[0096]

s1:外部开始供电(vddh开始供电),内部处于高阻态(z);

[0097]

s2:vcore1开始set up并完成,vcore2和vcore3此时会被压制(0),无输出;vcore1 ok(第一核心电压上电完标识)输出生效(0),准备复位vcore1负载,vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)此时可为不定态(x),也可压制输出生效(0),若输出生效(0)则026-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识),037-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识)可变成026-vcore3 ok(第三核心电压上电完标识),037-vcore3 ok(第三核心电压上电完标识);

[0098]

s3:vcore1输出正常,开始复位其负载,负载会出现短暂的不定态(x),直到复位完成;vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0);power_off和mbist_en(测试使能端)处于无效状态(invalid);vcore1 ok(第一核心电压上电完标识)输出无效(1);

[0099]

s4:vcore2、vcore3开始set up并完成;

[0100]

s5:vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0),复位vcore2、vcore3负载;

[0101]

s6:复位完成,进入正常工作状态;

[0102]

s7:开启mbist测试(cp测试),由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)生效,分别为:

[0103]

(1)来自于外部管脚,016-mbist_en(测试使能端);

[0104]

(2)来自于外部通信,022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)(p-offcmd)、08-isolated bias circuit、043-standby logic(待机逻辑部);

[0105]

vcore2关闭和vcore3 ok(第三核心电压上电完标识)生效;vcore1、vcore3可在此期间测量,测量电流适中,测量精度高;

[0106]

s8:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最大值,一般为1.1*vcore3;

[0107]

s9:由p-offcmd致power off(掉电信号端)生效,关闭内部vcore3,完全由外部控制;;

[0108]

s10:测试完成,外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最小值,一般为0.9*vcore3;

[0109]

s11:由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)无效;由p-offcmd致poweroff(掉电信号端)生效;

[0110]

vcore2开启上电,并由vcore3 ok(第三核心电压上电完标识)复位所有负载;

[0111]

s12:回到正常工作状态。

[0112]

如图5所示,为本发明技术中低功耗模式的时序分析,依据流程,具体实现如下,

[0113]

s1:外部开始供电(vddh开始供电),内部处于高阻态(z);

[0114]

s2:vcore1开始set up并完成,vcore2和vcore3此时会被压制(0),无输出;vcore1 ok(第一核心电压上电完标识)输出生效(0),准备复位vcore1负载,vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)此时可为不定态(x),也可压制输出生效(0),若输出生效(0)则026-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识),037-vcore1 ok(第一核心电压上电完标识)&vcore3 ok(第三核心电压上电完标识)可变成026-vcore3 ok(第三核心电压上电完标识),037-vcore3 ok(第三核心电压上电完标识);

[0115]

s3:vcore1输出正常,开始复位其负载,负载会出现短暂的不定态(x),直到复位完成;vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0);power_off和mbist_en(测试使能端)处于无效状态(invalid);vcore1 ok(第一核心电压上电完标识)输出无效(1);

[0116]

wake up(唤醒信号端)此时状态不影响后续状态推进;

[0117]

s4:vcore2、vcore3开始set up并完成;

[0118]

s5:vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0),复位vcore2、vcore3负载;

[0119]

s6:vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出无效(1)复位完成,进入正常工作状态;

[0120]

s7:开启低功耗模式(power off(掉电信号端)状态),由cross logic使power off(掉电信号端)生效,vcore2、vcore3关闭输出,vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0);此时,外部保障wake up(唤醒信号端)无效;

[0121]

s8:进入到低功耗模式(power off(掉电信号端)状态),此时,系统电流可低至1ua以内;

[0122]

s9:外部wake up(唤醒信号端)生效,清除power off(掉电信号端)状态;

[0123]

s10:内部开始复苏,vcore2、vcore3重新上电;

[0124]

s11:vcore2、vcore3负载由vcore3 ok(第三核心电压上电完标识)、vcore3 ok(第三核心电压上电完标识)输出生效(0)来完成复位;此时,外部wake up(唤醒信号端)可随意撤销;

[0125]

s12:回到正常工作状态。

[0126]

如图6所示,本发明技术中电源树关系梳理,按照vcore电压供电关系,分成三部分:

[0127]

(1)standby domain(待机域),vcore1供电网相关部件,包括:011-saio、012-sgpio、013-wake up(唤醒信号端)、014-vcore1、016-mbist_en(测试使能端)、041-regulator1(第一电压调节器)、043-standby logic(待机逻辑部)、044-svddh svcore ip(待机域双压供电ip单元)、045-svcore ip(待机域供电ip单元);

[0128]

(2)normal domain(标准域),vcore2供电网相关部件,包括:042-regulator2(第二电压调节器)、032-vcore2(第二核心电压端)、033-gpio(通用io端)、034-aio(模拟io端)、061-vddh vcore ip(标准域双压供电ip单元)、062-vcore ip(标准域核供电ip单元)、063-normal logic(标准域逻辑);

[0129]

(3)mbist domain(测试域),vcore3供电网相关部件,包括:042-regulator2(第二电压调节器)、022-mbist_dio(测试数字io端)、023-vcore3(第三核心电压端)、024-mbist_vh(测试高压供电端)、051-mbist logic(测试域逻辑)、052-non-volatile memory(非易失存储器);

[0130]

如图7所示,本发明技术中复位树关系梳理,按照vcore ok负载关系,分成三部分:

[0131]

(1)vcore1 ok(第一核心电压上电完标识),负载包括:043-standby logic(待机逻辑部)、044-svddh svcore ip(待机域双压供电ip单元)、052-non-volatile memory(非易失存储器);

[0132]

(2)vcore3 ok(第三核心电压上电完标识),负载包括:061-vddh vcore ip(标准域双压供电ip单元)、063-normal logic(标准域逻辑);

[0133]

(3)vcore3 ok(第三核心电压上电完标识),负载包括:051-mbist logic(测试域逻辑)、052-non-volatile memory(非易失存储器);

[0134]

其中052-non-volatile memory(非易失存储器)同时受vcore1 ok(第一核心电压上电完标识)和vcore3 ok(第三核心电压上电完标识)控制,保障上电过程中,052-non-volatile memory(非易失存储器)内部数据的绝对安全。

[0135]

如图8所示,本发明技术中上电和关电偏置细节分析,按照vcore ok负载关系,分成三部分:

[0136]

(1)vcore1 ok(第一核心电压上电完标识),负载包括:012-sgpio、013-wake up(唤醒信号端)、016-mbist_en(测试使能端)、044-svddh svcore ip(待机域双压供电ip单元)、033-gpio(通用io端)、022-mbist_dio(测试数字io端);

[0137]

(2)vcore3 ok(第三核心电压上电完标识),负载包括:033-gpio(通用io端)、061-vddh vcore ip(标准域双压供电ip单元);

[0138]

(3)vcore3 ok(第三核心电压上电完标识),负载包括:022-mbist_dio(测试数字

io端);

[0139]

其中vcore1 ok(第一核心电压上电完标识)驱动033-gpio(通用io端)和022-mbist_dio(测试数字io端)的目的是保障内部上电的绝对安全。

[0140]

如图9所示,本发明技术中低功耗关电偏置细节分析,低功耗(low power)模式下vcore2和vcore3关闭,主要关电负载有:042-regulator2(第二电压调节器)、033-gpio(通用io端)、061-vddh vcore ip(标准域双压供电ip单元)、062-vcore ip(标准域核心供电ip单元)、063-normal logic(标准域逻辑)、022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)、052-non-volatile memory(非易失存储器);

[0141]

如采用vddh和vcore供电,当vcore关闭,则需要power off(掉电信号端)信号偏置,类似负载有:042-regulator2(第二电压调节器)、033-gpio(通用io端)、061-vddh vcore ip(标准域双压供电ip单元)、022-mbist_dio(测试数字io端);

[0142]

同时,08-logic isolatedbias(隔离偏置逻辑部)对跨域信号隔离偏置,抑制漏电流。

[0143]

如图10所示,本发明技术中隔离偏置方法。图示了043-standby logic(待机逻辑部)与063-normal logic(标准域逻辑)交互的场景。

[0144][0145]

如图11所示,本发明技术中mbist关电偏置细节分析,mbist测试模式下vcore2,主要关电负载有:042-regulator2(第二电压调节器)、033-gpio(通用io端)、061-vddh vcore ip(标准域双压供电ip单元)、062-vcore ip(标准域核心供电ip单元)、063-normal logic(标准域逻辑);

[0146]

如采用vddh和vcore供电,当vcore关闭,则需要mbist_en(测试使能端)信号偏置,类似负载有:042-regulator2(第二电压调节器)、033-gpio(通用io端)、061-vddh vcore ip(标准域双压供电ip单元);

[0147]

同时,08-logic isolatedbias(隔离偏置逻辑部)对跨域信号隔离偏置,抑制漏电流。

[0148]

mbist_en(测试使能端)有两种方法:

[0149]

(1)来自于外部管脚,016-mbist_en(测试使能端);

[0150]

(2)来自于外部通信,022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)、08-isolatedbias circuit、043-standby logic(待机逻辑部),如图虚线框所示;

[0151]

如图12所示,本发明技术中mbist供电方法一流程,具体实现如下:

[0152]

s1:外部vddh供电,系统开始上电;

[0153]

s2:内部执行上电(power on)流程;

[0154]

s3:直到内部上电完成;

[0155]

s4:开启正常工作状态;

[0156]

s5:开启mbist测试(cp测试),由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)生效,分别为:

[0157]

(1)来自于外部管脚,016-mbist_en(测试使能端);

[0158]

(2)来自于外部通信,022-mbist_dio(测试数字io端)、051-mbist logic(测试域逻辑)(p-offcmd)、08-isolated bias circuit、043-standby logic(待机逻辑部);

[0159]

s6:vcore2关闭和vcore3 ok(第三核心电压上电完标识)生效;

[0160]

s7:vcore1、vcore3可在此期间测量,测量电流适中,测量精度高;

[0161]

s8:完成测量;

[0162]

s9:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最大值,一般为1.1*vcore3;

[0163]

s10:毫秒级延时,以便内部1.1*vcore3稳定下来;

[0164]

s11:由p-offcmd致power off(掉电信号端)生效,

[0165]

s12:关闭内部vcore3,完全由外部控制;

[0166]

s13:进入mbist测试流程;

[0167]

s14:直到测试完成,

[0168]

s15:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最小值,一般为0.9*vcore3;

[0169]

s16:由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)无效;由p-offcmd致poweroff(掉电信号端)生效;

[0170]

vcore2开启上电,并由vcore3 ok(第三核心电压上电完标识)复位所有负载;

[0171]

s17:回到正常工作状态。

[0172]

如图13所示,本发明技术中mbist供电方法二流程,具体实现如下:

[0173]

s1:外部vddh供电,同时,016-mbist_en(测试使能端)生效,023-vcore3(第三核心电压端)测试电压生效,此时,外部施加vcore3只要在安全范围,不需要固定偏向于最高值;

[0174]

s2:内部执行上电(power on)流程;

[0175]

s3:直到内部上电完成;此时,会自动切换到mbist测试状态;

[0176]

s4:进入到mbist流程;

[0177]

s5:直到测试完成;

[0178]

s15:外部电压供给,施加于023-vcore3(第三核心电压端),大小为核电压的最小值,一般为0.9*vcore3;

[0179]

s16:由p-offcmd或者016-mbist_en(测试使能端)导致mbist_en(测试使能端)无效;由p-offcmd致poweroff(掉电信号端)生效;

[0180]

vcore2开启上电,并由vcore3 ok(第三核心电压上电完标识)复位所有负载;

[0181]

s17:回到正常工作状态。

[0182]

注意:这种供电方式,一般不支持内部电压测量,至少不支持vcore3测量。

[0183]

图14所示,本发明技术中低功耗关电现场保存还原框架。包括:013-wake up(唤醒

信号端)、043-standby logic(待机逻辑部)、033-gpio(通用io端)、063-normal logic(标准域逻辑)、052-non-volatile memory(非易失存储器),08-isolatedbias circuit;

[0184]

其中,043-standby logic(待机逻辑部)一般为combinatorial or low speed logic;033-gpio(通用io端)用于用户指令操作(user configuration operation),例如,对052-non-volatile memory(非易失存储器)的控制,与063-normal logic(标准域逻辑)交互,可以是通用协议和自定义协议;033-gpio(通用io端)能发起保存现场指令;013-wake up(唤醒信号端)用于唤醒,能发起还原现场指令。

[0185]

如图15所示,本发明技术中低功耗关电现场保存还原流程,具体实现如下:

[0186]

s1:通过外部操作,施加033-gpio(通用io端),通过063-normal logic(标准域逻辑),固化低功耗控制程序到052-non-volatile memory(非易失存储器);

[0187]

s2:有两种操作方式:

[0188]

(1)软件操作:跳转到指定程序空间(提前固化保存函数);

[0189]

(2)硬件操作:启动power off(掉电信号端)硬件写存储,保存现场;

[0190]

s3:数据保存到non-volatile memory(非易失存储器)指定位置;

[0191]

s4:直到保存完成

[0192]

s5:soc正式进入power off(掉电信号端)状态;

[0193]

s6:外部013-wake up(唤醒信号端)启动唤醒流程;

[0194]

s7:依据唤醒方式判断是不是启动还原;

[0195]

(1)若启动还原则跳转到s8;

[0196]

(2)若不还原则跳转到s12;

[0197]

s8:有两种操作方式:

[0198]

(1)软件操作:跳转到指定程序空间(提前固化还原函数);

[0199]

(2)硬件操作:启动power off(掉电信号端)硬件读存储,还原现场;

[0200]

s9:从non-volatile memory(非易失存储器)指定位置读取;

[0201]

s10:直到还原完成;

[0202]

s11:继续上一次power off(掉电信号端)位置继续执行;

[0203]

s12:启动程序初始化执行流程。

[0204]

需要说明的是,尽管在本文中已经对上述各实施例进行了描述,但并非因此限制本发明的专利保护范围。因此,基于本发明的创新理念,对本文所述实施例进行的变更和修改,或利用本发明说明书及附图内容所作的等效结构或等效流程变换,直接或间接地将以上技术方案运用在其他相关的技术领域,均包括在本发明专利的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。