技术特征:

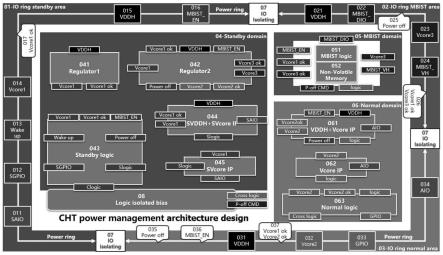

1.cht技术处理器电源管理设计架构,其特征在于:所述电源管理设计架构包括:待机区io环、测试区io环、标准区io环、待机域、测试域和标准域;所述待机区io环连接到模拟io端、通用数字io端、唤醒信号端、第一核心电压端,外部io域高压供电端、测试使能端和第一核心电压上电完标识;所述测试区io环连接到外部io域高压供电端、测试数字io端、第三核心电压端、测试高压供电端、掉电信号端、第一核心电压上电完标识和第三核心电压上电完标识;所述标准区io环连接到外部io域高压供电端、第二核心电压端、通用数字io端、模拟io端、掉电信号端、测试使能端、第一核心电压上电完标识和第三核心电压上电完标识;所述待机域包括第一电压调节器、第二电压调节器、待机域逻辑、双压供电ip单元、核心电压ip单元;所述的标准域包括标准域双压供电ip单元、待机域双压供电ip单元和标准域逻辑;所述测试域包含测试域逻辑和非易失存储器,所述测试域逻辑连接到所述第一核心电压上电完标识、第三核心电压端、第三核心电压上电完标识,所述测试域逻辑连接到测试io口和测试使能端;所述测试使能端生效时,第二核心电压端关闭、第二核心电压上电完标识生效以及所述测试域逻辑进入测试状态。2.根据权利要求1所述的cht技术处理器电源管理设计架构,其特征在于,所述设计架构的内部接口信息包括:所述的第一电压调节器连接到外部io域高压供电端、第一核心电压端和第一核心电压上电完标识;所述的第二电压调节器连接到外部io域高压供电端、第一核心电压端、第一核心电压上电完标识、掉电信号端、测试使能端、第二核心电压端、第三核心电压上电完标识、第三核心电压端和第三核心电压上电完标识。3.根据权利要求1或2所述的cht技术处理器电源管理设计架构,其特征在于,还包括io隔离区,所述的待机区io环、测试区io环、标准区io环之间通过io隔离区进行隔离。4.根据权利要求1至3任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的待机区io环连接到模拟io口、通用io口、唤醒信号端、第一核心电压端、外部io域高压供电端、测试使能端,并采用所述的第一核心电压上电完标识来进行上电偏置和掉电偏置;待机区io环的最小系统包括:唤醒信号端、外部io域高压供电端、测试使能端和第一核心电压上电完标识。5.根据权利要求1至3任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的测试区io环连接到所述的外部io域高压供电端、测试数字io端、第三核心电压端、测试高压供电端,并采用掉电信号端、第一核心电压上电完标识和第三核心电压上电完标识来进行上电偏置和掉电偏置,所述的测试区io环的最小系统包括:测试数字io端、测试高压供电端、掉电信号端和第三核心电压上电完标识。6.根据权利要求1至3任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的标准区io环包括所述的外部io域高压供电端、第二核心电压端、通用io端、模拟io端,并采用掉电信号端、测试使能端、第一核心电压上电完标识和第二核心电压上电完标识进行上电偏置和掉电偏置;所述的测试区io环的最小系统包括:通用io端、掉电信号端、测试使能端和第二核心电压上电完标识。

7.根据权利要求1或2所述的cht技术处理器电源管理设计架构,其特征在于,处理器芯片内部电路切割成为:所述的待机域、测试域和标准域,跨域逻辑交互信号经过隔离偏置逻辑部来隔离偏置。8.根据权利要求1、2、7任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的待机域还包括待机逻辑部、待机域双压供电ip单元、待机域核心供电ip单元,对外采用所述的待机区io环进行沟通,对内采用所述的隔离偏置逻辑部沟通;所述的第二电压调节器分成部分,如vcore2输出一路,vcore3输出另一路;所述的待机域的最小系统包括:第一电压调节器、第二电压调节器和待机逻辑部。9.根据权利要求1、2、7任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的测试域包括所述的测试域逻辑、非易失存储器,对外采用所述的测试区io环沟通,对内采用所述的隔离偏置逻辑部沟通。10.根据权利要求1、2、7任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的标准域包括所述的标准域双压供电ip单元、标准域核心供电ip单元、标准域逻辑,对外采用所述的标准区io环沟通,对内采用所述的隔离偏置逻辑部沟通;所述的标准域的最小系统包括:标准域逻辑。11.根据权利要求1、2、7任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的测试域与标准域通过测试逻辑块和标准域逻辑的逻辑网络进行直接逻辑沟通。12.根据权利要求1、2、7任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的隔离偏置逻辑部是跨域逻辑沟通的核心所在,所述的io隔离是io电路分割核心所在,以上两部分专为隔离偏置设计。13.根据权利要求1~12任意一项所述的cht技术处理器电源管理设计架构,其特征在于,所述的测试使能端用于与卡针连接。

技术总结

本发明涉及集成电路领域,特别是CHT技术(单发射多线程动态循环并行技术)处理器电源管理设计架构;本发明架构体系包括:待机区IO环、测试区IO环、标准区IO环、待机域、测试域和标准域。本发明创造了一种适用于CHT技术处理器的电源管理方法,发明了一种全新的电源管理设计架构。本发明技术满足超低功耗需求和MBIST测试需求(如CHTDFTFLOW需求),本发明旨在实现深层次电源管理策略,而非应用层面的(如DVFS方案)电源管理策略,特别对轻量化低功耗(如物联网)处理器具有重要应用价值。耗(如物联网)处理器具有重要应用价值。耗(如物联网)处理器具有重要应用价值。

技术研发人员:王杜

受保护的技术使用者:长沙方维科技有限公司

技术研发日:2022.10.20

技术公布日:2023/1/13

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。