ldmos架构及形成方法

1.相关申请

2.本技术要求2020年5月20日提交的题为“ldmos架构及形成方法(ldmos architecture and method for forming)”的美国非临时专利申请第16/879,046号的优先权,其出于所有目的通过引用方式并入本文。

背景技术:

3.金属氧化物场效晶体管(mosfet)通常包括多晶硅栅极、源极区域、漏极区域及沟道区域。源极区域及漏极区域具有第一导电性类型,而沟道区域具有第二导电性类型。在一些mosfet装置中,第一导电性类型是n型导电性,而第二导电性类型是p型导电性。在其他mosfet装置中,此关系是相反的。当mosfet装置处于导通状态时,响应于所施加的栅极电压,电流经由沟道区域在漏极区域与源极区域之间流动。当mosfet装置处于断开状态时,只要mosfet两端的反向偏置电压不超过击穿电压水平,电流就不会在漏极区域与源极区域之间流动。如果反向偏置电压超过击穿电压,则无论是否向栅极施加电压,大的不受控电流均可在源极区域与漏极区域之间流动。当反向偏置电压增加到击穿电压以上时,可发生雪崩击穿事件。在雪崩击穿事件期间,流过mosfet的电流以增加速率增加且可迅速超过mosfet的最大额定电流,从而可能损坏或破坏mosfet。

4.横向扩散mosfet(ldmos)是一类mosfet,其等另外包括横向漂移漏极(ldd)区域,以与典型mosfet的击穿电压相比增加击穿电压。ldd区域通过吸收电场的部分来允许ldmos在断开状态下承受更大电压,否则电场会导致mosfet击穿。

技术实现要素:

5.在一些示例中,一种用于形成半导体装置的方法涉及提供半导体晶片,所述半导体晶片具有衬底层及第一导电性类型的作用层。在所述作用层上形成第一栅极,所述第一栅极包括第一栅极多晶硅。在所述作用层上形成第二栅极,所述第二栅极从所述第一栅极横向安置且包括第二栅极多晶硅。在所述作用层上形成第一掩模区域。使用所述第一掩模区域、所述第一栅极多晶硅及所述第二栅极多晶硅作为掩模,在所述作用层中于所述第一栅极与所述第二栅极之间形成第二导电性类型的深阱、所述第二导电性类型的浅阱、所述第一导电性类型的源极区域及沟道区域,所述沟道区域被分割为所述第二导电性类型的第一沟道区域及所述第二导电性类型的第二沟道区域。使用一个或多个第二掩模区域,在所述作用层中形成所述第一导电性类型的第一漂移区域、所述第一导电性类型的第二漂移区域、所述第一导电性类型的第一漏极区域、所述第一导电性类型的第二漏极区域及所述第二导电性类型的源极连接区域。

6.在一些示例中,一种半导体装置包括半导体晶片,所述半导体晶片具有第一导电性类型的作用层。所述作用层包括第二导电性类型的深阱、所述第二导电性类型的浅阱、所述第一导电性类型的源极区域、所述第二导电性类型的第一沟道区域、所述第二导电性类型的第二沟道区域、所述第一导电性类型的第一漂移区域、所述第一导电性类型的第二漂

移区域、所述第一导电性类型的第一漏极区域、所述第一导电性类型的第二漏极区域及所述第二导电性类型的源极连接区域。所述半导体装置包括形成在所述作用层上方的第一栅极多晶硅。第一多晶硅栅极间隔物靠近所述第一栅极多晶硅横向安置。所述半导体装置包括形成在所述作用层上方的第二栅极多晶硅。第二多晶硅栅极间隔物靠近所述第二栅极多晶硅横向安置。所述源极连接区域横向安置在所述第一多晶硅栅极间隔物与所述第二多晶硅栅极间隔物之间。第一栅极屏蔽物形成在所述第一栅极多晶硅上方。第二栅极屏蔽物形成在所述第二栅极多晶硅上方。电介质区域形成在所述作用层上方。所述半导体装置包括金属源极触点,所述金属源极触点从所述电介质区域的顶部表面垂直延伸至所述源极连接区域,所述金属源极触点横向安置在所述第一多晶硅栅极间隔物与所述第二多晶硅栅极间隔物之间且具有沿所述金属源极触点的第一垂直范围的第一宽度,所述第一宽度宽于沿所述金属源极触点的第二垂直范围的第二宽度,所述金属源极触点的所述第一垂直范围的所述第一宽度与所述第一栅极屏蔽物横向重叠并接触。

附图说明

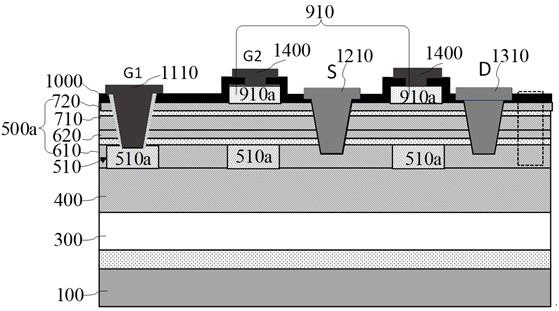

7.图1是根据一些实施方案的示例性ldmos装置的简化横截面图。

8.图2a至图2b是ldmos装置的现有技术示例。

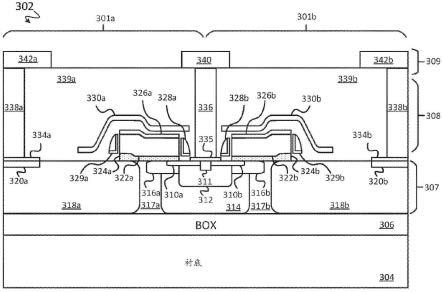

9.图3是根据一些实施方案的示例性ldmos装置的简化横截面图。

10.图4至图14是详述根据一些实施方案的用于形成图3中所示的ldmos装置的示例性过程的简化横截面图。

11.图15至图19b示出了根据一些实施方案的用于形成图3中所示的ldmos装置的示例性过程的一部分的简化步骤。

具体实施方式

12.与不具有轻掺杂漏极(ldd)区域的其他金属氧化物场效晶体管(mosfet)相比,横向扩散金属氧化物场效晶体管(ldmos)的ldd区域为ldmos装置提供了增加的击穿电压,代价是增加ldmos装置的导通电阻。ldd区域的导电性及ldd区域的长度各自分别与所述区域在电流流动方向上的阻抗成比例。因此,可通过减小ldd区域的掺杂水平或通过扩展ldd的横向范围来实现增加ldmos装置的击穿电压。此相互关系提出了困难设计问题,这是因为通常期望保持ldmos装置的导通状态电阻为低,或者当ldmos装置汲取功率装置(诸如ldmos装置)经常传导的大电流时,所述ldmos装置将消耗大量功率。

13.本文公开了一种半导体结构,所述半导体结构包括具有单个指状物或多个指状物的至少一个ldmos装置,与常规ldmos装置相比,所述至少一个ldmos装置有利地改进了几个关键特征。这些特征包括对过程差异的增强稳健性、与高电场及击穿条件相关的增强稳定性、与ldmos装置的用于源极/漏极电流的沟道区域的较低电阻连接,及/或在处置雪崩产生的少数载流子方面增加耐用性。与常规ldmos装置相比,本文公开的ldmos装置的额外优点包括归因于ldmos装置的源极区域的紧凑性而降低特定的rdson或rsp、提高可制造性的便利性;以及/或更低晶片成本。

14.与常规ldmos装置相比,图1示出了根据一些实施方案的横向扩散mosfet(ldmos)装置102的横截面的一部分,所述ldmos装置具有显著改进装置性能并减小制造差异的装置

架构。图1中已经省略了ldmos装置102的一些元件以简化对ldmos装置102的描述。一般而言,ldmos装置102是绝缘体上硅(soi)装置,其包括半导体晶片,所述半导体晶片包括衬底104、衬底104上的埋入式氧化物(box)层106(例如,sio2)及box层106上的作用层107。栅极及接触层108在作用层107上,且金属化层(即,顶部金属)109在栅极及接触层108上。

15.如本文所述,在第二层的至少一部分上形成、粘附或安置在所述第二层“上”或“形成在所述第二层上”的第一层。一般而言,第一层的最低垂直范围的至少一部分与第二层的最高垂直范围的至少一部分直接接触,或者与接合材料(诸如将第一层连接至第二层的粘合剂或焊料)直接接触。例如,ldmos装置102的作用层107在衬底104上方,但不在衬底104“上”。更确切地说,ldmos装置102的作用层107形成在box层106“上”。在一些实施方案中,接合元件(诸如化学粘合剂或焊料)可以插入形成于第二层上的第一层之间。

16.对于n型ldmos装置,作用层107通常包括n型导电性硅117、n型导电性源极区域110、p型导电性源极连接区域111、p型导电性浅阱112、p型导电性深阱114、p型导电性沟道区域116、n型导电性漂移区域118(即,ldd区域)及n型导电性漏极区域120。对于p型ldmos装置,区域导电性类型是相反的。栅极及接触层108通常包括栅极氧化物层124、栅极多晶硅122、金属源极触点的第一部分135、金属漏极触点的第一部分134、多晶硅栅极间隔物128、129、栅极触点126、栅极屏蔽物130、金属源极触点的第二部分136、金属漏极触点的第二部分138,及电介质139。金属化层109通常包括金属源极触点的第三部分140及金属漏极触点的第三部分142。

17.如本文所公开的,包括源极区域110、沟道区域116、浅阱112、深阱114及源极连接区域111的源极架构有利地提供了稳定电平面,ldmos装置102的栅极、漂移及漏极区域从所述稳定电平面在宽范围偏置条件下操作。如本文所公开的,使用示例性过程1500有利地形成此源极架构,所述示例性过程限制重要的源极受控电参数(如vt及ioff)的差异。与常规ldmos装置的源极架构相比,ldmos装置102的源极架构有利地提供了增加的骤回及非箝位电感开关(uis)耐用性、当ldmos装置102导通时呈现给电流的较低源极电阻及当ldmos装置102断开时的较低源极泄漏电流。栅极屏蔽物130有利地减小了栅极多晶硅122至漏极区域120的金属化物的电容耦合。另外,如本文所公开的,用于形成ldmos装置102的示例性过程1500涉及使用单个光掩蔽步骤来形成沟道区域116、浅阱112、深阱114及源极区域110。因此,与用于形成常规ldmos装置的常规过程相比,过程1500有利地减少了光掩蔽步骤的总数,在所述常规过程中,前述区域中的每一者在单独的光掩蔽步骤中进行处理。

18.漏极区域120经配置以接收偏置电压(未示出),且栅极多晶硅122控制沟道区域116的反转/耗尽,以经由漂移区域118及沟道区域116控制漏极区域120与源极区域110之间的电流流动。沟道区域116在作用层107中于栅极多晶硅122下方提供p型掺杂。沟道区域116的掺杂及横向范围有助于产生ldmos装置102的所要vt,且影响ldmos装置102的其他参数,诸如rsp、ids、ioff及gm。深阱114在源极区域110下方提供重p型掺杂。因此,深阱114有利地有助于弱化源极侧寄生双极晶体管,使得ldmos装置102的骤回及uis满足应用要求。源极区域110被重掺杂且比常规ldmos装置的源极区域更浅,以允许深阱114有利地有效地收集雪崩产生的少数载流子而无需源极侧寄生双极晶体管导通。

19.源极区域110、沟道区域116、深阱114及浅阱112的植入条件使得掺杂剂不会穿透栅极多晶硅122的厚度。此具有基于从作用层107上蚀刻掉栅极多晶硅122的位置来掺杂作

用层107的效果。在沟道区域116的情况下,掺杂剂物质以一角度植入且穿透栅极多晶硅122的边缘以形成沟道区域116。与用于形成常规ldmos装置的常规过程相比,将掺杂剂以此方式引入作用层107中有利地消除了对光致抗蚀剂的未对准或临界尺寸控制的处理差异。因此,与常规ldmos装置相比,使用如本文所公开的过程1500形成的ldmos装置102有利地包括:i)沟道区域116在栅极多晶硅122下方的可重复长度(即,横向范围),借此消除了ldmos装置102的电参数中的差异的重要来源;ii)在源极区域110正下方对准的深阱114,借此实现了ldmos装置102的稳定uis及骤回性能,所述性能在多指状物ldmos装置的相对指状物之间不变化;以及iii)被植入在栅极多晶硅122的边缘处且在受控距离内热驱动的源极区域110,借此有利地提供了源极区域110与沟道反转层的良好连接,借此改进了ldmos装置102的源极至漏极电流水平ids。

20.图2a示出了基本现有技术ldmos装置200,其包括源极触点201、漏极触点202、n 源极区域203、p 源极接触区域204、n 漏极区域205、p阱206、n外延区域207、栅极208及栅极氧化物209。p阱206形成本体区域,且沟道区域形成在本体区域的在栅极208下方的一部分中。n外延区域207在p阱206与n 漏极区域205之间在其顶部表面附近包括n漂移区域210。

21.与ldmos装置102相比,现有技术ldmos装置200具有几个缺点。例如,与利用ldmos装置102的改进设计实现的击穿电压bvdss相比,形成于p阱206中的沟道区域与n漂移区域210之间的结区域中的高电压通常导致相对较低的击穿电压。

22.图2b示出了另一现有技术ldmos装置220,其包括源极触点221、漏极触点222、n 源极区域223、p 源极连接区域224、n 漏极区域225、p阱区域226、p外延区域227、栅极228、栅极氧化物229、n漂移区域230及硅局部氧化(locos)隔离区域231。p阱区域226形成本体区域,且沟道区域形成在本体区域的在栅极228下方的一部分中。n漂移区域230植入在p外延区域227中,且locos隔离区域231形成在n漂移区域230上。栅极228的一部分作为场板在locos隔离区域231上方延伸。现有技术ldmos装置220是比ldmos装置200更高电压的装置。为了实现较高电压能力,必须延长n漂移区域230及/或必须减少n漂移区域230的掺杂。locos隔离区域231减少了n漂移区域230的掺杂。在这些设计中,必须将n 漏极区域225进一步移动远离p阱区域226,这是因为ldmos装置220的硅可在雪崩击穿发生之前处置~30v/um。在常规ldmos装置中,15v/um至20v/um是典型的雪崩极限。因此,为了增加bvdss,在这些设计中必须增加rsp。

23.图3示出了根据一些实施方案的多指状物ldmos装置302的横截面。在一些实施方案中,ldmos装置302通常包括两个指状物301a、301b,每个指状物与ldmos装置102类似或相同。在其他实施方案中,ldmos装置302包括两个以上指状物。一般而言,ldmos装置302包括衬底304、衬底304上的box层306、box层306上的n型作用层307、作用层307上的栅极及接触层308以及栅极及接触层308上的金属化层309。

24.ldmos装置302在本文中被描述为具有n型导电性(“n型”)区域及p型导电性(“p型”)区域的n型ldmos装置。然而,ldmos装置302可以替代地被实施为p型ldmos装置,因此交换了相应区域的导电性(即,n型区域变为p型区域)。

25.在指状物301a、301b之间共享作用层307的一些区域。指状物301a至301b之间共享的作用层307的区域包括重掺杂p型源极连接区域311、p型浅阱312及p型深阱314。作用层307的特定于第一指状物301a的第一部分包括第一n型硅区域317a、第一n型源极区域310a、

第一p型沟道区域316a、第一n型漂移区域318a(即,ldd区域)及第一n型漏极区域320a。作用层307的特定于第二指状物301b的第二部分包括第二n型硅区域317b、第二n型源极区域310b、第二p型沟道区域316b、第二n型漂移区域318b(即,ldd区域)及第二n型漏极区域320b。

26.在指状物301a至301b之间共享栅极及接触层308的一些元件。在指状物301a至301b之间共享的元件包括金属源极触点的第一部分335及金属源极触点的第二部分336。栅极及接触层308的特定于第一指状物301a的第一部分包括第一栅极氧化物层324a、第一栅极多晶硅322a、第一多晶硅栅极间隔物328a、329a、第一栅极触点326a、第一栅极屏蔽物330a、第一金属漏极触点的第一部分334a、第一金属漏极触点的第二部分338a及第一电介质339a。栅极及接触层308的特定于第二指状物301b的第二部分包括第二栅极氧化物层324b、第二栅极多晶硅322b、第二多晶硅栅极间隔物328b、329b、第二栅极触点326b、第二栅极屏蔽物330b、第二金属漏极触点的第一部分334b、第二金属漏极触点的第二部分338b及第二电介质339b。金属化层309通常包括在指状物301a、301b之间共享的金属源极触点的第三部分340、第一金属漏极触点的第三部分342a及第二金属漏极触点的第三部分342b。与常规ldmos装置相比,ldmos装置302的优点与参考ldmos装置102描述的这些优点类似或相同。

27.图4至图14是详述根据一些实施方案的用于在示例性过程1500的各个阶段处形成ldmos装置102或302的步骤的简化横截面示意图。图4至图14的细节在下文进行简单介绍,随后参考图15至图18及图19a至图19b进行详细论述。

28.图4是根据一些实施方案的形成与ldmos装置102、302相同或类似的ldmos装置402时的第一步骤的示意图的简化横截面图。ldmos装置402包括相应的第一指状物401a及第二指状物401b的第一及第二部分。ldmos装置402的由“a”指定的区域及元件被理解为第一指状物401a的一部分。ldmos装置402的由“b”指定的区域及元件被理解为第二指状物401b的一部分。ldmos装置402的未由“a”或“b”指定的区域及元件被理解为由两个指状物401a、401b共享。在一些实施方案中,通过过程1500形成的ldmos装置402可具有一个指状物、两个指状物或两个以上指状物。

29.ldmos装置402的区域通常包括衬底层404、形成于衬底层404上的埋入式氧化物(box)层406及形成于box层406上的n型硅作用层407。第一指状物401a的第一栅极包括形成于作用层407上的栅极氧化物424a及栅极多晶硅422a。第二指状物401b的第二栅极包括栅极氧化物424b及栅极多晶硅422b,其等形成于作用层407上且从栅极氧化物424a及栅极多晶硅422a横向安置。在一些实施方案中,ldmos装置402包括浅沟槽隔离结构(sti)(未示出)及深沟槽隔离结构(dti)(未示出),其等形成于作用层407中以提供ldmos装置402与形成于box 406上的其他半导体结构之间的隔离及/或终止。

30.图5示出了在已经在作用层407上形成第一掩模“mask

1”之后的ldmos装置402。根据一些实施方案,第一掩模mask1包括作为示例性过程1500的一部分形成于作用层407上的光致抗蚀剂区域561a、561b。还示出了作用层407的被暴露(即,其上未安置光致抗蚀剂或栅极多晶硅)的横向范围512、栅极多晶硅422a的第一横向范围513a、栅极多晶硅422a的第二横向范围514a、栅极多晶硅422b的第一横向范围513b及栅极多晶硅422b的第二横向范围514b。

31.如图所示,第一光致抗蚀剂区域561a形成在第一栅极多晶硅422a的第一横向范围

513a上,且不包括栅极多晶硅422a的第二横向范围514a及作用层407的暴露的横向范围512二者(即,未形成在所述二者上)。类似地,第二光致抗蚀剂区域561b形成在第二栅极多晶硅422b的第一横向范围513b上,且不包括栅极多晶硅422b的第二横向范围514b及作用层407的暴露的横向范围512二者(即,未形成在所述二者上)。在一些实施方案中,可以基于设计规则(例如,栅极多晶硅与源极触点间隔)、所要的操作参数及/或制造能力来选择横向范围512,可以基于ldmos装置402的所要的性能标准(诸如idsat及热载流子稳健性)来选择横向范围513a至513b,并且可以基于光致抗蚀剂区域561a至561b与栅极多晶硅422a至422b的所要的对准标准来选择横向范围514a至514b。

32.图6示出了使用光致抗蚀剂区域561a、561b及栅极多晶硅422a、422b作为形成沟道区域616的掩模通过以第一范围的倾斜角652a(如虚线箭头所示)植入和以第二范围的倾斜角652b(如实线箭头所示)植入的掺杂剂671在作用层407中形成p型沟道区域616。沟道区域616的植入条件使得掺杂剂不会穿透栅极多晶硅422a、422b的厚度。沟道区域616在栅极多晶硅422a下方横向延伸达第一横向范围614a。类似地,沟道区域616在栅极多晶硅422b下方横向延伸达第二横向范围614b。

33.在一些实施方案中,掺杂剂671是包括硼的p型掺杂剂。掺杂剂671的硼植入条件取决于栅极氧化物424a至424b的厚度及沟道区域616的所要沟道长度(例如,横向范围614a至614b的所要相应长度)。例如,在一些实施方案中,对于70埃的栅极氧化物424a至424b的栅极氧化物厚度,掺杂剂671的植入剂量可在1e13 b/cm2至7e13b/cm2的范围内,这取决于ldmos装置402的其他掺杂剂影响沟道区域616的掺杂的程度。在一些实施方案中,倾斜角652a至652b(相对于垂直于平行于作用层407的顶部表面的水平面的平面)在从7度至45度的范围内,且可被选择适于沟道区域616的所要横向范围614a至614b。倾斜角652a至652b的范围的较浅倾斜角(例如,7度)将比较大倾斜角(例如,45度)产生沟道区域616的更短沟道长度。

34.图7示出了根据一些实施方案的在使用光致抗蚀剂区域561a、561b及栅极多晶硅422a、422b作为掩模(即,mask1)通过以倾斜角753植入的掺杂剂772在作用层407中形成p型浅阱712及p型深阱714之后的ldmos装置402。p型浅阱712及p型深阱714将作用层407的n型作用硅的植入区域转换为p型硅,借此形成ldmos装置402,使得它表现出所要的骤回及uis性能。如图所示,阱712、714现在将图6中所示的沟道区域616分割为p型沟道区域716a、716b。类似于沟道区域616,阱712、714的植入条件使得掺杂剂不会穿透栅极多晶硅422a、422b的厚度。在一些实施方案中,倾斜角753垂直于平行于作用层407的顶部表面的水平面,在其他实施方案中,倾斜角753相对于平行于作用层407的顶部表面的水平面在70度至120度的范围内。在一些实施方案中,掺杂剂772是包括硼的p型掺杂剂且以从1e13 b/cm2至7e13 b/cm2的范围内的浓度植入。

35.图8示出了根据一些实施方案的在使用光致抗蚀剂区域561a、561b及栅极多晶硅422a、422b作为掩模(即,mask1)通过处于倾斜角854的掺杂剂873形成具有深度851的n型源极区域810之后的ldmos装置402。在一些实施方案中,光致抗蚀剂区域561a至561b延伸至ldmos装置402的外边缘。在一些实施方案中,倾斜角854相对于平行于作用层407的顶部表面的水平面在70度至120度的范围内。源极区域810的植入条件使得掺杂剂873不会穿透栅极多晶硅422a、422b的厚度。与常规ldmos装置的源极区域相比,源极区域810具有更高植入

浓度且具有更浅深度。在一些实施方案中,掺杂剂873是n型掺杂剂且包括砷,并以从1e14 as/cm2至2.5e15 as/cm2的范围内的相对较高浓度植入。为了实现浅深度,使用低能量植入来植入源极区域810,例如对于砷源极而言,所述低能量植入具有7kev至20kev的范围。在一些实施方案中,掺杂剂873包括第一及第二砷植入。第一砷植入是低能量高浓度砷植入以靠近作用层407的顶部表面形成n型源极区域810,如图8中对n型源极区域810的深度851的指示所示。在一些实施方案中,源极区域810的深度851在80nm至200nm的范围内。在一些实施方案中,与掺杂剂873的第一砷植入相比,掺杂剂873的第二砷植入以稍微更高能量且以类似浓度进行。在这些实施方案中,掺杂剂873的第二砷植入的能量在20kev至70kev的范围内。源极区域810与栅极多晶硅422a至422b对准。

36.在形成源极区域810之后,去除mask1的光致抗蚀剂区域561a至561b。

37.在用于形成ldmos装置的常规过程中,常规地在标准n 光/植入步骤处执行源极区域掺杂。因此,与本文所公开的ldmos装置402相比,使用常规过程形成的ldmos装置具有更深n型结。结果,因此,与ldmos装置402相比,常规ldmos装置的深p阱植入可能必须更深,且因此可能不与所述装置的作用层的栅极多晶硅开口自对准。相比之下,图5至图8示出了单个掩模(mask1)的使用,所述掩模包括光致抗蚀剂(561a至561b)且利用栅极多晶硅422a至422b以有利地形成ldmos装置402的经自对准以及与栅极多晶硅422a至422b对准的四个区域(616、712、714、810)。另外,使用常规n型光/植入步骤对与常规ldmos装置的栅极多晶硅相邻的源极区域的两侧进行掺杂可留下在所述装置的栅极多晶硅之间居中的抗蚀剂的长细线,以允许p型源极连接区域植入,这可能导致抗蚀剂提升的处理问题。本文公开的过程1500通过使用低于源极连接区域的p型掺杂剂浓度的源极区域掺杂剂浓度来避免此问题,借此允许p型掺杂剂对源极区域进行反掺杂。

38.图9示出了根据一些实施方案的在包括光致抗蚀剂区域962的第二掩模mask2形成于作用层407上之后且在使用光致抗蚀剂区域962作为漂移区域掩模通过处于倾斜角955的掺杂剂974在作用层407中形成漂移区域918a、918b(即,ldd区域)之后的ldmos装置402。用于形成n型漂移区域918a至918b的植入模块包括一个至几个植入步骤以定制漂移区域918a至918b的掺杂轮廓。以在5e11 p/cm2至7e12 p/cm2的范围内的浓度植入单独剂量的掺杂剂974。在一些实施方案中,倾斜角955垂直于平行于作用层407的顶部表面的水平面,在其他实施方案中,倾斜角955相对于平行于作用层407的顶部表面的水平面在70度至120度的范围内。在形成漂移区域918a至918b之后,去除mask2的光致抗蚀剂区域962。

39.图10示出了根据一些实施方案的在包括光致抗蚀剂区域1063的第三掩模mask3已经形成于作用层407上之后且在使用光致抗蚀剂区域1063作为漏极区域掩模通过处于倾斜角1056的掺杂剂1075在作用层407中形成n漏极区域1020a、1020b之后的ldmos装置402。还示出了形成于栅极多晶硅422a、422b的相应内侧及外侧上的多晶硅栅极间隔物1028a、1028b及1029a、1029b。多晶硅栅极间隔物1029a垂直安置在漂移区域918a上方,而多晶硅栅极间隔物1028a垂直安置在源极区域810上方。类似地,多晶硅栅极间隔物1029b垂直安置在漂移区域918b上方,而多晶硅栅极间隔物1028b垂直安置在源极区域810上方。在一些实施方案中,根据ldmos装置402的源极连接区域的所要横向范围来选择栅极间隔物1028a至1028b及1029a至1029b的相应横向范围。在一些实施方案中,掺杂剂1075是包括砷及磷的n型掺杂剂,且以例如3e15 as/cm2及8e13 p/cm2的高浓度植入,以形成与相应金属漏极触点

的低电阻欧姆接触。在形成漏极区域1020a至1020b之后,去除mask3的光致抗蚀剂区域1063。

40.图11a示出了根据一些实施方案的在包括光致抗蚀剂区域1164a、1164b的第四掩模mask4已经形成在作用层407上且使用光致抗蚀剂区域1164a、1164b作为掩模通过以倾斜角1157植入的掺杂剂1176在作用层407中已经形成重掺杂p型源极连接区域1111之后的ldmos装置402的第一示例。在一些实施方案中,光致抗蚀剂区域1164a至1164b延伸至ldmos装置402的外边缘。光致抗蚀剂区域1164a在作用层407上延伸超过多晶硅栅极间隔物1028a的内边缘达横向范围1114a。类似地,光致抗蚀剂区域1164b在作用层407上延伸超过多晶硅栅极间隔物1028b的内边缘达横向范围1114b。因此,光致抗蚀剂区域1164a延伸达或超过多晶硅栅极间隔物1028a的整个横向范围,而光致抗蚀剂区域1164b延伸达或超过多晶硅栅极间隔物1028b的整个横向范围。作用层407的在横向范围1114a与横向范围1114b之间的区域被暴露于以倾斜角1157植入的掺杂剂1176,以形成源极连接区域1111。如图所示,图8的源极区域810已经由源极连接区域1111分割为n型源极区域1110a、1110b。图11a和图11b中所示的源极连接区域1111/1111'是重掺杂p型区域,其适于与金属源极触点形成良好的欧姆接触。在一些实施方案中,倾斜角1157垂直于平行于作用层407的顶部表面的水平面,在其他实施方案中,倾斜角1157相对于平行于作用层407的顶部表面的水平面在70度至120度的范围内。在一些实施方案中,掺杂剂1176是包括硼的p型掺杂剂且以从1e15 b/cm2至5e15 b/cm2的范围内的高浓度植入。在一些实施方案中,横向范围1114a至1114b具有0nm至0.2μm的宽度,而作用层407的暴露区域的横向范围具有0.1μm至0.4μm的宽度。

41.图11b示出了根据一些实施方案的在包括光致抗蚀剂区域1164a'、1164b'的替代第四掩模mask4'已经形成在作用层407上且使用光致抗蚀剂区域1164a

′

、1164b'及多晶硅栅极间隔物1028a、1028b作为掩模通过处于倾斜角1157的掺杂剂1176在作用层407中已经形成重掺杂p型连接区域1111'之后的ldmos装置402的替代示例。在一些实施方案中,光致抗蚀剂区域1164a'至1164b'延伸至ldmos装置402的外边缘。如图所示,图8的源极区域810已经由源极连接区域1111'分割为n型源极区域1110a、1110b。

42.光致抗蚀剂区域1164a

′

不包括在多晶硅栅极间隔物1028a的横向范围1116a中(即,未形成在所述横向范围上),而光致抗蚀剂区域1164b'不包括在多晶硅栅极间隔物1028b的横向范围1116b中。作用层407的在多晶硅栅极间隔物1028a与多晶硅栅极间隔物1028b之间的区域被暴露于以倾斜角1157植入的掺杂剂1176,以形成源极连接区域1111'。多晶硅栅极间隔物1028a至1028b的横向范围1116a至1116b可操作以相对于掺杂剂1176将作用层407掩蔽,并且因此,由掺杂剂1176形成的源极连接区域1111'有利地与多晶硅栅极间隔物1028a至1028b的内边缘1115对准。在一些实施方案中,横向范围1116a至1116b具有30nm至100nm的宽度,而作用层407的暴露区域的横向范围具有0.2μm至0.6μm的宽度。

43.相比之下,通常在常规ldmos装置的栅极多晶硅之间拉开常规ldmos形成过程中的光致抗蚀剂区域,其裕度足以为源极植入和多晶硅栅极间隔物留出空间。然而,在所示实施方案中,光致抗蚀剂区域1164a'、1164b'被拉近多晶硅栅极间隔物1028a、1028b或与其等重叠,借此形成源极连接区域1111',使得源极连接区域1111'与多晶硅栅极间隔物1028a、1028b自对准。因此,多晶硅栅极间隔物1028a、1028b将源极区域1110a、1110b与掺杂剂1176屏蔽开。结果,与常规ldmos装置相比,有利地产生ldmos装置402的较小源极区域1110a至

1110b。

44.图12示出了根据一些实施方案的在作用层407上形成栅极及接触层1208的一些元件之后的ldmos装置402。图12中所示的栅极及接触层1208的元件包括第一金属漏极触点的第一部分1234a、第一栅极屏蔽物1230a、第一栅极触点1226a、金属源极触点1235、第二金属漏极触点的第一部分1234b、第二栅极屏蔽物1230b、第二栅极触点1226b及电介质1239。如图所示,第一栅极触点1226a形成在第一栅极多晶硅422a上。栅极屏蔽物1230a的第一部分形成在第一栅极触点1226a上方。栅极屏蔽物1230a的第二部分横向延伸超过多晶硅栅极间隔物1029a,且垂直地安置在漂移区域918a上方。栅极屏蔽物1230a的第二部分比栅极屏蔽物1230a的第一部分更靠近作用层407的顶部表面。类似地,第二栅极触点1226b形成在第二栅极多晶硅422b上。栅极屏蔽物1230b的第一部分形成在第二栅极触点1226b上方。栅极屏蔽物1230b的第二部分横向延伸超过多晶硅栅极间隔物1029b,且垂直地安置在漂移区域918b上方。栅极屏蔽物1230b的第二部分比栅极屏蔽物1230b的第一部分更靠近作用层407的顶部表面。在图12中所示的ldmos装置402的形成阶段处,电介质1239覆盖栅极及接触层1208中的所有部件。栅极屏蔽物1230a至1230b有利地减小了栅极多晶硅422a至422b与相应漏极区域1020a至1020b的金属化物的电容耦合。

45.图13示出了根据一些实施方案的在作用层407上形成栅极及接触层1208的额外元件及金属化层1309之后的ldmos装置402的第一示例。图13中所示的栅极及接触层1208的元件包括第一金属漏极触点的第二部分1338a、第二金属漏极触点的第二部分1338b、电介质的第一部分1339a及电介质(如图12所示,电介质1239)的第二部分1339b。金属化层1309包括第一金属漏极触点的第三部分1342a、金属源极触点的第三部分1340(即,顶部金属)及第二金属漏极触点的第三部分1342b(即,顶部金属)。还示出了横向范围1358、1359a、1359b及1360的尺寸指示符。

46.在一些实施方案中,ldmos装置402的源极区域的布局尺寸由栅极多晶硅422a、422b之间的横向范围1358、金属源极触点的第二部分1336的宽度1360、栅极多晶硅422a与金属源极触点的第二部分1336之间的横向范围1359a以及栅极多晶硅422b与金属源极触点的第二部分1336之间的横向范围1359b来确定且取决于ldmos装置402的技术节点。作为第一示例,对于0.18μm技术节点,栅极多晶硅422a、422b之间的横向范围1358(即,源极宽度)可等于0.25μm,金属源极触点的第二部分1336的宽度1360可等于0.22μm,且栅极多晶硅422a、422b与金属源极触点的第二部分1336之间的横向范围1359a、1359b可各自分别等于0.16μm。作为第二示例,对于90nm技术节点,栅极多晶硅422a、422b之间的横向范围1358可等于0.17μm,金属源极触点的第二部分1336的宽度1360可等于0.12μm,且栅极多晶硅422a、422b与金属源极触点的第二部分1336之间的横向范围1359a、1359b可分别等于0.10μm。在一些实施方案中,用于ldmos装置402的最小源极宽度(即,横向范围1358)的限制规则等于宽度1360加上横向范围1359a再加上横向范围1359b。因此,使用本段先前给出的示例性尺寸,对于0.18μm节点,ldmos装置402的源极宽度为0.54μm,而对于90nm技术节点,ldmos装置402的源极宽度为0.32μm。

47.图14示出了根据一些实施方案的在作用层407上形成栅极及接触层1208的额外元件及金属化层1309之后的ldmos装置402的第二示例。图14中所示的栅极及接触层1208的元件包括金属源极触点的第二部分1436的第二示例。在所示的示例性实施方案中,栅极屏蔽

物1230a用作金属源极触点的第二部分1436的金属源极触点蚀刻停止层,使得金属源极触点的第二部分1436沿第一垂直范围的宽度与栅极屏蔽物1430a的部分重叠。金属源极触点的第二部分1436在第一栅极屏蔽物1230a的顶部表面上方沿第一垂直范围具有第一宽度1460a,且在第一栅极屏蔽物1230a的顶部表面下方及在栅极多晶硅422a至422b之间沿第二垂直范围具有第二较窄宽度1460b。在所示示例中,第一宽度1460a宽于第二宽度1460b。通过有利地提供用于形成金属源极触点的第三部分1340的更宽区域,经重叠栅极屏蔽物部分允许源极触点在p型源极连接区域1111处变窄。即,宽度1460b窄于ldmos装置402的最小接触特征大小。结果,与常规ldmos装置相比,可以减小ldmos装置402的单元节距。

48.根据一些实施方案,图15中示出的示例性过程1500高层次地描述了用于形成ldmos装置302/402的细节。图15中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图4至图14描述图15的步骤。

49.在步骤1502处,提供具有作用n型层407的半导体晶片(例如,衬底404及box层406)。在步骤1504处,在作用层407上形成栅极氧化物424a至424b及栅极多晶硅422a至422b。在步骤1506处,作为被指定为mask1的过程的一部分,在作用层407中各自形成p型沟道区域616、p型浅阱712、p型深阱714及n型源极区域810。在步骤1508处,作为被指定为mask2的过程的一部分,在作用层407中形成n型漂移区域918a、918b。在步骤1510处,与栅极多晶硅422a至422b相邻地形成多晶硅栅极间隔物1028a至1028b、1029a至1029b。在步骤1512处,作为被指定为mask3的过程的一部分,在作用层407中形成n型漏极区域1020a至1020b。在步骤1514处,作为被指定为mask4的过程的一部分,在作用层407中形成p型源极连接区域1111(或者使用mask4'形成p型源极连接区域1111')。在步骤1516处,形成栅极屏蔽物1230a至1230b、栅极触点1226a至1226b、金属漏极触点1234a至1234b、1338a至1338b、金属源极触点1235、1336及顶部金属1340、1342a至1342b,且形成电介质1339a至1339b。

50.图16示出了根据一些实施方案的步骤1506(“mask1过程”)的示例性实施方案的细节。图16中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图5至图8描述图16的步骤。

51.在步骤1602处,在作用层407上形成掩蔽区域mask1。掩蔽区域mask1包括光致抗蚀剂区域561a、561b及有利地可操作以执行掩蔽功能的栅极多晶硅422a至422b。在步骤1604处,如图6所示,使用光致抗蚀剂区域561a、561b及栅极多晶硅422a至422b作为掩模,通过掺杂剂671在作用层407中形成p型沟道区域616。以第一范围的倾斜角652a植入且热驱动掺杂剂671以形成p型沟道区域616的第一部分,所述第一部分在栅极多晶硅422a下方水平地延伸达横向范围614a。类似地,以第二范围的倾斜角652b植入且热驱动掺杂剂671以形成p型沟道区域616的第二部分,所述第二部分在栅极多晶硅422b下方水平地延伸达横向范围614b。通过以倾斜角652a至652b进行的植入中的任一者或其组合来形成p型沟道区域616的第三部分,所述第三部分在栅极多晶硅422a的内边缘615与栅极多晶硅422b之间横向延伸。

52.在步骤1606处,如图7所示,使用光致抗蚀剂区域561a至561b及栅极多晶硅422a至422b作为掩模,通过掺杂剂772在作用层407中形成p型浅阱712。以倾斜角753植入掺杂剂772,使得p型浅阱712与栅极多晶硅422a至422b的内边缘615对准。

53.在步骤1608处,使用光致抗蚀剂区域561a至561b及栅极多晶硅422a至422b作为用于重p型掺杂的掩模,通过掺杂剂772在作用层407中形成p型深阱714。以倾斜角753植入掺杂剂772,使得深阱714与栅极多晶硅422a至422b的内边缘615对准,但掺杂剂772可扩散。

54.在步骤1610处,如图8所示,使用光致抗蚀剂区域561a、561b及栅极多晶硅422a、422b作为掩模,通过以倾斜角854植入的掺杂剂873在作用层407中形成n型源极区域810。在步骤1612处,去除mask1区域的光致抗蚀剂区域561a、561b。

55.图17示出了根据一些实施方案的步骤1508(“mask2过程”)的示例性实施方案的细节。图17中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图9描述图17的步骤。

56.在步骤1702处,在作用层407上形成掩蔽区域mask2。在一些实施方案中,掩蔽区域mask2包括光致抗蚀剂区域962,且栅极多晶硅422a至422b有利地可操作以执行掩蔽功能。在步骤1704处,如图9所示,使用光致抗蚀剂区域962及栅极多晶硅422a至422b作为掩模,通过以倾斜角955植入的掺杂剂974在作用层407中形成n型漂移区域918a至918b。在步骤1706处,去除mask2区域的光致抗蚀剂区域962。

57.图18示出了根据一些实施方案的步骤1512(“mask3过程”)的示例性实施方案的细节。图18中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图10描述图18的步骤。

58.在步骤1802处,在作用层407上形成掩蔽区域mask3。在一些实施方案中,掩蔽区域mask3包括光致抗蚀剂区域1063。在步骤1804处,如图10所示,使用光致抗蚀剂区域1063作为掩模,通过以倾斜角1056植入的掺杂剂1075在作用层407中形成n型漏极区域1020a、1020b。以倾斜角1056沉积掺杂剂1075,使得n漏极区域1020a至1020b与光致抗蚀剂区域1063的外边缘对准。在一些实施方案中,倾斜角1056相对于平行于作用层407的水平面的顶部表面在70度至120度的范围内。在步骤1806处,去除mask3区域的光致抗蚀剂区域1063。

59.图19a示出了根据一些实施方案的步骤1514(“mask4过程”)的第一示例性实施方案的细节。图19a中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图11a描述图19a的步骤。在步骤1902a处,在作用层407上形成掩蔽区域mask4。在一些实施方案中,掩蔽区域mask4包括光致抗蚀剂区域1164a、1164b。在步骤1904a处,如图11a所示,使用光致抗蚀剂区域1164a至1164b作为掩模,通过掺杂剂1176在作用层407中形成p型(即,p )源极连接区域1111。以倾斜角1157植入掺杂剂1176,使得p型源极连接区域1111与光致抗蚀剂区域1164a至1164b的内边缘对准。在步骤1906a处,去除mask4区域的光致抗蚀剂区域1164a、1164b。

60.图19b示出了根据一些实施方案的步骤1514(“mask4过程”)的第二示例性实施方案的细节。图19b中仅出于说明性和解释性目的示出了特定步骤、步骤顺序及步骤组合。其他实施方案可以实施不同的特定步骤、步骤顺序及步骤组合,以实现类似功能或结果。参考图11b描述图19b的步骤。

61.在步骤1902b处,在作用层407上形成掩蔽区域mask4′

。在一些实施方案中,掩蔽区

域mask4'包括光致抗蚀剂区域1164a'至1164b'。在步骤1904b处,如图11b所示,使用光致抗蚀剂区域1164a'至1164b'及多晶硅栅极间隔物1028a至1028b作为掩模,通过掺杂剂1176在作用层407中形成p型(即,p )源极连接区域1111'。掺杂物1176以倾斜角1157沉积,使得p型源极连接区域1111与多晶硅栅极间隔物1028a至1028b的内边缘1115对准。在步骤1906b处,去除mask4'区域的光致抗蚀剂区域1164a'、1164b'。

62.已经详细参考了所公开发明的实施方案,在附随图式中示出了其一个或多个示例。已经借助于解释本技术而不是对本技术的限制的方式提供了每个示例。实际上,尽管已经关于本发明的特定实施方案详细地描述了本说明书,但应当理解,所属领域的技术人员在理解前述内容之后可轻易想到对这些实施方案的替代、变型及等效物。例如,作为一个实施方案的一部分示出或描述的特征可与另一个实施方案一起使用以产生又一实施方案。因此,本主题意图涵盖随附权利要求及其等同物的范围内的所有这些修改及变型。在不脱离本发明的范围的情况下,所属领域的技术人员可对本发明实践这些及其他修改及变型,本发明的范围在随附权利要求中更具体地陈述。此外,所属领域的技术人员应当理解,前述描述仅是示例性的且不意图限制本发明。

63.术语“横向”及“水平”是指与衬底的平面或表面平行的方向或平面,而与定向无关。术语“垂直”是指垂直于水平面的方向。相对于水平面限定诸如“在......上”、“在......上方”、“底部”、“顶部”、“侧面”、“上部”及“在......上面”之类的术语。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。