1.本实用新型涉及量子计算领域,尤其是涉及一种超导量子计算机时序信号传输系统。

背景技术:

2.量子计算是一种遵循量子力学规律调控量子信息单元进行计算的新型计算模式,量子芯片是量子计算的核心结构,量子芯片上设有大量的量子比特结构。

3.随着所需量子芯片数量的增加或者量子芯片上比特数目的增多,所需的测控设备呈现几何增长,各种设备之间相互有信号的传输、供电电源的分配、时序信号的同步和统一、量子比特信号的反馈等互联互通作业。目前在扩展相应测控设备的同时,若只是单纯对测控设备的堆砌,将会导致设备的臃肿、维护的不便以及效率的低下。

技术实现要素:

4.本实用新型旨在至少解决现有技术中存在的技术问题之一。为此,本实用新型的一个目的在于提出一种超导量子计算机时序信号传输系统。

5.本实用新型实施例提供了一种超导量子计算机时序信号传输系统,包括:

6.时钟板卡和时序信号线,所述时钟板卡用于提供同步时钟信号和同步触发信号中的至少一个,所述时序信号线用于传输所述同步时钟信号和所述同步触发信号中的至少一个,所述时序信号线包括第一时序信号线和第二时序信号线;

7.多个电子学测控板卡单元,所述电子学测控板卡单元的板卡与所述时钟板卡通过所述第一时序信号线连接,所述电子学测控板卡单元用于测控量子比特的状态信息;

8.主控板卡,所述主控板卡与所述时钟板卡通过所述第二时序信号线连接,所述主控板卡用于对所述时钟板卡和所述电子学测控板卡单元进行控制和数据交互;

9.其中,所述第一时序信号线和所述第二时序信号线等长。

10.根据本实用新型实施例的超导量子计算机时序信号传输系统,通过设置时钟板卡到其他板卡的时钟信号和触发信号在背板做走线等长,使得背板到各板卡的时钟信号和触发信号是同相位的,使得超导量子计算机在进行多比特的测控时,可以统一操作,同步工作。

11.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡包括时钟缓冲寄存器,所述主控板卡包括第一锁相环电路,所述电子学测控板卡单元的板卡包括第二锁相环电路,所述时钟缓冲寄存器用于输出所述同步时钟信号,所述第一锁相环电路和所述第二锁相环电路用于接收所述同步时钟信号。

12.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括第三锁相环电路,所述第三锁相环电路和所述时钟缓冲寄存器连接,所述第三锁相环电路于向所述时钟缓冲寄存器输出参考时钟信号,所述参考时钟信号为所述同步时钟信号的一种。

13.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括时钟输出模块,所述时钟输出模块和所述第三锁相环电路连接,所述时钟输出模块用于将所述第三锁相环电路输出的所述参考时钟信号向外部输出。

14.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括时钟输入模块,所述时钟输入模块与所述第三锁相环电路连接,所述时钟输入模块用于向所述第三锁相环电路输入外部时钟信号,所述第三锁相环电路于向所述时钟缓冲寄存器输出所述外部时钟信号,所述外部时钟信号为所述同步时钟信号的一种。

15.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括触发缓冲寄存器,所述主控板卡包括第一触发甄别电路,所述电子学测控板卡单元的板卡包括第二触发甄别电路,所述触发缓冲寄存器用于输出所述同步触发信号,所述第一触发甄别电路和所述第二触发甄别电路用于接收所述同步触发信号。

16.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括第三逻辑处理器,所述第三逻辑处理器与所述触发缓冲寄存器连接,所述第三逻辑处理器用于向所述触发缓冲寄存器输出基准触发信号,所述基准触发信号为所述同步触发信号的一种。

17.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括触发输出模块,所述触发输出模块与所述第三逻辑处理器连接,所述触发输出模块用于将所述第三逻辑处理器输出的所述基准触发信号向外部输出。

18.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括触发输入模块和第三触发甄别电路,所述触发输入模块和所述第三触发甄别电路连接,所述第三触发甄别电路和所述第三逻辑处理器连接,所述触发输入模块用于接收外部触发信号,所述第三触发甄别电路用于处理所述外部触发信号,并将处理后的所述外部触发信号传输至所述第三逻辑处理电路,所述外部触发信号为所述同步触发信号的一种。

19.根据本实用新型一个实施例的超导量子计算机时序信号传输系统,所述时钟板卡还包括同步输入模块,所述同步输入模块与所述第三逻辑处理器连接,所述同步输入模块用于接收外部同步信号,并将所述外部同步信号输出至所述第三逻辑处理器。

20.本实用新型的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本实用新型的实践了解到。

附图说明

21.本实用新型的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

22.图1是本实用新型实施例提供的超导量子计算机的集成电子学系统的结构示意图;

23.图2是本实用新型实施例提供的电子学集成机箱内的部分结构示意图;

24.图3是本实用新型实施例提供的电子学集成机箱内的部分结构示意图;

25.图4是本实用新型实施例提供的超导量子计算机的集成电子学系统的背板的结构示意图;

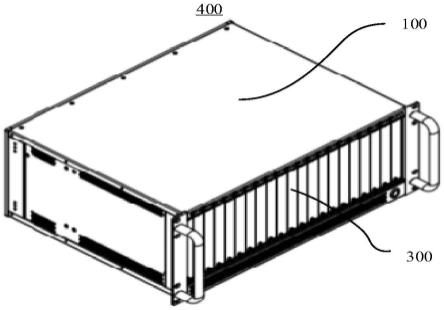

26.图5是本实用新型实施例提供的超导量子计算机的集成电子学系统的机箱的结构

示意图;

27.图6是本实用新型实施例提供的量子比特调制板卡的结构示意图;

28.图7是本实用新型实施例提供的量子比特读取板卡的结构示意图;

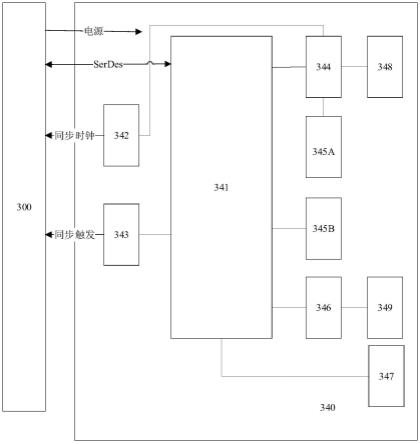

29.图8是本实用新型实施例提供的时钟板卡的结构示意图;

30.图9是本实用新型实施例提供的主控板卡的结构示意图;

31.图10是本实用新型实施例提供的超导量子计算机的结构示意图。

32.附图标记:100:机箱壳体;200:供电线;300:背板;

33.310:量子比特调制板卡;311:第一处理器;312:第一高速数模转换器;313:第一滤波电路;314:第一增益调节模块;315:第一输出驱动模块;316:第一动态随机存储器;

34.320:量子比特读取板卡;321:第二处理器;322:第一高速模数转换器;323:第二滤波电路;324:第二增益调节模块;325:第二高速数模转换器;326:第三滤波电路;327:第三增益调节模块;328:第二输出驱动模块;329:第二动态随机存储器;

35.330:主控板卡;331:第一逻辑处理器;332:第二逻辑处理器;333:第三动态随机存储器;334:微波控制模块;335:直流源控制模块;336:通信接口;337:第一触发甄别电路;338:第一锁相环电路;

36.340:时钟板卡;341:第三逻辑处理器;342:时钟缓冲寄存器;343:触发缓冲寄存器;344:第三锁相环电路;345a:时钟输出模块;345b:触发输出模块;346:第三触发甄别电路;347:同步输入模块;348:时钟输入模块;349:触发输入模块;

37.350:电子学测控板卡单元;

38.400:机箱;

39.500:时钟同步系统。

具体实施方式

40.下面详细描述本实用新型的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本实用新型,而不能理解为对本实用新型的限制。

41.在本实用新型的描述中,需要理解的是,术语“上”、“内”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

42.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示意性实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

43.下面参考图1-图10描述根据本实用新型实施例的超导量子计算机及其集成电子学系统、量子比特信号读出系统、电子学系统集成机箱以及时序信号传输系统。

44.本实用新型实施例的超导量子计算机的集成电子学系统包括背板300、电子学测

控板卡单元350和主控板卡330。

45.其中,如图4所示,背板300设有多个插槽,电子学测控板卡单元350的板卡与背板300的插槽插接,主控板卡330与背板300的插槽插接。

46.例如,背板300上设有十八个插槽,可供插接四个电子学测控板卡单元350,包括十二块量子比特调制板卡310,四块量子比特读取板卡320,一块主控板卡330及其他板卡。

47.再例如,背板300上也可以设有十二个插槽,可供插接两个电子学测控板卡单元350,包括六块量子比特调制板卡310,四块量子比特读取板卡320,一块主控板卡330及其他板卡。

48.背板300上插槽数目的可控性,可以使得背板300上的电子学测控板卡单元350的数目和插拔情况根据实际应用的调整,整体结构的适应性强。

49.背板300用于传输数据信号,主控板卡330用于通过背板300控制电子学测控板卡单元350进行量子比特的电子学测控。

50.相关技术中,通过模块化的设计来实现量子比特逻辑状态读取、检测和回传,在进行多比特的量子比特测控时,通常需要多台仪器设备或者多套量子测控系统组合,多个设备间的控制繁琐,数据处理规范不统一,处理效率低。

51.本实用新型实施例通过主控板卡330控制电子学测控板卡单元350进行量子比特的电子学测控,背板300上的电子学测控板卡单元350的数目和插拔情况可根据实际应用调整,在进行多比特的量子比特测控时,控制简单,数据处理规范统一,处理效率相比相关技术大幅提升。

52.根据本实用新型实施例的超导量子计算机的集成电子学系统,通过主控板卡330控制电子学测控板卡单元350进行量子比特的电子学测控,背板300上的电子学测控板卡单元350的数目和插拔情况可根据实际应用调整,实现多量子比特测控,处理效率高。

53.可以理解的是,电子学测控板卡单元350是超导量子计算机的超导量子计算机的量子比特信号读出系统的部件。

54.本实用新型实施例的超导量子计算机的量子比特信号读出系统包括多个电子学测控板卡单元350,每个电子学测控板卡单元350包括量子比特读取板卡320和至少一个量子比特调制板卡310,量子比特调制板卡310用于获取并调制量子比特的状态信息,量子比特读取板卡320用于读取并输出量子比特的状态信息;

55.需要说明的是,每个电子学测控板卡单元350包括量子比特读取板卡320和一个或者多个量子比特调制板卡310。

56.例如,一个电子学测控板卡单元350可以包括一个量子比特读取板卡320和一个量子比特调制板卡310。

57.再例如,一个电子学测控板卡单元350可以包括一个量子比特读取板卡320和三个量子比特调制板卡310。

58.电子学测控板卡单元350上的量子比特调制板卡310数目的可调性,可以灵活地应对多比特量子的测控。

59.超导量子计算机的量子比特信号读出系统还包括反馈控制线,同一个电子学测控板卡单元350中的量子比特调制板卡310和量子比特读取板卡320通过反馈控制线连接,反馈控制线用于传输量子比特的状态信息。

60.在实际执行中,反馈控制线可以设置在超导量子计算机的背板300上,同一个电子学测控板卡单元350内的量子比特读取板卡320通过反馈控制线,直接对该电子学测控板卡单元350内的三个量子比特调制板卡310进行反馈控制。

61.同一个电子学测控板卡单元350中的量子比特调制板卡310和量子比特读取板卡320通过反馈控制线连接,在该电子学测控板卡单元350中,量子比特调制板卡310执行量子比特的状态的调制工作,量子比特读取板卡320执行量子比特的状态的读取输出工作,完成量子比特的电子学测控。

62.在一些实施例中,超导量子计算机的集成电子学系统的电子学测控板卡单元350包括量子比特读取板卡320和至少一个量子比特调制板卡310,量子比特读取板卡320与背板300的插槽插接,量子比特调制板卡310也与背板300的插槽插接,量子比特调制板卡310用于获取并调制量子比特的状态信息,量子比特读取板卡320用于读取并输出量子比特的状态信息。

63.相关技术中,量子比特的读取和调制过程大多是通过调制模块和读取模块中间通过主控板传输,这样信息在传输的过程中从读取模块传送至主控板卡330,主控板卡330再传输至调制模块,可以看出信息的传输起始和终点在读取模块和调制模块,相关技术需要主控板卡330当作中介,在量子比特的电子学测控过程涉及其他无关部件,整体过程效率低下。

64.本实用新型实施例中在背板300上增设了反馈控制线,量子比特读取板卡320在采集到数据之后,可以直接通过背板300上设置的反馈控制线,将量子比特的状态信息直接传输至量子比特调制板卡310内,中间省去了在不相关部件过程的传输、处理、滞留时间,有效的提升了量子比特读取和调制过程的效率。

65.根据本实用新型实施例超导量子计算机的量子比特信号读出系统,在背板300上增设反馈控制线,可以使得在同一个电子学测控板卡单元350内的量子比特读取板卡320直接对相应的量子比特调制板卡310进行输出量子比特的状态信息,信息传输效率高,物理结构简单,方便后续的扩展。

66.在一些实施例中,电子学测控板卡单元350可以包括一个量子比特读取板卡320和三个量子比特调制板卡310。

67.其中,如图1所示,一块量子比特调制板卡310包含四通道输出,两块量子比特调制板卡310可以为四个量子比特提供xy操控,另一块量子比特调制板卡310的四通道为量子比特提供快z操控,一块量子比特读取板卡320可以读取四个量子比特信息,一块量子比特读取板卡320包括两通道的解调输出和两通道的数据采集,一个电子学测控板卡单元350可以为四个量子比特提供电子学测控。

68.在一些实施例中,量子比特调制板卡310包括至少一路第一任意波形生成通道,量子比特读取板卡320包括至少一路第二任意波形生成通道以及至少一路数据采集通道,第一任意波形生成通道用于调制量子比特的状态信息,第二任意波形生成通道用于解调量子比特的状态信息,数据采集通道用于读取量子比特的状态信息。

69.需要说明的是,每个量子比特调制板卡310可以包括一路第一任意波形生成通道或多路任意波生成通道,量子比特读取板卡320可以包括一路第二任意波形生成通道或者多路第二任意波形生成通道,一路数据采集通道或者多路数据采集通道。

70.例如,量子比特调制板卡310可以包括一路第一任意波形生成通道,量子比特读取板卡320可以包括一路第二任意波形生成通道以及一路数据采集通道。

71.再例如,量子比特调制板卡310可以包括四路任意波形生成通道,量子比特读取板卡320可以包括两路第二任意波形以及两路数据采集通道。

72.如图6所示,量子比特调制板卡310包括第一处理器311,第一处理器311连接着至少一路第一任意波形生成通道,第一任意波形生成通道用于调制量子比特的状态信息。

73.第一任意波形生成通道包括依次连接的第一高速数模转换器312、第一滤波电路313、第一增益调节模块314和第一输出驱动模块315,第一高速数模转换器312与第一处理器311连接。

74.其中,第一高速数模转换器312是将第一处理器311输出的数字信号转换为可供滤波电路处理的波形模拟信号,第一滤波电路313将第一高速数模转换器312转换过来的波形信号减少其高频成分,保留其低频部分,使后续输出的波形质量更好,第一增益调节模块314是调节波形信号的电压到合适的大小,第一输出驱动模块315将调制好的波形信号输出至背板300上。

75.量子比特调制板卡310还包括第一动态随机存储器316,第一动态随机存储器316与第一处理器311连接,动态随机存储器可以是一种半导体存储器,用于存储第一处理器311所收到的数字信号。此处第一动态随机存储器316可以是双倍速率同步动态随机存储器,与常规动态随机存储器相比双倍速率同步动态随机存储器具有更高数据传输效率。

76.在一些实施例中,量子比特调制板卡310包括四路任意波形生成通道、第一处理器311、第一动态随机存储器316,第一处理器311接收到从背板300输出的反馈控制信号,将信号输入第一动态随机存储器316中进行存储,在需要的时候读取。

77.第一处理器311再将反馈信号输入至第一高速数模转换器312中,将数字信号转换为波形信号,第一高速数模转换器312将转换的波形信号输入至第一滤波电路313,滤波电路对波形信号进行过滤,保留其有用的低频部分,使得波形信号质量更好,再将波形信号输入至第一增益调节模块314,第一增益调节模块314对波形信号的电压进行合适的大小调节,再由第一输出驱动模块315将调制后的波形信号输出至背板300上。

78.如图7所示,量子比特读取板卡320包括第二处理器321,第二处理器321设有至少一路数据采集通道和至少一路第二任意波形生成通道,第二任意波形生成通道用于解调量子比特的状态信息,数据采集通道用于读取量子比特的状态信息。

79.数据采集通道包括依次连接的第一高速模数转换器322一端、第二滤波电路323和第二增益调节模块324,第一高速模数转换器322另一端与第二处理器321连接。

80.其中,第一高速模数转换器322是将接收的波形模拟信号转换为可供滤波电路处理的数字信号,第二滤波电路323将高速模数转换器转换过来的数字信号减少其高频成分,保留其低频部分,使后续输出的波形质量更好,增益调节模块是调节数字信号电压到合适的大小。

81.第二任意波形生成通道包括依次连接的第二高速数模转换器325、第三滤波电路326、第三增益调节模块327和第二输出驱动模块328,第二高速数模转换器325与第二处理器321连接。

82.其中,第二高速数模转换器325是将第二处理器321输出的数字信号转换为可供滤

波电路处理的波形模拟信号,第三滤波电路326将高速数模转换器转换过来的波形信号减少其高频成分,保留其低频部分,使后续输出的波形质量更好,第三增益调节模块327是调节波形信号的电压到合适的大小,第二输出驱动模块328将解调好的波形信号输出至背板300上。

83.量子比特读取板卡320还包括第二动态随机存储器329,第二动态随机存储器329与第二处理器321连接。第二动态随机存储器329可以是一种半导体存储器,用于存储第二处理器321所收到的数字信号。

84.可选的第一动态随机存储器316也可以是双倍速率同步动态随机存储器,与常规动态随机存储器相比双倍速率同步动态随机存储器具有更高数据传输效率。

85.在一些实施例中,量子比特读取板卡320包括两路第二任意波形生成通道、两路数据采集通道、第二处理器321、第二动态随机存储器329,其中,第二处理器321接收到从背板300输出的反馈控制信号,将信号输入第二动态随机存储器329中进行存储,在需要的时候读取。

86.第二处理器321还接收由两路数据采集通道输出的量子比特状态信息,第二处理器321将处理好后的量子比特信息传输至背板300上。

87.如图6和图7所示,量子比特调制板卡310包括四路第一任意波形生成通道,量子比特读取板卡320包括两路第二任意波形生成通道和两路数据采集通道,第一任意波形生成通道用于调制量子比特的状态信息,第二任意波形生成通道用于解调量子比特的状态信息,数据采集通道用于读取量子比特的状态信息。

88.如图9所示,主控板卡330包括第一逻辑处理器331,第一逻辑处理器331用于与背板300的插槽所插接的板卡进行数据通信。

89.第一逻辑处理器331控制电子学测控板卡单元350对量子比特测控的相关工作。

90.主控板卡330还包括第二逻辑处理器332,第二逻辑处理器332与第一逻辑处理器331连接,第一逻辑处理器331用于将数据处理结果传输至第二逻辑处理器332,第二逻辑处理器332用于输出数据处理结果。

91.在一些实施例中,第一逻辑处理器331对量子比特的测控进行控制,向电子学测控板卡单元350发出控制信号,电子学测控板卡单元350接收信号后开始进行测控相关工作,量子比特读取板卡320采集量子比特信息,输入至背板300上,通过反馈控制线传输至量子比特调制板卡310,量子比特调制板卡310接收到量子比特的状态信息后,量子比特调制板卡310中的第二处理器321将量子比特状态信息传输至第一任意波生成通道进行调制,再将调制完成的量子比特状态信息输入至背板300,背板300再将量子比特状态信息输出至第一逻辑处理器331,第一逻辑处理器331并输出至第二逻辑处理器332中,第二逻辑处理器332将数据处理结果输出至上位机或交换机。

92.时钟板卡340与背板300的插槽插接,时钟板卡340用于为背板300的插槽所插接的板卡提供同步时钟信号和同步触发信号中的至少一个。

93.实际执行中,时钟板卡340通过背板300向背板300的插槽所插接的板卡发送同步时钟信号,为背板300的插槽上的各个板卡提供时钟信息,时钟板卡340通过背板300向背板300的插槽所插接的量子比特调制板卡310、量子比特读取板卡320发送同步触发信号,以触发一个电子学测控板卡单元350内的量子比特调制板卡310、量子比特读取板卡320进行测

控。

94.可以理解的是,时钟板卡340是超导量子计算机时序信号传输系统的部件,下面对本实用新型实施例的超导量子计算机时序信号传输系统进行描述。

95.本实用新型实施例的超导量子计算机时序信号传输系统包括时钟板卡340和时序信号线,时钟板卡340用于提供同步时钟信号和同步触发信号中的至少一个,时序信号线用于传输同步时钟信号和同步触发信号中的至少一个,时序信号线包括第一时序信号线和第二时序信号线。

96.需要说明的是,时钟板卡340可以提供同步时钟信号和同步触发信号中的一个,也可以都提供,时序信号线用于传输同步时钟信号和同步触发信号中的一个,也可以都传输。

97.例如,时钟板卡340可以只提供同步时钟信号,也可以只提供同步触发信号。

98.再例如,时钟板卡340可以同时提供同步时钟信号和同步触发信号。

99.时钟板卡340和对应时序信号线传输的可控性,保证了超导量子计算机时序信号传输系统中整体时序调度的灵活性,传输效率高。

100.在电子学测控板卡单元350中,电子学测控板卡单元350的板卡与时钟板卡340通过第一时序信号线连接,电子学测控板卡单元350用于测控量子比特的状态信息;

101.实际执行中,每个电子学测控板卡单元350包括量子比特读取板卡320和量子比特调制板卡310,其中,量子比特调制板卡310用于获取并调制量子比特的状态信息,量子比特读取板卡320用于读取并输出量子比特的状态信息,量子比特读取板卡320和量子比特调制板卡310分别通过第一时序信号线与时钟板卡340相连。

102.主控板卡330与时钟板卡340通过第二时序信号线连接,主控板卡330用于对时钟板卡340和电子学测控板卡单元350进行控制和数据交互;

103.其中,第一时序信号线和第二时序信号线走线等长。

104.实际执行中,系统中各板卡的同步时钟和同步触发信号由时钟板卡340提供,时钟板卡340到其他板卡的时钟信号和触发信号都在背板300做走线等长,使背板300到各板卡的时钟信号和触发信号是同相位的。

105.相关技术中,实现对更多量子比特数目的操控,只是简单的堆砌量子测控设备的数量,所以这些测控设备组合工作时,将会面对时序信号的同步性问题,不同量子测控设备的时序,相位不一,在统一对多比特量子进行测控时,无法同步工作,也就无法组合去对多比特的测控。

106.本实用新型实施例中,通过一个时钟板卡340设置,并且设置时钟板卡340到其他板卡的时钟信号和触发信号在背板300做走线等长,使得背板300到各板卡的时钟信号和触发信号是同相位的,从而使得多比特的量子测控可以统一操作,同步工作。

107.根据本实用新型实施例的超导量子计算机时序信号传输系统,通过设置时钟板卡340到其他板卡的时钟信号和触发信号在背板300做走线等长,使得背板300到各板卡的时钟信号和触发信号是同相位的,使得超导量子计算机在进行多比特的测控时,可以统一操作,同步工作。

108.如图8所示,时钟板卡340包括时钟缓冲寄存器342,主控板卡330包括第一锁相环电路338,电子学测控板卡单元350的板卡包括第二锁相环电路,时钟缓冲寄存器342用于输出同步时钟信号,第一锁相环电路338和第二锁相环电路用于接收同步时钟信号。

109.在一些实施例中,时钟板卡340包括时钟缓冲寄存器342和第三锁相环电路344,主控板卡330包括第一锁相环电路338,电子学测控板卡单元350的板卡包括第二锁相环电路,在时钟板卡340中,时钟缓冲寄存器342用于输出同步时钟信号,第三锁相环电路344用于接收外部同步时钟信号,在主控板卡330中,第一锁相环电路338用于接收背板300来自时钟板卡340的同步时钟信号,电子学测控板卡单元350的板卡中的第二锁相环电路也用于接收背板300来自时钟板卡340的同步时钟信号。

110.第三锁相环电路344和时钟缓冲寄存器342连接,第三锁相环电路344向时钟缓冲寄存器342输出参考时钟信号,参考时钟信号为同步时钟信号的一种。

111.时钟板卡340还包括时钟输出模块345a,时钟输出模块345a和第三锁相环电路344连接,时钟输出模块345a用于将第三锁相环电路344输出的参考时钟信号向外部输出。

112.时钟板卡340还包括时钟输入模块348,时钟输入模块348与第三锁相环电路344连接,时钟输入模块348用于向第三锁相环电路344输入外部时钟信号,第三锁相环电路344于向时钟缓冲寄存器342输出外部时钟信号,外部时钟信号为同步时钟信号的一种。

113.时钟板卡340还包括触发缓冲寄存器343和第三触发甄别电路346,主控板卡330包括第一触发甄别电路337,电子学测控板卡单元350的板卡包括第二触发甄别电路,触发缓冲寄存器343用于输出同步触发信号,第一触发甄别电路337和第二触发甄别电路用于接收、处理和发送同步触发信号,第三触发甄别电路346用于处理并输出触发信号至第三逻辑处理器341。

114.时钟板卡340还包括第三逻辑处理器341,第三逻辑处理器341与触发缓冲寄存器343连接,第三逻辑处理器341用于向触发缓冲寄存器343输出基准触发信号,基准触发信号为同步触发信号的一种。

115.时钟板卡340还包括触发输出模块345b,触发输出模块345b与第三逻辑处理器341连接,触发输出模块345b用于将第三逻辑处理器341输出的基准触发信号向外部输出。

116.时钟板卡340还包括触发输入模块349和第三触发甄别电路346,触发输入模块349和第三触发甄别电路346连接,第三触发甄别电路346和第三逻辑处理器341连接,触发输入模块349用于接收外部触发信号,第三触发甄别电路346用于处理外部触发信号,并将处理后的外部触发信号传输至第三逻辑处理器341,外部触发信号为同步触发信号的一种。

117.时钟板卡340还可以包括同步输入模块347,同步输入模块347与第三逻辑处理器341连接,同步输入模块347用于接收外部同步信号,并将外部同步信号输出至第三逻辑处理器341,其中外部同步信号用于同步多个电子学测控板卡系统

118.在一些实施例中,时钟板卡340支持外部时钟输入和参考时钟输出功能,该功能可以让多个系统共有统一的参考时钟,时钟板卡340支持外部触发输入和触发输出功能,该功能可以让多个系统共有相同的触发频率的内容。

119.通过统一的参考时钟,多个系统就可以保持同步的启动与终止工作,通过相同的触发频率内容,就可以让多个系统共同对一个多量子比特进行测量。

120.上述实施例中的时钟板卡340,主控板卡330,电子学测控板卡单元350均设置于背板300上。

121.可以理解的是,超导量子计算机的集成电子学系统可以集成为机箱400,下面对本实用新型实施例提供的超导量子计算机电子学系统集成机箱进行描述。

122.本实用新型实施例的超导量子计算机电子学系统集成机箱,包括

123.机箱壳体100;

124.背板300,背板300设于机箱壳体100,背板300内设有信号传输线,背板300上设有至少四个槽;

125.需要说明的是,背板300上可以设有四个插槽或者更多个插槽。

126.例如,背板300上可以设置四个插槽,供给一个主控板卡330、一个时钟板卡340、一个量子比特调制板卡310和一个量子比特读取板卡320进行插接。

127.再例如,背板300上可以设置十八个插槽,供给一个主控板卡330、一个时钟板卡340、十二个量子比特调制板卡310和四个量子比特读取板卡320进行插接。

128.主控板卡330、时钟板卡340、至少一个量子比特调制板卡310和至少一个量子比特读取板卡320通过背板300上的插槽插接于背板300,且主控板卡330、时钟板卡340、至少一个量子比特调制板卡310和至少一个量子比特读取板卡320均设有serdes接口,每个板卡的serdes接口都接在信号传输线上,信号传输线用于连接serdes接口以及传输serdes接口输出的数据信号。

129.需要说明的是,背板300上包括一个或者多个量子比特读取板卡320和一个或者多个量子比特调制板卡310。

130.例如,背板300上可以插接一个量子比特读取板卡320和一个量子比特调制板卡310。

131.再例如,背板300上也可以插接一个量子比特读取板卡320和三个量子比特调制板卡310。

132.在所有主控板卡330、时钟板卡340、量子比特调制板卡310和量子比特读取板卡320上均设有serdes接口用于进行控制和数据交互,其中信号传输线设置于背板300上,用于连接不同的serdes接口和传输serdes接口输出的数据信号,其中每个板卡的serdes接口都接在了信号传输线上。

133.实际执行中,如图5所示,背板300设置于机箱壳体100上,在背板300上设有信号传输线,在所有主控板卡330、时钟板卡340、量子比特调制板卡310和量子比特读取板卡320上均设有serdes接口,背板300上的信号传输线用于连接各个serdes接口以及传输serdes接口输出的数据信号。

134.相关技术中,要实现对更多比特数目的测控,量子测控设备的数量会呈现几何增长,这些测控设备之间存在相互之间的控制信号传输、供电电源的分配、时序信号的同步和统一、量子比特信号的反馈等等互通互联作业,上述作业有赖于各类线路布置和连接,若不同设备之间两两相互连接进行数据信息的传递,那么整个测控设备会出现纷繁杂乱的数据连接线,不仅显得构造臃肿,工作效率也低下。

135.在本实用新型实施例中,如图5所示,通过机箱400进行集成,在机箱壳体100上设置有背板300,背板300上设有信号传输线,背板300上的信号传输线连接着背板300上的主控板卡330,在时钟板卡340、量子比特调制板卡310和量子比特读取板卡320上设有serdes接口,从而使得多个电子学测控板卡单元350、主控板卡330、时钟板卡340可以相互之间传输控制信号,完成供电电源的分配、时序信号的同步和统一以及量子比特信号的反馈互通互联作业,整体结构集成度高,能够很好的协调不同的测控设备并使得各设备之间的连接

线路规整有条理,工作效率高,整个系统的扩展性大大提升。

136.根据本实用新型实施例的超导量子计算机电子学系统集成机箱,通过在设于机箱壳体100上的背板300上设置信号传输线,信号传输线连接serdes接口以及传输serdes接口输出的信号,使得多个电子学测控板卡单元350、主控板卡330和时钟板卡340可以相互之间传输控制信号,完成了供电电源的分配,实现了时序信号的同步和统一以及量子比特信号的反馈互通互联作业。

137.如图2和图3所示,第一高速连接器可以为xj3,第二高速连接器可以为xp3。

138.背板300还设有第一高速连接器和多个第二高速连接器,信号传输线包括第一信号传输线,第一高速连接器的第一端通过第一信号传输线分别与多个第二高速连接器的第一端连接,第一高速连接器的第二端与主控板卡330的serdes接口连接,多个第二高速连接器的第二端分别与至少一个量子比特调制板卡310和至少一个量子比特读取板卡320的serdes接口一一对应连接,第一信号传输线用于传输测控信号。

139.第一高速连接器两端分别连接着多个第二高速连接器的第一端和主控板卡330的serdes接口,从而第一高速连接器可以向主控板卡330收发多路serdes信号。

140.第二高速连接器两端分别连着第一高速连接器、至少一个量子比特调制板卡310和至少一个量子比特读取板卡320的serdes接口,从而可以收发电子学测控板卡单元350中量子比特调制板卡310和量子比特读取板卡320的serdes信号。

141.其中,第一高速连接器与主控板卡330和第二高速连接器,第二高速连接器与量子比特调制板卡310和量子比特读取板卡320之间用第一信号传输线连接,第一信号传输线完成了量子比特测控的信号传输。

142.如图2和图3所示,第三高速连接器可以为xj3,第四高速连接器可以为xp3。

143.背板300还设有第三高速连接器和多个第四高速连接器,信号传输线包括第二信号传输线,第三高速连接器的第一端通过第二信号传输线分别与多个第四高速连接器的第一端连接,第三高速连接器的第二端与时钟板卡340的serdes接口连接,多个第四高速连接器的第二端分别与主控板卡330、至少一个量子比特调制板卡310和至少一个量子比特读取板卡320的serdes接口一一对应连接,第二信号传输线用于传输同步时钟信号和同步触发信号中的至少一个。

144.其中,时钟板卡340的serdes接口通过第二信号传输线向第三高速连接器相连,第三高速连接器通过第二信号传输线与多个第四高速连接器的第一端相连,第四高速连接器的第二端通过信号传输线和serdes接口向主控板卡330和多个量子比特调制板卡310、量子比特读取板卡320输出时钟信号和触发信号。

145.主控板卡330还包括第一锁相环电路338和第一触发甄别电路337,第一锁相环电路338用于接收同步时钟信号,第一触发甄别电路337用于接收同步触发信号。

146.其中,第一锁相环电路338和第一触发甄别电路337均用serdes接口通过第二信号传输线与第四高速连接器相连,接收来自时钟板卡340的时钟信号和触发信号。

147.背板300上连接着电源模块,电源模块用于为背板300以及背板300的插槽所插接的板卡提供电能。

148.例如,如图2和图3所示,电源端子对应xp4,供电接口对应xj4,背板300上还设有电源端子、供电线200以及多个供电接口,电源端子通过供电线200分别与多个供电接口连接,

电源端子用于连接电源,多个供电接口分别与主控板卡330、时钟板卡340、量子比特调制板卡310和量子比特读取板卡320一一对应连接。

149.在一些实施例中,电源端子一端连接在电源上,另一端通过供电线200与多个供电接口相连,多个供电接口分别与各个板卡一一对应连接,为各个板卡进行电源的供应。

150.主控板卡330包括第一逻辑处理器331,serdes接口设置于第一逻辑处理器331上,通过信号传输线主控板卡330对其他板卡进行数据信号的收发。

151.主控板卡330还包括微波控制模块334和直流源控制模块335,微波控制模块334和直流源控制模块335分别与第一逻辑处理器331连接,微波控制模块334用于控制微波功率和频率,直流源控制模块335用于控制直流源电压输出。

152.主控板卡330还包括第二逻辑处理器332,第二逻辑处理器332与第一逻辑处理器331连接,第二逻辑处理器332设有通信接口336。

153.在一些实施例中,通信接口336是与交互上位机建立通信连接的高速网口或pcie接口,第二逻辑处理器332通过通信接口336实现输出数据和处理结果的功能。

154.主控板卡330内的第一逻辑处理器331和第二逻辑处理器332通过数据传输线相连,第一逻辑处理器331上的serdes接口收到来自其他板卡处理完成的信息后,通过数据传输线传输至第二逻辑处理器332,第一逻辑处理器331也用于对背板300的插槽所插接的板卡发送控制信号,第二逻辑处理器332通过通信接口336向上位机输出测控结果。

155.主控板卡330还包括第三动态随机存储器333和第四动态随机存储器,第三动态随机存储器333与第一逻辑处理器331连接,第四动态随机存储器与第二逻辑处理器332连接。

156.时钟板卡340和主控板卡330布置于背板300的中部,至少一个量子比特调制板卡310和至少一个量子比特读取板卡320布置于背板300的两端,至少一个量子比特调制板卡310和至少一个量子比特读取板卡320分布于时钟板卡340和主控板卡330的两侧。

157.在一些实施例中,时钟板卡340和主控板卡330布置于背板300的中部,十二个量子比特调制板卡310和四个量子比特读取板卡320布置于背板300的两端,每一端有两个电子学测控板卡单元350,每一个电子学测控板卡单元350有三个量子比特调制板卡310和两个量子比特读取板卡320。

158.需要说明的是,背板300上包括一个或者多个量子比特读取板卡320和一个或者多个量子比特调制板卡310。

159.例如,背板300上可以插接一个量子比特读取板卡320和一个量子比特调制板卡310。

160.再例如,背板300上也可以插接一个量子比特读取板卡320和三个量子比特调制板卡310。

161.本实用新型实施例还提供一种超导量子计算机,包括:

162.多个上述的超导量子计算机集成电子学系统;

163.如图10所示,设有多个网络连接端口的交换机,多个网络连接端口和多个超导量子计算机的集成电子学系统的主控板卡330一一对应连接。

164.其中,超导量子计算机集成电子学系统包括至少一套电子学测控板卡单元350、一个主控板卡330和一个时钟板卡340。

165.需要说明的是,超导量子计算机集成电子学系统上包括一套电子学测控板卡单元

350或者多套电子学测控板卡单元350。

166.例如,超导量子计算机集成电子学系统上包括一套电子学测控板卡单元350,可供插接包括三块量子比特调制板卡310,一块量子比特读取板卡320。

167.再例如,超导量子计算机集成电子学系统上包括四套电子学测控板卡单元350,可供插接包括十二块量子比特调制板卡310,四块量子比特读取板卡320。

168.在一些实施例中,超导量子计算机集成电子学系统机箱的背板300上设置了十八个插槽,超导量子计算机电子学系统上包括了四套电子学测控板卡单元350、一块主控板卡330和一块时钟板卡340,主控板卡330和时钟板卡340插接在背板300中间,两侧各分布了两套电子学测控板卡单元350。

169.超导量子计算机可以包括多个超导量子计算机集成电子学系统。

170.在一些实施例中,超导量子计算机可以包括三个超导量子计算机集成电子学系统,其中交换机的三个网络连接端口与对应不同超导量子计算机集成电子学系统的主控板卡330的第二逻辑处理器332相连,不同超导量子计算机集成电子学系统的主控板卡330收到的量子比特的测控结果输出至交换机中。

171.如图10所示,超导量子计算机包括设有多个时钟同步端口的时钟同步系统500,多个时钟同步端口与多个超导量子计算机的集成电子学系统的时钟板卡340一一对应连接。

172.在一些实施例中,时钟板卡340中的第三逻辑处理器341接收来自时钟同步系统500发送的时钟信号、同步信号和触发信号,再经由第三逻辑处理器341的serdes接口与背板300上的信号传输线传输至各个板卡,使得不同超导量子计算机集成电子学系统以及同一超导量子计算机集成电子学系统中不同板卡达到统一操作,达到同步工作的效果。

173.尽管已经示出和描述了本实用新型的实施例,本领域的普通技术人员可以理解:在不脱离本实用新型的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本实用新型的范围由权利要求及其等同物限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。