1.本发明涉及声呐电子系统技术领域,具体涉及一种多波束声呐信源信号生成电路及设备。

背景技术:

2.多波束声呐是一种基于水声技术用于执行水下观察探测任务的设备,在反蛙人入侵、水下航行器监测、近海监视防护等领域发挥着重要作用。在执行水下安防任务过程中,声呐发射机的主要任务就是产生一种或多种特定形式(波形)的信号并对其进行功率放大,驱动下级换能器将放大后的电信号转换位声波辐射至水体中。通常要求多波束声呐的信号源能够根据探测环境的不同做出相应的调整,以便在不同场景下针对不同目标均能获得较好的探测效果,这对多波束声呐提出了信号源可调整的需求。

3.目前在绝大多数海油平台安防、码头岸口等应用场景中,针对不同的探测目标,不同类型的脉冲信号在探测、定位等方面都具有各自优缺点,如利用cw信号进行高混响背景下的高速目标探测,fm脉冲信号的距离高分辨率和prn脉冲综合优势等,这就需要通过调节发射信号源生成的电信号的体制参数大小来实现。

4.现有的技术大多采用直接数字合成(dds)数字信号处理的方式,由不同的相位给出电压幅值,经过相幅变换后进行滤波,dds输出信号的频率、相位和幅度可在处理器控制下完成精确快速变换,这种方式具有高分辨率、快速转换时间的优势,但随着发射通道数的增加,所需信号形式种类的增多,dds输出频带范围受到内部dac和波形存储器工作速率的限制,由于其全数字方式设计使得输出信号存在杂散(相位累加器舍位误差造成、因存储器有限字长幅度量化误差造成和dac非理性特性造成等),考虑杂散影响结合pll频率合成技术结合dds虽可以解决,但无形中会造成硬件资源体积和成本的增加,使得多波束声呐难以适应更多的场景需求。

技术实现要素:

5.针对上述问题,发明人提供了一种多波束声呐信源信号生成电路及设备,可生成不同信号体制的声呐信号,满足实际使用需求。

6.根据第一方面,本发明提供了一种多波束声呐信源信号生成电路,其特征在于,包括:

7.数字编码电路模块,设于水下声呐内部,用于将接收到的原始信号数据包解译为多通道模拟信号,并将多通道模拟信号转换为多路编码数字信号,还用于将多路编码数字信号复制为时序同步的两组信号;

8.多通道信号转换电路,与所述数字编码电路模块的输出端信号连接,用于将第一组信号转换为正半周信号,将第二组信号转换为负半周信号;

9.功率放大电路,与多通道信号转换电路的输出端信号连接,所述功率放大电路的输出端与换能器连接,用于将正半周信号及负半周信号放大后接入换能器,驱动换能器发

出信源信号。

10.进一步地,多通道信号转换电路包括:多组锁存触发器组,每组锁存触发器组包括多片触发器芯片,每片触发器芯片并行处理多路信号。

11.进一步地,所述功率放大电路包括:

12.驱动电路,其输入端与下拉电阻和所述多通道信号转换电路的输出端连接;

13.推挽放大电路,其输入端设有由二极管v3、v4和电阻r3、r4构成的吸收电路。

14.进一步地,所述推挽放大电路包括:由电容c5、c6和电阻r5、r6构成的吸收高次谐波电路。

15.进一步地,所述数字编码电路模块还用于:当数字编码电路模块的使能信号由低到高时,对每一个通道的模拟信号通过时钟采样信号进行采样,同时进行模数转换。

16.进一步地,所述多通道信号转换电路包括:锁存触发器组a1、锁存触发器组a2和锁存触发器组b1;

17.所述锁存触发器组a1的输入端与第一组信号和时钟信号clka连接,用于当发射允许使能信号为低电平时,时钟信号clka触发第一组信号并进行时序缓存,获得缓存区信号;

18.所述锁存触发器组a2与缓存区信号和时钟信号clkb连接,用于当发射使能信号再次有效时,时钟信号clkb直接触发缓存区信号,获得正半周信号;

19.所述锁存触发器组b1的输入端与第二组信号和时钟信号clkb,用于当发射使能信号有效时直接输出负半周信号。

20.进一步地,所述时钟信号clka、clkb频率相同,且存在1/4个时钟周期的相位差。

21.进一步地,所述锁存触发器组a1、锁存触发器组a2和锁存触发器组b1均由8片触发器芯片组成,每片锁存触发器芯片并行处理16路信号,所述锁存触发器组a1、锁存触发器组a2和锁存触发器组b1均可处理128路多通道信号。

22.根据第二方面,本发明还提供了一种多波束声呐信源信号生成设备,包括:上位机、换能器、如权利要求上所述的多波束声呐信源信号生成电路,所述上位机位于水上,且与所述数字编码电路模块网络连接,用于设定发射信号参数,根据发射信号参数同步生成指定信号,并将指定信号转换后打包成数据包下发给数字编码电路模块。

23.进一步地,所述上位机还用于将指定信号通过门限进行限幅,并将限幅后的指定信号转换为二值化信号,打包成数据包下发给数字编码电路模块。

24.相比现有技术,本发明的有益效果:

25.(1)本发明提供的多波束声呐信源信号生成电路及设备,可根据实际需要提供不同信号体制的信源信号,可解决因不同探测环境需求变化导致声呐信号发射机提供信号源自适应能力不足的问题。

26.(2)满足了低成本的设计需求,未使用数字频率合成芯片以及缓存记忆芯片等高成本解决方案,采用触发器芯片,具有缓冲存储、触发时延低、抗干扰能力强、使寿命长、成本低等优点,符合多波束声呐信号源系统安全、稳定、高效的设计要求。

附图说明

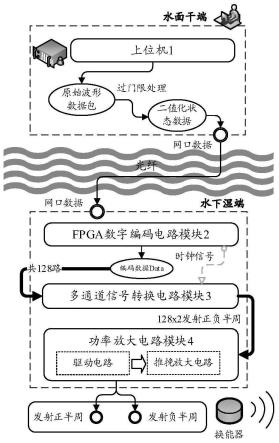

27.图1为实施例1的多波束声呐信源信号生成设备的示意图;

28.图2为实施例1中多通道信号转换电路原理图;

29.图3为实施例1中功率放大电路的原理图;

30.图4为图3中的驱动电路的原理图;

31.图5为实施例1中上位机生成原始信号波形及二值化处理原理图;

32.图6为实施例1中fpga编码电路模块时序编码数据生成原理图;

33.图7为实施例1中多通道信号转换电路模块各节点时序图。

具体实施方式

34.下面通过具体实施方式结合附图对本发明作进一步详细说明。

35.实施例1

36.如图1所示,本发明提供了一种多波束声呐信源信号生成设备,包括水面干端和水下湿端,水面干端为上位机1,其内置有信号生成软件,主要完成多波束声呐发射信号参数的配置,将原始波形数据通过rs串口发送到水下声呐头电子舱中,该程序为现有程序,在此不作赘述。水下湿端位于水下声呐头内部,其包括:依次信号连接的fpga数字编码电路模块2、多通道信号转换电路3、功率放大电路4及换能器。

37.fpga数字编码电路模块2与上位机1通过光纤进行连接,光纤将上位机1生成的数据包以网络传输协议传输给fpga数字编码电路模块2进行编码转换。多通道信号转换电路3与fpga数字编码电路模块2的输出端信号连接,用于将fpga数字编码电路模块2发送来的多路编码数字信号data转换成正半周信号和负半周信号具体地,如图2所示,多通道信号转换电路3包括:锁存触发器组a1、a2和b1,其中,锁存触发器组a1、a2和b1均由8片触发器芯片组成,每片锁存触发器芯片并行处理16路信号,因此,每组锁存触发器组a1、a2和b1均可处理128路多通道信号。在实际使用过程中,可根据实际情况进行相应调整,以实现如256/512等多路通道信号的处理。

38.如图3所示,功率放大电路4包括驱动电路及推挽放大电路,驱动电路输入ina/inb接正半周信号和负半周信号同时接入10kω下拉电阻r1、r2,保证无输入信号时推挽放大电路输入端为低电平。功率放大电路4接入12vdc完成对驱动电路供电,接入200vdc对推挽放大电路供电及变压转换。驱动电路采用双功率高速mosfet驱动芯片,输出峰值电流最大可达到1.5a,输入供电电压具有较宽的范围4.5v-18v。推挽放大电路输入端设有由二极管v3、v4和电阻r3、r4构成的吸收电路,防止推挽放大电路对驱动电路造成信号的串扰。驱动电路输入信号端接入驱动引脚是高阻抗的,同时也兼容ttl/cmos输入,驱动电路输出端outa和outb是低阻抗状态,同时也是cmos推挽式输出。输出端outa和outb经过直接吸收电路后接入推挽放大电路进行放大。推挽放大电路包括:mosfet管v1、v2,二极管v7、v8,变压器trans,由电容c5、c6和电阻r5、r6构成的吸收高次谐波电路,吸收高次谐波电路的设置可消除变压器trans感应产生的反向电压的峰值端尖刺干扰。推挽放大电路使换能器上获得声呐探测所需的最大电功率信号。输出端变压器trans采用高频功率型变压器进行升压,变比为n1∶n2=5∶8,通过变压后的正负半周信号接入换能器正负端。进一步地,mosfet管v1、v2能够通过最大电流限定为:

39.40.式中,p0为发射机的理论值功率,估算过程按照信号发射机输出功率理论值1.5倍计算(需考虑声呐实际工作式变压器损耗),v

cc

为mosfet管关断电压,v

ce

为mosfet管的开启电压。若考虑声呐发射信号源输出为占空比50%的方波时,mosfet管的导通时间为:

41.t

on

=1/2f042.f0为声纳生成发射信号的中心频率。

43.mosfet管在选取时,应满足开启时间tr和关断时间tf之和小于导通时间t

on

/10,以免产生较大的信号延迟。mosfet管v1导通时,加到mosfet管v2漏极上的电压变为2v

cc

;当mosfet管v2导通时,加到mosfet管v1漏极上的电压也为2v

cc

。同时考虑到变压器trans通常会引入尖峰脉冲影响,在选取mosfet管最大漏极源电压保留一定余量。

44.该推挽放大电路具有高度的抗闩锁性,因为其功率和电压额定值内的条件,当接地端gnd上出现高达5v的噪声尖峰(任一极性)时,电路功能不容易被损坏。当(任一极性)反向电流达到500ma加到电路上时,可直接接受并强制反馈到输出端,使得逻辑不受破坏,所述驱动电路中所有输入输出均可受到高达4千伏的防静电放电(esd)保护,同时增强后续推挽放大电路的功放能力。

45.具体地,多波束声呐信源信号生成的过程包括以下步骤:

46.下发原始信号步骤:人工在上位机1上设定发射信号参数,上位机1根据发射信号参数同步生成指定信号,并将指定信号转换后打包成数据包下发给fpga数字编码电路模块2。上位机1模拟原始信号数据方式可以忽略信号生成电路硬件噪声带来的干扰,保证了信号时序数据的稳定性。具体地,以中心频率为f0,初始相位的原始单频信号t∈[0,t],e(t)为信号包络,持续时间为t。定义信号幅度门限为t

th

,对s

ori

(t)连续进行过门限处理,即

[0047][0048]

其中,sh,s

l

分别对应于逻辑高电平于低电平状态。经转换后的信号波形如图5所示。图中以3个周期的单频信号方式为例进行说明,信号周期t=1/f0。通过门限t

th

进行信号限幅,转换为二值化状态数据,其中高电平状态sh(high level)可限幅至但不局限于门限t

th

,低电平状态s

l

(low level)可限幅至但不局限于t

th

。完成处理的二值化状态数据将通过光纤网络以数据包形式发送至fpga数字编码电路模块2。

[0049]

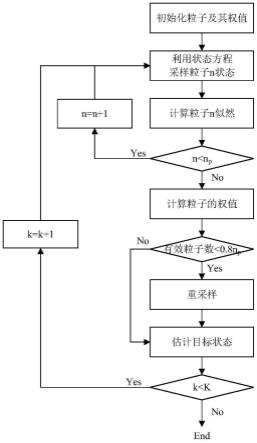

编码步骤:fpga数字编码电路模块2接收数据包后解译为多通道模拟信号,并将多通道模拟信号转换为多路编码数字信号data。具体地,fpga数字编码电路模块2通过网络通信协议收到上位机1发送过来的数据包后,当检测到使能信号由低到高时,对128个通道的模拟信号通过高频时钟采样信号进行采样,同时进行模数转换,采样信号频率fs,信号样本点数n=tfs,一个周期内的脉冲串经过fpga编码电路模块2进行编码转换后的数字信号如图6所示。128路编码信号脉冲串经过同步处理后存入arm内核中,供给后续多通道信号转换电路3进行处理。

[0050]

信号转换步骤:将多路编码数字信号data复制为时序同步的两组信号,多通道信号转换电路3将第一组信号转换为正半周信号将第二组信号转换为负半周信号

[0051]

具体地,fpga编码电路模块2输出的128路编码数据data表示为矩阵形式复制为两路时序同步的信号知第一组信号转换为正半周信号具体转换过程为:

[0052]

第一组信号和时钟信号clka输入锁存触发器组a1,锁存触发器组a2输入时钟信号clkb,时钟信号clka、clkb频率为且存在1/4个时钟周期的相位差。当发射允许使能信号为低电平时,时钟信号clka触发信号第一组信号并进行时序缓存,获得缓存区信号当发射使能信号再次有效时,缓存区信号输入锁存触发器组a2,时钟信号clkb直接触发缓存区信号获得正半周信号

[0053]

第二组信号转换为负半周信号具体过程为:

[0054]

第二组信号和时钟信号clkb输入锁存触发器组b1,当发射使能信号有效时直接输出负半周信号

[0055]

发射允许使能信号同时控制两组信号触发时序,经过锁存触发器组逻辑触发处理的两路发射信号(即知)满足同步、同周期、且不同时输出为高电平状态。

[0056]

如图7所示,输出信号与相互交叠。死区时间由pwm控制输出,为了使h桥上下半管不会因开启和关断延迟问题发生同时导通而设置的保护时段,死区时间设置较大,模块能够更加可靠的工作,但会带来输出波形的失真和输出效率的降低,设计死区时间小时,输出波形更好。以不炸毁mosfet管、输出不短路为目的,本发明通过时序控制方式将死区时间控制在200ns。

[0057]

功率放大步骤:功率放大电路4将正半周信号及负半周信号放大后接入换能器,驱动换能器发出信源信号。信源信号脉冲宽度tp与声呐最小探测距离与声呐最小探测距离rmin和声呐距离分辨率δr存在以下约束关系:

[0058]

t

p

≤2r

min

/c

[0059]

t

p

≤2δr/c

[0060]

其中,c为声速。

[0061]

以上应用了具体个例对本发明进行阐述,只是用于帮助理解本发明,并不用以限制本发明。对于本发明所属技术领域的技术人员,依据本发明的思想,还可以做出若干简单推演、变形或替换。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。