一种降低栅极沟槽处电场的sic功率mos器件结构

技术领域

1.本发明属于集成电路技术领域,涉及碳化硅功率器件,特别涉及一种降低栅极沟槽处电场的sic功率mos器件结构。

背景技术:

2.碳化硅(sic)材料具有宽禁带、高热导率、高击穿电场、高载流子饱和漂移速度等优异特性,因此特别适合制作高压、高功率的半导体电力电子器件。

3.沟槽型功率mos(umos)是基于槽栅工艺开发出的一种功率半导体器件,由于消除了vdmos结构中的jfet区,这为功率mos提供了降低内部阻抗的机会,使导通电阻更接近于理想值;相对于横向器件,其单元尺寸小,所以元胞密度更大,电流密度也就更大,在节省芯片面积的同时还能产生大的电流驱动,而且易形成亚微米沟道。因此,功率sic umos凭借比导通电阻小,元胞密度大的优势,使得其被称为第二代sic mosfet器件,且具有较高的市场占有率。

4.但是,umos在耐压方面不如横向器件,而且受到功率mos工作场景以及umos结构特性的限制,功率mos工作时源漏端往往会突然承受很大的电压,从而产生很大的电场,umos的结构特性决定了电场更容易集中于栅极氧化层拐角处,可能导致栅氧化层被击穿,存在严重的可靠性问题。目前解决栅氧化层可靠性的途径主要由两种,一种是改善栅氧化层质量,使其能承受更高的电场,这只能在材料方面做出改进;另一种是在不降低器件性能的前提下,将栅氧化层底部保护起来,使其受到的电场变小。所以sic umos在设计时存在低比导通电阻与高击穿电压之间的矛盾,这成为了当今umos技术发展的主要研究方向。

5.现有的保护措施,大多数采用在栅槽下方加p 屏蔽区域的方法来降低槽栅底部的电场,但是这种结构会产生pbody与p 屏蔽区域形成的jfet电阻,使导通电阻增加,后来在pbody下方加电流扩展层(csl)缓解导通导电增加的趋势,但效果并不明显,且巴利加优值也有所下降。

技术实现要素:

6.为了克服上述现有技术的缺点,本发明的目的在于提供一种降低栅极沟槽处电场的sic功率mos器件结构,采用多级阶梯氧结构,结合p 屏蔽区域与电流扩展层,以期在降低槽栅拐角处的电场的同时进一步降低导通电阻,并保证巴利加优值不显著下降甚至有所提高。

7.为了实现上述目的,本发明采用的技术方案是:

8.一种降低栅极沟槽处电场的sic功率mos器件结构,包括自下而上布置的漏区、衬底以及漂移区,在漂移区上方中央位置设置栅极多晶硅,在栅极多晶硅左右两侧设置对称的半元胞结构,每个所述半元胞结构,包括位于漂移区上方边沿的源级金属,源级金属下方设置p 区,p 区的下方和内侧均被pwell包围,所述源级金属内侧上方与栅极多晶硅之间设置n 源区,所述pwell向上延伸至所述n 源区远离栅极多晶硅的一侧底部,所述n 源区的另

一侧底部下方设置pbody,所述pbody与漂移区之间设置n型电流扩展层,所述栅极多晶硅除顶部外被氧化层包围,且栅极多晶硅的底部以及其氧化层的侧面与底部之间均以阶梯形式连接,所述氧化层的底部与漂移区之间设置p 区,所述p 区作为氧化层底部的电场终止层,其掺杂浓度大于所述p 区的掺杂浓度。

9.在一个实施例中,所述源级金属为铝,沟槽深度范围0.98~1.02μm。

10.在一个实施例中,所述p 区掺杂浓度范围(2.8~3.2)

×

10

18

,所述pwell的掺杂浓度范围(1.8~2.2)

×

10

18

,所述n 源区的掺杂浓度范围(4.8~5.2)

×

10

18

,所述pbody的深度范围0.48~0.52μm,掺杂浓度范围(1.8~2.2)

×

10

17

,所述n型电流扩展层的掺杂浓度范围(1.8~2.2)

×

10

17

,所述p 区的掺杂浓度范围(0.8~1.2)

×

10

20

。

11.在一个实施例中,所述p 区位于源级金属远离栅极多晶硅的一侧下方。

12.在一个实施例中,所述氧化层的侧面与底部之间的阶梯结构,仅与所述p 区相邻。

13.在一个实施例中,所述氧化层的侧面与底部之间的阶梯结构,同时与所述p 区和所述n型电流扩展层相邻。

14.在一个实施例中,所述n型电流扩展层的底部与槽栅底部平齐,n型电流扩展层的掺杂浓度为(1.2~1.4)

×

10

17

。

15.与现有技术相比,本发明的有益效果是:

16.1.本发明降低了导通电阻,电流驱动能力更强。

17.2.本发明降低了槽栅拐角处的电场,使得槽栅底部得到了更好的保护,巴利加优值fom(figure of merit)得到提高。

附图说明

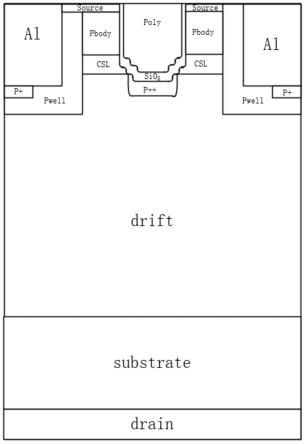

18.图1是本发明整体结构图。

19.图2是本发明顶部结构图。

20.图3是现有μmos结构示意图。

21.图4是现有μmos拐角处电场示意图。

22.图5是现有μmos改进后结构示意图。

23.图6是现有μmos改进后的拐角处电场示意图。

24.图7是本发明提出的阶梯氧μmos改进后结构1示意图。

25.图8是本发明提出的阶梯氧μmos改进后的拐角处电场示意图。

26.图9是本发明提出的阶梯氧μmos改进后结构2示意图。

27.图10是本发明提出的阶梯氧μmos改进后的拐角处电场示意图。

具体实施方式

28.下面结合附图和实施例详细说明本发明的实施方式。

29.sic沟槽型mos(μmos)相对于平面型mos(vdmos)器件,具有更低的导通电阻,但是其槽栅拐角处的电场强度很大,易引发可靠性问题,而且功率sic mosfet器件在应用过程中,通常是在大容量大功率且感性负载的场景下,这时器件会工作在阻断模式,栅氧sio2承受高电场,很容易达到sio2的临界击穿场强,造成氧化层退化或击穿,从而导致器件失效,

存在严重的安全隐患。具体而言,这些结构的槽栅底部电场强,影响栅极氧化层可靠性;现有的一些改进方法虽然能缓解槽栅底部电场,但使导通电阻变大。

30.基于此,本发明使用sentaurus软件进行结构设计并验证,其整体结构如图1所示,由于其结构是左右对称的,所以后续图片均以左半元胞形式给出。

31.参考图1和图2,本发明提供了一种降低栅极沟槽处电场的sic功率mos器件结构,包括漏区、衬底以及漂移区,衬底在漏区之上,漂移区在衬底之上,在漂移区上方中央位置设置栅极多晶硅,在栅极多晶硅左右两侧设置对称的半元胞结构。

32.以左半元胞的结构为例,其包括位于漂移区上方边沿的源级金属,本发明中,源级金属为铝,沟槽深度示例地可设置为0.98~1.02μm,优选1μm。本发明中,深度,指的是上下方向。

33.源级金属下方设置p 区,p 区优选设置在源级金属远离栅极多晶硅的一侧下方,也即其左右方向的宽度最好应小于源级金属的宽度,示例地,p 区掺杂浓度范围2.8~3.2

×

10

18

,优选3

×

10

18

。p 区的下方和内侧均被pwell包围,示例地,pwell的掺杂浓度范围1.8~2.2

×

10

18

,优选2

×

10

18

。pwell与漂移区构成的pn结是主要的承受电压区域,源级沟槽底部和栅极沟槽一起承受电压,所以槽栅下方的电场可以得到一定程度的缓解。

34.n 源区设置在源级金属内侧上方与栅极多晶硅之间,pwell向上延伸至n 源区左侧底部,示例地,n 源区的掺杂浓度范围4.8~5.2

×

10

18

,优选5

×

10

18

。n 源区的右侧底部下方设置pbody,pbody的左侧与pwell的右侧相接,示例地,pbody的深度范围0.48~0.52μm,优选0.5μm,掺杂浓度范围1.8~2.2

×

10

17

,优选2

×

10

17

。

35.本发明在pbody与漂移区之间设置n型电流扩展层,示例地,n型电流扩展层的掺杂浓度范围1.8~2.2

×

10

17

,优选2

×

10

17

。n型电流扩展层提高了电流通路的载流子浓度,所以是减小导通电阻的关键部分。

36.栅极多晶硅除顶部外,底面和各侧面均被氧化层即sio2包围,且栅极多晶硅的底部以及其氧化层的侧面与底部之间均以阶梯形式连接,氧化层的底部与漂移区之间设置p 区,p 区作为氧化层底部的电场终止层,其掺杂浓度显然应大于p 区的掺杂浓度,示例地,可为0.8~1.2

×

10

20

,优选1

×

10

20

。

37.根据该结构,本发明在在基本不影响器件其他性能前提下降低槽栅底部电场强度的同时,导通电阻较现有改进方法也有所降低,并且还可使得器件的击穿电压提高。其原理在于:电流扩展层提高了电流通路上的载流子浓度,所以使导通电阻降低;由于栅极氧化层为阶梯状,增大了器件处于雪崩状态时的耗尽区,所以器件的击穿电压提高。

38.图3示出了常规的umos结构形式,与本发明相比,其未设n型电流扩展层和p 区,导通电阻为7.322mω

·

cm2,击穿电压为1322v,巴利加优值fom(figure of merit)为0.238kv2/mω

·

cm2,由于栅氧化层底部没有保护,其底部电场达到了3.79mv,如图4所示。其参数条件:栅源电压vgs为15v,增加漏源电压,当漏源电压vds为1.86v时,得到导通电阻;栅源电压vgs为0v,增加漏源电压,当漏极电流id为1ma时,得到击穿电压。

39.现有技术对其进行改进后的结构形式如图5所示,增设了n型电流扩展层和p 区,但并未采用本发明的阶梯形式。

40.与图3的结构相比,该方案增加了p 区域,但是p 区域会和pbody形成jfet区域,使导通电阻变大,所以又引入n型电流扩展层降低导通电阻。导通电阻为11.062mω

·

cm2,

击穿电压为1466v,巴利加优值fom为0.194kv2/mω

·

cm2,可见此结构虽然击穿电压上升,但是导通电阻也变大了,所以巴利加优值有所下降,由于p 掩蔽区域的存在,最大电场出现在p 掩蔽区域下方,为3.37mv,但是槽栅底部得到了有效保护,其电场降低到了3mv以下,如图6所示。其参数条件与前述的图3和图4参数条件相同。

41.本发明使用阶梯形式,权衡了导通电阻、击穿电压和槽栅拐角处电场三者间的关系。阶梯形式的氧化层减弱了p 掩蔽区域的耗尽作用,所以槽栅拐角处得到保护的同时也降低了导通电阻,结构后的结构分别如图7和图9所示。

42.图7中的结构中,氧化层的侧面与底部之间的阶梯结构,同时与p 区和n型电流扩展层相邻。导通电阻为8.171mω

·

cm2,击穿电压为1429v,巴利加优值fom为0.25kv2/mω

·

cm2,与现有技术相比,导通电阻降低了26.1%,巴利加优值得到显著提升,最大电场出现在p 掩蔽区域下方,为3.09mv,其槽栅拐角处电场也降低到了3mv以下,如图8所示。其参数条件与前述的图3和图4参数条件相同。

43.图9中的结构中,氧化层的侧面与底部之间的阶梯结构,仅与p 区相邻。导通电阻为9.084mω

·

cm2,击穿电压为1461v,巴利加优值fom为0.235kv2/mω

·

cm2,与现有技术相比,击穿电压基本不变,导通电阻降低了17.9%,巴利加优值也得到提升,最大电场出现在p 掩蔽区域下方,为3.37mv,其槽栅拐角处电场为2.7mv左右,如图10所示,可以看出电场强度受到了显著抑制。其参数条件与前述的图3和图4参数条件相同。

44.在本发明的替代方案中,可通过改变电流扩展层的形状,并调节其掺杂浓度,以保护槽栅。示例地,可将n型电流扩展层的底部与槽栅底部保持平齐,并调整n型电流扩展层的掺杂浓度为(1.2~1.4)

×

10

17

,p 区域作为电场终止层,降低漏极高电场对槽栅底部的影响。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。